# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **General Description**

The MAX3710 limiting amplifier and burst mode laser driver provides a highly integrated, low-cost, high-performance PMD solution for GPON/EPON ONU applications in modules or directly on the ONU board.

The low-jitter laser diode driver provides transmit burst mode average power control (APC) of laser bias current as well as an integrated modulation current control loop (extinction ratio control, or ERC). The ERC eliminates the need for temperature lookup tables (LUTs) controlling the modulation current.

The low-noise limiting amplifier maximizes optical sensitivity and has adjustable SD/LOS threshold plus programmable output levels. The differential CML output stage features a slew-rate adjustment for 1.25Gbps EPON operation. Integrated bias current monitor, burst mode Tx power monitor, and a digital laser power monitor enable a low-cost implementation of the next-generation GPON and EPON modules with digital diagnostics.

A novel auto-calibration mode enables low-cost fiber optic module production. An integrated 3-wire digital interface controls the laser driver and limiting amplifier functions, and enables communication with a low-cost controller.

The MAX3710 is offered in a small, 4mm x 4mm, 24-pin TQFN package with exposed pad, and operates over the -40°C to +95°C temperature range.

#### Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- Simplifies Module Manufacturing

- ♦ Enables Single-Temperature Module Testing

♦ Production Laser Auto-Calibration Mode

- Improved ONU Performance

- Integrated APC and ERC Loops

- Separate Laser Driver Supply (Rogue ONU Shutdown)

- Flexibility

- ♦ LVDS, LVPECL, and CML Compatible High-Speed I/Os

- ♦ Programmable I/O Polarity

- ♦ 3-Wire Digital Interface

- Safety and Reliability

- ♦ Integrated Safety Features with FAULT Mask Register

- ♦ Supports SFP MSA and SFF-8472 Digital Diagnostic

- ♦ Selectable Analog Monitor of Laser Power or BIAS Current at BMON Pin

#### **Applications**

BOSA On-Board GPON/EPON ONU

#### **ABSOLUTE MAXIMUM RATINGS**

| $V_{CCX},V_{CCTO},V_{CCD}$ -0.3V to 4.0V                                      |

|-------------------------------------------------------------------------------|

| Voltage Range at DISABLE, SDA, SCL, CSEL,                                     |

| FAULT, LOS, MDREF, LPD0.3V to (V <sub>CC</sub> + 0.3V)                        |

| Voltage Range at RIN+, RIN $(V_{CC} - 1.7V)$ to $(V_{CC} + 0.3V)$             |

| Voltage Range at ROUT+, ROUT $(V_{CC} - 2V)$ to $(V_{CC} + 0.3V)$             |

| Voltage Range at TIN+, TIN-,                                                  |

| BEN+, BEN0.3V to (V <sub>CC</sub> + 0.3V)                                     |

| Voltage Range at TOUT0.3V to V <sub>CCTO</sub>                                |

| Voltage Range at IOUT(V <sub>CCTO</sub> - 1.8V) to (V <sub>CCTO</sub> + 1.2V) |

| Current Range into FAULT, LOS,                                                |

| MDIN, SDA1mA to +5mA                                                          |

| Current Range into LPD                                | 5mA to +5mA             |

|-------------------------------------------------------|-------------------------|

| Current out of ROUT+, ROUT                            | 40mA                    |

| Current into TOUT                                     | 180mA                   |

| Current into IOUT                                     | 120mA                   |

| Voltage Range at BMON                                 | 0.3V to V <sub>CC</sub> |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                         |

| TQFN (derate 27.8mW/°C above +70°C)                   | 2222mW                  |

| Storage Temperature Range                             | -55°C to +150°C         |

| Die Attach Temperature                                | +400°C                  |

| Lead Temperature (soldering, 10s)                     | +300°C                  |

| Soldering Temperature (reflow)                        | +260°C                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

| PARAMETER                       | SYMBOL               | CONDITIONS                                                                      | MIN  | ТҮР  | MAX  | UNITS             |  |

|---------------------------------|----------------------|---------------------------------------------------------------------------------|------|------|------|-------------------|--|

| OPERATING CONDITIONS            |                      |                                                                                 |      |      |      |                   |  |

| Power Supply Voltage            | V <sub>CC</sub>      |                                                                                 | 2.97 | 3.3  | 3.63 | V                 |  |

| POWER SUPPLY                    |                      |                                                                                 |      |      |      |                   |  |

| Power-Supply Current            | ICC                  | Includes Rx CML output current, excludes Tx $I_{BIAS}$ = 20mA, $I_{MOD}$ = 40mA |      | 75   | 110  | mA                |  |

| POWER-ON RESET                  |                      |                                                                                 |      |      |      |                   |  |

| $V_{CC}$ for Enable High        |                      | $V_{\mbox{\scriptsize CCX}}$ connected to $V_{\mbox{\scriptsize CCD}}$          |      | 2.55 | 2.75 | V                 |  |

| V <sub>CC</sub> for Enable Low  |                      | $V_{CCX}$ connected to $V_{CCD}$                                                | 2.3  | 2.45 |      | V                 |  |

| <b>Rx INPUT SPECIFICATION</b>   |                      |                                                                                 |      |      |      |                   |  |

| Differential Input Resistance   | R <sub>IN</sub>      |                                                                                 | 75   | 100  | 125  | Ω                 |  |

| Input Sensitivity               | V <sub>INMIN</sub>   | 2 <sup>23</sup> - 1 PRBS, 2.5Gbps, TX_EN = 0<br>(Note 2)                        |      | 1.3  | 2    | mV <sub>P-P</sub> |  |

| Input Overload                  | V <sub>INMAX</sub>   | (Note 2)                                                                        | 1.2  |      |      | V <sub>P-P</sub>  |  |

| Differential Input Datum Lago   | 0                    | Device powered on, $f \le 2GHz$                                                 |      | 19   |      | dB                |  |

| Differential Input Return Loss  | S <sub>DD11</sub>    | Device powered on, $f \le 5GHz$                                                 |      | 12   |      | UB                |  |

| Common-Mode Input Return        | c                    | Device powered on, $1GHz \le f \le 2GHz$                                        |      | 11   |      | dB                |  |

| Loss                            | S <sub>CC11</sub>    | Device powered on, $2GHz \le f \le 5GHz$                                        | 14   |      |      | uв                |  |

| <b>Rx OUTPUT SPECIFICATION</b>  |                      |                                                                                 |      |      |      |                   |  |

| Differential Output Resistance  | R <sub>OUTDIFF</sub> |                                                                                 | 75   | 100  | 125  | Ω                 |  |

| Differential Output Deturn Lass | <b>S</b>             | Device powered on, $f \le 2GHz$                                                 |      | 19   |      | dD                |  |

| Differential Output Return Loss | S <sub>DD22</sub>    | Device powered on, $2GHz \le f \le 5GHz$                                        |      | 15   |      | - dB              |  |

| Common-Mode Output Return       | C                    | Device powered on, $f \le 2GHz$                                                 |      | 14   |      | dB                |  |

| Loss                            | S <sub>CC22</sub>    | Device powered on, $2GHz \le f \le 5GHz$                                        |      | 10   |      | uв                |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                        | SYMBOL          | CO                                                                                                                            | NDITIONS                                                  | MIN                      | TYP | MAX  | UNITS             |

|--------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------|-----|------|-------------------|

|                                                  |                 | $\begin{array}{l} 4mV_{P-P} \leq V_{IN} \leq 1200mV_{P-P}, \\ SET\_CML[3:0] = 10d \end{array}$                                |                                                           | 600                      | 800 | 1000 | m)/               |

| Voltage                                          |                 | $4mV_{P-P} \le V_{IN} \le 12$<br>SET_CML[3:0] = 0                                                                             |                                                           |                          | 410 |      | mV <sub>P-P</sub> |

| CML Differential Output<br>Voltage When Disabled |                 | Output AC-couple<br>SET_CML[3:0] =                                                                                            | ed, V <sub>INMAX</sub> at input,<br>10d (Note 2)          |                          |     | 5    | mV <sub>P-P</sub> |

| Data Output Transition Time                      |                 | $4mV_{P-P} \le V_{IN} \le 12$<br>SLEW_RATE = 1                                                                                | 200mV <sub>P-P</sub> ,                                    |                          | 85  | 115  |                   |

| (20% to 80%) (Note 2)                            |                 | $4mV_{P-P} \le V_{IN} \le 12$<br>SLEW_RATE = 0                                                                                | 200mV <sub>P-P</sub> ,                                    |                          | 140 | 200  | ps                |

| LOS Output High Voltage                          | V <sub>OH</sub> | $R_{LOS} = 4.7 k\Omega - 10$                                                                                                  | 0k $\Omega$ to V <sub>CC</sub>                            | V <sub>CC</sub> -<br>0.1 |     |      | V                 |

| LOS Output Low Voltage                           | V <sub>OL</sub> | $R_{LOS} = 4.7 k\Omega - 10$                                                                                                  | 0k $\Omega$ to V <sub>CC</sub>                            | 0                        |     | 0.4  | V                 |

| Rx TRANSFER CHARACTERIS                          | TICS            |                                                                                                                               |                                                           |                          |     |      |                   |

|                                                  |                 | 2.5Gbps, 4mV <sub>P-P</sub><br>SET_CML[3:0] =                                                                                 | $\leq$ V <sub>IN</sub> $\leq$ 1200mV <sub>P-P</sub> , 10d |                          | 7   | 15   |                   |

| Deterministic Jitter<br>(Notes 2, 3)             | DJ              | 1.25Gbps, $4mV_{P-P} \le V_{IN} \le 1200mV_{P-P}$ ,<br>SET_CML[3:0] = 10d                                                     |                                                           |                          | 10  | 20   | ps <sub>P-P</sub> |

|                                                  |                 | $\begin{array}{l} 125 Mbps, \ 4mV_{P-P} \leq V_{IN} \leq 1200 mV_{P-P}, \\ SET_CML[3:0] = 10d, \ K28.5 \ pattern \end{array}$ |                                                           |                          | 21  |      |                   |

| Random Jitter                                    | RJ              | Input = 4mV <sub>P-P</sub> at<br>1111 0000 patterr<br>(Notes 2, 4)                                                            | t 2.5Gbps,<br>n, SET_CML[3:0] = 10d                       |                          | 3.5 | 5    | ps <sub>RMS</sub> |

| Low-Frequency Cutoff<br>(Simulated Value)        |                 | I/O coupling capa                                                                                                             | acitors = $1\mu F$                                        |                          | 10  |      | kHz               |

| Small-Signal Bandwidth<br>(Simulated Value)      |                 | SLEW_RATE = 1                                                                                                                 |                                                           |                          | 2.0 |      | GHz               |

| LOS SPECIFICATIONS (Notes 2                      | 2, 5)           |                                                                                                                               |                                                           |                          |     |      |                   |

| LOS Hysteresis                                   |                 | 10log(V <sub>DEASSERT</sub>                                                                                                   | (V <sub>ASSERT</sub> )                                    | 1.25                     | 2.2 |      | dB                |

| LOS Assert/Deassert Time                         |                 | (Note 6)                                                                                                                      |                                                           | 2.3                      |     | 30   | μs                |

| LOS Assert Sensitivity Range                     |                 | LOS_RANGE = 0                                                                                                                 |                                                           | 4.6                      |     | 36   | m\/= -            |

| LOS Assent Sensitivity hallge                    |                 | LOS_RANGE = 1                                                                                                                 |                                                           | 14                       |     | 115  | mV <sub>P-P</sub> |

|                                                  |                 |                                                                                                                               | SET_LOS = 5                                               | 3                        | 3.8 | 4.6  |                   |

|                                                  |                 | LOS assert                                                                                                                    | SET_LOS = 31                                              | 18                       | 23  | 28   |                   |

| LOS Assert/Deassert Level                        |                 |                                                                                                                               | SET_LOS = 63                                              | 36                       | 47  | 56   | mV <sub>P-P</sub> |

| (Low Range, LOS_RANGE = 0)                       |                 |                                                                                                                               | SET_LOS = 5                                               | 5                        | 6.5 | 8    |                   |

|                                                  |                 | LOS deassert                                                                                                                  | SET_LOS = 31                                              | 32                       | 39  | 46   |                   |

|                                                  |                 |                                                                                                                               | SET_LOS = 63                                              | 64                       | 80  | 95   |                   |

### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                          | SYMBOL            | COI                                         | NDITIONS                                     | MIN                   | TYP  | MAX                                       | UNITS             |

|----------------------------------------------------|-------------------|---------------------------------------------|----------------------------------------------|-----------------------|------|-------------------------------------------|-------------------|

|                                                    |                   |                                             | SET_LOS = 5                                  | 9                     | 11.5 | 14                                        |                   |

|                                                    |                   | LOS assert                                  | SET_LOS = 31                                 | 55                    | 68   | 80                                        |                   |

| LOS Assert/Deassert Level                          |                   |                                             | SET_LOS = 63                                 | 115                   | 138  | 160                                       | mV <sub>P-P</sub> |

| (High Range, LOS_RANGE = 1)                        |                   |                                             | SET_LOS = 5                                  | 15                    | 19   | 23                                        | ιινΡ-Ρ            |

|                                                    |                   | LOS deassert                                | SET_LOS = 31                                 | 97                    | 117  | 136                                       |                   |

|                                                    |                   |                                             | SET_LOS = 63                                 | 197                   | 238  | 278                                       |                   |

| Tx INPUT SPECIFICATIONS                            |                   |                                             |                                              |                       |      |                                           |                   |

| Differential Input Resistance<br>(TIN and BEN)     |                   |                                             |                                              |                       | 13   |                                           | kΩ                |

| Internal Common-Mode Bias<br>Voltage (TIN and BEN) |                   | For AC-coupled c                            | peration                                     |                       | 1.3  |                                           | V                 |

| Differential Input Voltage<br>(TIN and BEN)        |                   | DC-coupled, 1009<br>Figure 1 and Figu       | $\Omega$ , differential resistors, re 3      | 0.2                   |      | 1.6                                       | V <sub>P-P</sub>  |

| Common-Mode Input Voltage<br>Range (TIN and BEN)   |                   | DC-coupled, Figu                            | re 1 and Figure 3                            | 1.125                 |      | V <sub>CC</sub> -<br>V <sub>IN</sub> /2.5 | V                 |

|                                                    |                   | DISABLE = V <sub>CC</sub><br>DISABLE = GND  |                                              |                       |      | 10                                        |                   |

| DISABLE Input Current                              |                   |                                             |                                              | 33 60.                |      | 60.5                                      | μA                |

| DISABLE Input High Voltage                         | VIH               |                                             |                                              | 1.8                   |      | V <sub>CC</sub>                           | V                 |

| DISABLE Input Low Voltage                          | V <sub>IL</sub>   |                                             |                                              | 0                     |      | 0.8                                       | V                 |

| DISABLE Input Hysteresis                           | V <sub>HYST</sub> |                                             |                                              |                       | 80   |                                           | mV                |

| DISABLE Input Impedance                            | R <sub>PULL</sub> | Pullup resistor                             |                                              | 60                    | 100  | 138                                       | kΩ                |

| Tx OUTPUT SPECIFICATIONS                           |                   |                                             |                                              |                       |      | ·                                         |                   |

| FAULT Output High Voltage                          | V <sub>OH</sub>   | $R_{FAULT}$ is 4.7k $\Omega$ -              | 10k $\Omega$ to V <sub>CC</sub>              | V <sub>CC</sub> - 0.1 |      |                                           | V                 |

| FAULT Output Low Voltage                           | V <sub>OL</sub>   | $R_{FAULT}$ is 4.7k $\Omega$ -              | 10k $\Omega$ to V <sub>CC</sub>              | 0                     |      | 0.4                                       | V                 |

| LPD Output High Voltage                            | V <sub>OH</sub>   | $I_{LPD} = -1mA$                            |                                              | V <sub>CC</sub> - 0.5 | ,    |                                           | V                 |

| LPD Output Low Voltage                             | V <sub>OL</sub>   | $I_{LPD} = +1mA$                            |                                              | 0                     |      | 0.4                                       | V                 |

| LASER MODULATOR                                    |                   | -                                           |                                              |                       |      |                                           |                   |

| Maximum Modulation-On<br>Current                   |                   |                                             |                                              | 85                    |      |                                           | mA                |

| Minimum Modulation-On<br>Current                   |                   | -                                           |                                              |                       |      | 5                                         | mA                |

| Modulation Current DAC<br>Stability                |                   | 10mA ≤ I <sub>MOD</sub> ≤ 85mA (Notes 2, 7) |                                              |                       | 1    | 4                                         | %                 |

| Modulation Current Rise/Fall                       |                   | 20% to 80%, 10m $R_{LOAD} = 12\Omega$ , TR  | A ≤ I <sub>MOD</sub> ≤ 85mA,<br>F[1:0] = 11b |                       | 65   | 120                                       |                   |

| Time (Note 2)                                      |                   | 20% to 80%, 10m $R_{LOAD} = 12\Omega$ , TR  | A ≤ I <sub>MOD</sub> ≤ 85mA,<br>F[1:0] = 00b |                       | 72   |                                           | ps                |

### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                       | SYMBOL                                                         | CONDITIONS                                                                 | MIN | ТҮР | MAX  | UNITS             |

|-----------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------|-----|-----|------|-------------------|

| Compliance Voltage at TOUT                                      | ompliance Voltage at TOUT V <sub>TOUT</sub> Instanta<br>10mA s |                                                                            | 0.6 |     | 2.4  | V                 |

|                                                                 |                                                                | $10mA \le I_{MOD} \le 85mA$ , 2.5Gbps                                      |     | 15  | 40   |                   |

| Deterministic Jitter                                            | DJ                                                             | $10\text{mA} \le I_{MOD} \le 85\text{mA}, 1.25\text{Gbps}$                 |     | 15  |      | psp_p             |

| (Notes 2, 3)                                                    | 20                                                             | $10\text{mA} \le I_{\text{MOD}} \le 85\text{mA}$ , 125Mbps, K28.5 pattern  |     | 20  |      | P3P-P             |

| Random Jitter                                                   | RJ                                                             | $10mA \le I_{MOD} \le 20mA$ , 1111 0000 pattern                            |     | 1.2 | 1.65 | 00-110            |

| (Notes 2, 4)                                                    | ηJ                                                             | $20mA \le I_{MOD} \le 85mA$ , 1111 0000 pattern                            |     | 1   | 1.45 | ps <sub>RMS</sub> |

| BIAS GENERATOR                                                  |                                                                |                                                                            |     |     |      |                   |

| Maximum Bias Current                                            |                                                                | Current into TOUT                                                          | 70  |     |      | mA                |

| Minimum Bias Current                                            |                                                                | Current into TOUT                                                          |     |     | 1    | mA                |

| Bias Current DAC Stability                                      |                                                                | $2mA \le I_{BIAS} \le 70mA, V_{TOUT} = 2V$ (Notes 2, 7)                    |     | 1   | 4    | %                 |

| Bias Current Monitor Current                                    | I <sub>BIAS</sub> /                                            | External resistor to GND defines voltage gain, $2mA \le I_{BIAS} \le 6mA$  | 54  | 64  | 72   |                   |

| Gain                                                            | BMON                                                           | External resistor to GND defines voltage gain, $6mA \le I_{BIAS} \le 70mA$ | 64  | 72  | 80   | - A/A             |

| Compliance Voltage Range at BMON                                | V <sub>BMON</sub>                                              |                                                                            | 0   |     | 1.8  | V                 |

| BMON Current Gain Stability<br>(as Bias Monitor)                |                                                                | $2mA \le I_{BIAS} \le 70mA$ (Notes 2, 7)                                   |     | 2   | 5    | %                 |

| LASER CONTROL SPECIFICAT                                        | TIONS                                                          |                                                                            |     |     |      | •                 |

| APC Loop Stability (1.25Gbps,                                   |                                                                | $I_{MDINAVG} = 50\mu A, K_{MD} \times SE = 0.005$                          |     | 0.1 |      | 101 (10)          |

| 2 <sup>23</sup> - 1 PRBS Pattern) (Note 8)                      |                                                                | $I_{MDINAVG} = 2mA, K_{MD} \times SE = 0.05$                               |     | 0.1 |      | 10log(dB)         |

| APC Loop Stability (2.5Gbps,                                    |                                                                | $I_{MDINAVG} = 50\mu A$ , $K_{MD} \times SE = 0.005$                       |     | 0.1 |      | 101               |

| 2 <sup>23</sup> - 1 PRBS Pattern) (Note 8)                      |                                                                | $I_{MDINAVG} = 2mA, K_{MD} \times SE = 0.05$                               |     | 0.1 |      | 10log(dB)         |

| ERC Loop Stability (1.25Gbps, 2 <sup>23</sup> - 1 PRBS Pattern, |                                                                | $I_{MDINAVG} = 50\mu A, K_{MD} \times SE = 0.005$                          |     | 0.5 |      | - 10log(dB)       |

| e <sub>R</sub> = 11dB) (Note 8)                                 |                                                                | $I_{MDINAVG} = 2mA, K_{MD} \times SE = 0.05$                               |     | 0.5 |      |                   |

| ERC Loop Stability (2.5Gbps, 2 <sup>23</sup> - 1 PRBS Pattern,  |                                                                | $I_{MDINAVG} = 50\mu A, K_{MD} \times SE = 0.005$                          |     | 1.3 |      | - 10log(dB)       |

| $e_{\rm R} = 11$ dB) (Note 8)                                   |                                                                | $I_{MDINAVG} = 2mA, K_{MD} \times SE = 0.05$                               |     | 1.1 |      |                   |

| MDIN Bias Voltage                                               | V <sub>MDIN</sub>                                              |                                                                            |     | 1.2 |      | V                 |

| MD Average Current Range                                        | IMDINAVG                                                       | Average current into MDIN                                                  | 50  |     | 2000 | μA                |

| Programmable Extinction Ratio Range e <sub>R</sub>              |                                                                | P1/P0 (DPC closed-loop operation)                                          | 10  | 16  | 24   |                   |

### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                    | SYMBOL               | CONDITIONS                                                                                                                                    | MIN                        | ТҮР | MAX                         | UNITS |

|--------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|-----------------------------|-------|

| MD Current Monitor/BMON<br>Activation Time                   |                      | From the rising edge of the final SCL<br>clock of the 3-wire cycle to 90% of<br>steady state at BMON                                          |                            | 100 |                             | ns    |

| SAFETY FEATURES                                              |                      |                                                                                                                                               |                            |     |                             |       |

| Fault Threshold Voltage at<br>TOUT                           | V <sub>TOUT</sub>    | Fault always occurs for V <sub>TOUT</sub> < 0.35V, fault never occurs for V <sub>TOUT</sub> $\ge$ 0.55V                                       | 0.35                       |     | 0.55                        | V     |

| Fault Threshold Voltage at<br>MDIN                           | V <sub>MDIN</sub>    | Fault always occurs for V <sub>MDIN</sub> < 0.3V, fault never occurs for V <sub>MDIN</sub> $\ge$ 0.5V                                         | 0.3                        |     | 0.5                         | V     |

| Fault Threshold Voltage at<br>IOUT                           |                      | Fault always occurs for $V_{IOUT} < V_{CCTO}$<br>- 1.7V, fault never occurs for $V_{IOUT} \ge V_{CCTO}$ - 1.45V, $V_{CCTO} = 3.3V$            | V <sub>ССТО</sub><br>- 1.7 |     | V <sub>CCTO</sub><br>- 1.45 | V     |

| Warning Threshold Voltage at<br>BEN (Differential Voltage)   |                      | Warning occurs if I(BEN+) - (BEN-)I <<br>20mV and never occurs if I(BEN+) -<br>(BEN-)I ≥ 100mV                                                | 20                         |     | 100                         | mV    |

| Warning Threshold Voltage at<br>BEN (Common-Mode Voltage)    |                      | Warning occurs if both BEN+ and BEN-<br>fall below 880mV                                                                                      |                            | 880 |                             | mV    |

| Fault Threshold Voltage at<br>V <sub>CCTO</sub>              |                      | Fault always occurs for V_{CCTO} < 2V; fault never occurs for V_{CCTO} $\geq$ 2.95V                                                           | 2                          |     | 2.95                        | V     |

| Maximum Laser Current in<br>Disable State or Burst-Off State |                      | Combined total current into TOUT during<br>fault, DISABLE = 1, TX_EN = 0, or<br>BEN = 0                                                       |                            |     | 100                         | μA    |

| Tx TIMING SPECIFICATIONS                                     |                      | L                                                                                                                                             |                            |     |                             |       |

| DPC Loop Initialization Time                                 | t <sub>APCINIT</sub> | $I_{BIAS} = 40$ mA and $I_{MOD} = 60$ mA,<br>$I_{BIAS_{INT}} = 8$ mA, time from restart to<br>$I_{BIAS}$ and $I_{MOD}$ at 90% of steady state |                            | 3   |                             | μs    |

| Burst Enable Time                                            | <sup>t</sup> BSTART  | Time from 50% of BEN $\pm$ input signal to $I_{BIAS}$ and $I_{MOD}$ at 90% of steady state (Note 2)                                           |                            |     | 2                           | ns    |

| Burst Disable Time                                           | <sup>t</sup> BSTOP   | Time from 50% of BEN $\pm$ input signal to $I_{BIAS}$ and $I_{MOD}$ at 10% of steady state (Note 2)                                           |                            |     | 2                           | ns    |

| Minimum Burst-On Time to<br>Update BIAS and MOD              | <sup>t</sup> BRSTON  | MDON_DLY[1:0] = 00 (Note 2)                                                                                                                   |                            | 60  | 100                         | ns    |

| Minimum Burst-Off Time to<br>Update BIAS and MOD             | <sup>t</sup> BRSTOFF | (Note 2)                                                                                                                                      |                            | 110 | 200                         | ns    |

| DISABLE Assert Time t <sub>OFF</sub>                         |                      | Time from rising edge of DISABLE input signal to $\rm I_{BIAS}$ and $\rm I_{MOD}$ at 10% of steady state (Note 2)                             |                            | 30  | 100                         | ns    |

### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                | SYMBOL                                | CONDITIONS                                                                                                                                                                   | MIN   | TYP         | MAX             | UNITS              |

|--------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------|-----------------|--------------------|

| DISABLE Negate Time      | t <sub>ON</sub>                       | Time from falling edge of DISABLEinput signal to IBIAS and IMOD at 90% of<br>steady state (Note 2)                                                                           |       | 300         | ns              |                    |

| Fault Assert Time        | <sup>t</sup> FAULT                    | Time from fault condition to FAULT high, $C_{FAULT} \leq 20pF$ , $R_{FAULT}$ is $4.7k\Omega - 10k\Omega$ to $V_{CC}$ (Note 2)                                                |       | 2.5         | 10              | μs                 |

| LPD Assert Time          | tLPD-ASSERT                           | Time from positive BEN edge to 90% of steady state at LPD output, $C_{LPD} \le 10 pF$                                                                                        |       |             | 100             | ns                 |

| LPD Deassert Time        | t <sub>LPD-</sub><br>DEASSERT         | Time from negative BEN edge to 90% of steady state at LPD output, $C_{LPD} \le 10 pF$                                                                                        |       |             | 100             | ns                 |

| DISABLE to Reset         |                                       | Minimum required time DISABLE must<br>be held high to reset a fault                                                                                                          |       | 100         |                 | ns                 |

| LASER POWER DETECTOR     | (LPD) SPECIFICA                       | ATIONS                                                                                                                                                                       |       |             |                 |                    |

| LPD Threshold Values     |                                       | $ \begin{array}{l} {\sf KIMD[1:0]=00:\ N=LPD\_TH[2:0]+1,} \\ {\sf KIMD[1:0]=01:\ N=2\times(LPD\_TH[2:0]+1),} \\ {\sf KIMD[1:0]=1X:\ N=4\times(LPD\_TH[2:0]+1)} \end{array} $ |       | N x<br>12.5 |                 | μA                 |

| Rx OUTPUT LEVEL DAC      |                                       |                                                                                                                                                                              |       |             |                 |                    |

| Full-Scale Voltage       | V <sub>FS</sub>                       | SET_CML[3:0] = 15d                                                                                                                                                           | 820   | 1000        |                 | mV <sub>P-P</sub>  |

| Resolution               |                                       | 4 bits                                                                                                                                                                       |       | 40          |                 | mV <sub>P-P</sub>  |

| LOS THRESHOLD DAC        |                                       |                                                                                                                                                                              |       |             |                 |                    |

| Full-Scale Voltage       |                                       | LOS_RANGE = 0                                                                                                                                                                |       | 47          |                 | mV <sub>P-P</sub>  |

| Tull-Scale Vollage       |                                       | LOS_RANGE = 1                                                                                                                                                                |       | 138         |                 | ιιν <sub>Ρ</sub> Ρ |

| Resolution               |                                       | LOS_RANGE = 0                                                                                                                                                                |       | 0.75        |                 | mV <sub>P-P</sub>  |

| TIESOIUTION              |                                       | LOS_RANGE = 1                                                                                                                                                                |       | 2.2         |                 | ····νρ-ρ           |

| Integral Nonlinearity    |                                       | SET_LOS[5:0] = 5d to 63d                                                                                                                                                     |       | ±0.7        |                 | LSB                |

| BIAS CURRENT DAC         |                                       |                                                                                                                                                                              |       |             |                 |                    |

| Full-Scale Current       | I <sub>FS_BIAS</sub>                  | I <sub>BIAS</sub> = (12 + BIASREG[9:0]) × LSB_BIAS                                                                                                                           | 70    | 78          |                 | mA                 |

| Resolution               | LSB_BIAS                              | 10-bit DAC                                                                                                                                                                   |       | 75          |                 | μA                 |

| MODULATION CURRENT DA    | NC                                    |                                                                                                                                                                              |       |             |                 |                    |

| Full-Scale Current       | I <sub>FS_MOD</sub>                   | I <sub>MOD</sub> = (20 + MODREG[8:0]) x<br>LSB_MOD                                                                                                                           | 85 89 |             |                 | mA                 |

| Resolution               | LSB_MOD                               | 9-bit DAC                                                                                                                                                                    |       | 167         |                 | μA                 |

| 3-WIRE DIGITAL INTERFACE | <br>E                                 | · · · · · · · · · · · · · · · · · · ·                                                                                                                                        |       |             |                 |                    |

| Input High Voltage       | V <sub>IH</sub>                       |                                                                                                                                                                              | 2.0   |             | V <sub>CC</sub> | V                  |

| Input Low Voltage        | VIL                                   |                                                                                                                                                                              |       |             | 0.8             | V                  |

|                          | I I I I I I I I I I I I I I I I I I I | ļ                                                                                                                                                                            |       |             | -               | L                  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 2.97V \text{ to } +3.63V, T_A = -40^{\circ}\text{C} \text{ to } +95^{\circ}\text{C}; \text{CML}$  receiver output is AC-coupled to differential 100 $\Omega$  load; registers are set to default values, unless implied by test conditions. Typical values are at  $V_{CC} = +3.3V$ ,  $T_A = +25^{\circ}\text{C}$ , data rate = 2.5Gbps,  $I_{BIAS} = 20\text{mA}$ , and  $I_{MOD} = 40\text{mA}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                      | SYMBOL                            | CONDITIONS                                                                       | MIN                   | TYP | MAX | UNITS |

|------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------|-----------------------|-----|-----|-------|

| Input Leakage Current                          | I <sub>IL</sub> , I <sub>IH</sub> | Voltage at pin 0V to $V_{CC}$ , internal pullup or pulldown 75k $\Omega$ typical |                       |     | 85  | μA    |

| Output High Voltage                            | V <sub>OH</sub>                   | External pullup of 4.7k $\Omega$ to V_CC                                         | V <sub>CC</sub> - 0.1 |     |     | V     |

| Output Low Voltage                             | V <sub>OL</sub>                   | External pullup of 4.7k $\Omega$ to V <sub>CC</sub>                              |                       |     | 0.4 | V     |

| <b>3-WIRE DIGITAL INTERFACE T</b>              | IMING (Figure                     | 6)                                                                               | ·                     |     |     |       |

| SCL Clock Frequency                            | f <sub>SCL</sub>                  |                                                                                  |                       |     | 1   | MHz   |

| SCL Pulse-Width High                           | t <sub>CH</sub>                   |                                                                                  | 0.5                   |     |     | μs    |

| SCL Pulse-Width Low                            | t <sub>CL</sub>                   |                                                                                  | 0.5                   |     |     | μs    |

| SDA Setup Time                                 | t <sub>DS</sub>                   |                                                                                  |                       | 100 |     | ns    |

| SDA Hold Time                                  | t <sub>DH</sub>                   |                                                                                  |                       | 100 |     | ns    |

| SCL Rise to SDA Propagation<br>Time            | t <sub>D</sub>                    |                                                                                  |                       | 5   |     | ns    |

| CSEL Pulse-Width Low                           | tcsw                              |                                                                                  | 500                   |     |     | ns    |

| CSEL Leading Time Before the<br>First SCL Edge | tL                                |                                                                                  |                       | 500 |     | ns    |

| CSEL Trailing Time After the Last SCL Edge     | t <sub>T</sub>                    |                                                                                  |                       | 500 |     | ns    |

| SDA, SCL External Load                         | CB                                | Total bus capacitance on one line                                                |                       |     | 20  | pF    |

Note 1: Specifications at  $T_A = -40^{\circ}$ C and  $T_A = +95^{\circ}$ C are guaranteed by design and characterization, .

**Note 2:** Guaranteed by design and characterization,  $T_A = -40^{\circ}C$  to  $+95^{\circ}C$ .

- **Note 3:** The data input transition time is controlled by 4th-order Bessel filter with f<sub>-3dB</sub> = 0.75 x 1.25GHz and f<sub>-3dB</sub> = 0.75 x 2.5GHz, respectively. The deterministic jitter caused by this filter is not included in the DJ. A 2<sup>23</sup> 1 PRBS equivalent pattern was used.

- Note 4: RJ was tested without input filter.

- Note 5: For all Rx LOS specifications LOS\_LOWBW = 1 for 1.25Gbps operation and LOS\_LOWBW = 0 for 2.5Gbps operation.

- **Note 6:** Measurement includes an input AC-coupling capacitor of 0.1µF. The signal at the RIN input is switched between two amplitudes: Signal\_ON and Signal\_OFF.

- 1) Receiver operates at sensitivity level plus 1dB power penalty

- a) Signal\_OFF = 0

- Signal\_ON = 10log(min\_assert\_level) + 8dB

- b) Signal\_ON = 10log(max\_deassert\_level) + 1dB

- Signal\_OFF = 0

- 2) Receiver operates at overload

- Signal\_OFF = 0

- Signal\_ON =  $1.2V_{P-P}$

- max\_deassert\_level and min\_assert\_level are measured for one SET\_LOS setting

- Note 7: Stability is defined [I<sub>MEASURED</sub>) (I<sub>REFERENCE</sub>)]/(I<sub>REFERENCE</sub>) over the listed current range temperature and supply variation. Reference current measured at V<sub>CC</sub> = 3.3V and T<sub>A</sub> = +25°C. Measured current is measured at V<sub>CC</sub> = 3.3V ±5% and T<sub>A</sub> = -40°C to +95°C.

- **Note 8:** K<sub>MD</sub> is the laser diode to monitor diode gain in A/W. SE is the laser's slope efficiency.

### **MAX3710**

### 125Mbps to 2.5Gbps, Integrated Limiting Amplifier/ Burst Mode Laser Driver with Dual-Loop Power Control

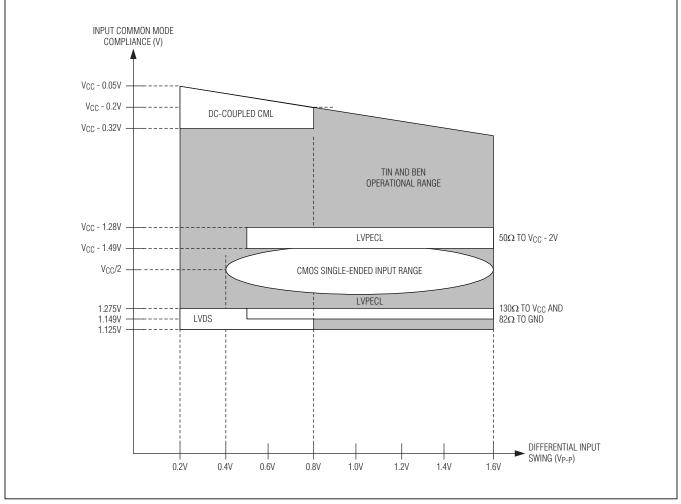

Figure 1. BEN/TIN Input Voltage Diagram

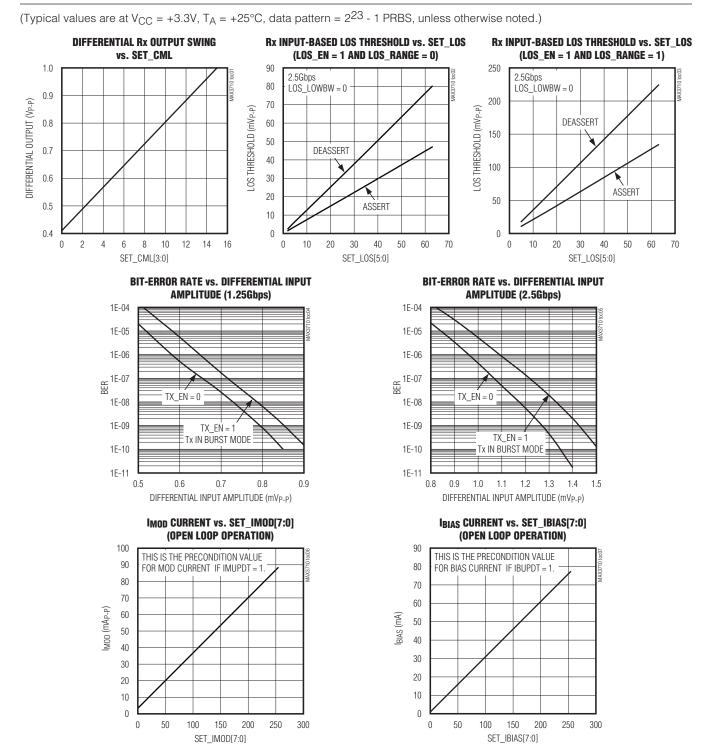

**Typical Operating Characteristics**

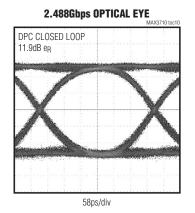

### **Typical Operating Characteristics (continued)**

(Typical values are at  $V_{CC}$  = +3.3V,  $T_A$  = +25°C, data pattern = 2<sup>23</sup> - 1 PRBS, unless otherwise noted.)

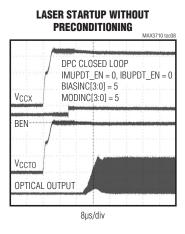

2µs/div

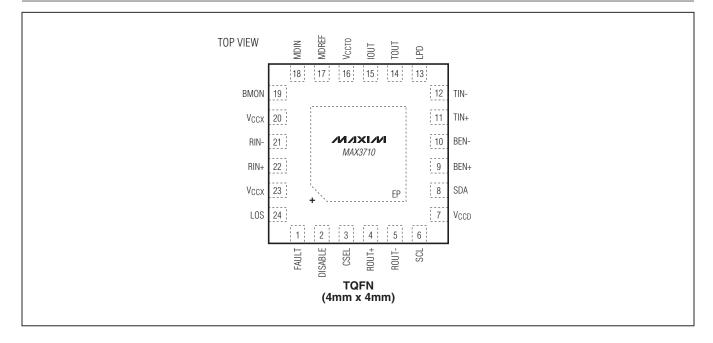

**Pin Configuration**

### **Pin Description**

| PIN | NAME    | OUTPUT FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | EQUIVALENT CIRCUIT  |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1   | FAULT   | Transmitter Fault, Open-Drain. Logic-high indicates a fault condition has been detected (FAULT_POL = 1). It remains high even after the fault condition has been removed. A logic-low occurs when the fault condition has been removed and the fault latch has been cleared by toggling the DISABLE signal, or by setting <u>MODECTRL</u> = 68h. FAULT should be pulled up to 3.3V supply through a 4.7k $\Omega$ to 10k $\Omega$ resistor. Note that pulling up the pin to a supply voltage above V <sub>CCX</sub> can turn on the ESD protection diode. | PROTECTION<br>FAULT |

| 2   | DISABLE | Transmitter Disable Input, TTL/CMOS. Set to logic-low for normal operation (DIS_POL = 1). Logic-high or open disables both the modulation current and the bias current. Internally pulled up by a $100k\Omega$ resistor to V <sub>CCX</sub> .                                                                                                                                                                                                                                                                                                             | DISABLE             |

| PIN  | NAME             | OUTPUT FUNCTION                                                                                                                                                                                                      | EQUIVALENT CIRCUIT                                                                 |

|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 3    | CSEL             | Chip-Select Input, CMOS. Setting CSEL to logic-high starts a cycle. Setting CSEL to logic-low ends the cycle and resets the control state machine. Internally pulled down by a $75k\Omega$ resistor to ground.       | CSEL                                                                               |

| 4, 5 | ROUT+,<br>ROUT-  | Differential Receiver Data Output, CML. This output has $50\Omega$ terminations to V <sub>CC</sub> . Polarity is set by the RX_POL bit.                                                                              | V <sub>CCX</sub><br>50Ω PROTECTION<br>FSD<br>PROTECTION<br>FOUT+<br>ROUT+<br>ROUT- |

| 6    | SCL              | Serial-Clock Input, CMOS. Internally pulled down by a 75k $\Omega$ resistor to ground.                                                                                                                               | SCL                                                                                |

| 7    | V <sub>CCD</sub> | Power Supply. Provides supply voltage to the digital block.                                                                                                                                                          | _                                                                                  |

| 8    | SDA              | Serial-Data Bidirectional Input, CMOS. Open-<br>drain output. This pin has a $75k\Omega$ internal pullup,<br>but it requires an external $4.7k\Omega$ to $10k\Omega$ pullup<br>to meet 3-wire timing specifications. | SDA                                                                                |

| PIN       | NAME          | OUTPUT FUNCTION                                                                                                                                                          | EQUIVALENT CIRCUIT                                                                                            |

|-----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 9, 10     | BEN+/<br>BEN- | Burst-Enable Input. This differential $13k\Omega$ input is compatible with LVDS, PECL, and CML input levels. The polarity is set by the BEN_POL bit.                     | BEN+                                                                                                          |

| 11,<br>12 | TIN+/TIN-     | Differential Transmitter Data Input. This differen-<br>tial 13kΩ input is compatible with LVDS, PECL,<br>and CML input levels. The polarity is set by the<br>TX_POL bit. | TIN-<br>$V_{CCX}$<br>$6.3k\Omega$<br>$6.3k\Omega$<br>$6.3k\Omega$<br>$210\Omega$<br>TIN-<br>ESD<br>PROTECTION |

| 13        | LPD           | Laser Power Detector Output. The polarity of the LPD signal is controlled by the LPD_POL bit. The output impedance is approximately $150\Omega$ .                        | PROTECTION<br>LPD                                                                                             |

| PIN       | NAME              | OUTPUT FUNCTION                                                                                                                                                                                                                                                                                    | EQUIVALENT CIRCUIT                                                                                           |

|-----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 14        | TOUT              | Noninverting Laser Diode Modulation and Bias<br>Current Output. Connect to the cathode of the<br>laser diode. A differential 1 at TIN± results in cur-<br>rent flow at the laser.                                                                                                                  | PROTECTION VCCTO<br>IOUT<br>TOUT                                                                             |

| 15        | IOUT              | Inverting Laser Diode Modulation and Bias<br>Current Output. Connect to the anode of the<br>laser diode.                                                                                                                                                                                           |                                                                                                              |

| 16        | V <sub>CCTO</sub> | Power-Supply Connection. Provides supply volt-<br>age to the transmitter output.                                                                                                                                                                                                                   | —                                                                                                            |

| 17        | MDREF             | Monitor Diode Reference. Connect this to a fil-<br>tered V <sub>CCTO</sub> .                                                                                                                                                                                                                       | MDREF                                                                                                        |

| 18        | MDIN              | Monitor Diode Input. Connect this pin to the<br>anode of the monitor diode. MDIN can be left<br>open for open-loop operation. Keep capacitance<br>minimized at this pin.                                                                                                                           |                                                                                                              |

| 19        | BMON              | Bias Current/Laser Power Monitor Output.<br>Current out of this pin develops a ground-refer-<br>enced voltage across external resistor(s) that is<br>proportional to the laser bias current or MDIN pin<br>current. The current sourced by this pin is typi-<br>cally 1/72 the laser bias current. | ESD<br>PROTECTION<br>ESD<br>PROTECTION<br>ESD<br>ESD<br>ESD<br>ESD<br>ESD<br>ESD<br>ESD<br>ESD<br>ESD<br>ESD |

| 20,<br>23 | V <sub>CCX</sub>  | Transceiver Power Supply. Provides supply volt-<br>age to the receiver and transmitter cores.                                                                                                                                                                                                      | _                                                                                                            |

| PIN       | NAME          | OUTPUT FUNCTION                                                                                                                                                                                                                                                                                                                                           | EQUIVALENT CIRCUIT |

|-----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 21,<br>22 | RIN-,<br>RIN+ | Differential Receiver Data Input. Contains 100Ω<br>differential termination on-chip. Connect these<br>inputs to the TIA outputs using 1µF coupling<br>capacitors.                                                                                                                                                                                         | RIN+               |

| 24        | LOS           | Receiver Loss-of-Signal (LOS) Output, Open Drain. This output goes to a logic-high when the level of the input signal drops below the <u>SET_LOS</u> register threshold. Polarity is set by LOS_POL. All LOS circuitry can be disabled by setting LOS_EN = 0. The LOS output is pulled up to host $V_{CC}$ with a 4.7k $\Omega$ to 10k $\Omega$ resistor. | PROTECTION         |

|           | EP            | Exposed Pad. Ground. This is the only electri-<br>cal connection to ground on the MAX3710<br>and must be soldered to circuit board ground<br>for proper thermal and electrical performance<br>(see the <i>Exposed-Pad Package and Thermal</i><br><i>Considerations</i> section).                                                                          |                    |

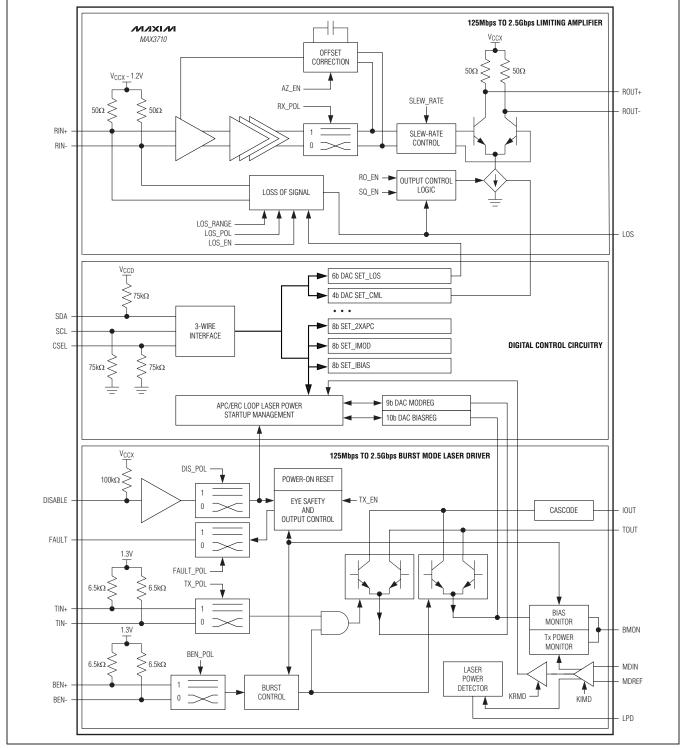

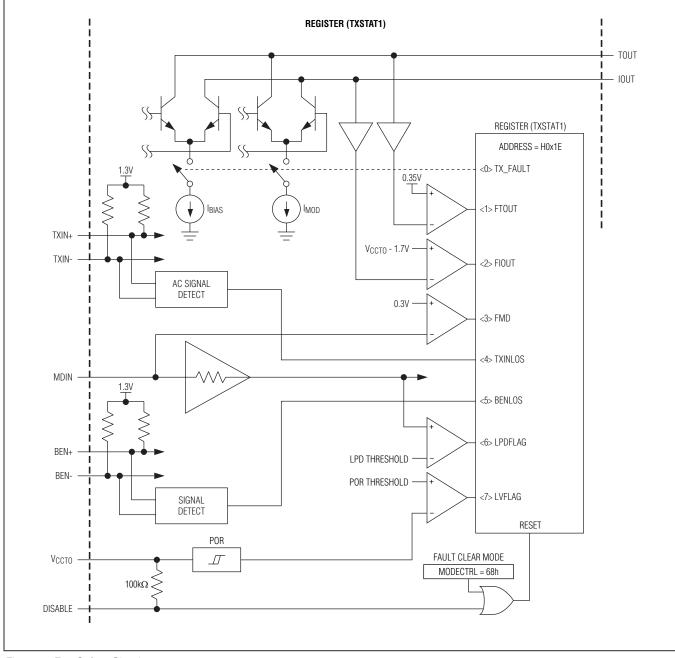

Figure 2. Functional Diagram

### **Detailed Description**

The MAX3710 combines a high-gain limiting amplifier with a burst-mode laser driver. The limiting amplifier includes offset cancellation and programmable signaldetect threshold. The laser driver includes average power and extinction ratio control, average or peak laser power measurement capability, overcurrent limiting, laser power detector, bias current/MD current monitor, and fault detection. A 3-wire serial control interface enables an external controller to set all parameters necessary for operation of the limiting amplifier and laser diode driver. The interface enables real-time laser bias and/or modulation current control and provides operation and status readouts.

The features and performance are specifically designed to be compatible with low-cost microcontrollers and provide complete EPON and GPON PMD functionality, including laser fault detection, diagnostics, and average power control with extinction ratio control. The MAX3710 includes all the logic required for laser protection, control loop operation, and monitor diode current measurement.

#### 1.25Mbps to 2.5Gbps Limiting Amplifier Block Description

Continuous Mode Limiter

The limiting amplifier consists of a multistage amplifier, offset-correction circuit, output buffer, and loss-of-signal/ signal-detect circuitry. Its low noise (1.3mV<sub>P-P</sub> typical sensitivity) and high gain can provide 0.3dB to 0.5dB of additional sensitivity in typical 2.5Gbps GPON applications. Programmable configuration options (LOS threshold, LOS polarity, CML output with adjustable level, slew rate, and output polarity) enhance layout flexibility and triplexer/ROSA compatibility.

#### High-Speed Input Signal Path

The inputs, RIN $\pm$ , have an internal 100 $\Omega$  differential termination and should be AC-coupled to the transimpedance amplifier.

#### **Offset Cancellation**

The limiting amplifier has approximately 68dB of gain, which makes it very susceptible to both DC offsets and pulse-width distortion in the signal from the transimpedance amplifier. A low-frequency feedback loop provides offset cancellation to compensate for these effects; the nominal small-signal low-frequency cutoff of the offset cancellation loop is 10kHz when 1  $\mu\text{F}$  AC-coupling capacitors are used.

#### Loss-of-Signal Circuitry (LOS)

This block detects amplitude of the incoming signal and compares it against a preset threshold, which is controlled by <u>SET\_LOS</u>[5:0]. The programming range of the LOS assert level is  $3.8mV_{P-P}$  to  $138mV_{P-P}$ .

Changing the LOS threshold during operation (i.e., without executing a reset) does not cause a glitch or incorrect LOS output. The detector has 2dB of hysteresis to control chatter at the LOS output. The LOS output polarity is controlled by the LOS\_POL bit. The entire LOS circuit block can be disabled by setting LOS\_EN = 0.

#### **Output Drivers**

The CML data outputs, ROUT±, are terminated with  $50\Omega$  to V<sub>CCX</sub>. The differential output level can be programmed through the <u>SET\_CML[3:0]</u> register between  $410mV_{P-P}$  and  $1000mV_{P-P}$ , and the output polarity can be inverted. Serial commands can also be used to manually disable the output (to its common-mode voltage, i.e., near zero differential voltage DC), or cause the limiting amp to automatically disable the output under an LOS condition (squelch through the SQ\_EN bit). The output slew rate can be optimized for either 2.5Gbps or low data-rate operation by setting the SLEW\_RATE bit.

#### 1.25Mbps to 2.5Gbps Laser Driver Block Description

The burst mode laser driver consists of TIN±/BEN± differential high-speed input buffers, TIN±/BEN± polarity switch buffers, DISABLE TTL/CMOS input buffer, combined laser modulator and bias generator, monitor diode current input buffer with calibration features, digital laser power detector (LPD) with CMOS output buffer, analog bias current monitor, analog transmit power monitor, APC and ERC loop circuitry, eye-safety monitoring, and FAULT output buffer.

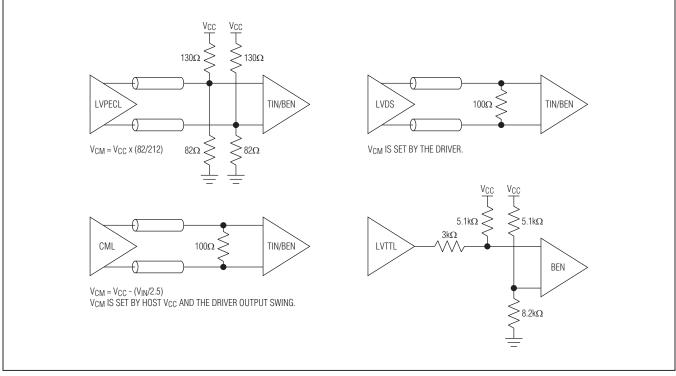

#### Differential High-Speed Input Buffers

The high-speed laser driver data inputs, BEN<sub>±</sub> and TIN<sub>±</sub>, are compatible with LVDS, LVPECL, and CML outputs. BEN can be driven single-ended (Figure 3). For burst mode operation TIN<sub>±</sub> should be DC-coupled with external differential termination of 100 $\Omega$  placed close to the input pins. The BEN<sub>±</sub> and TIN<sub>±</sub> inputs can also be DC-coupled to LVDS outputs using a 100 $\Omega$  differential termination. The polarity of TIN<sub>±</sub> and BEN<sub>±</sub> can be inverted by the TX\_POL and BEN\_POL bits, respectively.

### **MAX3710**

### 125Mbps to 2.5Gbps, Integrated Limiting Amplifier/ Burst Mode Laser Driver with Dual-Loop Power Control

Figure 3. Interfacing to the MAX3710 TIN± and BEN± Inputs

#### Laser Modulator and Bias Generator

The laser modulator provides DC coupled current into the cathode of the laser diode at the TOUT pin. The modulation current amplitude is set by <u>MODREG[8:0]</u>. The modulation current DAC guarantees modulation amplitudes up to 85mA.

The laser bias current output stage is similar to the modulation current output stage because the burst mode operation requires fast switching on/off times. The amplitude of the laser bias current is controlled by BIASREG[9:0]. The laser bias current DAC guarantees values up to 70mA.

During burst-on the modulation and bias currents are summed at the TOUT pin. During burst-off the bias and modulation currents are switched to the IOUT pin. Note that TOUT and IOUT are not differential in the general sense; TOUT must be connected to the laser diode cathode and the cascoded IOUT pin must be connected to the laser diode anode.

#### Monitor Diode Current Input Buffer

The input stage covers a large input signal range by having adjustable gain settings. The KIMD[1:0] bits set the current gain. This is followed by an adjustable transimpedance amplifier (TIA). The TIA gain settings are programmed by the KRMD[2:0] bits. The input has high bandwidth, allowing the MAX3710 to monitor not only average laser power, but also extinction ratio. In addition, laser power detection (LPD) for rogue ONUs is made possible by the MDIN input.

MDIN current is mirrored at the BMON output and selected by setting MDMON\_EN = 1 and MON\_SEL = 1. In this mode, the current sourced by BMON is scaled by  $K_{IMD}$ , where the value  $K_{IMD}$  is set by the KIMD[1:0] bits. The high bandwidth of the MDIN–BMON path enables tuning of the laser-to-monitor diode external components to minimize crosstalk and to optimize filtering on the MDIN signal.

#### **Digital Laser Power Detector**

This detector compares the monitor diode current value with a preset threshold and generates a CMOS logic level output at the LPD pin. The threshold level scales with gain settings at MDIN through KIMD[1:0].

There are two basic modes for reporting the results of LPD, which performs light detection during the off\_state: Off\_state is defined as a disable of the device by DISABLE, TX\_EN, MOD\_EN, BIAS\_EN, BEN, or a fault.

Mode 1, LPD\_MODE = 1:

LPD reports any light burst (when BEN = 1, the LPD output is high).

Mode 2,  $LPD_MODE = 0$ :

LPD reports light bursts during a laser off state only (when BEN = 1, the LPD output is low).

Polarity of the LPD output is selectable by setting the LPD\_POL bit. The mode of operation is controlled by the LPD\_MODE bit.

Use the LPD\_TH[2:0] bits to set the LPD threshold in steps of  $12.5\mu$ A/K<sub>IMD</sub>, where the value K<sub>IMD</sub> is set by the KIMD[1:0] bits. If the monitor diode exhibits a "slow-tail" behavior where the monitor diode current slowly decays after light disappears, the LPD threshold may need to be adjusted high enough so the LPD output does not produce an unintentional pulse directly after BEN transitions low.

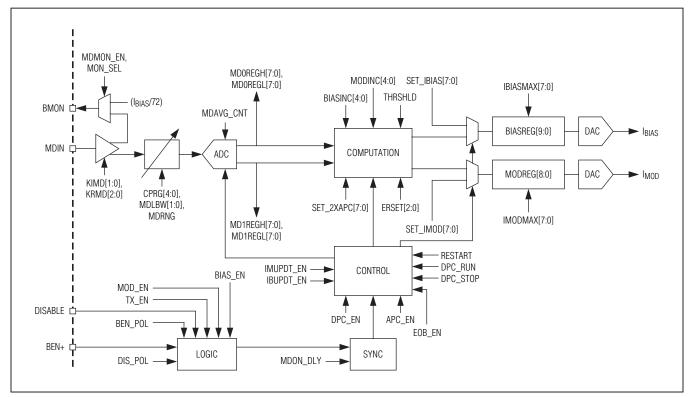

#### Average Power and Extinction Ratio Control Circuitry The MAX3710 includes full closed-loop control of laser average power and extinction ratio. Figure 4 shows the dual power control, or DPC, loop. Operation is as follows:

The monitor diode (MD) is connected to the MDIN pin, and the MD current is amplified by a gain set by the KIMD[1:0] and KRMD[2:0] bits.

The output of the MDIN input buffer is sent through a programmable filter, controlled by the CPRG[4:0], MDLBW[1:0], and MDRNG bits.

The filter output is fed to a 10MS/s analog-to-digital converter (ADC), where the peak values of both the high current and the low current (proportional to the high power and low power of the laser) are determined and converted to 16-bit digital words, MDOREGH[7:0] and MDOREGL[7:0], and <u>MD1REGH</u>[7:0] and <u>MD1REGL</u>[7:0]. The values are MD0[15:8] = MD0REGH[7:0], MD0[7:0] = MD0REGL[7:0], MD1[15:8] = MD1REGH[7:0], MD1[7:0] = MD1REGL[7:0]. The number of averages used to generate MD1[15:0] and MD0[15:0] is determined by MDAVG\_CNT.

To monitor average transmitter power, use the following equation:

$$P_{AVG} = 0.00292 \times \frac{\frac{MD0[15:0]}{8} + MD1[15:0]}{512 \times KIMD \times KRMD \times KRMD \times KRMD}$$

where  $K_{\mbox{\scriptsize MD}}$  is the laser diode to monitor diode gain in A/W.

For example, if  $K_{MD} = 0.1$ , KIMD[1:0] = 00(gain = 1), KRMD[2:0] = 000 (gain =  $2800\Omega$ ), MD0[15:0] = 35750d, and MD1[15:0] = 44680d, the calculated  $P_{AVG} = 1mW$ .

From the ADC to the TOUT/IOUT outputs, operation is dictated by the state of the BEN± pins. The ADC only samples during the burst-on time and is frozen during burst-off. Therefore, MD1 and MD0 values are held static during burst-off. The TX\_EN bit must also be high for the ADC to sample.

The delay from the rising edge of BEN to the first sample is selected by the MDON\_DLY[1:0] bits in 100ns steps. For MDON\_DLY[1:0] = 00, the minimum burst-on time for DPC updating is approximately 60ns (typ), and it can be adjusted up to 360ns by setting MDON\_DLY[1:0] = 11.

Returning to the main forward path of the DPC, MD1[15:0] and MD0[15:0] are used to compute the average power and extinction ratio at the MDIN input in the "COMPUTATION" block (Figure 4). These values are compared with the target values of average power (<u>SET\_2XAPC</u>[7:0]) and extinction ratio (ERSET[3:0] bits). If the error magnitude is greater than the value set by THRSHLD, then the output registers <u>BIASREG</u>[9:0] and <u>MODREG</u>[8:0] are updated with the error value. The update value is limited by the <u>BIASINC</u>[3:0] and <u>MODINC</u>[3:0] registers.

The <u>IBIASMAX[7:0]</u> and <u>IMODMAX[7:0]</u> values are used to limit <u>BIASREG[9:2]</u> and <u>MODREG[8:1]</u>. Note only the upper 8 bits of the output current registers are compared.

### **MAX3710**

### 125Mbps to 2.5Gbps, Integrated Limiting Amplifier/ Burst Mode Laser Driver with Dual-Loop Power Control

The EOB\_EN bit conditions updating of the output registers.

If EOB\_EN = 1, the output registers are only updated once immediately following the falling edge of BEN. However, the DPC must acquire the entire set of averages, N, set by MDAVG\_CNT, before changing <u>BIASREG[9:0]</u> and <u>MODREG[8:0]</u>. The averaging process can stretch over multiple bursts and freezes between bursts. Once the required number of averages has been satisfied, the ADC outputs freeze until BEN falls and <u>BIASREG[9:0]</u> and <u>MODREG[8:0]</u> can be updated.

If EOB\_EN = 0, the output registers are updated continuously while BEN = 1.

The "CONTROL" block (Figure 4) controls the updating and startup behavior of the entire DPC.

The bits APC\_EN and DPC\_EN control the operating mode of the DPC:

**Full DPC Mode.** DPC\_EN = 1, APC\_EN = X: BIASREG[9:0] and MODREG[8:0] are controlled based on the SET\_2XAPC[7:0] register and ERSET[3:0] targets.

**APC Only Mode.** DPC\_EN = 0, APC\_EN = 1: The <u>BIASREG[9:0]</u> register is controlled based on the <u>SET\_2XAPC[7:0]</u> target and <u>MODREG[8:0]</u> is controlled directly through <u>SET\_IMOD[7:0]</u>. <u>MODINC[4:0]</u> is used to adjust the lower bits of <u>MODREG[8:0]</u> using two's complement to increase or decrease its value.