# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#

# +3.3V/+5V, 8-Channel, Cascadable Relay Drivers with Serial/Parallel Interface

### **General Description**

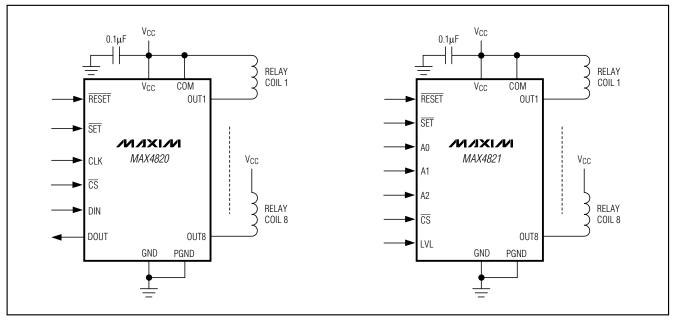

The MAX4820/MAX4821 8-channel relay drivers offer built-in kickback protection and drive +3.3V/+5V nonlatching or dual-coil-latching relays. These devices are especially useful when driving +3V relays. Each independent open-drain output features a  $2\Omega$  on-resistance and is guaranteed to sink 70mA (min) of load current. Both devices consume less than 50µA (max) quiescent current and have 1µA output off-leakage current.

The MAX4820 features an SPI™-/QSPI™-/MICROWIRE™compatible serial interface. Input data is shifted into an 8bit shift register and latched to the outputs when CS transitions from low to high. Each data bit in the shift register corresponds to a specific output, allowing independent control of all outputs.

The MAX4821 features a 4-bit (A0, A1, A2, LVL) parallel-input interface. The first three bits (A0, A1, A2) determine the output address, and the fourth bit (LVL) determines whether the selected output is switched on or off. Data is latched to the outputs when  $\overline{\text{CS}}$  transitions from low to high.

Both devices feature separate set and reset functions that allow the user to turn on or turn off all outputs simultaneously with a single control line. Built-in hysteresis (Schmidt trigger) on all digital inputs allows this device to be used with slow rising and falling signals, such as those from optocouplers or RC power-up initialization circuits. The MAX4820/MAX4821 are available in 20-pin TSSOP and space-saving 20-pin thin QFN packages.

Applications

Central Office ATE DSL, ADSL Line Cards Industrial Equipment

E1/T1 Redundancy

Pin Configurations continued at end of data sheet. Typical Application Circuits and Functional Diagrams appear at end of data sheet.

SPI and QSPI are trademarks of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp.

###

**\_Features**

- ♦ 8 Independent Output Channels

- Built-In Inductive Kickback Protection

- Drive +3V and +5V Relays

- Guaranteed 70mA (min) Coil Drive Current

- ♦ SET Function to Turn On All Outputs Simultaneously

- ♦ RESET Function to Turn Off All Outputs Simultaneously

- SPI-/QSPI-/MICROWIRE-Compatible Serial Interface (MAX4820)

- Serial Digital Output for Daisy Chaining (MAX4820)

- Parallel Interface (MAX4821)

- Low 50µA (max) Quiescent Supply Current

- Space-Saving 20-Pin Thin QFN Package

### **\_Ordering Information**

| ACKAGE |

|--------|

| QFN-EP |

| OP     |

| QFN-EP |

| OP     |

|        |

\*For maximum heat dissipation, packages have an exposed pad (EP) on the bottom. Solder exposed pad to GND.

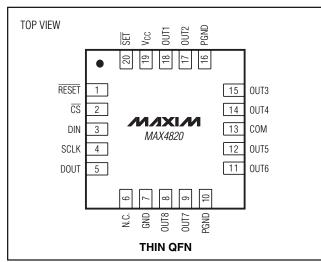

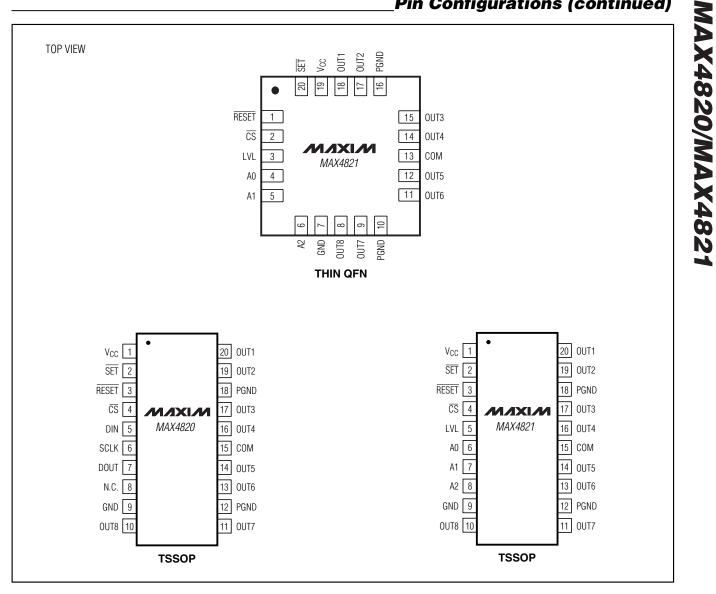

### **Pin Configurations**

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

(All voltages referenced to GND.)

| V <sub>CC</sub> , COM            | 0.3V to +6.0V                    |

|----------------------------------|----------------------------------|

| OUT                              |                                  |

| CS, SCLK, DIN, SET, RESET, A0,   | A1, A2, LVL0.3V to +6.0V         |

| DOUT                             | 0.3V to (V <sub>CC</sub> + 0.3V) |

| Continuous OUT_ Current (all out | tputs turned on)                 |

| Continuous OUT_Current (single   |                                  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )<br>20-Lead Thin QFN |                |

|---------------------------------------------------------------------------|----------------|

| (derate 16.9mW/°C above +70°C)                                            | 1350mW         |

| θJA                                                                       |                |

| 20-Pin TSSOP                                                              |                |

| (derate 21.7mW/°C above +70°C)                                            | 1739mW         |

| θ」Α                                                                       | 46°C/W         |

| Operating Temperature Range                                               | 40°C to +85°C  |

| Junction Temperature                                                      | +150°C         |

| Storage Temperature Range                                                 | 65°C to +150°C |

| Soldering Temperature (10s)                                               |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

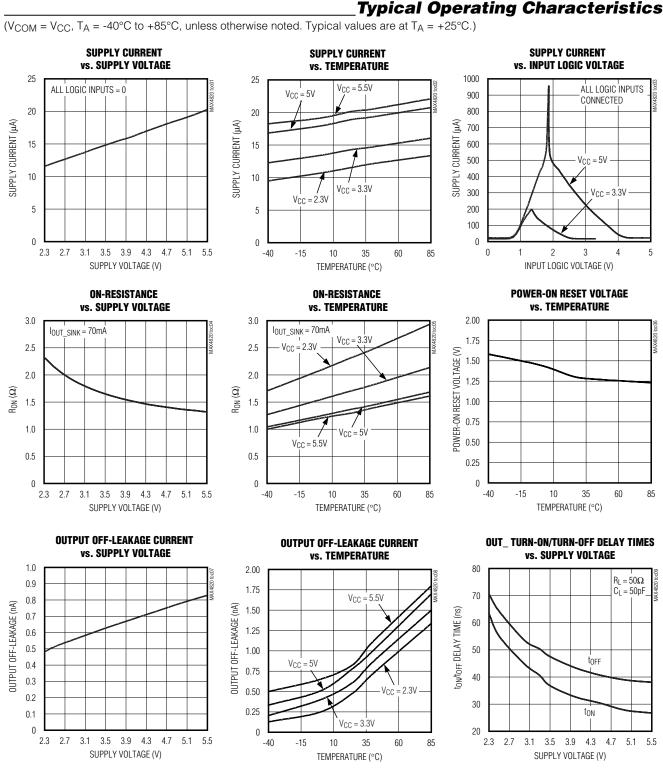

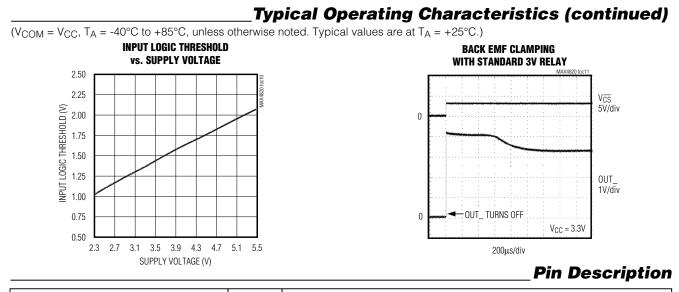

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3V \text{ to } +5.5V, V_{COM} = V_{CC}, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                      | SYMBOL            | CONDITIONS                        |                 | MIN                  | ТҮР  | МАХ  | UNITS |

|--------------------------------|-------------------|-----------------------------------|-----------------|----------------------|------|------|-------|

| Operating Voltage              | Vcc               |                                   |                 | 2.3                  |      | 5.5  | V     |

|                                |                   | I <sub>OUT_</sub> = 0,            | $V_{CC} = 3.6V$ |                      | 15   | 50   |       |

| Quiescent Current              | lq                | logic inputs = 0 or $V_{CC}$      | $V_{CC} = 5.5V$ |                      | 20   | 70   | μA    |

| Thermal Shutdown               |                   |                                   |                 |                      | 160  |      | °C    |

| Power-On Reset                 |                   |                                   |                 | 0.8                  | 1.5  | 2.2  | V     |

| Power-On Reset Hysteresis      |                   |                                   |                 |                      | 140  |      | mV    |

| DIGITAL INPUTS (SCLK, DIN, CS  | , LVL, A0, A      | 1, A2, RESET, SET)                |                 |                      |      |      |       |

| Input Logia High Voltage       | Mus               | $V_{CC} = 3.3V$                   |                 | 2.0                  |      |      | V     |

| Input Logic High Voltage       | VIH               | $V_{CC} = 5V$                     |                 | 2.4                  |      |      | v     |

| Input Logic Low Voltage        | Mu                | $V_{CC} = 3.3V$                   |                 |                      |      | 0.6  | V     |

| Input Logic Low Voltage        | VIL               | $V_{CC} = 5V$                     |                 |                      |      | 0.8  | v     |

| Input Logic Hysteresis         | V <sub>HYST</sub> |                                   |                 |                      | 150  |      | mV    |

| Input Leakage Currents         | ILEAK             | Input voltages = 0 or 5.5V        |                 | -1.0                 | 0.01 | +1.0 | μA    |

| CIN Input Capacitance          | CIN               |                                   |                 |                      | 5    |      | pF    |

| DIGITAL OUTPUT (DOUT)          |                   |                                   |                 |                      |      |      |       |

| DOUT Low Voltage               | VOL               | I <sub>SINK</sub> = 6mA           |                 |                      |      | 0.4  | V     |

| DOUT High Voltage              | VOH               | I <sub>SOURCE</sub> = 0.5mA       |                 | V <sub>CC</sub> - 0. | 5    |      | V     |

| RELAY OUTPUT DRIVERS (OUT      | 1–OUT8)           |                                   |                 |                      |      |      |       |

| OUT_ Drive Current             |                   | $V_{CC} = 2.7 V$                  |                 | 70                   |      |      | ~^^   |

| OUT_Drive Current              |                   | $V_{CC} = 4.5V$                   |                 | 70                   |      |      | mA    |

| OUT_ On-Resistance             | Ron               | V <sub>CC</sub> = 2.7V            |                 |                      | 2    | 6    | Ω     |

| OUT_ Voltage                   | Vout_             | $V_{CC} = 3.0V, I_{OUT} = 70r$    | nA              |                      |      | 0.4  | V     |

| IOUT Off-Leakage Current       | ILEAK             | $V_{OUT_} = V_{CC}$ , all outputs | s off           | -1                   |      | +1   | μA    |

| Kickback Diode Forward Voltage | VFORW             | I <sub>OUT</sub> = 150mA (Note 2) |                 |                      |      | 1.5  | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3V \text{ to } +5.5V, V_{COM} = V_{CC}, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                | SYMBOL          | CONDITIONS                                                                                                          | MIN | ТҮР | MAX | UNITS |

|------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| SPI TIMING (MAX4821)                     |                 | •                                                                                                                   |     |     |     |       |

| Turn-On Time (OUT_)                      | ton             | From rising edge of $\overline{CS}$ , $R_L = 50\Omega$ , $C_L = 50pF$                                               |     |     | 1.0 | μs    |

| Turn-Off Time (OUT_)                     | tOFF            | From rising edge of $\overline{\text{CS}}$ , $\text{R}_{\text{L}} = 50\Omega$ , $\text{C}_{\text{L}} = 50\text{pF}$ |     |     | 1.0 | μs    |

| SCLK Frequency                           | <b>f</b> SCLK   |                                                                                                                     | 0   |     | 2.1 | MHz   |

| Cycle Time                               | tCH + tCL       |                                                                                                                     | 480 |     |     | ns    |

| CS Fall to SCLK Rise Setup               | tcss            |                                                                                                                     | 240 |     |     | ns    |

| CS Rise to SCLK Hold                     | tCSH            |                                                                                                                     | 240 |     |     | ns    |

| SCLK High Time                           | tсн             |                                                                                                                     | 190 |     |     | ns    |

| SCLK Low Time                            | tCL             |                                                                                                                     | 190 |     |     | ns    |

| Data Setup Time                          | tDS             |                                                                                                                     | 100 |     |     | ns    |

| Data Hold Time                           | tDH             |                                                                                                                     | 0   |     |     | ns    |

| SCLK Fall to DOUT Valid                  | t <sub>DO</sub> | 50% of SCLK to 10% of DOUT, $C_L = 50pF$                                                                            |     | 85  | 120 | ns    |

| Rise Time (DIN, SCLK, CS, SET, RESET)    | tSCR            | 20% of V <sub>CC</sub> to 70% of V <sub>CC</sub> , C <sub>L</sub> = 50pF                                            |     |     | 2   | μs    |

| Fall Time (DIN, SCLK, CS,<br>RESET, SET) | tSCF            | 20% of V <sub>CC</sub> to 70% of V <sub>CC</sub> , C <sub>L</sub> = 50pF                                            |     |     | 2   | μs    |

| RESET Min Pulse Width                    | t <sub>RW</sub> |                                                                                                                     | 70  |     |     | ns    |

| SET Min Pulse Width                      | tsw             |                                                                                                                     | 70  |     |     | ns    |

| PARALLEL TIMING (MAX4820)                |                 | ·                                                                                                                   |     |     |     |       |

| Turn-On Time                             | t <sub>ON</sub> | From rising edge of $\overline{CS}$ , $R_L = 50\Omega$ , $C_L = 50pF$                                               |     |     | 1   | μs    |

| Turn-Off Time                            | toff            | From rising edge of $\overline{CS}$ , $R_L = 50\Omega$ , $C_L = 50pF$                                               |     |     | 1   | μs    |

| LVL Setup Time                           | tLS             |                                                                                                                     | 100 |     |     | ns    |

| LVL Hold Time                            | tLH             |                                                                                                                     | 0   |     |     | ns    |

| Address to CS Setup Time                 | tah             |                                                                                                                     | 100 |     |     | ns    |

| Address to CS Hold Time                  | tas             |                                                                                                                     | 0   |     |     | ns    |

| Rise Time (A2, A1, A0, LVL)              | tSCR            | 20% of V <sub>CC</sub> to 70% of V <sub>CC</sub> , $C_L = 50 pF$                                                    |     |     | 2   | μs    |

| Fall Time (A2, A1, A0, LVL)              | tSCF            | 20% of V <sub>CC</sub> to 70% of V <sub>CC</sub> , $C_L = 50 pF$                                                    |     |     | 2   | μs    |

| RESET Pulse Width                        | t <sub>RW</sub> |                                                                                                                     | 70  |     |     | ns    |

| SET Pulse Width                          | tsw             |                                                                                                                     | 70  |     |     | ns    |

Note 1: Specifications at -40°C are guaranteed by design and not production tested.

**Note 2:** After relay turn-off, inductive kickback may momentarily cause the voltage at OUT\_ to exceed V<sub>COM</sub>. This is considered part of normal operation and will not damage the device.

M/IXI/N

4

MAX4820/MAX4821

| PIN         |        | PIN         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                    |

|-------------|--------|-------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX         | 4820   | MAX4821     |        | NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FUNCTION                                                                                                                                                                                                                                                                                                           |

| THIN<br>QFN | TSSOP  | THIN<br>QFN | TSSOP  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | T ONOTION                                                                                                                                                                                                                                                                                                          |

| 1           | 3      | 1           | 3      | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reset Input. Drive $\overline{\text{RESET}}$ low to clear all latches and registers (all outputs are turned off). $\overline{\text{RESET}}$ overrides all other inputs. If $\overline{\text{RESET}}$ and $\overline{\text{SET}}$ are pulled low at the same time, then $\overline{\text{RESET}}$ takes precedence. |

| 2           | 4      | 2           | 4      | $\overline{CS}$ Chip-Select Input.<br><b>MAX4820:</b> Drive $\overline{CS}$ low to select the device. When $\overline{CS}$ is low, data at DIN is<br>clocked into the 8-bit shift register on SCLK's rising edge. Drive $\overline{CS}$ from low<br>to high to latch the data to the registers and activate the appropriate relays.<br><b>MAX4821:</b> Drive $\overline{CS}$ low to select the device and set level on LVL. Drive $\overline{CS}$<br>from low to high to latch the address and level data to the output. |                                                                                                                                                                                                                                                                                                                    |

| 3           | 5      |             | _      | DIN Serial Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                    |

| 4           | 6      | _           | —      | SCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Serial Clock Input                                                                                                                                                                                                                                                                                                 |

| 5           | 7      | _           |        | DOUT Serial Data Output. DOUT is the output of the 8-bit shift register. This output can be used to daisy chain multiple MAX4820s. The data at DOUT appears synchronous to SCLK's falling edge.                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                    |

| 6           | 8      | _           | _      | N.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | No Connection                                                                                                                                                                                                                                                                                                      |

| 7           | 9      | 7           | 9      | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Ground                                                                                                                                                                                                                                                                                                             |

| 8           | 10     | 8           | 10     | OUT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Open-Drain Output 8. Connect OUT8 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                                                                                                                  |

| 9           | 11     | 9           | 11     | OUT7 Open-Drain Output 7. Connect OUT7 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                    |

| 10, 16      | 12, 18 | 10, 16      | 12, 18 | PGND Power Ground. PGND is a return for the output sinks. Connect PGND pins together and to GND.                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                    |

| 11          | 13     | 11          | 13     | OUT6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Open-Drain Output 6. Connect OUT6 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                                                                                                                  |

MAX4820/MAX4821

###

### **Pin Description (continued)**

| PIN         |       | PIN         |       |                                                                                                                                                                                                                                               |                                                                                                                                                                                             |

|-------------|-------|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| МАХ         | 4820  | МАХ         | 4821  | NAME                                                                                                                                                                                                                                          | FUNCTION                                                                                                                                                                                    |

| THIN<br>QFN | TSSOP | THIN<br>QFN | TSSOP | NAME                                                                                                                                                                                                                                          | FUNCTION                                                                                                                                                                                    |

| 12          | 14    | 12          | 14    | OUT5                                                                                                                                                                                                                                          | Open-Drain Output 5. Connect OUT5 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                           |

| 13          | 15    | 13          | 15    | $\begin{array}{c} \mbox{COM} & \mbox{Common Free-Wheeling Diodes. Connect COM to V_{CC}. COM can also be connected to a separate supply that is higher than V_{CC}. In that case, bypa V_{CC} to GND with a 0.1 \mu F capacitor. \end{array}$ |                                                                                                                                                                                             |

| 14          | 16    | 14          | 16    | OUT4                                                                                                                                                                                                                                          | Open-Drain Output 4. Connect OUT4 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                           |

| 15          | 17    | 15          | 17    | OUT3                                                                                                                                                                                                                                          | Open-Drain Output 3. Connect OUT3 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                           |

| 17          | 19    | 17          | 19    | OUT2                                                                                                                                                                                                                                          | Open-Drain Output 2. Connect OUT2 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                           |

| 18          | 20    | 18          | 20    | OUT1                                                                                                                                                                                                                                          | Open-Drain Output 1. Connect OUT1 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                           |

| 19          | 1     | 19          | 1     | Vcc                                                                                                                                                                                                                                           | Input Supply Voltage. Bypass $V_{CC}$ to GND with a 0.1µF capacitor.                                                                                                                        |

| 20          | 2     | 20          | 2     | SET                                                                                                                                                                                                                                           | Set Input. Drive SET low to set all latches and registers high (all outputs are turned on). SET overrides all parallel and serial control inputs. RESET overrides SET under all conditions. |

| _           | _     | 3           | 5     | Level Input. LVL determines whether the selected address is switched on c<br>LVL off. A logic high on LVL switches on the addressed output. A logic low on<br>LVL switches off the addressed output.                                          |                                                                                                                                                                                             |

|             |       | 4           | 6     | A0 Digital Address "0" Input. (See Table 2 for address mapping.)                                                                                                                                                                              |                                                                                                                                                                                             |

| _           | —     | 5           | 7     | A1 Digital Address "1" Input. (See Table 2 for address mapping.)                                                                                                                                                                              |                                                                                                                                                                                             |

| —           | —     | 6           | 8     | A2 Digital Address "2" Input. (See Table 2 for address mapping.)                                                                                                                                                                              |                                                                                                                                                                                             |

| _           | —     | —           | —     | EP                                                                                                                                                                                                                                            | Exposed Pad. Solder exposed pad to GND.                                                                                                                                                     |

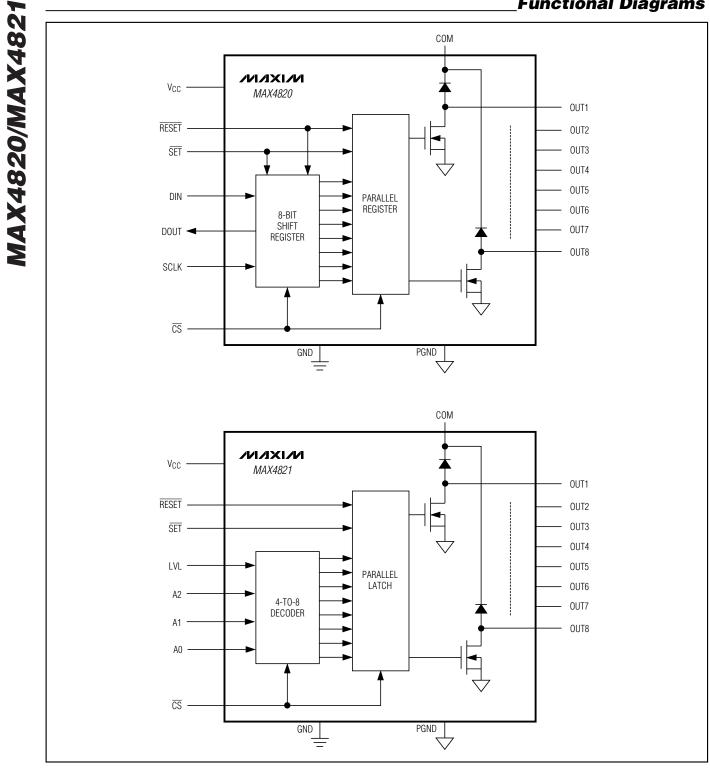

### **Detailed Description**

The MAX4820/MAX4821 8-channel relay drivers offer built-in kickback protection and drive +3.3V/+5V nonlatching or dual-coil-latching relays. These devices are especially useful when driving +3V relays. Each independent open-drain output features a  $2\Omega$  on-resistance and is guaranteed to sink 70mA (min) load current. Both devices consume less than 50µA (max) quiescent current and feature 1µA (min) output off-leakage current.

The MAX4820 features an SPI/QSPI/MICROWIRE-compatible serial interface. Input data is shifted into an 8-bit shift register and latched to the outputs when  $\overline{CS}$  transitions from low to high. Each data bit in the shift register corresponds to a specific output, allowing independent control of all outputs. The MAX4821 features a 4-bit (A0, A1, A2, LVL) parallel input interface. The three bits (A0, A1, A2) determine the output address, and LVL determines whether the selected output is switched on or off. Data is latched to the outputs when  $\overline{\text{CS}}$  transitions from low to high.

Both devices feature separate set and reset functions that allow the user to turn on or turn off all outputs simultaneously with a single control line. Built-in hysteresis (Schmidt trigger) on all digital inputs allows this device to be used with slow rising and falling signals, such as those from optocouplers or RC power-up initialization circuits. The MAX4820/MAX4821 are available in 20-pin TSSOP and space-saving 20-pin thin QFN packages.

///XI//

6

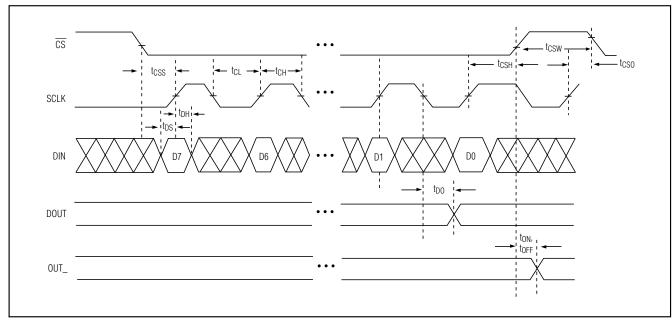

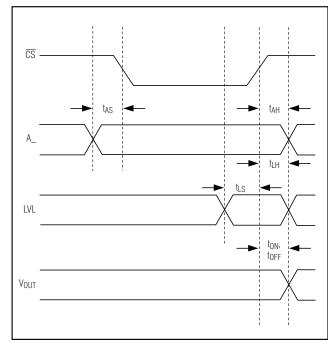

Figure 1. 3-Wire Serial-Interface Timing Diagram (MAX4820 only)

#### Table 1. Serial Input Address Map (MAX4820 Only)

| DIN  | D0   | D1   | D2   | D3   | D4   | D5   | D6   | D7   |

|------|------|------|------|------|------|------|------|------|

| OUT_ | OUT1 | OUT2 | OUT3 | OUT4 | OUT5 | OUT6 | OUT7 | OUT8 |

#### **Digital Interface** Serial Interface (MAX4820)

The serial interface consists of an 8-bit shift register and parallel latch controlled by SCLK and  $\overline{CS}$ . The input to the shift register is an 8-bit word. Each data bit controls one of the eight outputs, with the most significant bit (D7) corresponding to OUT8 and the least significant bit (D0) corresponding to OUT1 (see Table 1). When  $\overline{CS}$  is low (device is selected), data at DIN is clocked into the shift register synchronously with SCLK's rising edge. Driving  $\overline{CS}$  from low to high latches the data in the shift register to the parallel latch.

DOUT is the output of the shift register. Data appears on DOUT synchronously with SCLK's falling edge and is identical to the data at DIN delayed by eight clock cycles. When shifting the input data, D7 is the first bit in and out of the shift register.

While  $\overline{CS}$  is low, the switches always remain in their previous state. Drive  $\overline{CS}$  high after 8 bits of data have been shifted in to update the output state and inhibit further data from entering the shift register. When  $\overline{CS}$  is high, transitions at DIN and SCLK have no effect on the output, and the first input bit (D7) is present at DOUT.

If the number of data bits entered while  $\overline{CS}$  is low is greater or less than 8, the shift register contains only the last 8 data bits, regardless of when they were entered.

The 3-wire serial interface is compatible with SPI, QSPI, and MICROWIRE standards. The latch that drives the analog switch is updated on the rising edge of  $\overline{CS}$ , regardless of SCLK's state.

#### Parallel Interface (MAX4821)

The parallel interface consists of three address bits (A0, A1, A2) and one level selector bit (LVL). The address bits determine which output is updated, and the level bit determines whether the addressed output is switched on (LVL = high) or off (LVL = low). When  $\overline{CS}$  is high, the address and level bits have no effect on the state of the outputs. Driving  $\overline{CS}$  from low to high latches the address and level data to the parallel register and updates the state of the outputs. Address data entered after  $\overline{CS}$  is pulled low is not reflected in the state of the outputs following the next low-to-high transition on  $\overline{CS}$  (Figure 2).

Figure 2. Parallel Interface Timing Diagram (MAX4821 only)

#### **SET/RESET** Functions

The MAX4820/MAX4821 feature set and reset inputs that allow the user to simultaneously turn all outputs on or off using a single control line. Drive SET low to set all latches and registers to 1 and turn all outputs on. SET overrides all serial/parallel control inputs. Drive RESET low to clear all latches and registers and turn all outputs off. RESET overrides all other inputs, including SET.

# Table 2. Parallel Interface Address Map(MAX4821 Only)

| A2   | A1   | A0   | OUTPUT |

|------|------|------|--------|

| Low  | Low  | Low  | OUT1   |

| Low  | Low  | High | OUT2   |

| Low  | High | Low  | OUT3   |

| Low  | High | High | OUT4   |

| High | Low  | Low  | OUT5   |

| High | Low  | High | OUT6   |

| High | High | Low  | OUT7   |

| High | High | High | OUT8   |

#### Applications Information

#### **Daisy Chaining**

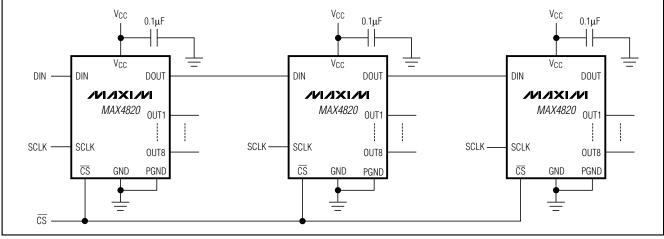

The MAX4820 features a digital output, DOUT, that provides a simple way to daisy chain multiple devices. This feature allows the user to drive large banks of relays using only a single serial interface. To daisy chain multiple devices, connect all  $\overline{\text{CS}}$  pins together, and connect the DOUT of one device to the DIN of another device (see Figure 3). During operation, a stream of serial data is shifted through all the MAX4820s in series. When  $\overline{\text{CS}}$  goes high, all outputs update simultaneously.

The MAX4820 can also be used in a slave configuration that allows the user to address individual devices. Connect all the DIN pins together, and use the  $\overline{CS}$  input to address one device at a time. Drive  $\overline{CS}$  low to select a slave and input the data into the shift register. Drive  $\overline{CS}$  high to latch the data and turn on the appropriate outputs. Typically, in this configuration only one slave is addressed at a time.

Figure 3. Daisy-Chain Configuration

MAX4820/MAX4821

#### Inductive Kickback Protection

The MAX4820/MAX4821 feature built-in inductive kickback protection to reduce the voltage spike on OUT\_ generated by a relay's coil inductance when the output is suddenly switched off. Internal diodes connected from each output to COM allow the inductor current to flow back to the supply. Connect the common cathode (COM) of the internal protection diodes to  $V_{\mbox{CC}}.$

COM also can be connected to a higher voltage than V<sub>CC</sub> (+6V max) for faster kickback recovery. In this configuration, bypass COM to PGND with a  $0.1\mu$ F capacitor.

| COMPANY                 | PHONE        | WEBSITE               |

|-------------------------|--------------|-----------------------|

| Aromat Corp.            | 310-524-9862 | www.aromat.com        |

| CP Clare Corp.          | 978-524-6700 | www.crouzet.com       |

| Coto Techonology        | 401-943-2686 | www.cotorelay.com     |

| Deustch Relays,<br>Inc. | 516-499-6000 | www.deutschrelays.com |

| Fujitsu<br>Takamisawa   | 408-745-4900 | www.fujitsufta.com    |

| Hella KG Hueck          | 734-414-0970 | www.hella.com         |

| COMPANY                                         | PHONE        | WEBSITE                |

|-------------------------------------------------|--------------|------------------------|

| NEC Electronics,<br>Inc.                        | 800-366-9782 | www.nec-global.com     |

| Omron<br>Electronics, Inc.                      | 847-843-7900 | www.oeiweb.omron.com   |

| Rockwell/Allen-<br>Bradley                      | 414-382-2000 | www.ab.com             |

| Siemens<br>Electromechanical<br>Component, Inc. | 770-371-3000 | www.sec.siemens.com    |

| Teledyne Relays                                 | 213-777-0077 | www.teledynerelays.com |

### **Relay Manufacturers**

M/X/M

**Functional Diagrams**

### Pin Configurations (continued)

**Chip Information**

**TRANSISTOR COUNT: 1301** PROCESS: BiCMOS

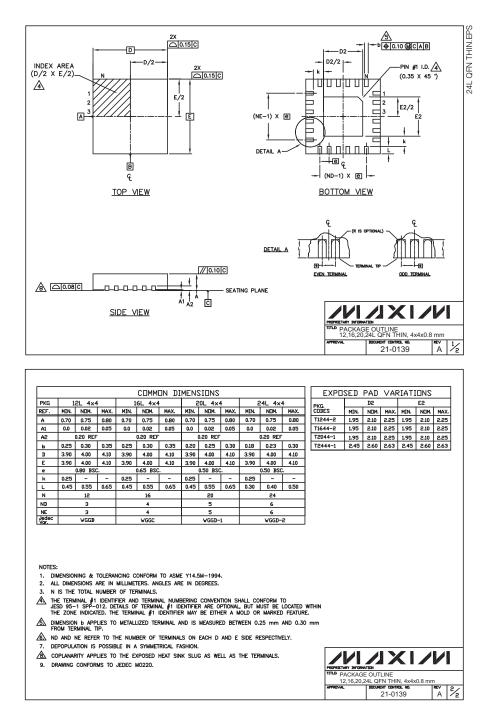

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>www.maxim-ic.com/packages</u>.)

M/IXI/M

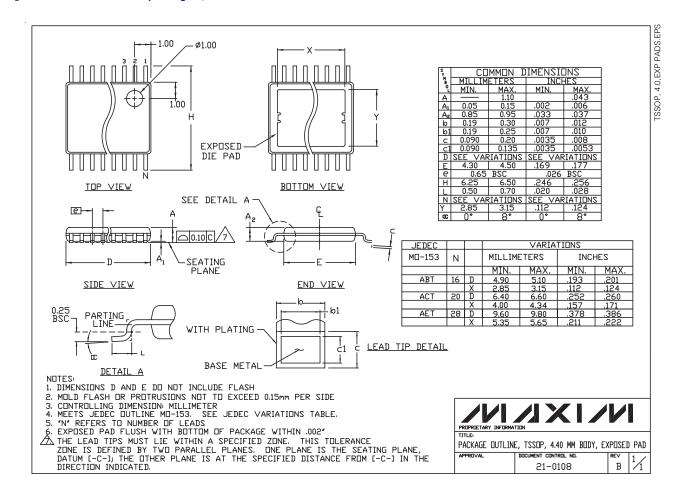

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>www.maxim-ic.com/packages</u>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2003 Maxim Integrated Products

Printed USA

**MAXIM** is a registered trademark of Maxim Integrated Products.

**MAX4820/MAX4821**

13