Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **General Description**

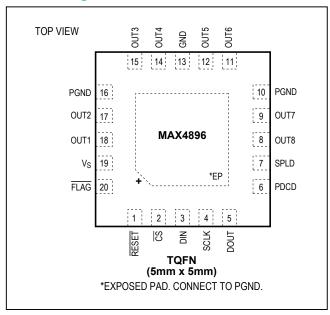

The MAX4896 8-channel relay and load driver is designed for medium voltage applications up to 50V. This device is offered in a 20-pin, 5mm x 5mm TQFN package, resulting in substantial board space savings.

The MAX4896 8-channel relay driver offers built-in inductive kickback protection, drive for latching/nonlatching or dual-coil relays, and open-load and short-circuit fault detection. The MAX4896 also protects against overcurrent conditions. Each independent open-drain output features a  $3\Omega$  (typ) on-resistance, and is guaranteed to sink 200mA of load current ( $V_S \ge 4.5V$ ).

A built-in overvoltage protection clamp handles kickback-voltage transients, which are common when driving inductive loads. Thermal-shutdown circuitry shuts off all outputs (OUT\_) when the junction temperature exceeds +160°C. The MAX4896 employs a reset input that allows the user to turn off all outputs simultaneously with a single control line.

The MAX4896 includes a 10MHz SPI™-/QSPI™-/MICROWIRE™-compatible serial interface. The serial interface is compatible with TTL-/CMOS-logic voltage levels and operates with a single +2.7V to +5.5V supply. In addition, the SPI output data can be used for diagnostics purposes including open-load and shortcircuit fault detection.

The MAX4896 is offered in the extended (-40°C to +85°C) and automotive (-40°C to +125°C) operating temperature ranges.

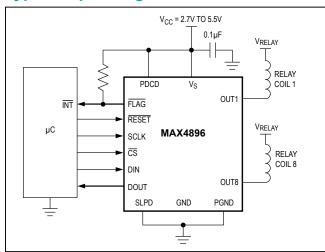

## **Typical Operating Circuit**

Pin Configuration appears at end of data sheet.

#### **Features**

- Supports Up to 50V Continuous Drain-to-Source Voltage

- Guaranteed Drive Current:

- V<sub>S</sub> ≥ 4.5V

200mA (All Channels On)

410mA (Individual Channels)

- V<sub>S</sub> ≤ 3.6V 100mA

- Built-In Output Clamp Protects Against Inductive Kickback

- +2.7V to +5.5V Logic Supply Voltage

- RESET Input Turns Off All Outputs Simultaneously

- Built-in Power-On Reset

- Automotive Temperature Range (-40°C to +125°C)

- SPI-/QSPI-/MICROWIRE-Compatible Serial Interface

- Serial Digital Output for Daisy Chaining and Diagnostics

- FLAG Output for µP Interrupt

- Open-Load and Short-Circuit Detection and Protection

- Thermal Shutdown

- Low 100µA (max) Quiescent Supply Current

- Space-Saving, 5mm x 5mm, 20-Pin TQFN Package

ATE

### **Applications**

- Industrial Equipment

- White Goods

- Power-Grid Monitoring and Protection Equipment

## **Ordering Information**

| PART        | TEMP RANGE      | PIN-PACKAGE                |

|-------------|-----------------|----------------------------|

| MAX4896ETP+ | -40°C to +85°C  | 20 TQFN-EP*<br>(5mm x 5mm) |

| MAX4896ATP+ | -40°C to +125°C | 20 TQFN-EP*<br>(5mm x 5mm) |

<sup>\*</sup>EP = Exposed pad.

SPI and QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

<sup>+</sup>Denotes lead(Pb)-free/RoHS-compliant package.

### **Absolute Maximum Ratings**

| (All voltages referenced to GND.)                        | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|----------------------------------------------------------|-------------------------------------------------------|

| V <sub>S</sub> 0.3V to +7.0V                             | 20-Pin TQFN (derate 21.3mW/°C above +70°C)1702mW      |

| OUT(-0.3V to +50V)                                       | Maximum Output Clamp Energy (E <sub>OUT</sub> )       |

| Continuous OUT_ Voltage+50V                              | Operating Temperature Range40°C to +125°C             |

| CS, SCLK, DIN, RESET, SPLD, PDCD0.3V to +7.0V            | Junction Temperature+150°C                            |

| DOUT0.3V to (V <sub>S</sub> + 0.3V)                      | Storage Temperature Range65°C to +150°C               |

| PGND to GND(-0.3V to +0.3V)                              | Lead Temperature (soldering, 10s)+300°C               |

| Continuous OUT_ Current, T <sub>A</sub> = +25°C (Note 1) | Soldering Temperature (reflow)+260°C                  |

| All Outputs On210mA                                      |                                                       |

| Single Output On420mA                                    |                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Thermal Characteristics (Note 2)**

20 TOFN-FP

Junction-to-Ambient Thermal Resistance (θ<sub>JC</sub>).......2°C/W Junction-to-Case Thermal Resistance (θ<sub>JC</sub>).........2°C/W

- **Note 1:** Maximum continuous current at a given temperature must be calculated such that the maximum continuous power dissipation for the package is not exceeded.

- **Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_S = +2.7 V \text{ to } +5.5 V, T_A = -40 ^{\circ} C \text{ to } +125 ^{\circ} C, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25 ^{\circ} C.$ ) (Note 3)

| PARAMETER                         | SYMBOL            | CONDITIONS                                                        |                       | MIN  | TYP  | MAX | UNITS |

|-----------------------------------|-------------------|-------------------------------------------------------------------|-----------------------|------|------|-----|-------|

| Operating Voltage                 | VS                |                                                                   |                       | 2.7  |      | 5.5 | V     |

| Ouissant Current                  | 1                 | I <sub>OUT</sub> = 0, logic inputs = 0 or                         | V <sub>S</sub> = 3.6V |      | 5    | 70  |       |

| Quiescent Current                 | l <sub>CC</sub>   | $V_S$ , RESET = low                                               | V <sub>S</sub> = 5V   |      | 10   | 100 | μA    |

| Dynamic Average Supply<br>Current | IS                | $f_{SCLK} = 10MHz, f_{DIN} = 0.5 x f_{COUT} = 50pF, V_{S} = 5.5V$ | CLK,                  |      |      | 6   | mA    |

| Thermal Shutdown                  | T <sub>SHD</sub>  |                                                                   |                       |      | +160 |     | °C    |

| Thermal-Shutdown Hysteresis       | T <sub>SHDH</sub> |                                                                   |                       |      | 20   |     | °C    |

| Power-On Reset                    | V <sub>RST</sub>  | V <sub>S</sub> falling                                            | 1.8                   | 2.05 | 2.3  | V   |       |

| Power-On-Reset Hysteresis         | V <sub>RSTH</sub> |                                                                   |                       |      | 140  |     | mV    |

| DIGITAL INPUTS (SCLK, DIN,        | CS, RESET, P      | DCD, SPLD)                                                        |                       |      |      |     |       |

| Input Logio High Voltago          | V                 | V <sub>S</sub> = 2.7V to 3.6V                                     |                       | 2.0  |      |     | V     |

| Input Logic-High Voltage          | V <sub>IH</sub>   | V <sub>S</sub> = 4.5V to 5.5V                                     |                       | 2.4  |      |     | \ \ \ |

| Imput Logic Low Voltage           | V                 | V <sub>S</sub> = 2.7V to 3.6V                                     |                       |      |      | 0.6 | V     |

| Input Logic-Low Voltage           | V <sub>IL</sub>   | V <sub>S</sub> = 4.5V to 5.5V                                     |                       |      |      | 0.8 | \ \ \ |

| Input Logic Hysteresis            | V <sub>HYST</sub> |                                                                   |                       | 230  |      | mV  |       |

| Input Leakage Currents            | I <sub>LEAK</sub> | Input voltages = 0 or +5.5V                                       | -1                    |      | +1   | μA  |       |

| Input Capacitance                 | C <sub>IN</sub>   |                                                                   |                       |      | 10   |     | pF    |

## **Electrical Characteristics (continued)**

$(V_S = +2.7 V \text{ to } +5.5 V, T_A = -40 ^{\circ} \text{C to } +125 ^{\circ} \text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25 ^{\circ} \text{C.})$  (Note 3)

| PARAMETER                                            | SYMBOL                | CONI                                                                                             | MIN                        | TYP                  | MAX | UNITS |      |  |

|------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------|----------------------------|----------------------|-----|-------|------|--|

| RELAY OUTPUT DRIVERS (OU                             | JT1–OUT8)             |                                                                                                  |                            | '                    |     |       |      |  |

|                                                      |                       |                                                                                                  | T <sub>J</sub> = +25°C     |                      | 5   | 6     |      |  |

|                                                      |                       | $I_{OUT} = 50$ mA,<br>$V_{S} = 2.7$ V                                                            | T <sub>J</sub> = +125°C    |                      |     | 11    |      |  |

| OUT ON Desistance                                    |                       | VS - 2.7 V                                                                                       | T <sub>J</sub> = +150°C    |                      | 1   | 12    | Ω    |  |

| OUT_ ON Resistance                                   | R <sub>ON</sub>       |                                                                                                  | T <sub>J</sub> = +25°C     |                      | 3   | 4     |      |  |

|                                                      |                       | $I_{OUT} = 100 \text{mA},$<br>$V_{S} = 4.5 \text{V}$                                             | T <sub>J</sub> = +125°C    |                      |     | 7     |      |  |

|                                                      |                       | VS - 4.5V                                                                                        | T <sub>J</sub> = +150°C    |                      |     | 8     |      |  |

| I <sub>OUT</sub> Off-Leakage Current                 | ILEAK                 | PDCD = high or RESE                                                                              | ET = low, all outputs Off  | -1                   |     | +1    | μA   |  |

| OUT Clamping Voltage                                 | V <sub>CLAMP</sub>    | (Note 4)                                                                                         |                            | 50                   |     | 75    | V    |  |

| OUT Current-Limit Threshold                          | I <sub>LIM</sub>      | V <sub>S</sub> ≥ 4.5V                                                                            |                            | 400                  |     | 960   | mA   |  |

| OUT Capacitance                                      |                       | V <sub>OUT</sub> = 16V, f = 1MHz                                                                 | Z                          |                      | 30  |       | pF   |  |

| DIAGNOSTIC                                           |                       |                                                                                                  |                            | •                    |     |       | •    |  |

| Open-Load Detection Voltage<br>Threshold             | V <sub>DS(OL)</sub>   | OUT_falling                                                                                      |                            | 0.75                 | 1   | 1.15  | V    |  |

| Open-Load Detection-Voltage-<br>Threshold Hysteresis | V <sub>DS(OLH)</sub>  |                                                                                                  |                            |                      | 40  |       | mV   |  |

| OUT_ Pulldown Current                                | I <sub>PD(OL)</sub>   | PDCD = low                                                                                       |                            | 150                  | 300 | 500   | μA   |  |

| Fault Delay/Filtering Time                           | t <sub>D(FAULT)</sub> | From rising edge at C diagnostic data                                                            | S at 50% to valid          | 30                   | 90  | 280   | μs   |  |

| DIGITAL OUTPUT (DOUT, FLA                            | <del>G</del> )        |                                                                                                  |                            | ,                    |     | -     |      |  |

| DOLLT Lave Vellage                                   | .,,                   | 2.7V ≤ V <sub>S</sub> ≤ 3.6V, I <sub>SINK</sub> = 0.3mA                                          |                            |                      |     | 0.4   |      |  |

| DOUT Low Voltage                                     | V <sub>OL</sub>       | 4.5V ≤ V <sub>S</sub> ≤ 5.5V, I <sub>SIN</sub>                                                   | IK = 0.5mA                 |                      |     | 0.4   | V    |  |

| DOLLT His boy Malla and                              |                       | 2.7V ≤ V <sub>S</sub> ≤ 3.6V, I <sub>SOURCE</sub> = 0.25mA                                       |                            | V <sub>S</sub> - 0.5 |     |       | .,   |  |

| DOUT High Voltage                                    | V <sub>OH</sub>       | 4.5V ≤ V <sub>S</sub> ≤ 5.5V, I <sub>SO</sub>                                                    | URCE = 0.4mA               | V <sub>S</sub> - 0.5 |     | -     | V    |  |

| FLAG Low Voltage                                     |                       | I <sub>SINK</sub> = 0.5mA                                                                        |                            |                      |     | 0.4   | V    |  |

| FLAG Off-Leakage Current                             |                       | 4.5V ≤ V <sub>S</sub> ≤ 5.5V, V <sub>FL</sub>                                                    | <del>AG</del> = 5.5V       | -1                   |     | +1    | μA   |  |

| TIMING                                               |                       |                                                                                                  |                            |                      |     |       |      |  |

| Turn On Time (OUT.)                                  |                       | From rising edge of $\overline{C}$<br>$V_{OUT}$ = 90%VP, VP :<br>$C_L$ = 50pF, 2.7V $\leq$ $V_S$ | = 15V, $R_L = 300\Omega$ , |                      |     | 20    |      |  |

| Turn-On Time (OUT_)                                  | t <sub>ON</sub>       | From rising edge of $\overline{C}$<br>$V_{OUT}$ = 90%VP, VP :<br>$C_L$ = 50pF, 4.5V $\leq$ $V_S$ | =16V, $R_L$ = 150Ω,        |                      |     | 10    | - μs |  |

|                                                      | 4-                    | From rising edge of $\overline{C}$<br>$V_{OUT}$ = 10%VP, VP = $C_L$ = 50pF, 2.7V $\leq V_S$      | = 15V, $R_L = 300\Omega$ , |                      |     | 15    | 1:0  |  |

| Turn-Off Time (OUT_)                                 | t <sub>OFF</sub>      | From rising edge of $\overline{C}$<br>$V_{OUT}$ = 90%VP, VP :<br>$C_L$ = 50pF, 4.5V < $V_S$      | $= 16V, R_L = 150Ω,$       |                      |     | 10    | - μs |  |

## **Electrical Characteristics (continued)**

$(V_S = +2.7 V \text{ to } +5.5 V, T_A = -40 ^{\circ} \text{C to } +125 ^{\circ} \text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25 ^{\circ} \text{C.})$  (Note 3)

| PARAMETER                               | SYMBOL                            | CONDIT                                                          | IONS                                                    | MIN | TYP | MAX | UNITS |

|-----------------------------------------|-----------------------------------|-----------------------------------------------------------------|---------------------------------------------------------|-----|-----|-----|-------|

|                                         |                                   | T - 105°C                                                       | $2.7V \le V_{S} < 3.6V$                                 | 0   |     | 6   |       |

| COLIV Francisco                         | £                                 | T <sub>A</sub> = +85°C                                          | $4.5V \le V_{\hat{S}} \le 5.5V$                         |     |     | 11  | ]     |

| SCLK Frequency                          | fsclk                             | T - 1425°C                                                      | $2.7V \le V_{S} \le 3.6V$                               | 0   |     | 5   | MHz   |

|                                         |                                   | T <sub>A</sub> = +125°C                                         | $4.5 \text{V} \le \text{V}_{\text{S}} \le 5.5 \text{V}$ |     |     | 10  |       |

| Cycle Time                              | tt-t                              | $2.7V \le V_{S} \le 3.6V$                                       |                                                         | 200 |     |     | ne    |

| Cycle Time                              | t <sub>CH</sub> + t <sub>CL</sub> | $4.5 \text{V} \le \text{V}_{\text{S}} \le 5.5 \text{V}$         |                                                         | 100 |     |     | ns    |

| CS Fall-to-SCLK Rise Setup              | <b>t</b>                          | $2.7V \le V_{S} \le 3.6V$                                       |                                                         | 100 |     |     | ne    |

| CS Fall-10-SCLN Rise Setup              | tcss                              | $4.5 \text{V} \le \text{V}_{\text{S}} \le 5.5 \text{V}$         |                                                         | 50  |     |     | ns    |

| CS Rise-to-SCLK Hold                    |                                   | $2.7V \le V_{\text{S}} \le 3.6V$                                |                                                         | 100 |     |     | 200   |

| CS RISE-10-SCLN HOID                    | tcsH                              | 4.5V ≤ V <sub>S</sub> ≤ 5.5V                                    |                                                         | 50  |     |     | ns    |

| 0011/11/11/17                           |                                   | $2.7V \le V_{\text{S}} \le 3.6V$                                |                                                         | 80  |     |     |       |

| SCLK High Time                          | t <sub>CH</sub>                   | 4.5V ≤ V <sub>S</sub> ≤ 5.5V                                    |                                                         | 40  |     |     | ns    |

| SCLK Low Time                           | 4                                 | $2.7V \le V_{S} \le 3.6V$                                       |                                                         | 80  |     |     | ns    |

| SCLK LOW TIME                           | t <sub>CL</sub>                   | $4.5 \text{V} \le \text{V}_{\text{S}} \le 5.5 \text{V}$         |                                                         | 40  |     |     | 113   |

| Data Setup Time                         | <b>4</b>                          | $2.7V \le V_{S} \le 3.6V$                                       |                                                         | 40  |     |     | ne    |

| Data Setup Time                         | t <sub>DS</sub>                   | $4.5V \le V_{\hat{S}} \le 5.5V$                                 |                                                         | 20  |     |     | ns    |

| Data Hold Time                          | 4                                 | $2.7V \le V_{S} \le 3.6V$                                       |                                                         | 5   |     |     |       |

| Data Hold Tillle                        | t <sub>DH</sub>                   | $4.5 \text{V} \leq \text{V}_{\text{S}} \leq 5.5 \text{V}$       |                                                         | 0   |     |     | ns    |

| SCLK Fall-to-DOUT Valid                 | <b>t</b>                          | 50% of SCLK to 20% of $V_S$ falling edge, $C_1 = 50pF$ , 50% at | 2.7V ≤ V <sub>S</sub> ≤ 3.6V                            |     |     | 70  | - ns  |

| SCEN Fail-to-DOOT Valid                 | tDO                               | SCLK to 80% of VS rising edge                                   | 4.5V ≤ V <sub>S</sub> ≤ 5.5V                            |     |     | 30  | 115   |

| Rise Time (DIN, SCLK, $\overline{CS}$ , |                                   | 20% of V <sub>S</sub> to 70% of                                 | 2.7V ≤ V <sub>S</sub> ≤ 3.6V                            |     |     | 2   |       |

| RESET)                                  | t <sub>SCR</sub>                  | V <sub>S</sub> , C <sub>L</sub> = 50pF (Note 5)                 | 4.5V ≤ V <sub>S</sub> ≤ 5.5V                            |     |     | 2   | μs    |

| Fall Time (DIN, SCLK, CS,               | to                                | 20% of V <sub>S</sub> to 70% of                                 | $2.7V \le V_{S} \le 3.6V$                               |     |     | 2   |       |

| RESET)                                  | tscf                              | $V_S$ , $C_L = 50pF$ (Note 5)                                   | 4.5V ≤ V <sub>S</sub> ≤ 5.5V                            |     |     | 2   | - µs  |

| RESET Min Pulse Width                   | t <sub>RW</sub>                   |                                                                 |                                                         | 70  |     |     | ns    |

**Note 3:** Specifications at -40°C are guaranteed by design and not production tested.

**Note 4:** The output stages are compliant with the transient immunity requirements, as specified in ISO 7637 Part 3 with test pulses 1, 2, 3a, and 3b.

Note 5: Guaranteed by design.

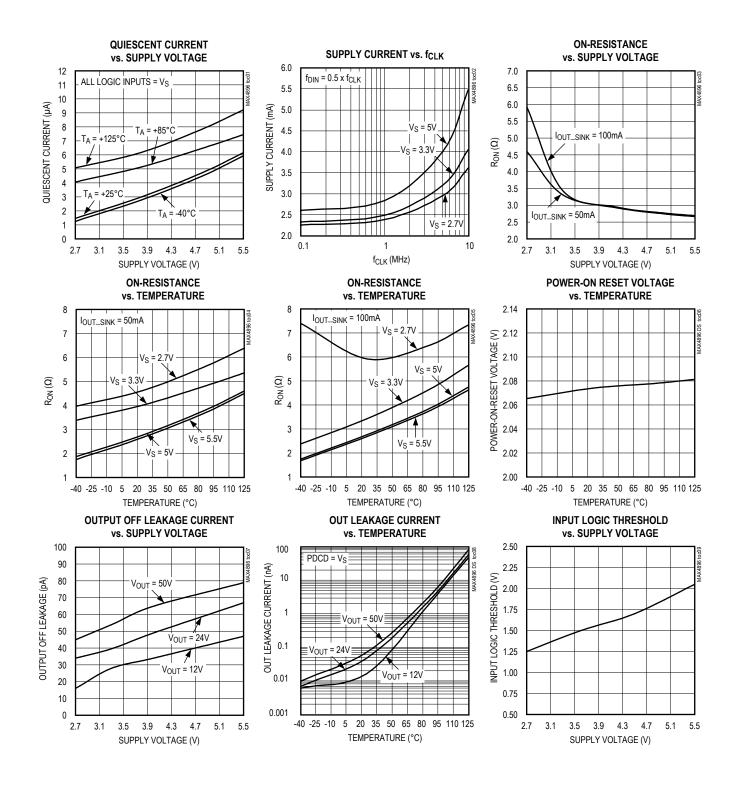

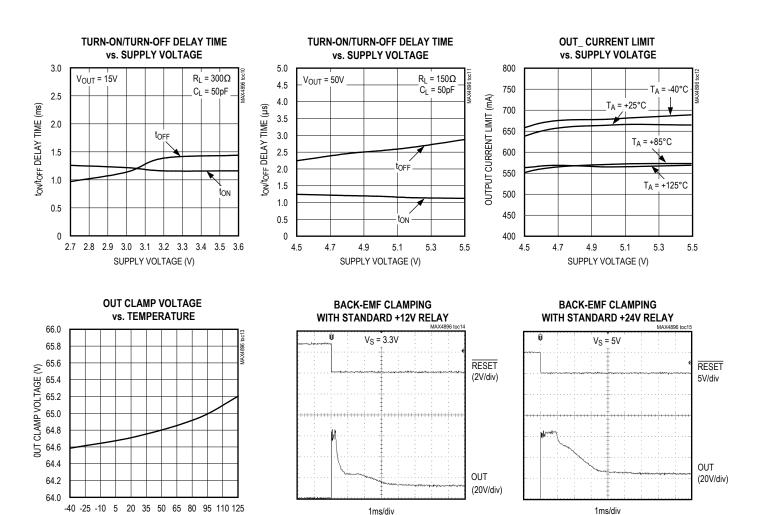

## **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

TEMPERATURE (°C)

## **Pin Description**

| PIN    | NAME      | FUNCTION                                                                                                                                                                                                                                                                  |

|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | RESET     | Reset Input. Drive RESET low to clear all latches and registers (all outputs are turned off). All OUT pulldown currents are disabled when RESET = low.                                                                                                                    |

| 2      | <u>cs</u> | Chip Select Input. Drive $\overline{CS}$ low to select the device. When $\overline{CS}$ is low, data at DIN is clocked into the 8-bit shift register on SCLK's rising edge. Drive $\overline{CS}$ from low to high to latch the data to the registers.                    |

| 3      | DIN       | Serial Data Input                                                                                                                                                                                                                                                         |

| 4      | SCLK      | Serial Clock Input                                                                                                                                                                                                                                                        |

| 5      | DOUT      | Serial Data Output. DOUT is the output of the 8-bit shift register. This output can be used to daisy chain multiple MAX4896s. The data at DOUT appears synchronous to SCLK's falling edge.                                                                                |

| 6      | PDCD      | Pulldown Current Disable. Drive PDCD high to disable OUT's pulldown current source. Drive PDCD low to enable OUT_ pulldown current source. PDCD must be low to detect an open-load fault.                                                                                 |

| 7      | SPLD      | Short-Protection Latch-Off Disable Input. Drive SPLD high to disable the built-in short-circuit protection latch-off feature. When SPLD is low, an overloaded channel is turned off immediately. See the <i>Output Short-Circuit/Current-Limiting Protection</i> section. |

| 8      | OUT8      | Open-Drain Output 8. Connect OUT8 to the low side of a relay coil. OUT8 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                                 |

| 9      | OUT9      | Open-Drain Output 7. Connect OUT7 to the low side of a relay coil. OUT7 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                                 |

| 10, 16 | PGND      | Power Ground. PGND is the ground return path for the output sinks. Connect PGND pins together and to GND.                                                                                                                                                                 |

| 11     | OUT6      | Open-Drain Output 6. Connect OUT6 to the low side of a relay coil. OUT6 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                                 |

| 12     | OUT5      | Open-Drain Output 5. Connect OUT5 to the low side of a relay coil. OUT5 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                                 |

| 13     | GND       | Ground                                                                                                                                                                                                                                                                    |

| 14     | OUT4      | Open-Drain Output 4. Connect OUT4 to the low side of a relay coil. OUT4 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                                 |

| 15     | OUT3      | Open-Drain Output 3. Connect OUT3 to the low side of a relay coil. OUT3 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                                 |

| 17     | OUT2      | Open-Drain Output 2. Connect OUT2 to the low side of a relay coil. OUT2 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                                 |

| 18     | OUT1      | Open-Drain Output 1. Connect OUT1 to the low side of a relay coil. OUT1 is pulled to PGND when activated and is otherwise high impedance.                                                                                                                                 |

| 19     | Vs        | Input Supply Voltage. Bypass V <sub>S</sub> to GND with a 0.1µF capacitor.                                                                                                                                                                                                |

| 20     | FLAG      | Open-Drain Fault Output. FLAG asserts low when a fault occurs at OUT1–OUT8.                                                                                                                                                                                               |

| _      | EP        | Exposed Paddle. Internally connected to GND. Connect to a large PCB ground plane to improve thermal dissipation. Enhances thermal conductivity; not intended as an electrical connection point.                                                                           |

#### **Detail Description**

The MAX4896 is an 8-channel relay and load driver for medium voltage applications up to 50V. The MAX4896 features built-in inductive kickback protection, drive for latching/nonlatching, or dual-coil relays and an internal register for detecting open-load and short-circuit faults. Each independent open-drain output features a 3 $\Omega$  onresistance and is guaranteed to sink 400mA at  $V_S \geq 4.5V$ , and 100mA at  $V_S \leq 3.6V$ .

The MAX4896 also incorporates a logic input (PDCD) that allows the device to continue operating when an overcurrent condition lasts longer than the 280µs (max) fault delay time. A built-in overvoltage protection clamp handles kickback voltage transients, which are common when driving inductive loads. Thermal-shutdown circuitry shuts off all outputs (OUT\_) when the junction temperature exceeds +160°C.

The MAX4896 employs a reset input that allows the user to turn off all outputs simultaneously with a single control line.

The MAX4896 includes a 10MHz SPI-/QSPI-/MICROWIRE compatible serial interface. The serial interface is compatible with TTL-/CMOS-logic voltage levels and operates with a single +2.7V to +5.5V supply.

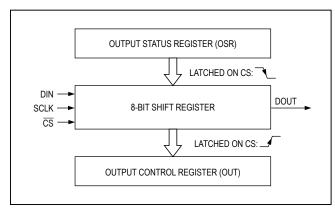

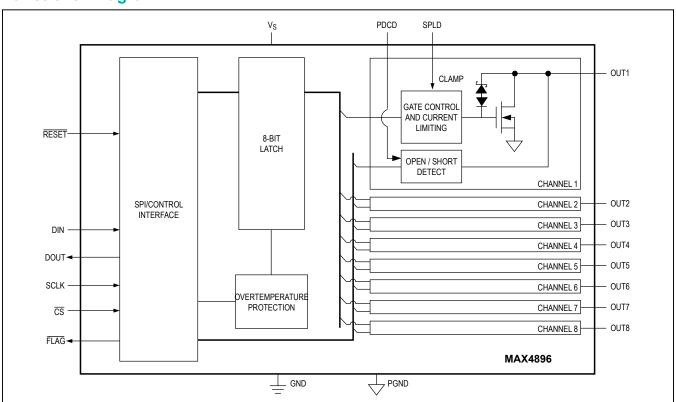

#### Serial Interface

The serial interface consists of an 8-bit input shift register, a parallel latch (output control register) controlled by SCLK and  $\overline{\text{CS}}$ , and an output status register containing diagnostics information. The input to the shift register

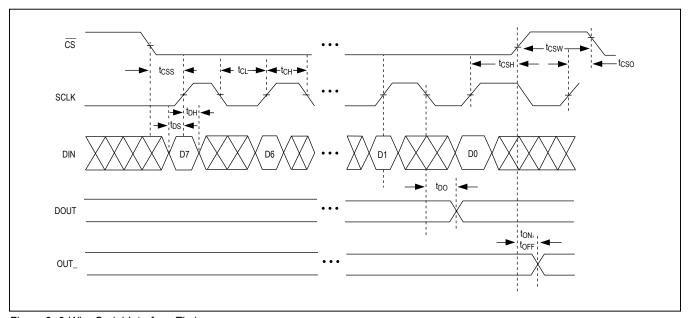

Figure 1. Serial Interface

is an 8-bit word. Each data bit controls one of the eight outputs, with the most significant bit (D7) corresponding to OUT8, and the least significant bit (D0) corresponding to OUT1 (see Table 1). When  $\overline{\text{CS}}$  is low, data at DIN is clocked into the shift register synchronously with SCLK's rising edge. Driving  $\overline{\text{CS}}$  from low to high latches the data in the shift register to the output control register.

DOUT is the output of the internal output status register for diagnostics purposes (see Figure 2 and Tables 2 and 3). Status data for each channel is transferred to the shift register at the falling edge of  $\overline{\text{CS}}$ . The data bits contained in the shift register are then transferred to the DOUT output synchronously with SCLK's falling edge.

While  $\overline{CS}$  is low, the switches always remain in their previous states. Drive  $\overline{CS}$  high after 8 bits of data have been shifted in to update the output state, and to further inhibit data from entering the shift register. When  $\overline{CS}$  is high, transitions at DIN and SCLK have no effect on the output, and the first input bit (D7) is present at DOUT.

If the number of data bits entered while  $\overline{CS}$  is low is greater or less than 8, the shift register contains only the last 8 data bits, regardless of when they were entered.

The 3-wire serial interface is compatible with SPI, QSPI, and MICROWIRE standards. The latch that drives the analog output stages is updated on the rising edge of  $\overline{\text{CS}}$ , regardless of SCLK's state.

#### **Diagnostic Information**

The MAX4896 contains an internal output status register used for diagnostics information for each output (see Tables 1, 2, and 3). When a fault condition is detected at any channel for longer than the minimum fault-filtering time (t<sub>D(FAULT) min</sub>), the fault information is latched into the corresponding position in the output status register (see Table 2), and the FLAG asserts. Status/diagnostics data for each channel in the output status register is transferred to the output shift register at the falling edge of CS. While  $\overline{CS}$  is low, the diagnostics bits are then transferred to DOUT synchronously with SCLK's falling edge. A rising edge at CS resets the output status register data. During normal operation, the output status bit is the same as the DIN bit (DO1 = D1, DO2 = D2). When the MAX4896 is operating with a fault condition, the output status bit is the inverse of the DIN bit (DO1 = 0, D1 = 1).

**Table 1. Serial-Input Address**

| DIN  | D0   | D1   | D2   | D3   | D4   | D5   | D6   | D7   |

|------|------|------|------|------|------|------|------|------|

| OUT_ | OUT1 | OUT2 | OUT3 | OUT4 | OUT5 | OUT6 | OUT7 | OUT8 |

## **Table 2. Serial-Output Address**

| DIN  | DO0  | DO1  | DO2  | DO3  | DO4  | DO5  | DO6  | DO7  |

|------|------|------|------|------|------|------|------|------|

| OUT_ | OUT1 | OUT2 | OUT3 | OUT4 | OUT5 | OUT6 | OUT7 | OUT8 |

**Table 3. Status-Register Output Diagnostic**

| OUTPUT STATUS | T STATUS DO_STATUS BIT DIAGNOSTIC |                                                          |  |

|---------------|-----------------------------------|----------------------------------------------------------|--|

| Off           | Low                               | Normal operation.                                        |  |

| Off           | High                              | Fault condition. Output open or short circuit.           |  |

| On Low        |                                   | Fault condition. Short circuit to positive load voltage. |  |

| On            | High                              | Normal operation.                                        |  |

Figure 2. 3-Wire Serial-Interface Timing

The minimum fault-filtering time helps mask short-duration fault conditions, such as driving highly capacitive loads.

The typical diagnostics software routine works as follows:

- Write data to the MAX4896

- Wait for t<sub>D</sub>(FAULT) maximum to ensure diagnostics data is ready and valid

- Write same data to the MAX4896 and read out the diagnostics data from the shift register

Use Table 3 to diagnose the output state.

To reduce processor overhead, an interrupt-based diagnostics routine is possible. The diagnostics routine will analyze diagnostics data only when the  $\overline{\text{FLAG}}$  output triggers an interrupt.

#### Output Short-Circuit/ Current-Limiting Protection

The MAX4896 channels (OUT\_) are protected against short-circuits conditions. When the channel's output current exceeds the current-limit threshold ( $I_{LIM}$ ) for longer than the minimum fault-filtering time ( $t_{D(FAULT)}$  min), the short-circuit protection is activated. The shortcircuit protection behavior is determined by the logic level at SPLD. When SPLD = high, an overloaded channel remains in a current-limited state until the short-circuit condition is removed or thermal shutdown is reached. This allows the operation of loads where the inrush currents may exceed the MAX4896 internal current limit.

When SPLD = low, an overloaded channel immediately turns off (latched-off). When a shorted output is latched off, the channel can be turned back on after the next serial input data is latched into the MAX4896.

#### **Open-Load Detection**

The MAX4896 features an output pulldown current source, along with a voltage comparator, to detect an open-load fault condition. To enable the open-load detection function, PDCD must be low. The voltage at OUT\_ is compared with the diagnostics threshold voltage  $(V_{DS(OL)})$  to determine whether a open-load fault condition exists.

#### **Thermal Shutdown**

If the junction temperature exceeds  $+160^{\circ}$ C, all outputs are switched off immediately (no filtering time) and  $\overline{FLAG}$  asserts. The hysteresis is approximately  $+20^{\circ}$ C, disabling thermal shutdown once the temperature drops below  $+140^{\circ}$ C.

#### **RESET**

The MAX4896 features an asynchronous reset input that allows the user to simultaneously turn all outputs off using a single control line. Drive RESET low to clear all latches and registers, and to turn off all outputs. While RESET is low, the OUT pulldown currents are disabled, regardless of the state of PDCD.

#### **FLAG** Output

$\overline{\text{FLAG}}$  is an open-drain latched output that can be connected to a μP interrupt and pulls low whenever a fault condition (short-circuit and/or open-load) is detected in any of the eight outputs for longer than the minimum fault-filtering time ( $t_{D(FAULT)}$  min). When not using all channels, connect unused outputs to  $V_S$  through a 10kΩ pullup resistor to avoid inadvertently triggering the  $\overline{\text{FLAG}}$ .  $\overline{\text{FLAG}}$  asserts immediately, (no filtering time), when a thermal-shutdown fault condition is detected. The latch  $\overline{\text{FLAG}}$  deasserts on  $\overline{\text{CS}}$  rising edge.

### **Applications Information**

#### **Daisy Chaining**

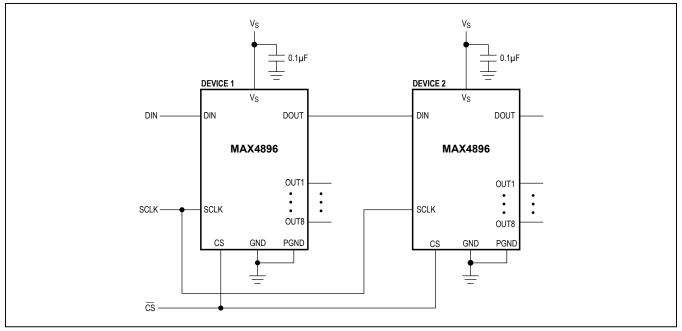

The MAX4896 features a digital output (DOUT) that provides a simple way to daisy chain multiple devices. This feature allows the user to drive large banks of relays using only a single serial interface. To daisy chain multiple devices, connect all  $\overline{CS}$  inputs together and connect the DOUT of one device to the DIN of another device (see Figure 3). During operation, a stream of serial data is shifted through all the MAX4896s in series.

#### **Inductive Kickback Protection**

Each output features an output protection clamp, limiting the OUT voltage to 65V (typ). The clamp protects against voltage transient when driving inductive loads.

Figure 3. Daisy-Chain Configuration

## **Functional Diagram**

## **Pin Configuration**

## **Chip Information**

PROCESS: BICMOS

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE | OUTLINE        | LAND        |

|------------|---------|----------------|-------------|

| TYPE       | CODE    | NO.            | PATTERN NO. |

| 20 TQFN-EP | T2055+5 | <u>21-0140</u> | 90-0010     |

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                             | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------------------------|------------------|

| 0                  | 10/05            | Initial release                                         | _                |

| 1                  | 6/07             | Removal of future product notice                        | -                |

| 2                  | 12/07            | EP clarification                                        | 7                |

| 3                  | 7/12             | Updated FLAG Output section                             | 10               |

| 4                  | 5/14             | Removed automotive reference under Applications section | 1                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.