Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **General Description**

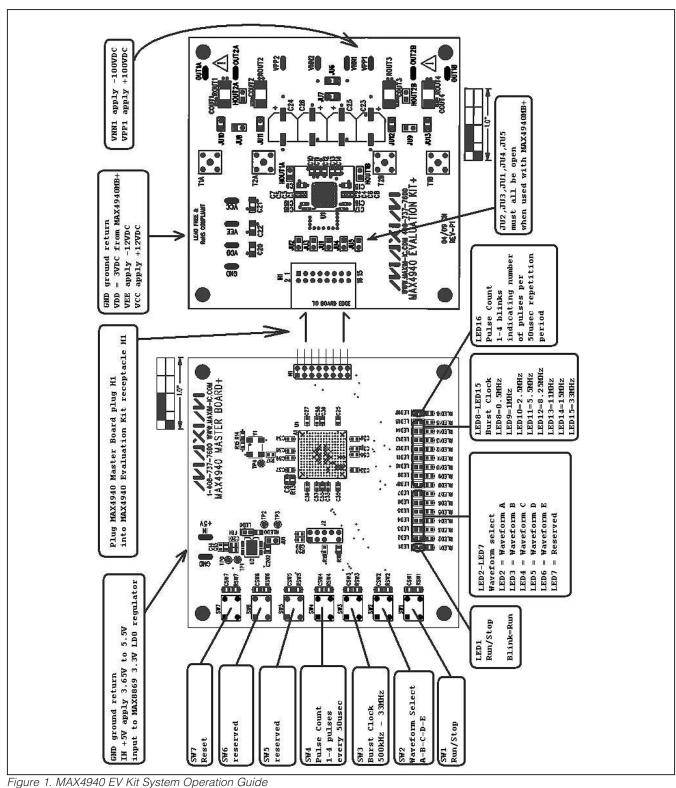

The MAX4940 evaluation kit (EV kit) provides a proven design to evaluate the MAX4940 quad, high-voltage pulse driver. The MAX4940 EV kit can be driven by the MAX4940 Master Board, a signal generator based on the Altera EPM1270F256C5N MAX II CPLD.

The MAX4940 EV kit comes with a MAX4940CTN+ installed. Contact the factory for free samples of the pincompatible MAX4940ACTN+ to evaluate this device.

For complete evaluation, including test waveform generation, order the MAX4940MB+ together with the MAX4940FVKIT+

#### **Features**

- ♦ 3.5mm Scope Probe Jacks

- ♦ Proven PCB Layout

- ◆ Fully Assembled and Tested

- ◆ Stand-Alone Waveform Generation (MAX4940MB+)

#### **Ordering Information**

| PART          | TYPE                            |

|---------------|---------------------------------|

| MAX4940EVKIT+ | EV Kit                          |

| MAX4940MB+    | Master Board (signal generator) |

<sup>+</sup>Denotes lead(Pb)-free and RoHS compliant.

#### **Component Lists**

#### MAX4940 EV Kit

| DESIGNATION   | QTY | DESCRIPTION                                                                   |

|---------------|-----|-------------------------------------------------------------------------------|

| COUT1-COUT4   | 4   | 220pF ±10%, 100V X7R ceramic capacitors (0402) Murata GRM155R72A221K          |

| C1–C8         | 8   | 3300pF ±10%, 100V X7R ceramic capacitors (0402)<br>Murata GRM155R72A332K      |

| C9-C15        | 7   | 0.1µF ±10%, 100V X7R ceramic capacitors (0603) Murata GRM188R72A104K          |

| C16-C19       | 4   | 0.1µF ±10%, 16V X7R ceramic<br>capacitors (0402)<br>Murata GRM155R71C104K     |

| C20, C21, C22 | 3   | 10µF ±10%, 25V X7R ceramic capacitors (1206) Murata GRM31CR71E106K            |

| C23-C26       | 4   | 10μF ±20%, 160V aluminum electrolytic capacitors (G13) Panasonic EEV-EB2C100Q |

| DESIGNATION                                           | QTY | DESCRIPTION                                                          |

|-------------------------------------------------------|-----|----------------------------------------------------------------------|

| H1                                                    | 1   | Dual-row, right-angle header (2 x 8)                                 |

| HOUT1A,<br>HOUT1B,<br>HOUT2A,<br>HOUT2B, JU1–<br>JU13 | 17  | 2-pin headers                                                        |

| ROUT1-ROUT4                                           | 4   | 1kΩ ±5%, 1W resistors (2512)<br>Panasonic ERJ-1TYJ102U               |

| T1A, T1B, T2A,<br>T2B                                 | 4   | Scope probe jacks, 3.5mm                                             |

| U1                                                    | 1   | Quad high-voltage pulse driver<br>(56 TQFN-EP*)<br>Maxim MAX4940CTN+ |

| _                                                     | 11  | Shunts                                                               |

| _                                                     | 1   | PCB: MAX4940 EVALUATION<br>KIT+                                      |

<sup>\*</sup>EP = Exposed pad.

#### **Component Lists (continued)**

#### **MAX4940 Master Board**

| DESIGNATION                                | QTY | DESCRIPTION                                                       |

|--------------------------------------------|-----|-------------------------------------------------------------------|

| C8                                         | 1   | 560pF ±5%, 50V C0G ceramic capacitor (0603) TDK C1608C0G1H561J    |

| C14                                        | 1   | 4.7µF ±10%, 6.3V X5R ceramic capacitor (0603) TDK C1608X5R0J475K  |

| C15, C26, C27,<br>C34, C35,<br>CSW1-CSW7   | 12  | 0.01µF ±10%, 50V X7R ceramic capacitors (0603) TDK C1608X7R1H103K |

| C25, C31, C32,<br>C33, C36–C39,<br>C55–C59 | 13  | 0.1µF ±10%, 50V X7R ceramic capacitors (0603) TDK C1608X7R1H104K  |

| C69                                        | 1   | 10pF ±5%, 50V C0G ceramic capacitor (0603) TDK C1608C0G1H100J     |

| C201, C202                                 | 2   | 1µF ±10%, 10V X7R ceramic capacitors (0603) TDK C1608X7R1A105K    |

| FB1                                        | 1   | Ferrite bead (0603)<br>TDK MMZ1608R301A                           |

| H1                                         | 1   | Dual-row, right-angle header (2 x 8)                              |

| .12                                        | 1   | 10-pin header (2 x 5)                                             |

|                                      |     | ·                                                                   |

|--------------------------------------|-----|---------------------------------------------------------------------|

| DESIGNATION                          | QTY | DESCRIPTION                                                         |

| JU1                                  | 0   | Not installed, 2-pin header                                         |

| LED0-LED16                           | 17  | Red LEDs (0805)                                                     |

| RLED0-RLED16                         | 17  | 200Ω ±5% resistors (0603)                                           |

| R13                                  | 1   | 1kΩ ±5% resistor (0603)                                             |

| R14, R16, R19,<br>R20, RSW1–<br>RSW7 | 11  | 10kΩ ±5% resistors (0603)                                           |

| R15                                  | 0   | Not installed, resistor (0603)                                      |

| R17                                  | 1   | 33Ω ±5% resistor (0603)                                             |

| SW1-SW7                              | 7   | Momentary pushbutton switches, normally open                        |

| TP0-TP4                              | 0   | Not installed, multipurpose test points                             |

| U1                                   | 1   | CPLD, 1270 logic elements<br>(256 FBGA)<br>Altera EPM1270F256C5N    |

| U2                                   | 1   | 3.3V, 1000mA LDO regulator<br>(16 TSSOP-EP*)<br>Maxim MAX8869EUE33+ |

| Y1                                   | 1   | 66MHz crystal oscillator<br>(7.5mm x 5mm)                           |

| _                                    | 1   | PCB: MAX4940 MASTER<br>BOARD+                                       |

<sup>\*</sup>EP = Exposed pad.

#### **Component Suppliers**

| SUPPLIER                               | PHONE        | WEBSITE                     |

|----------------------------------------|--------------|-----------------------------|

| Altera Corp.                           | 800-800-3753 | www.altera.com              |

| Murata Electronics North America, Inc. | 770-436-1300 | www.murata-northamerica.com |

| Panasonic Corp.                        | 800-344-2112 | www.panasonic.com           |

| TDK Corp.                              | 847-803-6100 | www.component.tdk.com       |

**Note:** Indicate that you are using the MAX4940 when contacting these component suppliers.

#### **Quick Start**

#### **Required Equipment**

- MAX4940 EV kit

- MAX4940 Master Board (or equivalent signal generator)

- +5V DC power supply

- ±12V DC dual-tracking power supplies

- ±100V DC at 20mA high-voltage, dual-tracking power supplies

- Recommended: Oscilloscope to view high-voltage outputs

#### **Procedure**

The MAX4940 EV kit is fully assembled and tested. Follow the steps below to verify board operation:

- 1) Verify that the jumpers are in their default positions, as shown in Table 1 with one exception (JU1 must be open).

- 2) Connect the MAX4940 EV kit to the MAX4940 Master Board signal generator.

- Connect an oscilloscope probe to T1A on the MAX4940 EV kit.

- 4) Connect all power-supply ground returns to GND.

- 5) Connect the +5V DC power supply to the IN +5V pad on the MAX4940 Master Board. This powers the on-board MAX8869 +3.3V linear regulator, which drives the CPLD and the MAX4940's VDD supply.

- 6) Connect the +12V DC power supply to VCC on the MAX4940 EV kit.

- Connect the -12V DC power supply to VEE on the MAX4940 EV kit.

- Connect the +100V DC power supply to VPP1 on the MAX4940 EV kit.

- Connect the -100V DC power supply to VNN1 on the MAX4940 EV kit.

- 10) Enable the +5V DC power supply.

- 11) Enable the ±12V DC power supplies.

- 12) Enable the ±100V DC power supplies.

- 13) Set the MAX4940 Master Board to generate waveform A by pressing SW2 until LED2 is lit.

- 14) Verify that the oscilloscope shows expected high-voltage outputs from waveform A (OUT1A).

- 15) Set the MAX4940 Master Board to generate waveform B by pressing SW2 until LED3 is lit.

- 16) Verify that the oscilloscope shows expected high-voltage outputs from waveform B (OUT1A).

- 17) Set the MAX4940 Master Board to generate waveform C by pressing SW2 until LED4 is lit.

- 18) Verify that the oscilloscope shows expected high-voltage outputs from waveform C (OUT1A).

- 19) Set the MAX4940 Master Board to generate waveform D by pressing SW2 until LED5 is lit.

- 20) Verify that the oscilloscope shows expected high-voltage outputs from waveform D (OUT1A).

- 21) Reduce the VPP/VNN supplies to ±5V DC.

- 22) Set the MAX4940 Master Board to generate waveform E by pressing SW2 until LED6 is lit.

- 23) Verify that the oscilloscope shows expected outputs from waveform E (OUT1A).

- 24) Repeat steps 13–23 to view waveforms OUT1B, OUT2A, and OUT2B.

# \_Detailed Description of Hardware MAX4940 EV Kit

The MAX4940 EV kit provides a proven layout for the MAX4940. Capacitors C1-C8 are the "flying caps" for

the MAX4940's internal charge pump. Jumpers JU1–JU5 are used to drive EN and the clamp inputs when the EV kit board is used without the master board. On-board dummy-load circuits are enabled by jumpers JU10–JU13.

Figure 2. MAX4940 Jumper Guide

#### Table 1. MAX4940 EV Kit Jumper Descriptions (JU1-JU13)

| JUMPER | SIGNAL          | SHUNT POSITION                                                                                                            | DESCRIPTION                                                                                                     |     |                                                                                               |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------|

| JU1    | ΓNI             | 1-2*                                                                                                                      | Enable input EN connects to VDD, enabling the high-voltage outputs for normal operation                         |     |                                                                                               |

| 301    | EN Open         | Enable input EN is not connected to VDD (required when driven with MAX4940 Master Board, or other external signal source) |                                                                                                                 |     |                                                                                               |

| 11.10  | JU2 CLP1A Open* | CL D1A                                                                                                                    | CL D1 A                                                                                                         | 1-2 | Clamp input CLP1A connects to VDD, enabling the always-on active clamp feature (MAX4940 only) |

| 302    |                 | Open*                                                                                                                     | CLP1A is not connected to VDD (required when driven with MAX4940 Master Board, or other external signal source) |     |                                                                                               |

| 11.10  | JU3 CLP2A —     | 1-2                                                                                                                       | Clamp input CLP2A connects to VDD, enabling the always-on active clamp feature (MAX4940 only)                   |     |                                                                                               |

| JU3    |                 | Open*                                                                                                                     | CLP2A is not connected to VDD (required when driven with MAX4940 Master Board, or other external signal source) |     |                                                                                               |

Table 1. MAX4940 EV Kit Jumper Descriptions (JU1–JU13) (continued)

| JUMPER  | SIGNAL       | SHUNT POSITION | DESCRIPTION                                                                                                     |

|---------|--------------|----------------|-----------------------------------------------------------------------------------------------------------------|

| JU4     | ULIA OL DOD  | 1-2            | Clamp input CLP2B connects to VDD, enabling the always-on active clamp feature (MAX4940 only)                   |

| 304     | CLP2B        | Open*          | CLP2B is not connected to VDD (required when driven with MAX4940 Master Board, or other external signal source) |

| 11.15   | CLP1B        | 1-2            | Clamp input CLP1B connects to VDD, enabling the always-on active clamp feature (MAX4940 only).                  |

| JU5     | CLAIR        | Open*          | CLP1B is not connected to VDD (required when driven with MAX4940 Master Board, or other external signal source) |

| JU6     | VNN1, VNN2   | 1-2*           | VNN1 and VNN2 are connected together (required when U1 = MAX4940)                                               |

| JU7     | VPP1, VPP2   | 1-2*           | VPP1 and VPP2 are connected together (required when U1 = MAX4940)                                               |

| JU8     | OUT1A, OUT2A | Open*          | OUT1A and OUT2A are independent (required when U1 = MAX4940)                                                    |

| JU9     | OUT1B, OUT2B | Open*          | OUT1B and OUT2B are independent (required when U1 = MAX4940)                                                    |

| JU10    | Load-1A      | 1-2*           | Dummy load ROUT1/COUT1 connects to OUT1A                                                                        |

| 3010    | LOAU-TA      | Open           | Dummy load ROUT1/COUT1 is disconnected                                                                          |

| JU11    | Load-2A      | 1-2*           | Dummy load ROUT2/COUT2 connects to OUT2A                                                                        |

| 3011    | LOau-ZA      | Open           | Dummy load ROUT2/COUT2 is disconnected                                                                          |

| JU12    | Load-2B      | 1-2*           | Dummy load ROUT3/COUT3 connects to OUT2B                                                                        |

| JU 12   | LUau-ZD      | Open           | Dummy load ROUT3/COUT3 is disconnected                                                                          |

| 11.14.0 | Load-1B      | 1-2*           | Dummy load ROUT4/COUT4 connects to OUT1B                                                                        |

| JU13    | LUau-ID      | Open           | Dummy load ROUT4/COUT4 is disconnected                                                                          |

<sup>\*</sup>Default position.

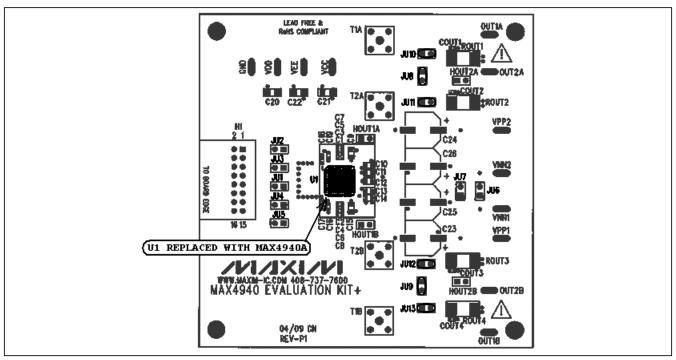

Figure 3. MAX4940A Jumper Guide

#### MAX4940 Master Board

The EPM1270F256C5N (U1) is from Altera's MAX II family of CPLDs. Contact Altera for any questions regarding the CPLD. See the *Component Suppliers* table for contact information.

The MAX8869 (U2) is a high-current, low-dropout (LDO) linear regulator, preset to 3V output. This regulator supplies the CPLD and the MAX4940 EV kit VDD supply.

#### **Pushbutton Switch Operation**

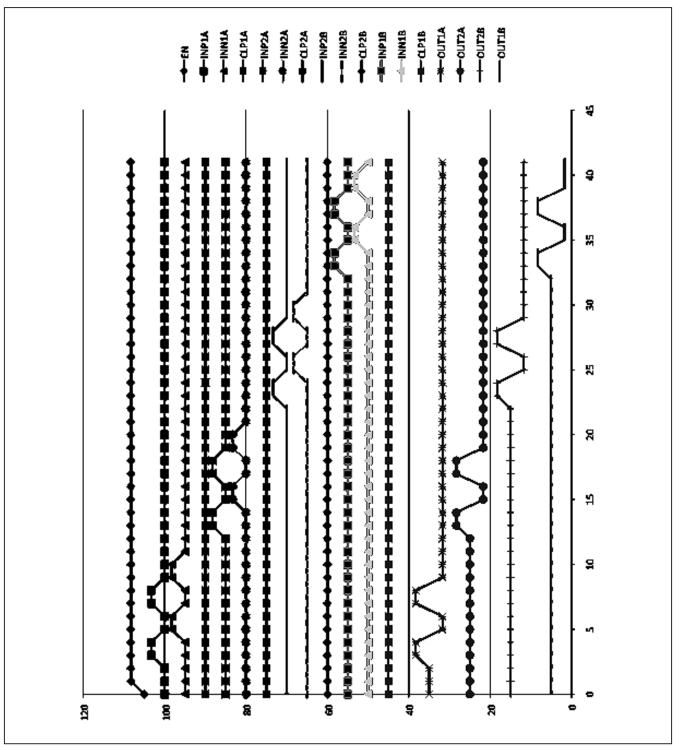

The MAX4940 Master Board firmware is controlled by pushbutton switches SW1–SW7. SW1 toggles between run and stop mode. Pressing and releasing SW2 selects the waveform. Pressing and releasing SW3 selects the burst frequency. SW4 selects the number of times to repeat the waveform. Pressing SW7 resets the MAX4940 Master Board configuration to run waveform A at the fastest burst clock, one pulse every 50µs.

Every 50µs the MAX4940 Master Board self-triggers the selected waveform. The waveform data is determined by

SW2. The burst frequency is determined by SW3, and the number of times the waveform repeats is determined by SW4. Waveform E automatically activates continuous-wave mode, repeating the waveform continuously. For waveform E, the enable output EN is driven with a 10% duty-cycle signal with approximately a 100ms period.

The use of an oscilloscope is recommended to confirm that the correct operation mode is selected.

#### **Evaluating the MAX4940A**

With power disconnected, replace U1 with the MAX4940A IC. Configure the jumpers according to Table 2. Jumpers JU2–JU7 must be open. Move the shunts from JU6 and JU7 to JU8 and JU9. Follow the steps in the *Quick Start* section except a signal source must be used in place of the master board. In addition, use two separate power supplies for VPP1/VNN1 and VPP2/VNN2. Refer to the MAX4940A IC data sheet for more information.

Table 2. MAX4940A Jumper Descriptions (JU1-JU13)

| JUMPER  | SIGNAL       | SHUNT POSITION | DESCRIPTION                                                                                                               |  |

|---------|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------|--|

| 11.14   | EN.          | 1-2*           | Enable input EN connects to VDD, enabling the high-voltage outputs for normal operation                                   |  |

| JU1     | EN           | Open           | Enable input EN is not connected to VDD (required when driven with MAX4940 Master Board, or other external signal source) |  |

| JU2     | CLP1A        | Open*          | CLP1A is not connected to VDD (required when U1 = MAX4940A)                                                               |  |

| JU3     | CLP2A        | Open*          | CLP2A is not connected to VDD (required when U1 = MAX4940A)                                                               |  |

| JU4     | CLP2B        | Open*          | CLP2B is not connected to VDD (required when U1 = MAX4940A)                                                               |  |

| JU5     | CLP1B        | Open*          | CLP1B is not connected to VDD (required when U1 = MAX4940A)                                                               |  |

| JU6     | VNN1, VNN2   | Open           | VNN1 and VNN2 are independent (required when U1 = MAX4940A)                                                               |  |

| JU7     | VPP1, VPP2   | Open           | VPP1 and VPP2 are independent (required when U1 = MAX4940A)                                                               |  |

| JU8     | OUT1A, OUT2A | 1-2            | OUT1A and OUT2A are connected together (required when U1 = MAX4940A)                                                      |  |

| JU9     | OUT1B, OUT2B | 1-2            | OUT1B and OUT2B are connected together (required when U1 = MAX4940A)                                                      |  |

| 11.14.0 | 1 1 . 4 . 4  | 1-2*           | Dummy load ROUT1/COUT1 connects to OUT1A                                                                                  |  |

| JU10    | Load-1A      | Open           | Dummy load ROUT1/COUT1 is disconnected                                                                                    |  |

| II Ia a | 1 1 0 0      | 1-2*           | Dummy load ROUT2/COUT2 and in connects to OUT2A                                                                           |  |

| JU11    | Load-2A      | Open           | Dummy load ROUT2/COUT2 is disconnected                                                                                    |  |

| 11110   | JU12 Load-2B | 1-2*           | Dummy load ROUT3/COUT3 connects to OUT2B                                                                                  |  |

| JU12    |              | Open           | Dummy load ROUT3/COUT3 is disconnected                                                                                    |  |

| 11110   | Lood 1D      | 1-2*           | Dummy load ROUT4/COUT4 connects to OUT1B                                                                                  |  |

| JU 13   | JU13 Load-1B | Open           | Dummy load ROUT4/COUT4 is disconnected                                                                                    |  |

<sup>\*</sup>Default position.

Table 3. MAX4940 Master Board Control Table

| SIGNAL               | SWITCH | LED    | STATE           | MEANING                   |

|----------------------|--------|--------|-----------------|---------------------------|

| D /Ot                | C/V/4  | LED4   | Blinking        | Run mode                  |

| Run/Stop             | SW1    | LED1   | On              | Stop mode                 |

|                      |        | LED2   | On              | Waveform A (see Figure 4) |

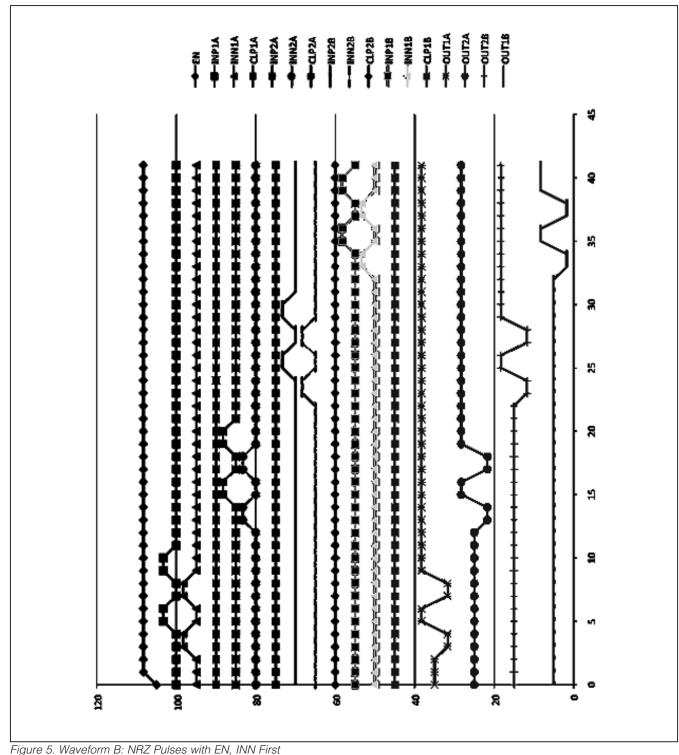

|                      |        | LED3   | On              | Waveform B (see Figure 5) |

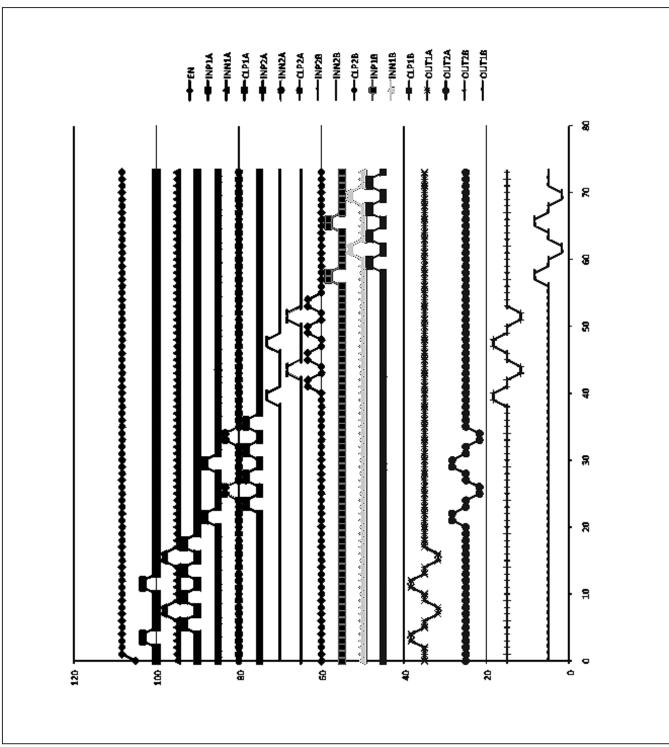

| Waveform             | SW2    | LED4   | On              | Waveform C (see Figure 6) |

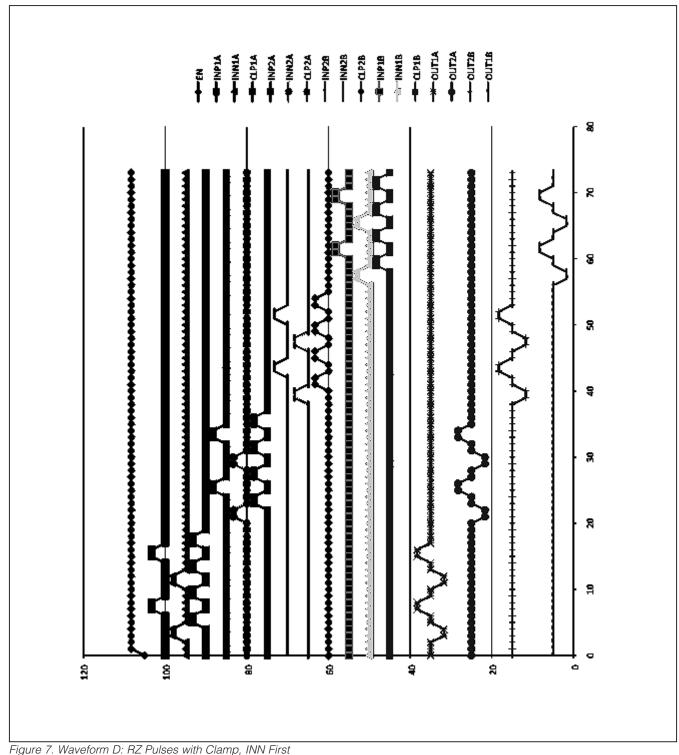

| vvaveioiiii          | 3002   | LED5   | On              | Waveform D (see Figure 7) |

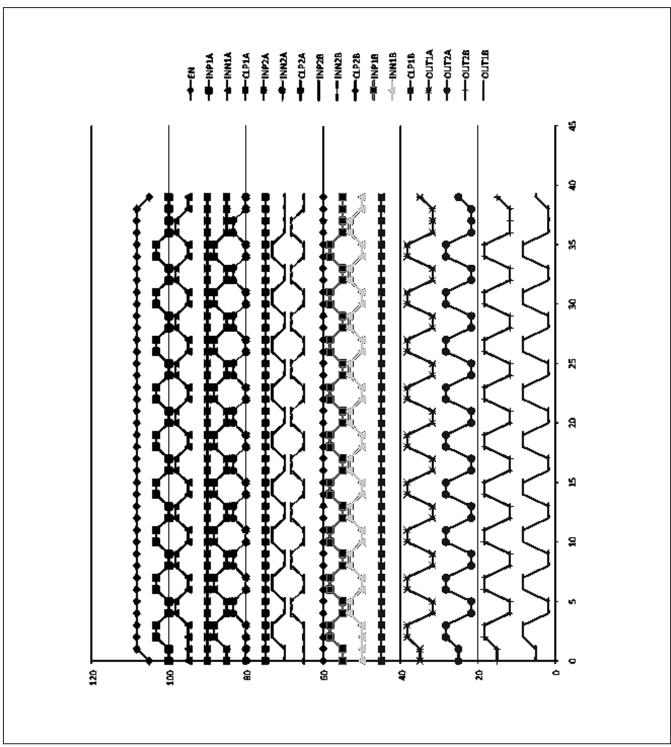

|                      |        | LED6   | On              | Waveform E (see Figure 8) |

|                      |        | LED7   | On              | Reserved                  |

|                      | SW3    | LED8   | On              | 0.5MHz                    |

|                      |        | LED9   | On              | 1MHz                      |

|                      |        | LED10  | On              | 2.53MHz                   |

| Burst clock timebase |        | LED11  | On              | 5.5MHz                    |

| Durst clock timebase |        | LED12  | On              | 8.25MHz                   |

|                      |        | LED13  | On              | 11MHz                     |

|                      |        | LED14  | On              | 15MHz                     |

|                      |        | LED15  | On              | 33MHz                     |

|                      |        |        | Flashes 1 time  | 1 pulse every 50µs        |

| Pulse repeat         | SW4    | LED16  | Flashes 2 times | 2 pulses every 50µs       |

| ruise repeat         |        | LED 16 | Flashes 3 times | 3 pulses every 50µs       |

|                      |        |        | Flashes 4 times | 4 pulses every 50µs       |

Table 4. SW1 Run/Stop Functions

| FUNCTION  | INDICATOR     |

|-----------|---------------|

| Run mode  | LED1 blinking |

| Stop mode | LED1 on       |

**Note:** Each time SW1 is pressed and released, the next function is selected.

**Table 5. SW2 Waveform Functions**

| FUNCTION   | INDICATOR | REMARKS                                        |

|------------|-----------|------------------------------------------------|

| Waveform A | LED2      | NRZ pulses with EN, INP first (see Figure 4)   |

| Waveform B | LED3      | NRZ pulses with EN, INN first (see Figure 5)   |

| Waveform C | LED4      | RZ pulses with clamp, INP first (see Figure 6) |

| Waveform D | LED5      | RZ pulses with clamp, INN first (see Figure 7) |

| Waveform E | LED6      | CW pulses (see Figure 8)                       |

| Reserved   | LED7      | Reserved                                       |

**Note:** Each time SW2 is pressed and released, the next function is selected.

**Table 6. SW3 Burst Clock Functions**

| FUNCTION (MHz) | INDICATOR |

|----------------|-----------|

| 0.5            | LED8      |

| 1              | LED9      |

| 2.53           | LED10     |

| 5.5            | LED11     |

| 8.25           | LED12     |

| 11             | LED13     |

| 15             | LED14     |

| 33             | LED15     |

**Note:** Each time SW3 is pressed and released, the next function is selected.

**Table 7. SW4 Functions**

| FUNCTION            | INDICATOR             |

|---------------------|-----------------------|

| 1 pulse every 50µs  | LED16 flashes 1 time  |

| 2 pulses every 50µs | LED16 flashes 2 times |

| 3 pulses every 50µs | LED16 flashes 3 times |

| 4 pulses every 50µs | LED16 flashes 4 times |

**Note:** Each time SW4 is pressed and released, the next function is selected.

Figure 4. Waveform A: NRZ Pulses with EN, INP First

10

Figure 6. Waveform C: RZ Pulses with Clamp, INP First

MIXIM 12

Figure 8. Waveform E: Alternating INP and INN

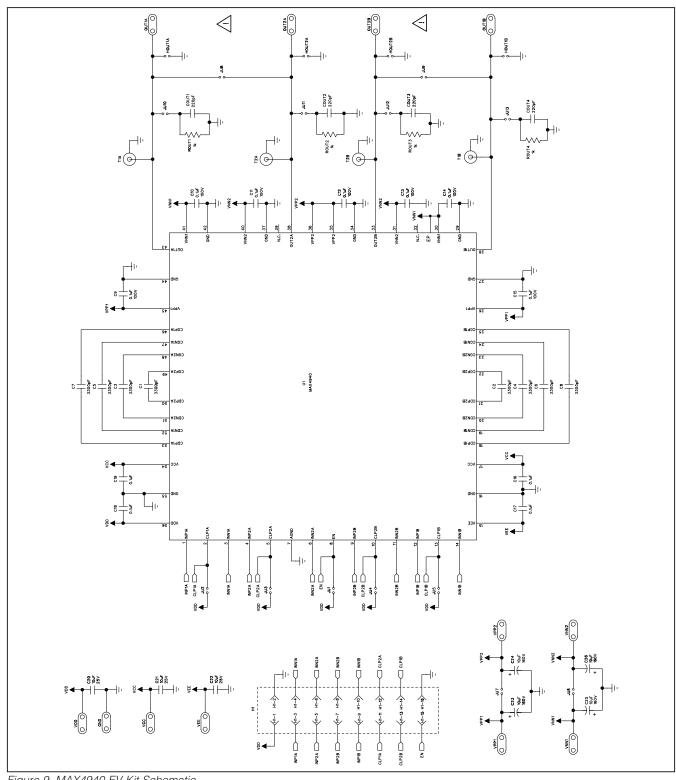

Figure 9. MAX4940 EV Kit Schematic

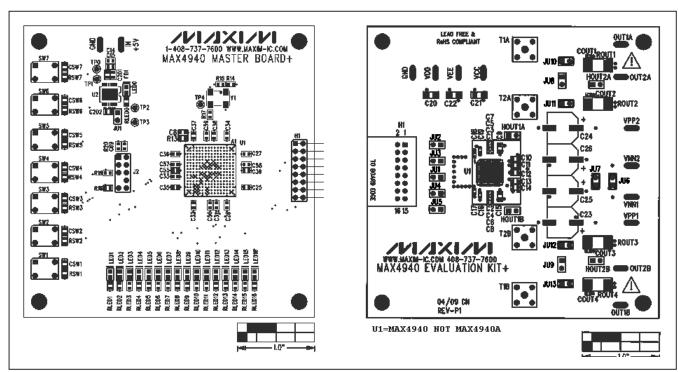

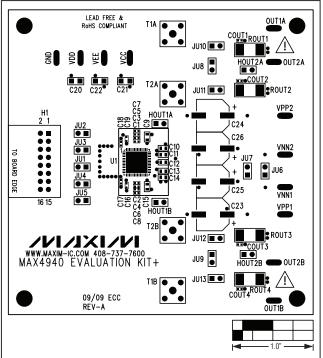

Figure 10. MAX4940 EV Kit Component Placement Guide—Component Side

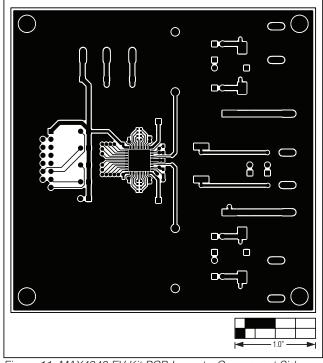

Figure 11. MAX4940 EV Kit PCB Layout—Component Side

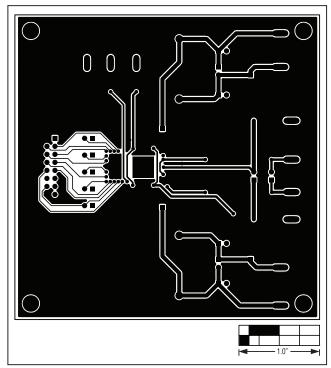

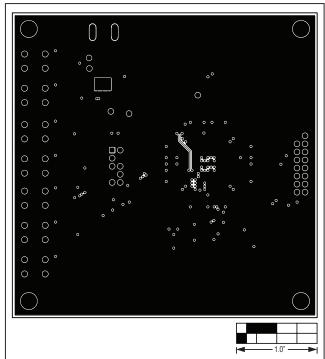

Figure 12. MAX4940 EV Kit PCB Layout—Solder Side

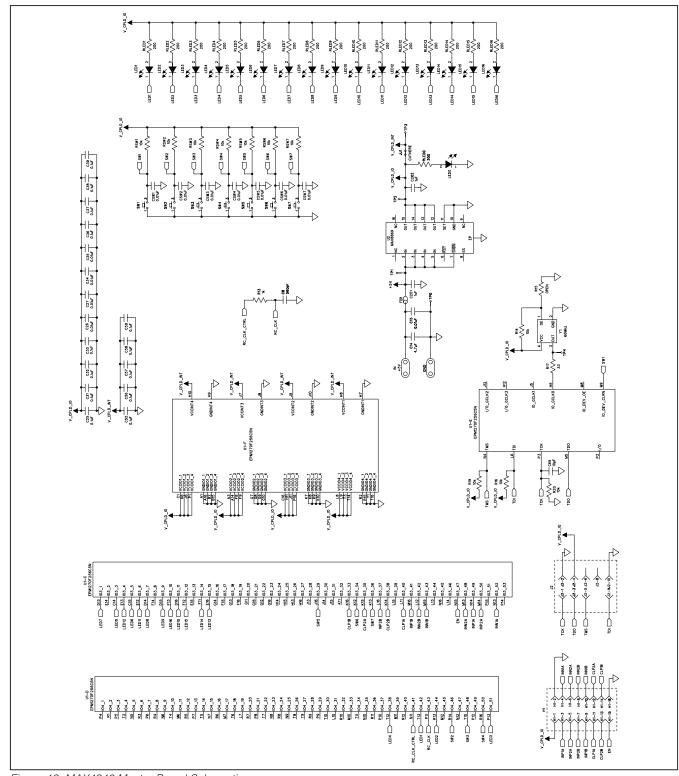

Figure 13. MAX4940 Master Board Schematic

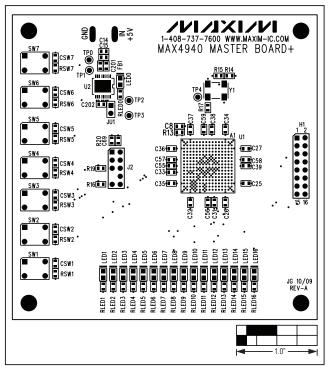

Figure 14. MAX4940 Master Board Component Placement Guide—Component Side

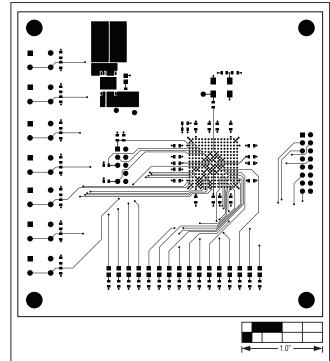

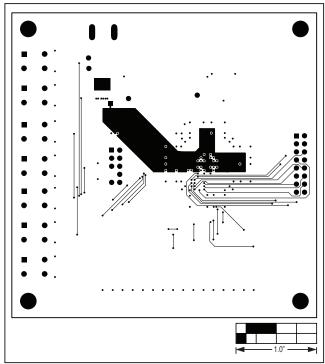

Figure 15. MAX4940 Master Board PCB Layout—Component Side

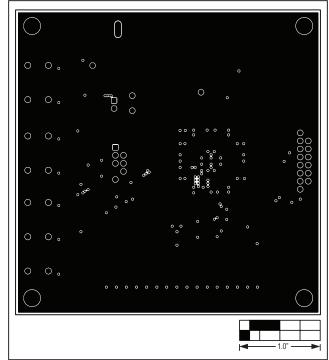

Figure 16. MAX4940 Master Board PCB Layout—Ground Layer 2

Figure 17. MAX4940 Master Board PCB Layout—Power Layer 3

Figure 18. MAX4940 Master Board PCB Layout—Solder Side