# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **General Description**

The MAX536/MAX537 combine four 12-bit, voltage-output digital-to-analog converters (DACs) and four precision output amplifiers in a space-saving 16-pin package. Offset, gain, and linearity are factory calibrated to provide the MAX536's  $\pm 1$  LSB total unadjusted error. The MAX537 operates with  $\pm 5V$  supplies, while the MAX536 uses -5V and +10.8V to +13.2V supplies.

Each DAC has a double-buffered input, organized as an input register followed by a DAC register. A 16-bit serial word is used to load data into each input/DAC register. The serial interface is compatible with either SPI/QSPI™ or MICROWIRE™, and allows the input and DAC registers to be updated independently or simultaneously with a single software command. The DAC registers can be simultaneously updated with a hardware LDAC pin. All logic inputs are TTL/CMOS compatible.

## **Applications**

- Industrial Process Controls Automatic Test Equipment

- Digital Offset and Gain Adjustment

- Motion Control Devices

- Remote Industrial Controls

- Microprocessor-Controlled Systems

## **Features**

- Four 12-Bit DACs with Output Buffers

- Simultaneous or Independent Control of Four DACs via a 3-Wire Serial Interface

- Power-On Reset

- SPI/QSPI and MICROWIRE Compatible

- ◆ ±1 LSB Total Unadjusted Error (MAX536)

- ♦ Full 12-Bit Performance without Adjustments

- ♦ ±5V Supply Operation (MAX537)

- Double-Buffered Digital Inputs

- Buffered Voltage Output

- ♦ 16-Pin DIP/SO Packages

## **Ordering Information**

| PART                                            | TEMP RANGE     | PIN-<br>PACKAGE | INL<br>(LSB) |  |  |  |  |  |

|-------------------------------------------------|----------------|-----------------|--------------|--|--|--|--|--|

| MAX536ACPE+                                     | 0°C to +70°C   | 16 PDIP         | ±0.5         |  |  |  |  |  |

| MAX536BCPE+                                     | 0°C to +70°C   | 16 PDIP         | ±1           |  |  |  |  |  |

| MAX536ACWE+                                     | 0°C to +70°C   | 16 Wide SO      | ±0.5         |  |  |  |  |  |

| MAX536BCWE+                                     | 0°C to +70°C   | 16 Wide SO      | ±1           |  |  |  |  |  |

| MAX536AEPE+                                     | -40°C to +85°C | 16 PDIP         | ±0.5         |  |  |  |  |  |

| MAX536BEPE+                                     | -40°C to +85°C | 16 PDIP         | ±1           |  |  |  |  |  |

| MAX536AEWE+                                     | -40°C to +85°C | 16 Wide SO      | ±0.5         |  |  |  |  |  |

| MAX536BEWE+                                     | -40°C to +85°C | 16 Wide SO      | ±1           |  |  |  |  |  |

| +Denotes a lead/Ph)-free/BoHS-compliant package |                |                 |              |  |  |  |  |  |

+Denotes a lead(Pb)-free/RoHS-compliant package.

Ordering Information continued at end of data sheet.

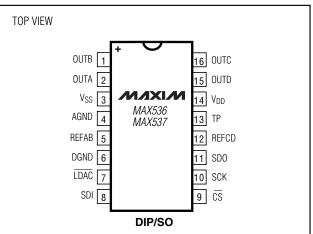

## Pin Configuration

SPI and QSPI are trademarks of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp.

##

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

V<sub>DD</sub> to AGND or DGND MAX536.....-0.3V to +13.2V MAX537 -0.3V to +7V

| MAX537                       | 0.3V to +7V                      |

|------------------------------|----------------------------------|

| VSS to AGND or DGND          | 7V to +0.3V                      |

| SDI, SCK, CS, LDAC, TP, SDO  |                                  |

| to AGND or DGND              | 0.3V to (V <sub>DD</sub> + 0.3V) |

| REFAB, REFCD to AGND or DGND | 0.3V to (VDD + 0.3V)             |

| OUT_ to AGND or DGND         |                                  |

| Maximum Current into Any Pin |                                  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                 |

|-------------------------------------------------------|-----------------|

| Plastic DIP (derate 10.53mW/°C above +70°C) .         | 842mW           |

| Wide SO (derate 9.52mW/°C above +70°C)                | 762mW           |

| Operating Temperature Ranges                          |                 |

| MAX53_AC_E/BC_E                                       | 0°C to +70°C    |

| MAX53_AE_E/BE_E                                       | 40°C to +85°C   |

| Storage Temperature Range                             | -65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C          |

| Soldering Temperature (reflow)                        | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS—MAX536**

$(V_{DD} = +12V, V_{SS} = -5V, REFAB/REFCD = 8V, AGND = DGND = 0V, R_L = 5k\Omega, C_L = 100pF, T_A = T_{MIN}$  to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T\_A = +25°C.)

| PARAMETER                                       | SYMBOL    | CONDITI                                         | ONS                                                              | MIN | ТҮР   | MAX    | UNITS |  |

|-------------------------------------------------|-----------|-------------------------------------------------|------------------------------------------------------------------|-----|-------|--------|-------|--|

| STATIC PERFORMANCE—ANAL                         | OG SECTIO | N                                               |                                                                  |     |       |        |       |  |

| Resolution                                      | Ν         |                                                 |                                                                  | 12  |       |        | Bits  |  |

|                                                 |           | T 0500                                          | MAX536A                                                          |     |       | ±1.0   |       |  |

|                                                 |           | $T_A = +25^{\circ}C$                            | MAX536B                                                          |     |       | ±2.0   |       |  |

| Tatal Use divete d Error (Nate 1)               |           |                                                 | MAX536AC                                                         |     |       | ±2.0   |       |  |

| Total Unadjusted Error (Note 1)                 | TUE       | T. T to T                                       | MAX536BC                                                         |     |       | ±3.0   | LSB   |  |

|                                                 |           | $T_A = T_{MIN}$ to $T_{MAX}$                    | MAX536AE                                                         |     |       | ±2.5   |       |  |

|                                                 |           |                                                 | MAX536BE                                                         |     |       | ±3.5   |       |  |

| Integral Nonlinearity                           | INL       | MAX536A                                         |                                                                  |     | ±0.15 | ±0.50  | LSB   |  |

| Integral Nonlinearity                           |           | MAX536B                                         |                                                                  |     |       | ±1     | LOD   |  |

| Differential Nonlinearity                       | DNL       | Guaranteed monotonic                            |                                                                  |     |       | ±1     | LSB   |  |

|                                                 |           | $T_A = +25^{\circ}C$                            | MAX536A                                                          |     |       | ±2.5   |       |  |

|                                                 |           |                                                 | MAX536B                                                          |     |       | ±5.0   |       |  |

| Offset Error                                    |           |                                                 | MAX536AC                                                         |     |       | ±5.0   | mV    |  |

| Oliset Elloi                                    |           | $T_A = T_{MIN}$ to $T_{MAX}$                    | MAX536BC                                                         |     |       | ±7.5   | IIIV  |  |

|                                                 |           | IA = IMIN IO IMAX                               | MAX536AE                                                         |     |       | ±6.1   |       |  |

|                                                 |           |                                                 | MAX536BE                                                         |     |       | ±8.5   |       |  |

|                                                 |           | RL = ∞                                          |                                                                  |     | -0.1  | ±1.0   |       |  |

| Gain Error                                      |           | $R_{I} = 5k\Omega$                              | MAX536_C/E                                                       |     | -0.6  | ±1.5   | LSB   |  |

|                                                 |           |                                                 | MAX536_M                                                         |     |       | ±2.0   |       |  |

| V <sub>DD</sub> Power-Supply Rejection<br>Ratio | PSRR      | $T_A = +25^{\circ}C$ , 10.8V < $V_{DD} < 13.2V$ |                                                                  |     | ±0.02 | ±0.125 | LSB/V |  |

| V <sub>SS</sub> Power-Supply Rejection Ratio    | PSRR      | $T_A = +25^{\circ}C, -5.5V < V_{DE}$            | $T_A = +25^{\circ}C, -5.5V < V_{DD} < -4.5V$ $\pm 0.03 \pm 0.30$ |     |       |        | LSB/V |  |

## **ELECTRICAL CHARACTERISTICS—MAX536 (continued)**

$(V_{DD} = +12V, V_{SS} = -5V, REFAB/REFCD = 8V, AGND = DGND = 0V, R_L = 5k\Omega, C_L = 100pF, T_A = T_{MIN}$  to T\_MAX, unless otherwise noted. Typical values are at T\_A = +25°C.)

| PARAMETER                               | SYMBOL                  | CONDITIONS                               |                                               | MIN  | ТҮР   | МАХ                 | UNITS |  |

|-----------------------------------------|-------------------------|------------------------------------------|-----------------------------------------------|------|-------|---------------------|-------|--|

| MATCHING PERFORMANCE (T                 | A = +25°C)              |                                          |                                               |      |       |                     |       |  |

|                                         |                         | MAX536A                                  |                                               |      |       | ±1.0                | 1.05  |  |

| Total Unadjusted Error                  | TUE                     | MAX536B                                  |                                               |      |       | ±2.0                | LSB   |  |

| Gain Error                              |                         |                                          |                                               |      | ±0.1  | ±1.0                | LSB   |  |

| Offeet Freez                            |                         | MAX536A                                  |                                               |      | ±1.2  | ±2.5                |       |  |

| Offset Error                            |                         | MAX536B                                  |                                               |      | ±1.2  | ±5.0                | mV    |  |

| Integral Nonlinearity                   | INL                     |                                          |                                               |      | ±0.2  | ±1.0                | LSB   |  |

| REFERENCE INPUT                         |                         |                                          |                                               |      |       |                     |       |  |

| Reference Input Range                   | REF                     |                                          |                                               | 0    |       | V <sub>DD</sub> - 4 | V     |  |

| Reference Input Resistance              | R <sub>REF</sub>        | Code dependen                            | it, minimum at code 555                       | 5    |       |                     | kΩ    |  |

| MULTIPLYING-MODE PERFOR                 | MANCE                   |                                          |                                               |      |       |                     |       |  |

| Reference 3dB Bandwidth                 |                         | $V_{REF} = 2V_{P-P}$                     |                                               |      | 700   |                     | kHz   |  |

|                                         |                         | Input code =                             | $V_{REF} = 10V_{P-P}$ at 400Hz                |      | -100  |                     | -10   |  |

| Reference Feedthrough                   |                         | all 0s                                   | V <sub>REF</sub> = 10V <sub>P-P</sub> at 4kHz |      | -82   |                     | dB    |  |

| Total Harmonic Distortion Plus<br>Noise | THD+N                   | V <sub>REF</sub> = 2.0V <sub>P-P</sub> a |                                               |      | 0.024 |                     | %     |  |

| DIGITAL INPUTS (SDI, SCK, CS            | , LDAC)                 | 1                                        |                                               |      |       |                     |       |  |

| Input High Voltage                      | VIH                     |                                          |                                               | 2.4  |       |                     | V     |  |

| Input Low Voltage                       | VIL                     |                                          |                                               |      |       | 0.8                 | V     |  |

| Input Leakage Current                   |                         | $V_{IN} = 0V \text{ or } V_{DD}$         |                                               |      |       | 1.0                 | μA    |  |

| Input Capacitance (Note 2)              |                         |                                          |                                               |      |       | 10                  | pF    |  |

| DIGITAL OUTPUT (SDO)                    |                         |                                          |                                               |      |       |                     |       |  |

| Output Low Voltage                      | Vol                     | SDO sinking 5m                           | A                                             |      | 0.13  | 0.40                | V     |  |

| Output Leakage Current                  |                         | $SDO = OV to V_{DI}$                     | D                                             |      |       | ±10                 | μA    |  |

| DYNAMIC PERFORMANCE (RL                 | = 5kΩ, C <sub>L</sub> = | 100pF)                                   |                                               |      |       |                     |       |  |

| Voltage Output Slew Rate                |                         |                                          |                                               |      | 5     |                     | V/µs  |  |

| Output Settling Time                    |                         | To ±0.5 LSB of f                         | ull scale                                     |      | 3     |                     | μs    |  |

| Digital Feedthrough                     |                         |                                          |                                               |      | 5     |                     | nV-s  |  |

| Digital Crosstalk (Note 3)              |                         | $V_{REF} = 5V$                           |                                               |      | 8     |                     | nV-s  |  |

| POWER SUPPLIES                          |                         |                                          |                                               |      |       |                     |       |  |

| Positive Supply Range                   | V <sub>DD</sub>         |                                          |                                               | 10.8 |       | 13.2                | V     |  |

| Negative Supply Range                   | V <sub>SS</sub>         |                                          |                                               | -4.5 |       | -5.5                | V     |  |

| Positive Supply Current                 |                         | $T_A = +25^{\circ}C$                     |                                               |      | 8     | 18                  | ^     |  |

| (Note 4)                                | IDD                     | $T_A = T_{MIN}$ to $T_{MAX}$             |                                               |      |       | 25                  | - mA  |  |

| Negative Supply Current                 | 1                       | T <sub>A</sub> = +25°C                   |                                               |      | -6    | -16                 | ^     |  |

| (Note 4)                                | ISS                     | $T_A = T_{MIN}$ to $T_{M}$               | AX                                            |      |       | -23                 | mA    |  |

## **ELECTRICAL CHARACTERISTICS—MAX536 (continued)**

$(V_{DD} = +12V, V_{SS} = -5V, REFAB/REFCD = 8V, AGND = DGND = 0V, R_L = 5k\Omega, C_L = 100pF, T_A = T_{MIN}$  to T\_MAX, unless otherwise noted. Typical values are at T\_A = +25°C.)

| PARAMETER                                       | SYMBOL           | CONDI                            | TIONS    | MIN | ТҮР | MAX | UNITS |

|-------------------------------------------------|------------------|----------------------------------|----------|-----|-----|-----|-------|

| TIMING CHARACTERISTI                            | CS (Note 5)      |                                  |          |     |     |     |       |

| Internal Power-On Reset<br>Pulse Width (Note 2) | <b>t</b> POR     |                                  |          |     |     | 20  | μs    |

| SCK Clock Period                                | tCP              |                                  |          | 100 |     |     | ns    |

| SCK Pulse Width High                            | tсн              |                                  |          | 30  |     |     | ns    |

| SCK Pulse Width Low                             | tCL              |                                  |          | 30  |     |     | ns    |

| CS Fall to SCK Rise<br>Setup Time               | tcss             |                                  |          | 20  |     |     | ns    |

| SCK Rise to <del>CS</del> Rise<br>Hold Time     | tcsн             |                                  |          | 10  |     |     | ns    |

| SDI Setup Time                                  | t <sub>DS</sub>  |                                  |          | 40  | 26  |     | ns    |

| SDI Hold Time                                   | tDH              |                                  |          | 0   |     |     | ns    |

| SCK Rise to SDO Valid                           | tDO1             | 1k $\Omega$ pullup on SDO        | SDO high |     | 78  | 105 | ns    |

| Propagation Delay (Note 6)                      | 1001             | to VDD, C <sub>LOAD</sub> = 50pF | SDO low  |     | 50  | 80  | 113   |

| SCK Fall to SDO Valid                           | t <sub>DO2</sub> | 1k $\Omega$ pullup on SDO        | SDO high |     | 81  | 110 | - ns  |

| Propagation Delay (Note 7)                      | 1002             | to VDD, C <sub>LOAD</sub> = 50pF | SDO low  |     | 53  | 85  | 110   |

| CS Fall to SDO Enable (Note 8)                  | t <sub>DV</sub>  |                                  |          |     | 27  | 45  | ns    |

| CS Rise to SDO Disable (Note 9)                 | t <sub>TR</sub>  |                                  |          |     | 40  | 60  | ns    |

| SCK Rise to CS Fall Delay                       | tCS0             | Continuous SCK, SCK edg          | 20       |     |     | ns  |       |

| CS Rise to SCK Rise<br>Hold Time                | tCS1             | SCK edge ignored                 |          | 20  |     |     | ns    |

| LDAC Pulse Width Low                            | tLDAC            |                                  |          | 30  |     |     | ns    |

| CS Pulse Width High                             | tcsw             |                                  |          | 40  |     |     | ns    |

Note 1: TUE is specified with no resistive load.

Note 2: Guaranteed by design.

Note 3: Crosstalk is defined as the glitch energy at any DAC output in response to a full-scale step change on any other DAC.

Note 4: Digital inputs at 2.4V; with digital inputs at CMOS levels, IDD decreases slightly.

**Note 5:** All input signals are specified with  $t_{R} = t_{F} \le 5n_{S}$ . Logic input swing is 0 to 5V.

Note 6: Serial data clocked out of SDO on SCK's falling edge. (SDO is an open-drain output for the MAX536. The MAX537's SDO pin has an internal active pullup.)

Note 7: Serial data clocked out of SDO on SCK's rising edge.

Note 8: SDO changes from High-Z state to 90% of final value.

Note 9: SDO rises 10% toward High-Z state.

## **ELECTRICAL CHARACTERISTICS—MAX537**

$(V_{DD} = +5V, V_{SS} = -5V, REFAB/REFCD = 2.5V, AGND = DGND = 0V, R_L = 5k\Omega, C_L = 100pF, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at T\_A = +25°C.)

| PARAMETER                                    | SYMBOL    | COND                                                                     | ITIONS                                            | MIN | ТҮР   | MAX                   | UNITS |

|----------------------------------------------|-----------|--------------------------------------------------------------------------|---------------------------------------------------|-----|-------|-----------------------|-------|

| STATIC PERFORMANCE-ANAL                      | OG SECTIO | N                                                                        |                                                   |     |       |                       |       |

| Resolution                                   | Ν         |                                                                          |                                                   | 12  |       |                       | Bits  |

| 1                                            |           | MAX537A                                                                  |                                                   |     | ±0.15 | ±0.50                 |       |

| Integral Nonlinearity                        | INL       | MAX537B                                                                  |                                                   |     |       | ±1                    | LSB   |

| Differential Nonlinearity                    | DNL       | Guaranteed monotoni                                                      | c                                                 |     |       | ±1                    | LSB   |

|                                              |           | T <sub>A</sub> = +25°C                                                   | MAX537A                                           |     |       | ±3.0                  |       |

|                                              |           | TA = +23 C                                                               | MAX537B                                           |     |       | ±6.0                  |       |

| Offset Error                                 |           |                                                                          | MAX537AC                                          |     |       | ±6.0                  | mV    |

| Oliset Ellor                                 |           | $T_A = T_{MIN}$ to $T_{MAX}$                                             | MAX537BC                                          |     |       | ±9.0                  | IIIV  |

|                                              |           | TA - TMIN TO TMAX                                                        | MAX537AE                                          |     |       | ±7.0                  |       |

|                                              |           |                                                                          | MAX537BE                                          |     |       | ±11.0                 |       |

| Gain Error                                   |           | RL = ∞                                                                   |                                                   |     | -0.3  | ±1.5                  | LSB   |

| Gamenor                                      |           | $R_L = 5k\Omega$                                                         |                                                   |     | -0.8  | ±3.0                  | LOD   |

| V <sub>DD</sub> Power-Supply Rejection Ratio | PSRR      | $T_A = +25^{\circ}C, \ 4.5V \le V$                                       | DD ≤ 5.5V                                         |     | ±0.01 | ±0.5                  | LSB/V |

| V <sub>SS</sub> Power-Supply Rejection Ratio | PSRR      | $T_{A} = +25^{\circ}C, -5.5V \leq N$                                     | / <sub>SS</sub> ≤ -4.5V                           |     | ±0.02 | ±0.7                  | LSB/V |

| MATCHING PERFORMANCE (TA                     | = +25°C)  | ſ                                                                        |                                                   | 1   |       |                       |       |

| Gain Error                                   |           |                                                                          |                                                   |     | ±0.1  | ±1.25                 | LSB   |

| Offset Error                                 |           | MAX537A                                                                  |                                                   |     | ±0.3  | ±3.0                  | mV    |

|                                              |           | MAX537B                                                                  |                                                   |     | ±0.3  | ±6.0                  |       |

| Integral Nonlinearity                        | INL       |                                                                          |                                                   |     | ±0.35 | ±1.0                  | LSB   |

| REFERENCE INPUT                              |           | I                                                                        |                                                   |     |       |                       |       |

| Reference Input Range                        | REF       |                                                                          |                                                   | 0   |       | V <sub>DD -</sub> 2.2 | V     |

| Reference Input Resistance                   | RREF      | Code dependent, min                                                      | imum at code 555 hex                              | 5   |       |                       | kΩ    |

| MULTIPLYING-MODE PERFORM                     | ANCE      | I                                                                        |                                                   | 1   |       |                       |       |

| Reference 3dB Bandwidth                      |           | $V_{REF} = 2V_{P-P}$                                                     |                                                   |     | 700   |                       | kHz   |

| Reference Feedthrough                        |           | Input code = all 0s                                                      | V <sub>REF</sub> = 10V <sub>P-P</sub> at<br>400Hz |     | -100  |                       | dB    |

|                                              |           |                                                                          | V <sub>REF</sub> = 10V <sub>P-P</sub> at<br>4kHz  |     | -82   |                       | uD    |

| Total Harmonic Distortion Plus<br>Noise      | THD+N     | $V_{\text{REF}} = 850 \text{mV}_{\text{P-P}} \text{ at } 100 \text{kHz}$ |                                                   |     | 0.024 |                       | %     |

| DIGITAL INPUTS (SDI, SCK, CS,                | LDAC)     |                                                                          |                                                   |     |       |                       |       |

| Input High Voltage                           | VIH       |                                                                          |                                                   | 2.4 |       |                       | V     |

| Input Low Voltage                            | VIL       |                                                                          |                                                   |     |       | 0.8                   | V     |

| Input Leakage Current                        |           | $V_{IN} = 0V \text{ or } V_{DD}$                                         |                                                   |     |       | 1.0                   | μA    |

| Input Capacitance (Note 2)                   |           |                                                                          |                                                   |     |       | 10                    | pF    |

## **ELECTRICAL CHARACTERISTICS—MAX537 (continued)**

$(V_{DD} = +5V, V_{SS} = -5V, REFAB/REFCD = 2.5V, AGND = DGND = 0V, R_L = 5k\Omega, C_L = 100pF, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                  | SYMBOL                   | CONDITIONS                           | MIN                      | ТҮР                       | MAX  | UNITS |

|--------------------------------------------|--------------------------|--------------------------------------|--------------------------|---------------------------|------|-------|

| DIGITAL OUTPUT (SDO)                       |                          |                                      | •                        |                           |      |       |

| Output High Voltage                        | V <sub>OH</sub>          | SDO sourcing 2mA                     | V <sub>DD</sub> -<br>0.5 | V <sub>DD</sub> -<br>0.25 |      | V     |

| Output Low Voltage                         | VOL                      | SDO sinking 2mA                      |                          | 0.13                      | 0.40 | V     |

| DYNAMIC PERFORMANCE (RL =                  | = 5kΩ, CL = <sup>·</sup> | 100pF)                               |                          |                           |      |       |

| Voltage Output Slew Rate                   |                          |                                      |                          | 5                         |      | V/µs  |

| Output Settling Time                       |                          | To ±0.5 LSB of full scale            |                          | 5                         |      | μs    |

| Digital Feedthrough                        |                          |                                      |                          | 5                         |      | nV-s  |

| Digital Crosstalk (Note 3)                 |                          |                                      |                          | 5                         |      | nV-s  |

| POWER SUPPLIES                             |                          |                                      |                          |                           |      |       |

| Positive Supply Range                      | V <sub>DD</sub>          |                                      | 4.5                      |                           | 5.5  | V     |

| Negative Supply Range                      | V <sub>SS</sub>          |                                      | -4.5                     |                           | -5.5 | V     |

| Desitive Supply Surrent (Nets 4)           | IDD                      | $T_A = +25^{\circ}C$                 |                          | 5.5                       | 12   |       |

| Positive Supply Current (Note 4)           |                          | $T_A = T_{MIN}$ to $T_{MAX}$         |                          |                           | 16   | mA    |

|                                            | ISS                      | $T_A = +25^{\circ}C$                 |                          | -4.7                      | -10  |       |

| Negative Supply Current (Note 4)           |                          | $T_A = T_{MIN}$ to $T_{MAX}$         |                          |                           | -14  | mA    |

| TIMING CHARACTERISTICS (Not                | te 5)                    |                                      |                          |                           |      |       |

| Internal Power-On Reset Pulse              |                          |                                      |                          |                           | 50   |       |

| Width (Note 2)                             | <b>t</b> POR             |                                      |                          |                           | 50   | μs    |

| SCK Clock Period                           | tCP                      |                                      | 100                      |                           |      | ns    |

| SCK Pulse Width High                       | tсн                      | MAX537_C/E                           | 35                       |                           |      | ns    |

| SCK Pulse Width Low                        | tCL                      | MAX537_C/E                           | 35                       |                           |      | ns    |

| CS Fall to SCK Rise Setup Time             | tcss                     | MAX537_C/E                           | 40                       |                           |      | ns    |

| SCK Rise to $\overline{CS}$ Rise Hold Time | tCSH                     |                                      | 0                        |                           |      | ns    |

| SDI Setup Time                             | tDS                      | MAX537_C/E                           | 40                       | 24                        |      | ns    |

| SDI Hold Time                              | tDH                      |                                      | 0                        |                           |      | ns    |

| SCK Rise to SDO Valid                      | <b>1</b>                 |                                      |                          | 110                       | 000  |       |

| Propagation Delay (Note 6)                 | tDO1                     | $C_{LOAD} = 50 pF, MAX537_C/E$       |                          | 116                       | 200  | ns    |

| SCK Fall To SDO Valid                      | t <sub>DO2</sub>         | C <sub>LOAD</sub> = 50pF, MAX537_C/E |                          | 123                       | 210  | ns    |

| Propagation Delay (Note 7)                 | .002                     |                                      |                          |                           |      |       |

## ELECTRICAL CHARACTERISTICS—MAX537 (continued)

$(V_{DD} = +5V, V_{SS} = -5V, REFAB/REFCD = 2.5V, AGND = DGND = 0V, R_L = 5k\Omega, C_L = 100pF, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                            | SYMBOL          | CONDITIONS                       | MIN | ТҮР | MAX | UNITS |

|------------------------------------------------------|-----------------|----------------------------------|-----|-----|-----|-------|

| CS Fall to SDO Enable                                | t <sub>DV</sub> | $C_{LOAD} = 50 pF, MAX537_C/E$   |     | 75  | 140 | ns    |

| $\overline{\text{CS}}$ Rise to DSO Disable (Note 10) | t <sub>TR</sub> | $C_{LOAD} = 50 pF, MAX537_C/E$   |     | 70  | 130 | ns    |

| SCK Rise to $\overline{CS}$ Fall Delay               | tcso            | Continuous SCK, SCK edge ignored | 35  |     |     | ns    |

| CS Rise to SCK Rise Hold Time                        | tCS1            | SCK edge ignored, MAX537_C/E     | 35  |     |     | ns    |

| LDAC Pulse Width High                                | tLDAC           | MAX537_C/E                       | 50  |     |     | ns    |

| CS Pulse Width High                                  | tcsw            | MAX537_C/E                       | 100 |     |     | ns    |

**Note 2:** Guaranteed by design.

Note 3: Crosstalk is defined as the glitch energy at any DAC output in response to a full-scale step change on any other DAC.

Note 4: Digital inputs at 2.4V; with digital inputs at CMOS levels, IDD decreases slightly.

**Note 5:** All input signals are specified with  $t_R = t_F \le 5ns$ . Logic input swing is 0 to 5V.

**Note 6:** Serial data clocked out of SDO on SCK's falling edge. (SDO is an open-drain output for the MAX536. The MAX537's SDO pin has an internal active pullup.)

**Note 7:** Serial data clocked out of SDO on SCK's rising edge.

Note 10: When disabled, SDO is internally pulled high.

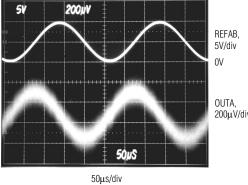

500µs/div INPUT CODE = ALL 0s

500uS

INPUT CODE = ALL 0s

///XI//

MAX536/MAX537

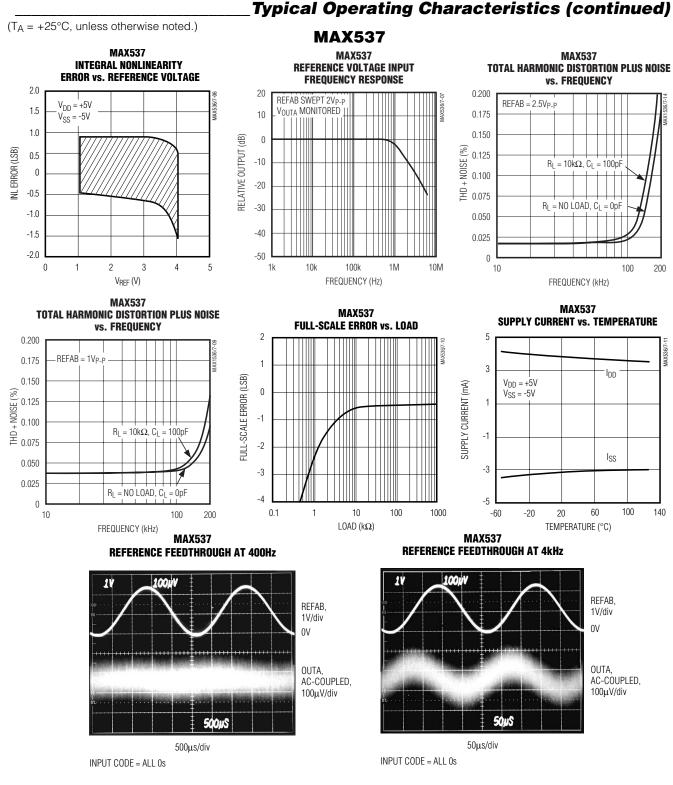

## Typical Operating Characteristics (continued)

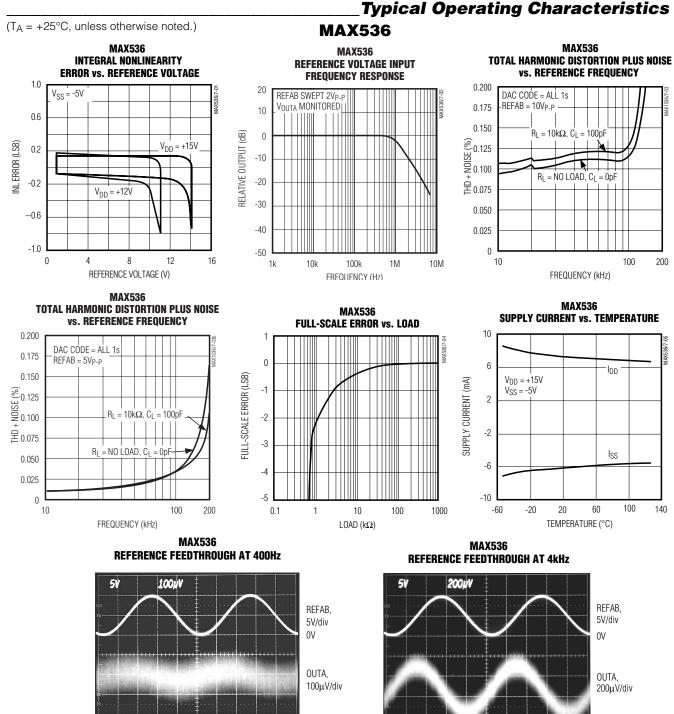

$(T_A = +25^{\circ}C, unless otherwise noted.)$

#### **MAX536**

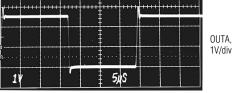

MAX536 DYNAMIC RESPONSE (ALL BITS ON, OFF, ON)

$V_{DD}$  = +15V,  $V_{SS}$  = -5V, REFAB = 5V,  $C_L$  = 100pF,  $R_L$  = 10k $\Omega$

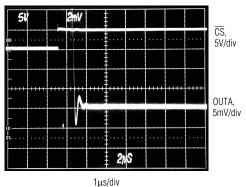

MAX536 POSITIVE FULL-SCALE SETTLING TIME (ALL BITS OFF TO ALL BITS ON)

$V_{DD}$  = +15V,  $V_{SS}$  = -5V, REFAB = 10V,  $C_L$  = 100pF,  $R_I$  = 10k $\Omega$

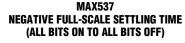

MAX536 NEGATIVE FULL-SCALE SETTLING TIME (ALL BITS ON TO ALL BITS OFF)

$V_{DD}$  = +15V,  $V_{SS}$  = -5V, REFAB = 10V,  $C_{I}$  = 100pF,  $R_{I}$  = 10k $\Omega$

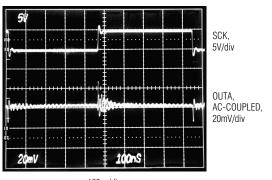

## SCK, 5V/div SCK, 5V/div UUTA, AC-COUPLED, 10mV/div

$V_{DD}$  = +15V,  $V_{SS}$  = -5V, REFAB = 10V,  $\overline{CS}$  = HIGH, DIN TOGGLING AT  $\frac{1}{2}$  THE CLOCK RATE, OUTA = 5V

MAX536 DIGITAL FEEDTHROUGH

/N/IXI/N

MAX536/MAX537

10

## Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, unless otherwise noted.)$

**MAX537**

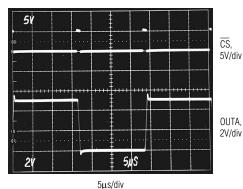

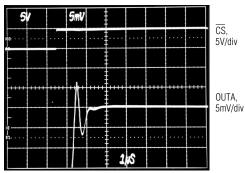

MAX537 DYNAMIC RESPONSE (ALL BITS ON, OFF, ON)

$5\mu s/div \label{eq:VDD} V_{DD}$  = +5V,  $V_{SS}$  = -5V, REFAB = 2.5V, C\_L = 100pF, R\_L = 10k $\Omega$

$V_{DD}$  = +5V,  $V_{SS}$  = -5V, REFAB = 2.5V,  $C_L$  = 100pF,  $R_L$  = 10k $\Omega$

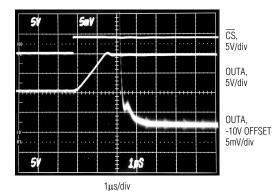

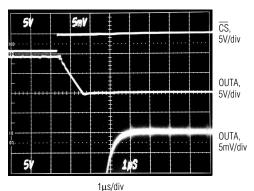

MAX537 POSITIVE FULL-SCALE SETTLING TIME (ALL BITS OFF TO ALL BITS ON)

$1\mu s/div \label{eq:VDD} V_{DD}$  = +5V,  $V_{SS}$  = -5V, REFAB = 2.5V,  $C_L$  = 100pF,  $R_L$  = 10k $\Omega$

MAX537 Digital Feedthrough

$\begin{array}{c} 100\text{ns/div} \\ \text{V}_{\text{DD}} = +5\text{V}, \ \text{V}_{SS} = -5\text{V}, \ \text{REFAB} = 2.5\text{V}, \ \overline{\text{CS}} = \text{HIGH}, \\ \text{DIN TOGGLING AT } 1_2^{} \text{THE CLOCK RATE}, \\ \text{OUTA} = 1.25\text{V} \end{array}$

## Pin Description

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                        |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | OUTB            | DAC B Output Voltage                                                                                                                                                                                                            |

| 2   | OUTA            | DAC A Output Voltage                                                                                                                                                                                                            |

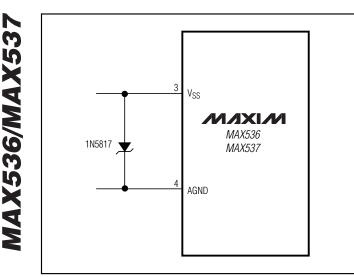

| 3   | V <sub>SS</sub> | Negative Power Supply                                                                                                                                                                                                           |

| 4   | AGND            | Analog Ground                                                                                                                                                                                                                   |

| 5   | REFAB           | Reference Voltage Input for DAC A and DAC B                                                                                                                                                                                     |

| 6   | DGND            | Digital Ground                                                                                                                                                                                                                  |

| 7   | LDAC            | Load DAC Input (active low). Driving this asynchronous input low transfers the contents of all input registers to their respective DAC registers.                                                                               |

| 8   | SDI             | Serial Data Input. Data is shifted into an internal 16-bit shift register on SCK's rising edge.                                                                                                                                 |

| 9   | CS              | Chip-Select Input (active low). A low level on $\overline{CS}$ enables the input shift register and SDO. On $\overline{CS}$ 's rising edge, data is latched into the appropriate register(s).                                   |

| 10  | SCK             | Shift Register Clock Input                                                                                                                                                                                                      |

| 11  | SDO             | Serial Data Output. SDO is the output of the internal shift register. SDO is enabled when $\overline{CS}$ is low.<br>For the MAX536, SDO is an open-drain output. For the MAX537, SDO has an active pullup to V <sub>DD</sub> . |

| 12  | REFCD           | Reference Voltage Input for DAC C and DAC D                                                                                                                                                                                     |

| 13  | TP              | Test Pin. Connect to V <sub>DD</sub> for proper operation.                                                                                                                                                                      |

| 14  | Vdd             | Positive Power Supply                                                                                                                                                                                                           |

| 15  | OUTD            | DAC D Output Voltage                                                                                                                                                                                                            |

| 16  | OUTC            | DAC C Output Voltage                                                                                                                                                                                                            |

## **Detailed Description**

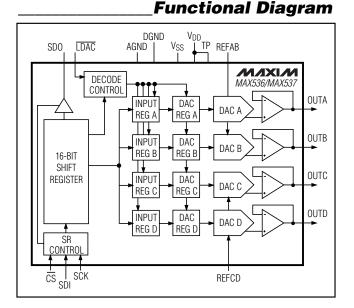

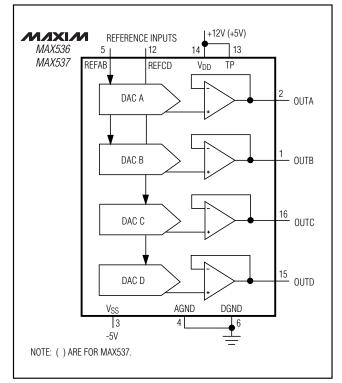

The MAX536/MAX537 contain four 12-bit voltage-output DACs that are easily addressed using a simple 3-wire serial interface. They include a 16-bit data-in/data-out shift register, and each DAC has a double-buffered input composed of an input register and a DAC register (see the *Functional Diagram* on the front page).

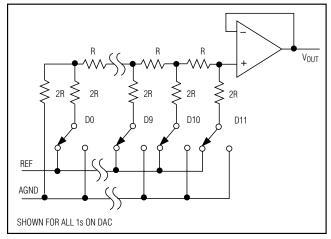

The DACs are "inverted" R-2R ladder networks that convert 12-bit digital inputs into equivalent analog output voltages in proportion to the applied reference-voltage inputs. DAC A and DAC B share the REFAB reference input, while DAC C and DAC D share the REFCD reference input. The two reference inputs allow different full-scale output voltage ranges for each pair of DACs. Figure 1 shows a simplified circuit diagram of one of the four DACs.

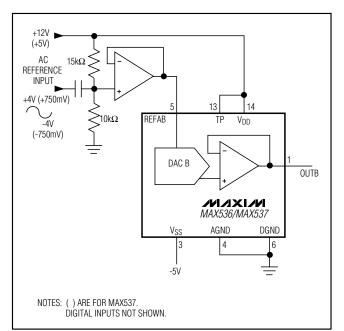

#### **Reference Inputs**

The two reference inputs accept positive DC and AC signals. The voltage at each reference input sets the full-scale output voltage for its two corresponding DACs. The REFAB/REFCD voltage range is 0V to ( $V_{DD}$  - 4V) for the MAX536 and 0V to ( $V_{DD}$  - 2.2V) for the MAX537. The output voltages V<sub>OUT</sub> are represented by

Figure 1. Simplified DAC Circuit Diagram

a digitally programmable voltage source as:

$V_{OUT} = N_B (V_{REF})/4096$

where NB is the numeric value of the DAC's binary input code (0 to 4095) and VREF is the reference voltage.

The input impedance at each reference input is code dependent, ranging from a low value of typically  $6k\Omega$  (with an input code of 0101 0101 0101) to a high value of  $60k\Omega$  (with an input code of 0000 0000 0000). Since the input impedance at the reference pins is code dependent, load regulation of the reference source is important.

The REFAB and REFCD reference inputs have a  $5k\Omega$  guaranteed minimum input impedance. When the two reference inputs are driven from the same source, the effective minimum impedance becomes  $2.5k\Omega$ .

The reference input capacitance is also code dependent and typically ranges from 125pF to 300pF.

#### **Output Buffer Amplifiers**

All MAX536/MAX537 voltage outputs are internally buffered by precision unity-gain followers with a typical slew rate of  $5V/\mu s$  for the MAX536 and  $3V/\mu s$  for the MAX537.

With a full-scale transition at the MAX536 output (0 to 8V or 8V to 0), the typical settling time to  $\pm 0.5$  LSB is 3µs when loaded with 5k $\Omega$  in parallel with 100pF (loads less than 5k $\Omega$  degrade performance).

With a full-scale transition at the MAX537 output (0 to 2.5V or 2.5V to 0), the typical settling time to  $\pm$ 0.5 LSB

is 5µs when loaded with 5k $\Omega$  in parallel with 100pF (loads less than 5k $\Omega$  degrade performance).

Output dynamic responses and settling performances of the MAX536/MAX537 output amplifier are shown in the *Typical Operating Characteristics*.

#### **Serial-Interface Configurations**

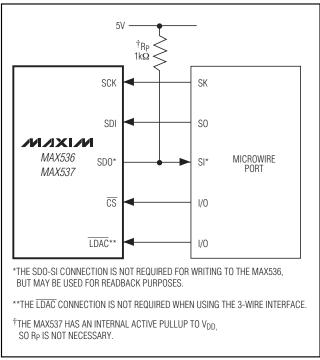

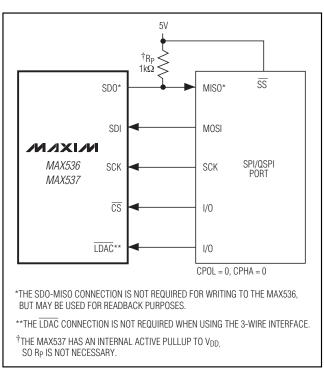

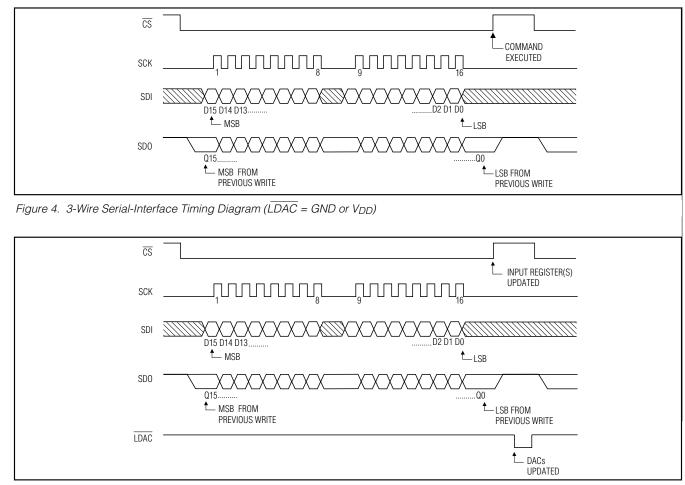

The MAX536/MAX537's 3-wire or 4-wire serial interface is compatible with both MICROWIRE (Figure 2) and SPI/QSPI (Figure 3). In Figures 2 and 3, LDAC can be tied either high or low for a 3-wire interface, or used as the fourth input with a 4-wire interface. The connection between SDO and the serial-interface port is not necessary, but may be used for data echo. (Data held in the shift register of the MAX536/MAX537 can be shifted out of SDO and returned to the microprocessor for data verification; data in the MAX536/MAX537 input/DAC registers cannot be read.)

With a 3-wire interface ( $\overline{CS}$ , SCK, SDI) and  $\overline{LDAC}$  tied high, the DACs are double-buffered. In this mode, depending on the command issued through the serial interface, the input register(s) may be loaded without affecting the DAC register(s), the DAC register(s) can be loaded directly, or all four DAC registers may be simultaneously updated from the input registers. With a 3wire interface ( $\overline{CS}$ , SCK, SDI) and  $\overline{LDAC}$  tied low (Figure

Figure 2. Connections for MICROWIRE

M/XI/N

Figure 3. Connections for SPI/QSPI

Figure 5. 4-Wire Serial-Interface Timing Diagram for Asynchronous DAC Updating Using LDAC

Figure 6. Detailed Serial-Interface Timing Diagram

MAX536/MAX537

4), the DAC registers remain transparent. Any time an input register is updated, the change appears at the DAC output with the rising edge of  $\overline{\text{CS}}$ .

The 4-wire interface ( $\overline{CS}$ , SCK, SDI,  $\overline{LDAC}$ ) is similar to the 3-wire interface with  $\overline{LDAC}$  tied high, except  $\overline{LDAC}$  is a hardware input that simultaneously and asynchronously loads all DAC registers from their respective input registers when driven low (Figure 5).

#### **Serial-Interface Description**

The MAX536/MAX537 require 16 bits of serial data. Data is sent MSB first and can be sent in two 8-bit packets or one 16-bit word ( $\overline{CS}$  must remain low until 16 bits are transferred). The serial data is composed of two DAC address bits (A1, A0), two control bits (C1, C0), and the 12 data bits D11...D0 (Figure 7). The 4-bit address/control code determines the following: 1) the register(s) to be updated and/or the status of the input and DAC registers (i.e., whether they are in transparent or latch mode), and 2) the edge on which data is clocked out of SDO.

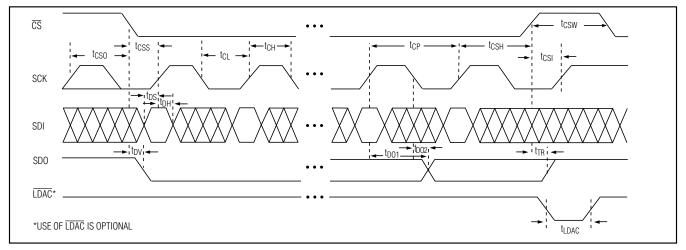

Figure 6 shows the serial-interface timing requirements. The chip-select pin  $\overline{(CS)}$  must be low to enable the DAC's serial interface. When CS is high, the interface control circuitry is disabled and the serial data output pin (SDO) is driven high (MAX537) or is a high-impedance open drain (MAX536).  $\overline{CS}$  must go low at least  $t_{CSS}$  before the rising serial clock (SCK) edge to properly clock in the first bit. When  $\overline{CS}$  is low, data is clocked into the internal shift register via the serial data input pin (SDI) on SCK's rising edge. The maximum guaranteed clock frequency is 10MHz. Data is latched into the appropriate MAX536/MAX537 input/DAC registers on  $\overline{CS}$ 's rising edge.

| MSE | MSBLSB         |                   |    |                     |  |  |  |  |  |  |

|-----|----------------|-------------------|----|---------------------|--|--|--|--|--|--|

|     |                |                   |    |                     |  |  |  |  |  |  |

|     | ress<br>its    | Control<br>Bits   |    | Data Bits<br>MSBLSB |  |  |  |  |  |  |

| A1  | A0             | C1                | C0 | D11D0               |  |  |  |  |  |  |

| -   | 4 Ado<br>Contr | dress/<br>ol Bits | -> | ← 12 Data Bits − ►  |  |  |  |  |  |  |

Figure 7. Serial-Data Format (MSB Sent First)

Interface timing is optimized when serial data is clocked out of the microcontroller/microprocessor on one clock edge and clocked into the MAX536/MAX537 on the other edge. Table 1 lists the serial-interface programming commands. For certain commands, the 12 data bits are "don't cares".

The programming command Load-All-DACs-From-Shift-Register allows all input and DAC registers to be simultaneously loaded with the same digital code from the input shift register. The NOP (no operation) command allows the register contents to be unaffected and is useful when the MAX536/MAX537 are configured in a daisy-chain (see the *Daisy-Chaining Devices* section). The command to change the clock edge on which serial data is shifted out of the MAX536/MAX537 SDO pin also loads data from all input registers to their respective DAC registers.

#### Serial-Data Output

The serial-data output, SDO, is the internal shift register's output. The MAX536/MAX537 can be programmed so that data is clocked out of SDO on SCK's rising (Mode 1) or falling (Mode 0) edge . In Mode 0, output data at SDO lags input data at SDI by 16.5 clock cycles, maintaining compatibility with MICROWIRE, SPI/QSPI, and other serial interfaces. In Mode 1, output data lags input data by 16 clock cycles. On power-up, SDO defaults to Mode 1 timing.

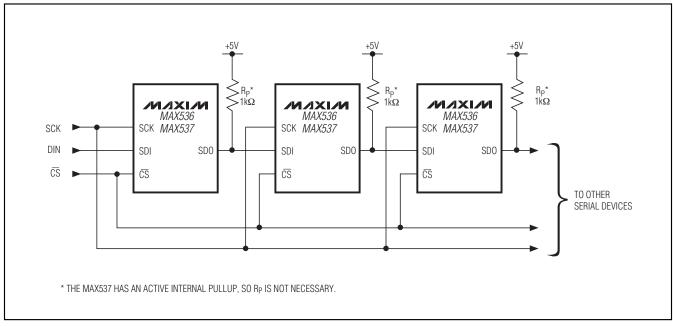

For the MAX536, SDO is an open-drain output that should be pulled up to +5V. The data sheet timing specifications for SDO use a 1k $\Omega$  pullup resistor. For the MAX537, SDO is a complementary output and does not require an external pullup.

#### **Test Pin**

The test pin (TP) is used for pre-production analysis of the IC. Connect TP to V<sub>DD</sub> for proper MAX536/MAX537 operation. Failure to do so affects DAC operation.

#### **Daisy-Chaining Devices**

Any number of MAX536/MAX537s can be daisy-chained by connecting the SDO pin of one device (with a pullup resistor, if appropriate) to the SDI pin of the following device in the chain (Figure 8).

Since the MAX537's SDO pin has an internal active pullup, the SDO sink/source capability determines the time required to discharge/charge a capacitive load. Refer to the serial data out V<sub>OH</sub> and V<sub>OL</sub> specifications in the *Electrical Characteristics*.

|    | 16-BIT SERIAL WORD |    |    | FUNCTION        |   |                                                                                                                                        |

|----|--------------------|----|----|-----------------|---|----------------------------------------------------------------------------------------------------------------------------------------|

| A1 | <b>A</b> 0         | C1 | C0 | D11D0           |   | FUNCTION                                                                                                                               |

| 0  | 0                  | 0  | 1  | 12-bit DAC data | 1 | Load DAC A input register; DAC output unchanged.                                                                                       |

| 0  | 1                  | 0  | 1  | 12-bit DAC data | 1 | Load DAC B input register; DAC output unchanged.                                                                                       |

| 1  | 0                  | 0  | 1  | 12-bit DAC data | 1 | Load DAC C input register; DAC output unchanged.                                                                                       |

| 1  | 1                  | 0  | 1  | 12-bit DAC data | 1 | Load DAC D input register; DAC output unchanged.                                                                                       |

| 0  | 0                  | 1  | 1  | 12-bit DAC data | 1 | Load input register A; all DAC registers updated.                                                                                      |

| 0  | 1                  | 1  | 1  | 12-bit DAC data | 1 | Load input register B; all DAC registers updated.                                                                                      |

| 1  | 0                  | 1  | 1  | 12-bit DAC data | 1 | Load input register C; all DAC registers updated.                                                                                      |

| 1  | 1                  | 1  | 1  | 12-bit DAC data | 1 | Load input register D; all DAC registers updated.                                                                                      |

| Х  | 0                  | 0  | 0  | 12-bit DAC data | Х | Load all DACs from shift register.                                                                                                     |

| Х  | 1                  | 0  | 0  | *****           | Х | No operation (NOP)                                                                                                                     |

| 0  | Х                  | 1  | 0  | XXXXXXXXXXXXX   | 1 | Update all DACs from their respective input registers.                                                                                 |

| 1  | 1                  | 1  | 0  | *****           | x | Mode 1 (default condition at power-up), DOUT clocked out on SCK's rising edge. All DACs updated from their respective input registers. |

| 1  | 0                  | 1  | 0  | *****           | х | Mode 0, DOUT clocked out on SCK's falling edge. All DACs updated from their respective input registers.                                |

| 0  | 0                  | Х  | 1  | 12-bit DAC data | 0 | Load DAC A input register; DAC A is immediately updated.                                                                               |

| 0  | 1                  | Х  | 1  | 12-bit DAC data | 0 | Load DAC B input register; DAC B is immediately updated.                                                                               |

| 1  | 0                  | Х  | 1  | 12-bit DAC data | 0 | Load DAC C input register; DAC C is immediately updated.                                                                               |

| 1  | 1                  | Х  | 1  | 12-bit DAC data | 0 | Load DAC D input register; DAC D is immediately updated.                                                                               |

## Table 1. Serial-Interface Programming Commands

"X" = Don't Care. LDAC provides true latch control: when LDAC is low, the DAC registers are transparent; when LDAC is high, the DAC registers are latched.

When daisy-chaining MAX536s, the delay from  $\overline{CS}$  low to SCK high (t<sub>CSS</sub>) must be the greater of:

#### tDV + tDS or

#### ttr + trc + tds - tcsw

where  $t_{RC}$  is the time constant of the external pullup resistor (R<sub>p</sub>) and the load capacitance (C) at SDO. For  $t_{RC}$  < 20ns,  $t_{CSS}$  is simply  $t_{DV}$  +  $t_{DS}$ . Calculate  $t_{RC}$  from the following equation:

$$t_{RC} = R_{p}(C) \left[ ln \left( \frac{V_{PULLUP}}{V_{PULLUP} - 2.4V} \right) \right]$$

where  $V_{\mbox{PULLUP}}$  is the voltage to which the pullup resistor is connected.

Additionally, when daisy-chaining devices, the maximum clock frequency is limited to:

$$f_{SCK}(max) = \frac{1}{2(t_{DO} + t_{RC} - 38ns + t_{DS})}$$

For example, with t\_RC = 23ns (5V  $\pm 10\%$  supply with R\_p = 1k\Omega and C = 30pF), the maximum clock frequency is 8.7MHz.

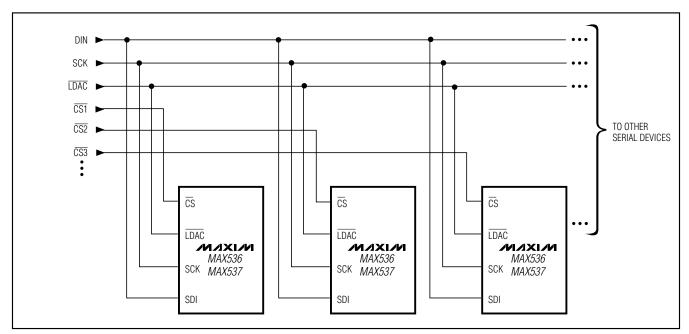

Figure 9 shows an alternate method of connecting several MAX536/MAX537s. In this configuration, the data bus is common to all devices; data is not shifted through a daisy-chain. More I/O lines are required in this configuration because a dedicated chip-select input ( $\overline{CS}$ ) is required for each IC.

Figure 8. Daisy-Chaining MAX536/MAX537s with a 3-Wire Serial Interface

Figure 9. Multiple devices sharing a common DIN line may be simultaneously updated by bringing LDAC low. CS1, CS2, CS3... are driven separately, thus controlling which data are written to devices 1, 2, 3...

# MAX536/MAX537

## **Applications Information**

#### Interfacing to the M68HC11\*

PORT D of the 68HC11 supports SPI. The four registers used for SPI operation are the Serial Peripheral Control Register, the Serial Peripheral Status Register, the Serial Peripheral Data I/O Register, and PORT D's Data Direction Register. These registers have a default starting location of \$1000.

On reset, the PORT D register (memory location \$1008) is cleared and bits 5-0 are configured as general-purpose inputs. Setting bit 6 (SPE) of the Serial Peripheral Control Register (SPCR) configures PORT D for SPI as follows:

| BIT | •  |    |     |      |      |     |     |  |

|-----|----|----|-----|------|------|-----|-----|--|

| 7   | 6  | 5  | 4   | 3    | 2    | 1   | 0   |  |

| NA  | ME |    |     |      |      |     |     |  |

| -   | -  | SS | SCK | MOSI | MISO | TXD | RXD |  |

Bits 6 and 7 are not used. Writes to these bits are ignored.

The PORT D Data Direction Register (DDRD) determines whether the port bits are inputs or outputs. Its configuration is shown below:

| BIT  |      |      |      |      |      |      |  |

|------|------|------|------|------|------|------|--|

| 7 6  | 5    | 4    | 3    | 2    | 1    | 0    |  |

| NAME |      |      |      |      |      |      |  |

|      | DDD5 | DDD4 | DDD3 | DDD2 | DDD1 | DDD0 |  |

Setting DDD\_ = 0 configures the port bit as an input, while setting DDD\_ = 1 configures the port bit as an output. Writes to bits 6 and 7 have no effect.

In SPI mode with MSTR = 1, when a PORT D bit is expected to be an input ( $\overline{SS}$ , MISO, RXD), the corresponding DDRD bit (DDD\_) is ignored. If the bit is expected to be an output (SCK, MOSI, TXD), the corresponding DDRD bit must be set for the bit to be an output.

## Table 2. Serial Peripheral Control-Register Definitions

| NAME   |                                                                                                                                          |                                                                                                                                                                                                                                                                                                  | DEFINITION             |  |  |  |  |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|--|--|--|--|--|--|

| SPIE   | determine                                                                                                                                | Serial Peripheral Interrupt Enable. Clearing SPIE disables the SPI hardware-interrupt request; the SPSR is polled to<br>determine when an SPI data transfer is complete. Setting SPIE requests a hardware interrupt when the Serial Peripheral<br>Status Register's SPIF bit or MODF bit is set. |                        |  |  |  |  |  |  |  |  |

| SPE    | 0                                                                                                                                        | etting SPE (Serial Peripheral System Enable) configures PORT D for SPI. Clearing SPE configures the port as a general-<br>urpose I/O port.                                                                                                                                                       |                        |  |  |  |  |  |  |  |  |

| DWOM   | When DWOM is set, the six PORT D outputs are open drain. When DWOM is cleared, the outputs are complementary                             |                                                                                                                                                                                                                                                                                                  |                        |  |  |  |  |  |  |  |  |

| MSTR   | Master/Slave select option                                                                                                               |                                                                                                                                                                                                                                                                                                  |                        |  |  |  |  |  |  |  |  |

| CPOL   | Determines clock polarity. When set, the serial clock idles high while data is not being transferred; when cleared, the clock idles low. |                                                                                                                                                                                                                                                                                                  |                        |  |  |  |  |  |  |  |  |

| CPHA   | Determine                                                                                                                                | s the clock                                                                                                                                                                                                                                                                                      | phase.                 |  |  |  |  |  |  |  |  |

|        | SPI Clock-Rate Select                                                                                                                    |                                                                                                                                                                                                                                                                                                  |                        |  |  |  |  |  |  |  |  |

|        | SPR1                                                                                                                                     | SPR0                                                                                                                                                                                                                                                                                             |                        |  |  |  |  |  |  |  |  |

| SPR1/0 | 0                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                | μP clock divided by 2  |  |  |  |  |  |  |  |  |

| 3FR1/0 | 0                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                | μP clock divided by 4  |  |  |  |  |  |  |  |  |

|        | 1                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                | μP clock divided by 16 |  |  |  |  |  |  |  |  |

|        | 1                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                | μP clock divided by 32 |  |  |  |  |  |  |  |  |

## Table 3. Serial Peripheral Status-Register Definitions

| NAME                                                                                                                 | DEFINITION                                                                                                                                                                                                                    |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| SPIF SPIF is set when an SPI data transfer is complete. It is cleared by reading the SPSR and then accessing the SPI |                                                                                                                                                                                                                               |  |  |  |  |  |  |

| WCOL                                                                                                                 | The Write Collision flag is set when a write to the SPDR occurs while a data transfer is in progress. It is cleared by reading the SPSR and then accessing the SPDR.                                                          |  |  |  |  |  |  |

| MODF                                                                                                                 | The Mode Fault flag detects master/slave conflicts in a multimaster environment. It is set when the "master" controller has its SS line (PORT D) pulled low, and cleared by reading the SPSR followed by a write to the SPCR. |  |  |  |  |  |  |

\*M68HC11 is a Motorola microcontroller. General information about the device was obtained from M68HC11 technical manuals.

Table 4. M68HC11 Programming Code

\* 68HC11 Programming Code for interfacing to the MAX536/MAX537 DACs. Data for the MAX536/MAX537 is stored in memory locations \$0100 and \$0101. Release Date February 24, 1994 \* Revision 0 \* Technical support provided by Motorola \* Additional assistance provided by Diane Scott \* 68HC11 Code Instruction EQU \$0000 ; Memory location for beginning of program STRT REGBLK EQU \$1000 ; Starting address for 68HC11 register block \* The following registers will be addressed relative to the start of the \* register block (REGBLK) using indexed addressing mode. \* The effective address = contents of Index Register X + offset. PORTD EQU \$08 ; PORT D memory location ; PORT D Data Direction Register memory location DDRD EQU \$09 SPCR EQU \$28 ; SPCR memory location SPSR EQU \$29 ; SPSR memory location SPDR EQU \$2A ; SPDR memory location \* Start of main program ORG STRT MAIN LDAA #\$74 ; an arbitrary MAX536/MAX537 DAC code (load input ; register B with 1/4 of full-scale value: all DAC STAA \$0100 ; registers updated) is loaded into data memory LDAA #\$00 STAA \$0101 ; locations \$0100 and \$0101. LDX #REGBLK ; load Index Register X with starting address of register block LDAA #\$38 ; SPI outputs (SCK, MOSI, and /SS configured as an output) ; configured by setting the Data Direction Register bits STAA DDRD,X ; load data into the Data Direction Register LDAA #\$2F ; set /SS and MOSI high; set SCK low ; load data into PORTD to set-up SPI control lines STAA PORTD,X ; set data for SPCR LDAA #\$51 ; load data into the SPCR STAA SPCR,X BCLR PORTD,X \$20 ; bring /CS low ; load high byte of digital data into Accumulator(A) LDAA \$0100 ; load high byte of MAX536/MAX537 data into SPDR STAA SPDR,X LDAA SPSR,X ; beginning of loop to poll the SPSR WAIT1 BITA #\$80 ; mask all bits except SPIF (transfer complete) flag WAIT1 ; branch if SPIF is not set to beginning of loop BEQ LDAA \$0101 ; load low byte of digital data into Accumulator(A) ; load low byte of MAX536/MAX537 data into SPDR SPDR,X STAA WAIT2 LDAA SPSR,X ; beginning of loop to poll the SPSR ; mask all bits except SPIF (transfer complete) flag BITA #\$80 BEQ WAIT2 ; branch if SPIF is not set to beginning of loop LDAA SPDR,X LDAA SPDR,X ; read the SPDR to clear the SPIF bit in the SPSR BSET PORTD,X \$20 ; bring /CS high to latch data into the MAX536/MAX537 \* The MAX536/MAX537 is now configured to have  $V_{OUTB} = V_{REF}$  (1024/4096)

MAX536/MAX537

SS is an input intended for use in a multimaster environment. However, SS or unused PORT D bit RXD, TXD, or possibly MISO (if DAC readback is not used) should be configured as a general-purpose output and used as CS by setting the appropriate Data Direction Register bit.

The SPCR configuration (memory location \$1028) is shown below:

| <b>BIT</b><br>7 6 | 5     | 4      | 3       | 2    | 1      | 0    |

|-------------------|-------|--------|---------|------|--------|------|

| NAME<br>SPIE SPE  | DWOM  | MSTR   | CPOL    | СРНА | SPR1   | SPR0 |

| SETTING           | AFTE  | R RESE | ET      |      |        |      |

| 0 0               | 0     | 0      | 0       | 1    | U*     | U*   |

| SETTING           | FOR T | YPICA  | L SPI ( | СОММ | JNICAT | ION  |

| 0 1               | 0     | 1      | 0       | 0    | 0**    | 1**  |

\*U = Unknown

\*\*Depends on µP clock frequency.

Always configure the 68HC11 as the "master" controller and the MAX536/MAX537 as the "slave" device.

When MSTR = 1 in the SPCR, a write to the Serial Peripheral Data I/O Register (SPDR), located at memory location \$102A, initiates the transmission/reception of data. The data transfer is monitored and the appropriate flags are set in the Serial Peripheral Status Register (SPSR).

The SPSR configuration is shown below:

| BIT              |                    |   |      |   |   |   |   |  |

|------------------|--------------------|---|------|---|---|---|---|--|

| 7                | 6                  | 5 | 4    | 3 | 2 | 1 | 0 |  |

| NAN<br>SPIF      | I <b>E</b><br>WCOL | _ | MODF | _ | _ | _ | _ |  |

| RESET CONDITIONS |                    |   |      |   |   |   |   |  |

| 0                | 0                  | 0 | 0    | 0 | 0 | 0 | 0 |  |

An example of 68HC11 programming code for a two-byte SPI transfer to the MAX536/MAX537 is given in Table 4. SS is used for  $\overline{CS}$ , the high byte of MAX536/MAX537 digital data is stored in memory location \$0100, and the low byte is stored in memory location \$0101.

#### Interfacing to Other Controllers

When using MICROWIRE, refer to the section on *Interfacing to the M68HC11* for guidance, since MICROWIRE can be considered similar to SPI when CPOL = 0 and CPHA = 0. When interfacing to Intel's 80C51/80C31 microcontroller family, use bit-pushing to configure a desired port as the MAX536/MAX537 interface port. Bitpushing involves arbitrarily assigning I/O port bits as interface control lines, and then writing to the port each time a signal transition is required.

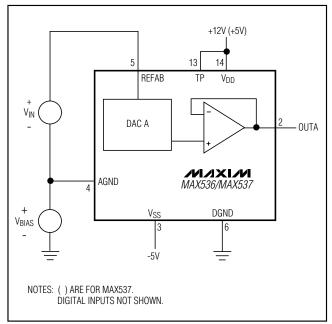

#### **Unipolar Output**

For a unipolar output, the output voltages and the reference inputs are the same polarity. Figure 10 shows the MAX536/MAX537 unipolar output circuit, which is also the typical operating circuit. Table 5 lists the unipolar output codes.

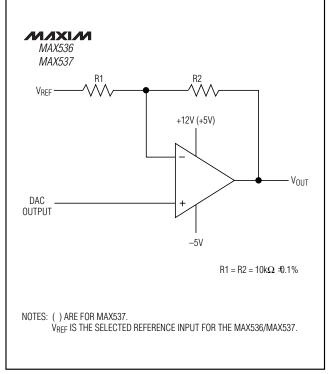

#### **Bipolar Output**

The MAX536/MAX537 outputs can be configured for bipolar operation using Figure 11's circuit. One op amp and two resistors are required per DAC. With R1 = R2:

$$V_{OUT} = V_{REF} [(2N_B/4096) - 1]$$

where  $N_B$  is the numeric value of the DAC's binary input code. Table 6 shows digital codes and corresponding output voltages for Figure 11's circuit.

#### Table 5. Unipolar Code Table

| DAC<br>MSB | CONTEN | NTS<br>LSB | ANALOG OUTPUT                                                      |

|------------|--------|------------|--------------------------------------------------------------------|

| 1111       | 1111   | 1111       | +V <sub>REF</sub> ( <u>4095</u> )                                  |

| 1000       | 0000   | 0001       | +V <sub>REF</sub> ( <u>2049</u> )                                  |