# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

19-2226; Rev 1; 7/04

EVALUATION KIT AVAILABLE

#

## **Temperature Sensor and** System Monitor in a 10-Pin µMAX

Monitors Local Temperature

Monitors Vcc (3.3V Nominal)

Alert Response Address

Tiny 10-Pin µMAX Package

MAX6683EVKIT Available

+2.7V to +5.5V Supply Range

♦ -40°C to +125°C Temperature Range

♦ 60Hz or 50Hz Line-Frequency Rejection

User-Programmable Voltage and Temperature

Alert Function with Ability to Respond to SMB

Nominal)

Thresholds

## **General Description**

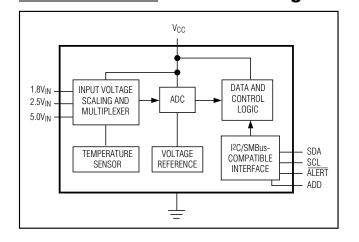

The MAX6683 system supervisor monitors multiple power-supply voltages, including its own, and also features an on-board temperature sensor. The MAX6683 converts voltages to an 8-bit code and temperatures to an 11-bit (10-bit-plus-sign) code using an analog-todigital converter (ADC). A multiplexer automatically sequences through the voltage and temperature measurements. The digitized signals are then stored in registers and compared to the over/underthreshold limits programmed over the SMBus<sup>™</sup>/l<sup>2</sup>C<sup>™</sup>-compatible 2wire serial interface.

When a temperature measurement exceeds the programmed threshold, or when an input voltage falls outside the programmed voltage limits, the MAX6683 generates a latched interrupt output ALERT. Three interrupt modes are available for temperature excursions. These are default mode, one-time interrupt mode, and comparator mode. The ALERT output is cleared, except for temperature interrupts generated in comparator mode, by reading the Interrupt Status register (Table 5). The ALERT output can also be masked by writing to the appropriate bits in the Interrupt Mask register (Table 6) or by setting bit 1 of the Configuration register (Table 4) to zero. The MAX6683 SMBus/I<sup>2</sup>Ccompatible interface also responds to the SMB alert response address.

### **Applications**

Workstations

Servers

Networking

Telecommunications

##

**Ordering Information**

| PART       | TEMP RANGE      | PIN-PACKAGE |

|------------|-----------------|-------------|

| MAX6683AUB | -40°C to +125°C | 10 µMAX     |

### **Pin Configuration**

SMBus is a trademark of Intel Corp. I<sup>2</sup>C is a trademark of Philips Corp.

Maxim Integrated Products 1

Features **MAX6683** Monitors Three External Voltages (1.8V, 2.5V, 5V

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

All Voltages Referenced to GND

| All Pins.                                             | 0.3V to +6.0V |

|-------------------------------------------------------|---------------|

| SDA, ALERT Current                                    | 1mA to +50mA  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |               |

| 10-Pin µMAX (derate 5.6mW/°C above +70°               | C)444mW       |

| Junction Temperature              | +150°C         |

|-----------------------------------|----------------|

| Operating Temperature Range       | 40°C to +125°C |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

| /7    |                                          | Cumpless steemwise meter                   | Tuning Luglugg are at V/ | $CC = +3.3V, T_A = +25^{\circ}C.$                            |

|-------|------------------------------------------|--------------------------------------------|--------------------------|--------------------------------------------------------------|

| ( )   | $\Lambda = -40^{-1}(10) + 125^{-1}(10)$  | <ul> <li>Unless otherwise holed</li> </ul> | TVOICAL VALUES ARE AL VO | $10^{\circ} = \pm 3.3^{\circ} = \pm 23^{\circ} = 10^{\circ}$ |

| · · · | A = 100000000000000000000000000000000000 |                                            | i ypiour vuluoo uro ur v | 50 - 1000, $1A - 120$                                        |

| PARAMETER                    | SYMBOL          | CONDITIONS                                                 | MIN | TYP   | MAX   | UNITS |

|------------------------------|-----------------|------------------------------------------------------------|-----|-------|-------|-------|

| POWER SUPPLY                 |                 |                                                            |     |       |       |       |

| Supply Voltage               | V <sub>CC</sub> |                                                            | 2.7 |       | 5.5   | V     |

| Quere la Quere et            | ICC             | Operating                                                  |     | 200   | 500   |       |

| Supply Current               | I <sub>SD</sub> | Shutdown mode, interface inactive                          |     |       | 10    | μA    |

| Power-On Reset (POR) Voltage |                 | V <sub>CC</sub> , rising or falling edge                   |     | 2     |       | V     |

| TEMPERATURE                  |                 |                                                            |     |       |       |       |

|                              |                 | $T_A = +25^{\circ}C, V_{CC} = +3.3V$                       |     |       | ±3    |       |

| Accuracy                     |                 | $0^{\circ}C \le T_{A} \le +125^{\circ}C, V_{CC} = +3.3V$   |     |       | ±4    | °C    |

|                              |                 | $-40^{\circ}C \le T_A \le +125^{\circ}C, V_{CC} = +3.3V$   |     |       | ±6    |       |

| Resolution                   |                 | Read word mode                                             |     | 0.125 |       | °C    |

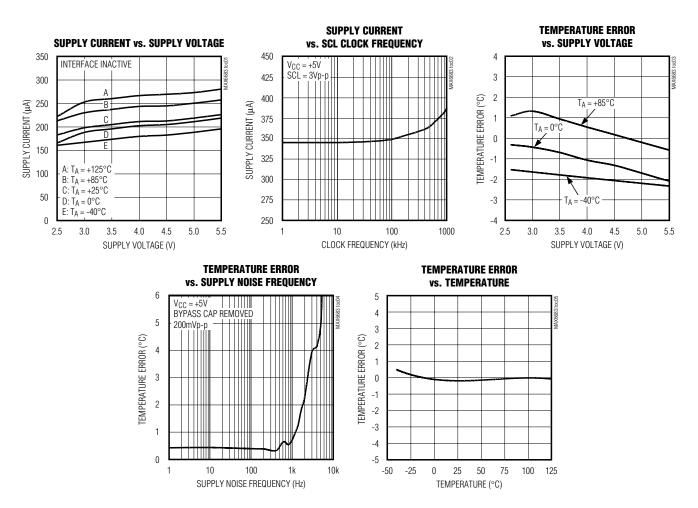

| Supply Sensitivity           | PSS             |                                                            |     | 0.7   | ±1.5  | °C/V  |

| ADC CHARACTERISTICS          |                 |                                                            |     |       |       |       |

| Total Unadjusted Error       | TUE             | V <sub>IN</sub> > 10LSBs                                   |     |       | ±1.5  | %     |

| Differential Nonlinearity    | DNL             | V <sub>IN</sub> > 10LSBs                                   |     |       | ±1    | LSB   |

| Supply Sensitivity           | PSS             |                                                            |     | ±1    |       | LSB/V |

| Input Resistance             | RIN             | 1.8V <sub>IN</sub> , 2.5V <sub>IN</sub> , 5V <sub>IN</sub> | 100 | 150   | 200   | kΩ    |

| Total Monitoring Cycle Time  | t <sub>c</sub>  | (Note 1)                                                   |     | 200   | 300   | ms    |

| SCL, SDA, ADD                |                 |                                                            |     |       |       |       |

| Logic Input Low Voltage      | VIL             |                                                            |     |       | 0.8   | V     |

|                              | N               | $V_{CC} \le 3.6V$                                          | 2.0 |       |       | N     |

| Logic Input High Voltage     | VIH             | V <sub>CC</sub> > 3.6V                                     | 2.6 |       |       | V     |

| Input Leakage Current        | ILEAK           | $V_{IN} = 0 \text{ or } 5V$                                |     |       | ±1    | μA    |

| Output Low Voltage           | Vol             | I <sub>SINK</sub> = 3mA                                    |     |       | 400   | mV    |

| ALERT                        |                 |                                                            | •   |       |       |       |

|                              |                 | $I_{SINK} = 1.2 mA, V_{CC} > 2.7 V$                        |     |       | 0.3   | V     |

| Output Low Voltage           | Vola            | $I_{SINK} = 3.2 \text{mA}, V_{CC} > 4.5 \text{V}$          |     |       | 0.4 V |       |

## **ELECTRICAL CHARACTERISTICS (continued)**

(T<sub>A</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = +3.3V, T<sub>A</sub> = +25°C.)

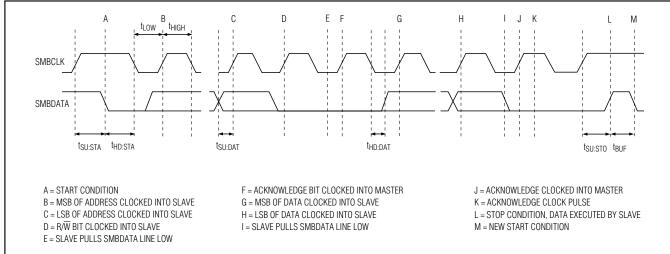

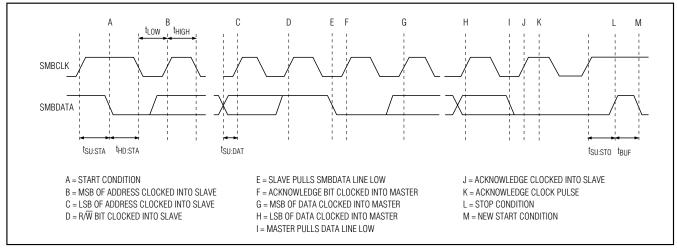

| PARAMETER                                                    | SYMBOL                   | CONDITIONS                        | MIN                       | ТҮР                       | MAX | UNITS |  |

|--------------------------------------------------------------|--------------------------|-----------------------------------|---------------------------|---------------------------|-----|-------|--|

| TIMING (Figures 3 and 4)                                     | FIMING (Figures 3 and 4) |                                   |                           |                           |     |       |  |

| Serial Clock Frequency                                       | fscl                     |                                   | 0                         |                           | 400 | kHz   |  |

| Bus Free Time Between Stop<br>and Start                      | T <sub>BUF</sub>         |                                   | 1.3                       |                           |     | μs    |  |

| Start Condition Hold Time                                    | thd:sta                  |                                   | 0.6                       |                           |     | μs    |  |

| Stop Condition Hold Time                                     | tsu:sto                  |                                   | 0.6                       |                           |     | μs    |  |

| Clock Low Time                                               | TLOW                     |                                   | 1.3                       |                           |     | μs    |  |

| Clock High Time                                              | THIGH                    |                                   | 0.6                       |                           |     | μs    |  |

| Data Setup Time                                              | tsu:dat                  |                                   | 100                       |                           |     | ns    |  |

| Data Hold Time                                               | thd:dat                  | (Note 2)                          | 0                         |                           | 0.9 | μs    |  |

| Receive SCL/SDA Minimum<br>Rise Time                         |                          | (Note 3)                          |                           | 20 +<br>0.1C <sub>b</sub> |     | ns    |  |

| Receive SCL/SDA Maximum<br>Rise Time t <sub>R</sub> (Note 3) |                          | (Note 3)                          |                           | 300                       |     | ns    |  |

| Receive SCL/SDA Minimum Fall t <sub>F</sub>                  |                          | (Note 3)                          |                           | 20 +<br>0.1C <sub>b</sub> |     | ns    |  |

| Receive SCL/SDA Maximum Fall<br>Time                         |                          | (Note 3)                          |                           | 300                       |     | ns    |  |

| Transmit SDA Fall Time $t_F$ $C_b$ = 400pF, $I_{SINK}$ = 3mA |                          | $C_b = 400 pF$ , $I_{SINK} = 3mA$ | 20 +<br>0.1C <sub>b</sub> |                           | 300 | ns    |  |

| Pulse Width of Spike<br>Suppressed                           |                          | (Note 4)                          |                           | 50                        |     | ns    |  |

Note 1: Total monitoring time includes temperature conversion and four analog input voltage conversions.

Note 2: A master device must provide at least a 300ns hold time for the SDA signal, referred to V<sub>IL</sub> of the SCL signal, to bridge the undefined region of SCL's falling edge.

**Note 3:**  $C_b$  = total capacitance of one bus line in pF. Rise and fall times are measured between  $0.3 \times V_{CC}$  to  $0.7 \times V_{CC}$ .

**Note 4:** Input filters on SDA, SCL, and ADD suppress noise spikes <50ns.

$(V_{CC} = +3.3V, ADD = GND, T_A = +25^{\circ}C, unless otherwise noted.)$

#### \_Typical Operating Characteristics

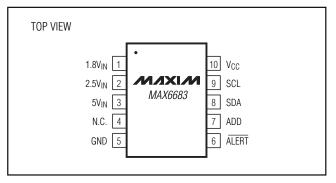

### **Pin Description**

| PIN | NAME               | FUNCTION                                                                                                                                                                                                                                                 |

|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 1.8V <sub>IN</sub> | Analog Input. Monitors 1.8V nominal supply.                                                                                                                                                                                                              |

| 2   | $2.5V_{IN}$        | Analog Input. Monitors 2.5V nominal supply.                                                                                                                                                                                                              |

| 3   | 5V <sub>IN</sub>   | Analog Input. Monitors 5V nominal supply.                                                                                                                                                                                                                |

| 4   | N.C.               | No Connect. Not internally connected. Connect to GND to improve thermal conductivity.                                                                                                                                                                    |

| 5   | GND                | Ground                                                                                                                                                                                                                                                   |

| 6   | ALERT              | SMBus Alert (Interrupt) Output, Open Drain. Alerts the master that a temperature or voltage limit has been violated.                                                                                                                                     |

| 7   | ADD                | SMBus/I <sup>2</sup> C-Compatible Address Select Input. ADD is sampled at the beginning of each SMBus/I <sup>2</sup> C transaction, and the 2LSBs of the Slave Address register are detemined by ADD's connection to GND, SDA, SCL, or V <sub>CC</sub> . |

| 8   | SDA                | SMBus/I <sup>2</sup> C-Compatible Serial Data Interface                                                                                                                                                                                                  |

| 9   | SCL                | SMBus/I <sup>2</sup> C-Compatible Clock Input                                                                                                                                                                                                            |

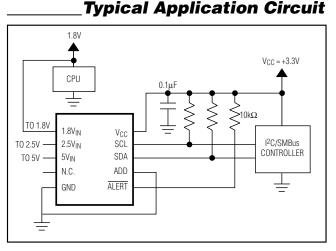

| 10  | V <sub>CC</sub>    | Supply Voltage Input, +2.7V to +5.5V. Also serves as a voltage monitor input. Bypass $V_{CC}$ to GND with a 0.1µF capacitor.                                                                                                                             |

## **Detailed Description**

The MAX6683 is a voltage and temperature monitor designed to communicate through an SMBus/I<sup>2</sup>C interface with an external microcontroller ( $\mu$ C). A  $\mu$ C with no built-in I<sup>2</sup>C or SMBus capabilities can generate SMBus serial commands by "bit-banging" general-purpose input-output (GPIO) pins.

The MAX6683 can monitor external supply voltages of typically 1.8V, 2.5V, 5V, as well as its own supply voltage and temperature. This makes it ideal for supervisor and thermal management applications in telecommunications, desktop and notebook computers, workstations, and networking equipment. Voltage inputs are converted to an 8-bit code and temperature is converted to an 11-bit code. The high-order 8 bits of the temperature conversion can be read using a read byte operation through the I<sup>2</sup>C interface. The full 11-bit temperature conversion is read using a read word operation and disregarding the lower 5 bits of the low byte. By setting bit 5 of the Configuration Register to 1, the temperature conversion can be reduced to 9 bits with a four-fold reduction in conversion time. In this case, the lower 7 bits of the low byte should be disregarded; 8bit temperature data has a resolution of 1°C/LSB, while 11-bit temperature data has a resolution of 0.125°C/ LSB. Setting bit 5 of the Configuration Register to 1 reduces the monitoring cycle time by a factor of 4. In this case, a read word operation for temperature data yields a 9-bit code in which the lower 7 bits of the low byte should be disregarded. The LSB of the 9-bit temperature data has a value of 0.5°C.

Each input voltage is scaled down by an on-chip resistive voltage-divider so that its output, at the nominal input voltage, is 3/4 of the ADC's full-scale range, or a decimal count of 192 (Table 3). Input voltages other than the nominal values may be used; ensure that they fall within the usable ranges of pins to which they are applied. Attenuate voltages greater than 6V with an external resistive voltage-divider.

Writing a 1 to bit 0 of the Configuration Register starts the monitoring function. The device performs a sequential sampling of all the inputs, starting with the internal temperature sensor and continuing with 2.5V<sub>IN</sub>, 1.8V<sub>IN</sub>, 5V<sub>IN</sub>, and V<sub>CC</sub>. If the master terminates the conversion, the sequential sampling does not stop until the sampling cycle is completed and the results are stored. When it starts again, it always starts with the temperature measurement.

An interrupt signal is generated when a temperature measurement goes above the hot limit or when a voltage measurement is either above the high limit or below the low limit. This causes the open-drain output ALERT to go to the active-low state and set each corresponding interrupt status bit (bits 0 through 4) to 1 (Table 5). The interrupt is cleared by reading the Interrupt Status Register except for temperature interrupts generated in comparator mode. Reading the Interrupt Status Register also clears the register itself, except for temperature interrupt bits set in comparator mode.

## Table 1. Register Map

| ADDRESS | READ/WRITE | POWER-ON DEFAULT       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------|------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 20h     | R          | _                      | Data register for 2.5 V <sub>IN</sub> measurement                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 21h     | R          | _                      | Data register for 1.8VIN measurement                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 22h     | R          | _                      | Data register for 5VIN measurement                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 23h     | R          | _                      | Data register for V <sub>CC</sub> measurement                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 27h     | R          | _                      | Data register for temperature measurement                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 2Bh     | R/W        | 1101 0011 (1.1 × 2.5V) | High limit for 2.5V <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 2Ch     | R/W        | 1010 1101 (0.9 × 2.5V) | Low limit for 2.5V <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 2Dh     | R/W        | 1101 0011 (1.1 × 1.8V) | High limit for 1.8V <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 2Eh     | R/W        | 1010 1101 (0.9 × 1.8V) | Low limit for 1.8VIN                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 2Fh     | R/W        | 1101 0011 (1.1 × 5V)   | High limit for 5V <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 30h     | R/W        | 1010 1101 (0.9 × 5V)   | Low limit for 5V <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 31h     | R/W        | 1101 0011 (1.1 × 3.3V) | High limit for V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 32h     | R/W        | 1010 1101 (0.9 × 3.3V) | Low limit for V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 39h     | R/W        | 0101 0000 (+80°C)      | Hot temperature limit                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 3Ah     | R/W        | 0100 0001 (+65°C)      | Hot temperature hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 40h     | R/W        | 0000 1000              | Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 41h     | R          | 0000 0000              | Interrupt Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 43h     | R/W        | 0000 0000              | Interrupt Mask Register                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 48h     | R/W        | 0010 1XXY              | Device Address Register. The values of XX are dependent on the status of the ADD pin.         Power-On Default       ADD Connection         0010       100Y       To GND         0010       101Y       To VCC         0010       110Y       To SDA         0010       111Y       To SCL         Y (bit 0) is the SMBus read/write bit. When the 7-bit chip address is read back from the Serial Address Register, an 8-bit word is presented with a zero in bit 0 (Y). |  |

| 4Bh     | R/W        | 0000 0000              | Temperature Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

Unless the fault is removed, the ALERT output only remains cleared until the end of the next conversion cycle where it is again asserted. The ALERT output can also be masked by writing to the appropriate bits in the Interrupt Mask Register (Table 6) or by setting bit 1 of the Configuration Register (Table 4) to zero.

The 2-wire serial interface accepts both  $I^2C$  and standard SMBus Write Byte, Read Byte, Read Word, Send Byte, and Receive Byte commands to program the alarm thresholds and to read voltage and temperature data. Voltage data is scaled so that when the nominal voltage is present at an input (e.g., 1.8V for the 1.8V<sub>IN</sub> input), the conversion result is equal to 3/4 of the ADC full-scale range or a decimal count of 192 (Table 1). When using the Read Byte command, the temperature data format is 7 bits plus sign with the LSB equal to 1°C, in two's complement format. When using the Read Word command, the temperature data format is 10 bits plus sign, with the LSB equal to 0.125°C, in two's complement format. See Table 2 for the temperature data format.

The MAX6683 has only one address input, ADD. Connect ADD to GND,  $V_{CC}$ , SDA, or SCL to select one of four different address codes. Whenever an SMBus/I<sup>2</sup>C transaction is initiated, the 2LSBs of the Slave Address Register are determined by connection, setting the chip address to one of four possible values. In addition, an address code can also be directly writ-

# Table 2. Temperature Data Format(Two's Complement)

| HIGH BYTE           |                            |                         |

|---------------------|----------------------------|-------------------------|

| TEMPERATURE<br>(°C) | DIGITAL OUTPUT<br>(BINARY) | DIGITAL OUTPUT<br>(HEX) |

| +125                | 0111 1101                  | 7D                      |

| +25                 | 0001 1001                  | 19                      |

| +1                  | 0000 0001                  | 01                      |

| 0                   | 0000 0000                  | 00                      |

| -1                  | 1111 1111                  | FF                      |

| -25                 | 1110 0111                  | E7                      |

| -40                 | 1101 1000                  | D8                      |

| LOW BYTE            |                            |                         |

| 0.875               | 1110 0000                  | D0                      |

| 0.125               | 0010 0000                  | 20                      |

ten to the Serial Address Register. This code overwrites the code set by connection of the ADD pin, until the MAX6683 is taken through a POR cycle.

#### **ADC and Multiplexer**

The ADC integrates over a 66ms period, an integral multiple of the line period with excellent noise rejection. The internal oscillator is trimmed to produce a 66ms conversion time for temperature and 33ms for each voltage. This is equivalent to 4 and 2 cycles of 60Hz, respectively, and provides protection against noise pickup from the main supply. The internal oscillator frequency can be changed to provide the same protection against 50Hz by setting bit 7 in the Configuration Register to 1 (Table 4). The multiplexer automatically sequences through the inputs, measuring voltages and temperature.

#### Low-Power Shutdown Mode

Setting bit 0 in the Configuration Register to zero stops the monitoring loop and puts the MAX6683 into low-power shutdown mode. In this mode, the SMBus/l<sup>2</sup>C interface remains active, and the supply current drops to  $10\mu$ A or less.

#### **Power-On Reset**

**MAX6683**

The MAX6683 POR supply voltage is typically 2V. Below this supply voltage, all registers are reset, the device is put into shutdown mode, and the SMBus/I<sup>2</sup>C interface is inactive.

#### **Alarm Threshold Registers**

Two registers, a hot temperature limit ( $T_{HOT}$ ) at 39h and a hot temperature hysteresis ( $T_{HYST}$ ) at 3Ah, store alarm threshold data (Table 1). If a measured temperature exceeds the value of  $T_{HOT}$ , an ALERT is asserted. Alerts are cleared and reasserted depending on the interrupt mode selected in the Temperature Configuration Register (see ALERT Interrupts).

| ADC OUTPUT<br>CODE | INPUT VOLTAGE<br>AT 1.8V <sub>IN</sub> | INPUT VOLTAGE<br>AT 2.5V <sub>IN</sub> | INPUT VOLTAGE<br>AT 5V <sub>IN</sub> | V <sub>CC</sub> = +3.3V |

|--------------------|----------------------------------------|----------------------------------------|--------------------------------------|-------------------------|

| LSB weight         | 9.375mV (1.8V/192)                     | 13mV (2.5V/192)                        | 26mV (5V/192)                        | 17.2mV (3.3V/192)       |

| 0                  | < 9.375mV                              | < 13mV                                 | < 26mV                               | —                       |

| 1                  | 9.375mV to 18.75mV                     | 13mV to 26mV                           | 26mV to 52mV                         | —                       |

| 2                  | 18.75mV to 28.125mV                    | 26mV to 39mV                           | 52mV to 78mV                         | _                       |

|                    | —                                      | _                                      | —                                    | —                       |

| 64 (1/4 scale)     | 600mV to 609.4mV                       | 833mV to 846mV                         | 1.664V to 1.692V                     | —                       |

| —                  | —                                      | _                                      | —                                    | —                       |

| 128 (1/2 scale)    | 1.2V to 1.2094V                        | 1.667V to 1.680V                       | 3.330V to 3.560V                     | —                       |

| —                  | —                                      | _                                      | —                                    | —                       |

| 192 (3/4 scale)    | 1.8V to 1.737V                         | 2.5V to 2.513V                         | 5V to 5.026V                         | 3.3V to 3.317V          |

| —                  | —                                      | _                                      | —                                    | —                       |

| 253                | 2.372V to 2.381V                       | 3.294V to 3.307V                       | 6.566V to 6.640V                     | 4.348V to 4.366V        |

| 254                | 2.381V to 2.391V                       | 3.572V to 3.586V                       | 6.615V to 6.640V                     | 4.366V to 4.383V        |

| 255                | = 2.391V                               | = 3.586V                               | = 6.640V                             | = 4.383V                |

### Table 3. Voltage Data Format

## Table 4. Configuration Register (Address 40h, Power-On Default = 08h)

| BIT | NAME                     | READ/WRITE | DESCRIPTION                                                                                                                                                                                                                                                                                                                       |

|-----|--------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Start/Stop               | R/W        | This bit controls the monitoring loop. Setting the bit to zero stops the monitoring loop and puts the device into shutdown mode. The I <sup>2</sup> C/SMBus interface is still active during the shutdown mode. Setting the bit to 1 starts the monitoring cycle. All high/low limits should be set before setting this bit to 1. |

| 1   | ALERT Enable             | R/W        | This bit is used to enable or disable the $\overline{\text{ALERT}}$ output. Setting the bit to 1 enables the $\overline{\text{ALERT}}$ output; setting the bit to 0 disables the $\overline{\text{ALERT}}$ output.                                                                                                                |

| 2   | Reserved                 | —          | —                                                                                                                                                                                                                                                                                                                                 |

| 3   | ALERT Clear              | R/W        | This bit is used to clear the ALERT output when it is set to high. It does not affect the Interrupt Status Register. The monitoring loop does not start until the bit is set to zero.                                                                                                                                             |

| 4   | Line Frequency<br>Select | R/W        | This bit controls the internal clock frequency. Setting the bit to 1 changes the clock frequency to 51.2kHz from 61.4kHz. This can improve the measurement accuracy when the power-line frequency is at 50Hz.                                                                                                                     |

| 5   | Short Cycle              | R/W        | This bit reduces the conversion time by a factor of 4 when it is set to 1.                                                                                                                                                                                                                                                        |

| 6   | Reserved                 |            | _                                                                                                                                                                                                                                                                                                                                 |

| 7   | Reset                    | R/W        | This bit is used as a reset signal for the register initialization. The 1 of this bit resets all the register values into the power-up default mode, including bit 7 itself.                                                                                                                                                      |

### Table 5. Interrupt Status Register (Address 41h, Power-Up Default = 00h)

| BIT     | NAME                    | READ/WRITE | DESCRIPTION                                                                                                                                                                                                                                                 |

|---------|-------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 2.5VIN-Error            | R          | A 1 indicates either a high or low limit has been exceeded at the $\rm 2.5V_{IN}$ input.                                                                                                                                                                    |

| 1       | 1.8VIN-Error            | R          | A 1 indicates either a high or low limit has been exceeded at the $1.8 V_{\mbox{IN}}$ input.                                                                                                                                                                |

| 2       | 5V <sub>IN</sub> -Error | R          | A 1 indicates either a high or low limit has been exceeded at the $5 V_{\mbox{\scriptsize IN}}$ input.                                                                                                                                                      |

| 3       | V <sub>CC</sub> -Error  | R          | A 1 indicates either a high or low limit has been exceeded at the $V_{\mbox{CC}}$ input.                                                                                                                                                                    |

| 4       | Temp-Error              | R          | A 1 indicates either a high or low limit has been exceeded at the internal temperature sensor. The conditions that generate and clear this bit depend on the temperature interrupt mode selected by bits 0 and 1 in the Temperature Configuration Register. |

| 5, 6, 7 | Reserved                | _          | —                                                                                                                                                                                                                                                           |

The POR state of the T<sub>HOT</sub> register is 0101 0000 or +80°C. The POR state of the T<sub>HYST</sub> register is 0100 0001 or +65°C.

High and low limits for the voltage inputs are stored in registers 2Bh through 32h. If a measured voltage is less than  $V_{LOW}$  or greater than  $V_{HIGH}$ , an  $\overline{ALERT}$  is asserted.

The POR states of the high and low voltage limits are 1.1 and 0.9 times the nominal voltage for each input.

#### **Interrupt Status Byte Functions**

The Interrupt Status Register records temperature or voltage fault conditions whenever a limit is exceeded (Table 5). Bits 0 through 3 correspond to the 2.5V, 1.8V, 5V, and V<sub>CC</sub> voltage inputs and bit 4 corresponds to the temperature. If a threshold has been crossed, the appropriate bit contains a 1. In the default and one-time interrupt modes, reading the status register clears the register until a new out-of-range condition is detected.

### Table 6. Interrupt Mask Register (Address 43h, Power-Up Default = 00h)

| BIT     | NAME     | READ/WRITE | DESCRIPTION                                                                                                                                      |

|---------|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 2.5V     | R/W        | Setting the bit to 1 disables the Interrupt Status Register bit (bit 0) and the $\rm \overline{ALERT}$ output for the 2.5V_{IN} input.           |

| 1       | 1.8V     | R/W        | Setting the bit to 1 disables the Interrupt Status Register bit (bit 1) and the $\overline{\rm ALERT}$ output for the 1.8V_{IN} input.           |

| 2       | 5V       | R/W        | Setting the bit to 1 disables the Interrupt Status Register bit (bit 2) and the $\overline{\text{ALERT}}$ output for the 5V <sub>IN</sub> input. |

| 3       | 3.3V     | R/W        | Setting the bit to 1 disables the Interrupt Status Register bit (bit 3) and the $\overline{\text{ALERT}}$ output for the V_{CC} input.           |

| 4       | Temp.    | R/W        | Setting the bit to 1 disables the Interrupt Status Register bit (bit 4) and the ALERT output for temperature.                                    |

| 5, 6, 7 | Reserved | _          | _                                                                                                                                                |

#### Table 7. Temperature Configuration Register (Address 4Bh, Power-Up Default = 00h)

| BIT  | NAME                                | READ/WRITE | DESCRIPTION                                                                                                                                                        |

|------|-------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0, 1 | Hot Temperature<br>Interrupt Select | R/W        | Bit 1, bit $0 = 00$ : Default mode<br>Bit 1, bit $0 = 01$ : One-time interrupt mode<br>Bit 1, bit $0 = 10$ : Comparator mode<br>Bit 1, bit $0 = 11$ : Default mode |

| 2–7  | Reserved                            |            | _                                                                                                                                                                  |

#### **ALERT** Interrupts

An out-of-range voltage or temperature causes the ALERT output signal to be asserted. However, if the assertion is caused by an out-of-range temperature, the ALERT output can operate in one of three different modes: default, one-time interrupt, or comparator mode. In the default and one-time interrupt modes, the ALERT signal and Interrupt Status Register are cleared by reading the Interrupt Status Register (Table 5). In comparator mode, ALERT is only cleared when the fault condition is removed. Reading the Interrupt Status Register clears all but bit 4 of the Status Register if the fault condition is not removed. Reading the Interrupt Status Register with the fault condition removed clears the entire register. Unless the fault is removed, ALERT is reasserted after the next conversion cycle. The ALERT output can also be masked by writing to the appropriate bits in the Interrupt Mask Register (Table 6) or by setting bit 1 of the Configuration Register (Table 4) to zero.

The interrupt does not halt conversions. New temperature and voltage data continue to be available over the SMBus interface after ALERT is asserted. The three temperature ALERT modes are shown in Figure 1 and are selected through the Temperature Configuration Register (Table 7). The ALERT output pin is open drain, so the device can share a common interrupt line.

#### Default Mode

An interrupt is initiated when temperature exceeds  $T_{HOT}$  (address 39h). The interrupt is cleared only by reading the Interrupt Status Register. An interrupt continues to be generated on subsequent measurements until the temperature goes below  $T_{HYST}$  (address 3Ah).

#### **One-Time Interrupt Mode**

An interrupt is initiated when temperature exceeds  $T_{HOT}$  (address 39h). The interrupt is cleared only by reading the Interrupt Status Register. The next interrupt is then initiated when temperature falls below the  $T_{HYST}$  (address 3Ah).

#### **Comparator Mode**

An interrupt is initiated when temperature exceeds  $T_{HOT}$  (address 39h). The ALERT output remains asserted low until the temperature goes below  $T_{HOT}$ . Reading the Interrupt Status Register does not clear the ALERT output or interrupt status bit in the register. The interrupt continues to be generated on subsequent measurements until the temperature falls below  $T_{HOT}$ .

**MAX6683**

| TEMPERATURE<br>MONITORING CYCLE<br>INTERRUPT<br>STATUS READ<br>THOT<br>THYST<br>ALERT<br>ALERT<br>ALERT<br>ALERT<br>ALERT<br>ALERT<br>COMPARATOR MODE |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

Figure 1. Alert Response to Temperature Interrupts

|         | S AD                                                             | DRESS                                                  | ;         | W/R                                                                   | АСК                 | co                                          | MMAND                   |                                  | ACK                                      | D                          | ΑΤΑ                 |                  | ACK                                                                                       |                                                    | Р                                                            |

|---------|------------------------------------------------------------------|--------------------------------------------------------|-----------|-----------------------------------------------------------------------|---------------------|---------------------------------------------|-------------------------|----------------------------------|------------------------------------------|----------------------------|---------------------|------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------|

|         | 7                                                                | ' bits                                                 |           | 0                                                                     |                     |                                             | 8 bits                  |                                  |                                          | 8                          | bits                |                  |                                                                                           |                                                    |                                                              |

| ea      | lent to                                                          | Addre<br>chip-s<br>re interf<br>nat                    | elect li  |                                                                       |                     |                                             | nd Byte: :<br>you are w |                                  |                                          | set b                      | y the<br>olds,      | e comr<br>config | oes into t<br>nand by<br>uration r                                                        | rte (to s                                          | set                                                          |

| s       | ADDRES                                                           | s v                                                    | //R       |                                                                       | IMAND               | ACK                                         | S                       | ADD                              | RESS                                     | W/R                        | AC                  | ж                | DATA                                                                                      | Ā                                                  | Р                                                            |

|         | 7 bits                                                           |                                                        | 0         | 6                                                                     | bits                |                                             |                         | 7                                | bits                                     | 1                          |                     |                  | 8 bits                                                                                    |                                                    |                                                              |

|         | Slave Ad<br>lent to chip<br>a 3-wire in                          | o-selec                                                | t line of | which                                                                 | ,                   | te: selec<br>er you a                       |                         | due to                           | Address<br>c chang<br>irection           |                            |                     | th               | ata Byte<br>ne registe<br>ommand                                                          | er set by                                          |                                                              |

| en<br>S | lent to chip                                                     | o-selec<br>terface                                     | t line of | which<br>readin                                                       | registen<br>ng from | er you a                                    | re                      | due to<br>flow di                | o chang                                  | e in da<br>Format          | ita-                | th               | ne registe                                                                                | er set by                                          |                                                              |

|         | lent to chip<br>a 3-wire in<br>a Byte Form                       | o-selec<br>terface                                     | t line of | which<br>readin                                                       | registen<br>ng from | er you a                                    | re                      | due to<br>flow di                | o chang<br>irection<br><b>Byte I</b>     | e in da<br>Format<br>SS W  | ita-                | th<br>C          | ne registe<br>ommand                                                                      | er set by<br>byte                                  | y the                                                        |

| S       | lent to chip<br>a 3-wire in<br>a <b>Byte Form</b><br>ADDRESS     | b-selector<br>terface<br><b>bat</b><br><b>W/R</b><br>0 | t line of | which<br>reading                                                      | ID AC               | <b>K P</b><br>ata to the                    | R                       | due to<br>flow di                | o chang<br>irection<br>Byte I<br>ADDRE   | e in da<br>Format<br>SS W  | ita-<br>t<br>Ī/R    | ACK              | DATA                                                                                      | reads d<br>er comr<br>st Read<br>for SME           | P<br>lata from<br>manded<br>Byte or<br>nission;<br>Bus alert |

| S       | lent to chip<br>a 3-wire in<br>ad Byte Form<br>ADDRESS<br>7 bits | b-selector<br>terface<br><b>bat</b><br><b>W/R</b><br>0 | t line of | which<br>readin<br>8 bits<br>Data Byte:<br>register co<br>last Read E | In registering from | K     P       ata to the d by the rite Byte | R                       | due to<br>flow di<br>eceive<br>S | b chang<br>irection Byte I ADDRE: 7 bits | e in da<br>Formati<br>SS W | ita-<br><b>i</b> /R | ACK              | DATA<br>8 bits<br>ata Byte:<br>he regist<br>y the las<br>/rite Byte<br>so used<br>esponse | reads d<br>er com<br>t Read<br>for SME<br>return a | P<br>lata from<br>manded<br>Byte or<br>nission;<br>Bus alert |

Figure 2. SMBus Protocols

Figure 3. SMBus Write Timing Diagram

Figure 4. SMBus Read Timing Diagram

#### SMBus/I<sup>2</sup>C-Compatible Digital Interface

From a software prospective, the MAX6683 appears as a set of byte-wide registers that contain voltage and temperature data, alarm threshold values, or control bits.

The device employs five standard SMBus protocols: write byte, read byte, read word, send byte, and receive byte (Figures 2, 3, 4).

#### **Slave Address**

The device address can be set to one of four different values by pin strapping ADD to GND, SDA, SCL, or

V<sub>CC</sub>, so more than one MAX6683 can reside on the same bus without address conflicts (Table 1). The address pin state is checked at the beginning of each SMBus/I<sup>2</sup>C transaction and is insensitive to glitches on V<sub>CC</sub>. Any address code can also be written to the Serial Address Register and overwrites the code set by connecting the ADD pin until the MAX6683 is taken through a POR cycle.

The MAX6683 also responds to the SMBus alert response address (see Alert Response Address).

| _         |        |     | UPPEF | R BYTE |    |    |    |      |    |    | LOWE | R BYTE |   |         |          |

|-----------|--------|-----|-------|--------|----|----|----|------|----|----|------|--------|---|---------|----------|

| D10       | D9     | D8  | D7    | D6     | D5 | D4 | D3 | D2   | D1 | D0 | Х    | Х      | Х | Х       | Х        |

| 11-BIT RE | AD FOR | MAT |       |        |    |    |    |      |    |    |      |        |   |         |          |

|           |        |     | UPPEF | R BYTE |    |    |    | <br> |    |    | LOWE | R BYTE |   |         |          |

| D8        | D7     | D6  | D5    | D4     | D3 | D2 | D1 | DO   | Х  | х  | х    | х      | х | х       | Х        |

| 9-BIT REA | D FORN | ИАТ |       |        |    |    |    |      |    |    |      |        |   | X = D0N | I'T CARE |

Figure 5. Read Temperature Format

#### Alert Response Address

The SMBus alert response interrupt pointer provides quick fault identification for simple slave devices that lack the complex, expensive logic needed to be a bus master. Usually the ALERT outputs of several slave devices are wire-ORed to the same interrupt input of the host master. Upon receiving an interrupt signal, the host master can broadcast a receive byte transmission (Figure 2) with the alert response address (0001 100). A read operation is denoted by a 1 in the eighth address bit. Then, any slave device that generated an interrupt attempts to identify itself by putting its own address on the bus.

The alert response can activate several different slave devices simultaneously, similar to the I<sup>2</sup>C general call. If more than one slave attempts to respond, bus arbitration rules apply, and the device with the lower address code wins. The losing device does not generate an acknowledge signal and continues to hold the interrupt line low until serviced. The MAX6683 does not automatically clear its ALERT when it responds to an alert response address. The host master must then clear or mask the ALERT by reading the Interrupt Status Register, writing to the Interrupt Mask Register, or setting bit 1 of the Configuration Register to zero before it can identify other slaves generating an interrupt.

#### **Command Byte Functions**

The 8-bit Command Byte Register (Table 1) is the master index that points to the other data, configuration, limits, and address registers within the MAX6683. The functions of those other registers are described below.

#### **Configuration Byte Functions**

The Configuration Register (Table 4) is a read-write register with several functions:

- Bit 0 puts the MAX6683 into software standby mode (STOP) or autoconvert (START) mode. The 2-wire interface is still active in the standby mode. All voltage and temperature limits should be set before setting this bit to 1.

- Bit 1 enables and disables the ALERT output. Setting this bit to 1 enables the ALERT output.

- Bit 2 is reserved.

- Bit 3 clears the ALERT output and stops the monitoring loop when set to 1. Clearing the output does not affect the contents of the Interrupt Status Registers.

- Bit 4 sets the analog-to-digital conversion speed to minimize interference from power-line frequencies. Setting this bit to 1 can improve accuracy when the power-line frequency is 50Hz. When the power-line frequency is 60Hz, bit 4 should be zero.

- Bit 5 reduces the oversampling ratio in the ADC from 8 to 2. This reduces the monitoring cycle time by a factor of 4 to typically 50ms at the cost of reduced noise rejection.

- Bit 6 is reserved.

- Bit 7 resets all register values to their power-up default values. To reset all registers, set bit 7 to 1. This also resets bit 7 to its power-up value of zero.

#### **Read Temperature**

The MAX6683 reads out temperature in an 8-, 9-, or 11-bit two's complement format. To obtain the 8-bit temperature data (7 bits plus sign), execute a Read Byte command to the Temperature Data Register (address 27h).

To obtain the 11-bit temperature data (10 bits plus sign), execute a Read Word command to the Temperature Data Register (address 27h). When per-

**Functional Diagram**

forming a Read Word operation, the MAX6683 writes the 11 bits of data to the bus in two 8-bit words. The upper byte contains the MSBs, while the lower byte contains the 3LSBs (Figure 5). D9–D3 of the upper byte represent the whole decimal number of the temperature conversion and D10 is sign. D2–D0 of the lower byte represent 1/2, 1/4, 1/8 of a degree, respectively, and the remaining bits are disregarded.

Nine-bit temperature data (8 bits plus sign) is obtained by setting bit 5 of the Configuration Register (address 40h) to 1, reducing the conversion time by a factor of four, and executing a Read Word command to the Temperature Data Register (address 27h). The upper byte contains the MSBs, while the lower byte contains the LSB (Figure 5). D7–D1 of the upper byte represent the whole decimal number of the temperature conversion and D0 is sign. D0 of the lower byte represents 1/2 of a degree, and the remaining bits are disregarded.

#### \_\_Applications Information

#### Sensing Circuit Board and Component Temperatures

Temperature sensor ICs like the MAX6683 that sense their own die temperatures must be mounted on or close to the object whose temperature they are intended to measure. Because there is a good thermal path between the 10-pin µMAX package's metal leads and the IC die, the MAX6683 can accurately measure the temperature of the circuit board to which it is soldered. If the sensor is intended to measure the temperature of a heat-generating component on the circuit board, it should be mounted as close as possible to that component and should share supply and ground traces (if they are not noisy) with that component where possible. This maximizes the heat transfer from the component to the sensor.

The thermal path between the plastic package and the die is not as good as the path through the leads, so the MAX6683, like all temperature sensors in plastic packages, is less sensitive to the temperature of the surrounding air than to the temperature of the leads.

Wiring and circuits must be kept insulated and dry to avoid leakage and corrosion, especially if they operate at cold temperatures where condensation can occur.

## \_Chip Information

TRANSISTOR COUNT: 13,446 PROCESS: BICMOS

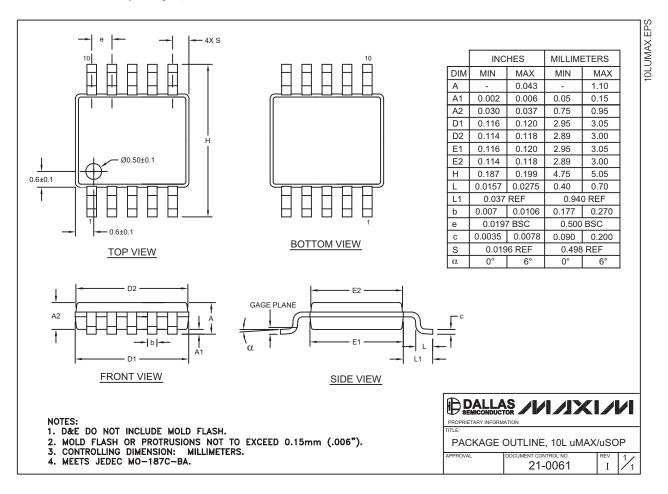

## **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

14

MAX6683

© 2004 Maxim Integrated Products

Printed USA

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

MAXIM is a registered trademark of Maxim Integrated Products.