Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### General Description

The MAX768 low-noise, dual-output, regulated charge pump provides a negative output for biasing GaAsFET power amplifiers, and a positive output for powering voltage-controlled oscillators (VCOs) in wireless handsets. The outputs can also be used to power LCDs. Output ripple is less than 2mVp-p. The MAX768 is intended for use in low-voltage systems where a simple charge-pump inverter is inadequate, or where the VCO needs more range to improve its signal-to-noise ratio. The input range is 2.5V to 5.5V, enabling direct power from 1Li+ and 3-cell NiMH/NiCd batteries.

The MAX768 includes a voltage-doubler charge pump, followed by an inverting charge pump. This combination produces unregulated outputs that are ±2x the input. Two internal low-dropout linear regulators provide the low-noise, regulated positive and negative outputs. Output current is guaranteed to be at least 5mA per output. The linear regulators use CMOS devices, so the quiescent current remains independent of output loading (even in dropout), and the dropout voltage approaches zero with no load current.

The MAX768 has two preset switching frequencies (25kHz or 100kHz), or can be synchronized by an external clock from 20kHz to 240kHz. This flexibility permits users to optimize their designs based on noise, capacitor size, and quiescent-supply-current criteria.

The device features Dual Mode™ operation: the output voltage is preset to +5V and -5V, or can be adjusted by adding external resistor dividers. Other features include independent shutdowns and a logic output that signals when the negative voltage has risen to within 10% of its regulation setpoint (to protect the power amplifier GaAsFET). The MAX768 is available in a space-saving, 16-pin QSOP, which is the same size as a standard 8-pin SO.

#### **Applications**

GaAsFET Power Amp Bias

Voltage-Controlled Oscillator (VCO) Supply

Tuner Diode Power Supply

Positive and Negative LCD Supply

Cellular Phone

PCS and Cordless Phone

Wireless Handsets

Wireless Handheld Computers

Wireless PCMCIA Cards

Modems

#### Features

- **♦ Dual Positive/Negative Regulated Outputs:** ±5Vout from 3Vin

- Output-Ready Indicator to Protect GaAsFET PAs

- ♦ 2.5V to 5.5V Input Voltage Range

- ♦ Low-Noise Output Ripple: < 2mVp-p</p>

- ♦ Synchronizable Switching Frequency

- Uses Only Small, Low-Cost Capacitors

- ♦ 0.1µA Independent Shutdown Controls

- ♦ Adjustable Output Voltages

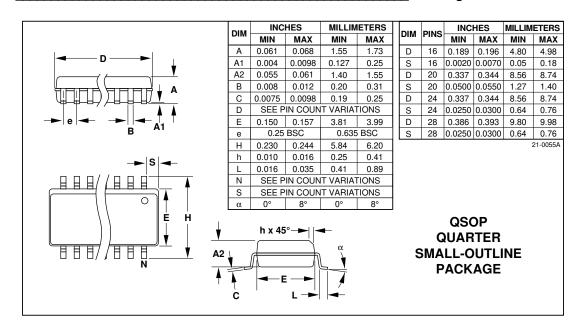

- **♦ Small 16-Pin QSOP Package**

#### Ordering Information

| PART      | TEMP. RANGE    | PIN-PACKAGE |

|-----------|----------------|-------------|

| MAX768C/D | 0°C to +70°C   | Dice*       |

| MAX768EEE | -40°C to +85°C | 16 QSOP     |

<sup>\*</sup>Dice are specified at T<sub>A</sub> = +25°C, DC parameters only.

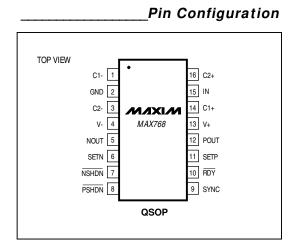

#### Pin Configuration appears at end of data sheet.

Dual Mode is a trademark of Maxim Integrated Products.

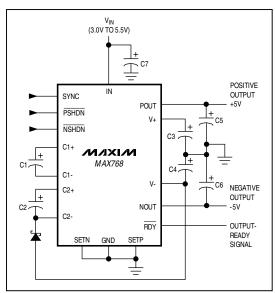

### Typical Operating Circuit

### MIXIM

### **ABSOLUTE MAXIMUM RATINGS**

| VIN, C1-, SYNC, PSHDN, NSHDN to GND V+, C1+, C2+, RDY to GND SETP to GND SETN to GND V-, C2- to GND OUTP, OUTN Short Circuited to GND NOUT to V- | -0.3V to +12V<br>-0.3V to +3V<br>-3V to +0.3V<br>-12V to +0.3V<br>-12V to +0.3V |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| NOUT to VPOUT to V+                                                                                                                              |                                                                                 |

|                                                                                                                                                  |                                                                                 |

| Continuous Power Dissipation ( $T_A = +70$ °C) |               |

|------------------------------------------------|---------------|

| QSOP (derate 8.70mW/°C above +70°C)            | 696mW         |

| Operating Temperature Range                    |               |

| MAX768EEE                                      | 40°C to +85°C |

| Maximum Junction Temperature                   | +150°C        |

| Storage Temperature Range                      |               |

| Lead Temperature (soldering, 10sec)            | +300°C        |

|                                                |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = +3V, SYNC = IN, SETN = SETP = GND, \overline{NSHDN} = \overline{PSHDN} = IN, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ . See Figure 2.) (Note 1)

| Input Voltage Range   3.0                                                                                                                             | 2.5   | 5.5   | V       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|---------|

|                                                                                                                                                       | 5.00  |       | V       |

| Positive Output Voltage 0mA < ILOAD < 5mA Viv. = 3.0V to 5.5V 4.81                                                                                    |       |       | 1 - 1   |

| 1 Ositive Output voitage   Offia < ILOAD < SITIA, VIN = 3.0V to 3.3V   4.01                                                                           |       | 5.14  | V       |

| Negative Output Voltage 0mA < I <sub>LOAD</sub> < 5mA, V <sub>IN</sub> = 3.0V to 5.5V -5.10                                                           | -5.00 | -4.82 | V       |

| Positive Output Voltage Adjustable Range (Note 2) 1.25                                                                                                |       | 11    | V       |

| Negative Output Voltage Adjustable Range (Note 3) -11                                                                                                 |       | -1.25 | V       |

| Maximum POUT, NOUT Output Currents $V_{IN} = 3V$ , $V_{POUT} \ge 4.81V$ , $V_{NOUT} \le -4.82V$ 5                                                     |       |       | mA      |

| No-Load Supply Current at 100kHz VIN = 3.0V                                                                                                           | 0.8   | 1.4   | mA      |

| (both regulators active) V <sub>IN</sub> = 5.5V                                                                                                       | 1.5   |       | IIIA    |

| No-Load Supply Current at 100kHz (negative regulator off)  NSHDN = GND                                                                                | 0.3   |       | mA      |

| No-Load Supply Current at 25kHz (both regulators active) VSYNC = GND                                                                                  | 0.45  | 0.80  | mA      |

| Property Velters (0.0 Ver.   Ver.   Ver.   Ver.   Pout = Nout = 0.1mA                                                                                 | 20    |       | mV      |

| Dropout Voltage (2 x V <sub>IN</sub> -  V <sub>OUT</sub>  )   2 x V <sub>IN</sub> -  V <sub>OUT</sub>     I <sub>POUT</sub> = I <sub>NOUT</sub> = 5mA | 420   | 900   | 1111    |

| $V_{IN} = 3V \text{ to } 5.5V \qquad \qquad -0.12$                                                                                                    | 0.0   | 0.12  | %/V     |

| Load Regulation IPOUT = 0mA to 5mA, INOUT = 0mA to -5mA                                                                                               | 0.06  | 0.12  | %/mA    |

| Output Voltage Noise  CPOUT = CNOUT = 10µF, POUT                                                                                                      | 1.2   |       | m\/n n  |

| 10kHz < f < 1MHz NOUT                                                                                                                                 | 1.7   |       | - mVp-p |

| Shutdown/SYNC Logic-Low Input Threshold                                                                                                               |       | 0.4   | ٧       |

| Shutdown/SYNC Logic-High Input Threshold 2.0                                                                                                          |       |       | ٧       |

| SHUTDOWN                                                                                                                                              |       |       |         |

| SHDN Input Bias Current VSHDN = 3V                                                                                                                    | 0.1   | 2     | μΑ      |

| Shutdown Supply Current $\overline{\text{NSHDN}} = \overline{\text{PSHDN}} = \text{SYNC} = \text{GND}$                                                | 0.1   | 10    | μΑ      |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = +3V, SYNC = IN, SETN = SETP = GND, \overline{NSHDN} = \overline{PSHDN} = \overline{IN}, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ . See Figure 2.) (Note 1)

| PARAMETER                        | CONDITIONS                                             |                                                | MIN    | TYP   | MAX    | UNITS |

|----------------------------------|--------------------------------------------------------|------------------------------------------------|--------|-------|--------|-------|

| SYNC                             | '                                                      |                                                |        |       |        |       |

| SYNC Frequency Range (external)  |                                                        |                                                | 20     |       | 240    | kHz   |

| SYNC Duty Cycle (external)       |                                                        |                                                | 40     |       | 60     | %     |

| Ossillatar Fraguenay (internal)  | SYNC = GND (divid                                      | SYNC = GND (divide by 4)                       |        | 25    | 28.5   | kHz   |

| Oscillator Frequency (internal)  | V <sub>SYNC</sub> = 3V                                 | VSYNC = 3V                                     |        | 100   | 115    |       |

| SYNC Input Leakage Current       |                                                        |                                                |        | 0.1   | 2      | μΑ    |

| SET INPUT                        | '                                                      |                                                |        |       |        |       |

| Positive Set-Reference Voltage   | 0.4                                                    | T <sub>A</sub> = +25°C                         | 1.217  | 1.25  | 1.283  | V     |

| Positive Set-herefelice voltage  | I <sub>POUT</sub> = 0.1mA                              | $T_A = -40^{\circ}C \text{ to } + 85^{\circ}C$ | 1.215  | 1.25  | 1.285  |       |

| Negative Cat Deference Valtage   | 0.4.4                                                  | T <sub>A</sub> = +25°C                         | -1.270 | -1.25 | -1.230 | V     |

| Negative Set-Reference Voltage   | INOUT = 0.1mA                                          | $T_A = -40^{\circ}C \text{ to } + 85^{\circ}C$ | -1.275 | -1.25 | -1.225 |       |

| SETP, SETN Input Leakage Current | V <sub>SETP</sub> = V <sub>SETN</sub> = 1              | .3V                                            |        | 0.01  | 0.1    | μΑ    |

| RDY OUTPUT                       | '                                                      |                                                |        |       |        |       |

| RDY Output Threshold             | Percent of V <sub>NOUT</sub> , I <sub>NOUT</sub> = 5mA |                                                | 85     | 94    | 98     | %     |

| Output Low Voltage               | I <sub>SINK</sub> = 2mA                                |                                                |        |       | 0.25   | V     |

| Output Off Current               | V <sub>RDY</sub> = 10V                                 | V <sub>RDY</sub> = 10V                         |        | 0.01  | 2      | μΑ    |

| Maximum Sink Current             |                                                        |                                                |        | 10    |        | mA    |

Note 1: Parameters to -40°C are guaranteed by design, not production tested.

Note 2: Maximum output voltage range is from the positive reference voltage to 2 x V<sub>IN</sub> - dropout voltage.

Note 3: Maximum output voltage range is from the negative reference voltage to -2 x VIN + dropout voltage.

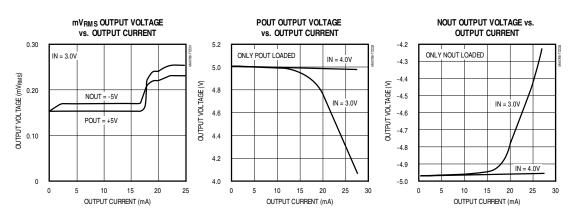

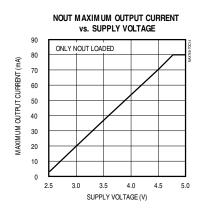

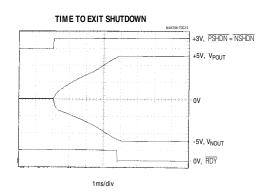

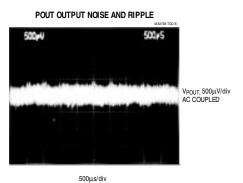

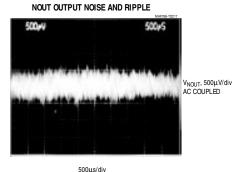

### \_Typical Operating Characteristics

(SYNC = IN,  $T_A = +25$ °C, unless otherwise noted.)

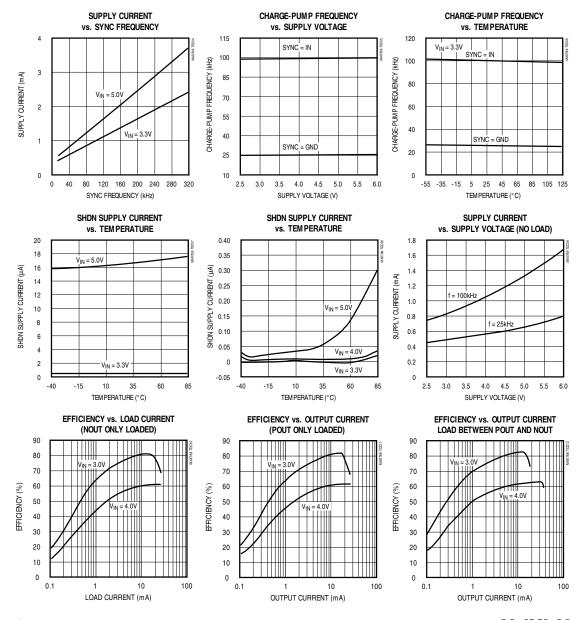

\_\_\_\_\_Typical Operating Characteristics (continued)

(SYNC = IN, T<sub>A</sub> = +25°C, unless otherwise noted.)

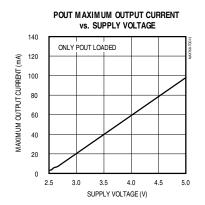

Typical Operating Characteristics (continued)

(SYNC = IN,  $T_A = +25$ °C, unless otherwise noted.)

NOUT = -5V AT 5mA IN = 3.0V

POUT = +5V AT 5mA

IN = 3.0V

Pin Description

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                  |  |  |  |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | C1-   | Negative Terminal of the Doubler Charge-Pump Capacitor. See Table 2 for capacitor selection.                                                                                                                                              |  |  |  |

| 2   | GND   | Ground                                                                                                                                                                                                                                    |  |  |  |

| 3   | C2-   | Negative Terminal of the Inverter Charge-Pump Capacitor                                                                                                                                                                                   |  |  |  |

| 4   | V-    | Inverter Charge-Pump Output. See Table 2 for capacitor selection.                                                                                                                                                                         |  |  |  |

| 5   | NOUT  | Negative Regulator Output. See Table 2 for capacitor selection.                                                                                                                                                                           |  |  |  |

| 6   | SETN  | Set Negative Output Voltage Input. Connect SETN to GND for factory-preset -5V. Connect a resistor divider between NOUT, SETN, and GND for custom output voltage setting.                                                                  |  |  |  |

| 7   | NSHDN | Negative-Supply Shutdown Input. Pull $\overline{\text{NSHDN}}$ low to turn off the inverting charge pump, the negative regulator, and the bias-ready indicator. If $\overline{\text{PSHDN}}$ is also low, the part completely shuts down. |  |  |  |

| 8   | PSHDN | Positive-Supply Shutdown Input. Pull PSHDN low to turn off the positive regulator. If NSHDN is also low, the part completely shuts down.                                                                                                  |  |  |  |

| 9   | SYNC  | Clock Synchronizing Input. Connect an external 20kHz ≤ f <sub>CLK</sub> ≤ 240kHz to SYNC to synchronize the MAX768 to that frequency. Connect SYNC to GND to select the internal 25kHz clock, or to IN for the internal 100kHz clock.     |  |  |  |

| 10  | RDY   | Output-Ready Indicator. This open-drain output pulls to GND when the negative output voltage (NOUT) is within 10% of the regulation voltage.                                                                                              |  |  |  |

| 11  | SETP  | Set Positive Output Voltage Input. Connect SETP to GND for factory-preset +5V output. Connect a resistor divider between POUT, SETP, and GND for custom output voltage setting.                                                           |  |  |  |

| 12  | POUT  | Positive Regulator Output. See Table 2 for capacitor selection.                                                                                                                                                                           |  |  |  |

| 13  | V+    | Doubler Charge-Pump Output. See Table 2 for capacitor selection.                                                                                                                                                                          |  |  |  |

| 14  | C1+   | Positive Terminal of the Doubler Charge-Pump Capacitor. See Table 2 for capacitor selection.                                                                                                                                              |  |  |  |

| 15  | IN    | Supply (3V to 5.5V). Bypass IN with 4.7μF to GND.                                                                                                                                                                                         |  |  |  |

| 16  | C2+   | Positive Terminal of the Inverter Charge-Pump Capacitor. See Table 2 for capacitor selection.                                                                                                                                             |  |  |  |

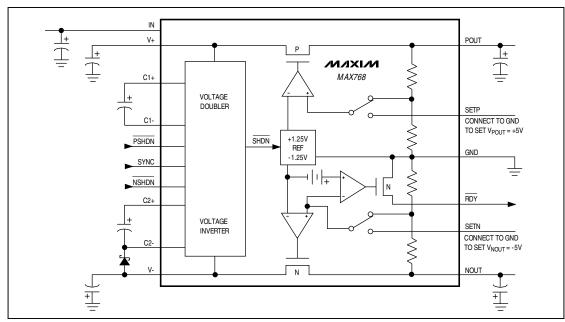

Figure 1. Functional Diagram

#### **Detailed Description**

The MAX768 requires only seven external capacitors to implement a regulated voltage doubler/inverter. These can be ceramic or polarized electrolytic capacitors ranging from 2.2µF to 47µF. Figure 1 is a functional diagram of the MAX768. The applied input voltage (VIN) is first doubled to a value of 2VIN by a capacitor charge pump and then stored in the V+ reservoir capacitor. Next, the voltage at V+ is inverted to -2VIN and stored at the V- reservoir capacitor. The voltages at V+ and V- are then linear regulated and appear at POUT and NOUT, respectively. The ripple noise induced by the doubling and inverting charge pump is reduced by the linear regulators to 1.2mVp-p for POUT and 1.7mVp-p for NOUT. In addition, the linear regulator's excellent AC rejection attenuates noise from the incoming supply. A minimum of 5mA is available at each output. When NOUT is more negative than 90% of the regulated output voltage, the open-drain RDY output pulls to GND.

The charge pump operates in three modes: when \$\overline{SYNC}\$ = \$GND\$, the charge pump operates at 25kHz; when \$\overline{SYNC}\$ = IN, it operates at 100kHz, or \$\overline{SYNC}\$ can be overdriven with an external clock in the 20kHz to 240kHz range. The clock must have a 40% to 60% duty cycle.

### Applications Information

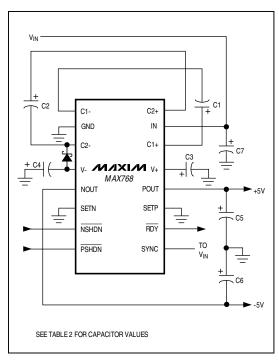

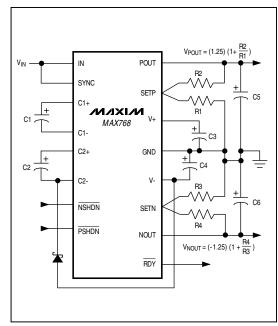

#### Setting the Output Voltage

Connect SETP or SETN directly to GND to select a fixed +5V or -5V output voltage, respectively (Figure 2). Select an alternative voltage for either output by connecting SETP or SETN to the midpoint of a resistor voltage divider from POUT or NOUT, respectively, to GND (Figure 3). (2 x VIN) must be 1.0V above the absolute value of the output voltage to ensure proper regulation. Calculate the output voltage from the formulas below. Choose R1 and R3 at between  $100k\Omega$  to  $400k\Omega$ .

$$R2 = \left(R1\right)\left(\frac{V_{POUT}}{V_{PSET REF}} - 1\right)$$

$$R4 = \left(R3\right)\left(\frac{V_{NOUT}}{V_{NSET REF}} - 1\right)$$

where VPSET REF = 1.25V (typical) and VNSET REF = -1.25V (typical).

#### Table 1. Shutdown-Control Logic

| PSHDN | NSHDN | POUT<br>STATUS            | NOUT<br>STATUS            | SUPPLY<br>CURRENT<br>(mA) |

|-------|-------|---------------------------|---------------------------|---------------------------|

| 1     | 1     | Positive output active    | Negative output active    | 0.8                       |

| 1     | 0     | Positive output active    | Negative output inactive  | 0.7                       |

| 0     | 1     | Positive output inactive  | Negative output active    | 0.3                       |

| 0     | 0     | Shutdown (low-power mode) | Shutdown (low-power mode) | 0.0001                    |

#### Table 2. Charge-Pump Capacitor Selection (Figure 2)

| SYNC           | FREQUENCY | CAPACITORS             |        |       |

|----------------|-----------|------------------------|--------|-------|

| INPUT          | (kHz)     | C1, C2, C3, C4         | C5, C6 | C7    |

| GND            | 25        | 10μF                   |        |       |

| IN             | 100       | 2.2μF                  | 10μF   | 4.7μF |

| External Clock | 20 to 240 | $C = 220\mu F/f (kHz)$ |        |       |

#### Shutdown

The MAX768 has two active-low, TTL logic-level shutdown inputs:  $\overline{\text{PSHDN}}$  and  $\overline{\text{NSHDN}}.$  When both inputs are pulled low, the MAX768 shuts down and the supply current is reduced to  $10\mu\text{A}$  max over temperature. Pulling  $\overline{\text{PSHDN}}$  low turns off the positive linear regulator; the doubler charge pump remains active. Pulling the  $\overline{\text{NSHDN}}$  input low while  $\overline{\text{PSHDN}}$  remains high turns off the inverter charge pump, the negative linear regulator, and the output-ready indicator (Table 1).

#### Capacitors

The overall dropout voltage is a function of the charge pump's output resistance and the voltage drop across the linear regulator. The charge-pump output resistance is a function of the switching frequency and the capacitor's ESR value. Therefore, minimizing the charge-pump capacitors' ESR minimizes dropout voltage.

$$\begin{split} R_{POUT} &= 84 \; + \; 8 \big( \text{C1}_{\text{ESR}} \big) \; + \; \big( \text{C3}_{\text{ESR}} \big) \; + \; \frac{2}{f_{\text{OSC}}\text{C1}} \\ R_{\text{NOUT}} &= 84 \; + \; 8 \big( \text{C1}_{\text{ESR}} \big) \; + \; 4 \big( \text{C2}_{\text{ESR}} \big) + \\ & (\text{C4}_{\text{ESR}}) \; + \; \frac{2}{f_{\text{OSC}}\text{C1}} \; + \; \frac{1}{f_{\text{OSC}}\text{C2}} \end{split}$$

See Table 2 for capacitor selection. All capacitors should be either surface-mount ceramic chip or tantalum. External capacitor values may be adjusted to optimize size, performance, and cost.

Figure 2. MAX768 Standard Application Circuit

Figure 3. MAX768 Adjustable Configuration

#### Switching-Frequency Control

For applications sensitive to the MAX768's internal switching frequency, connect an external TTL/CMOS (within IN and GND) clock to SYNC. The clock must be a 20kHz to 240kHz square wave between 40% and 60% duty cycle.

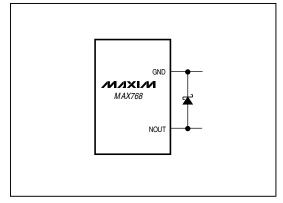

#### Schottky Diodes

When under heavy loads, where POUT is sourcing into NOUT (i.e., load current flows from POUT to NOUT, rather than from supply to ground), do not allow NOUT to pull above ground. In applications where large currents from POUT to NOUT are likely, use a Schottky diode (1N5817) between GND and NOUT, with the anode connected to GND (Figure 4).

Connect a IN5817-type Schottky diode from C2- to V-to assure proper start-up.

Figure 4. A Schottky diode protects the MAX768 when a large current flows from POUT to NOUT.

#### Layout and Grounding

Good layout is important, primarily for good noise performance:

- Mount all components as close together as possible.

- Keep traces short to minimize parasitic inductance and capacitance. This includes connections to SETP and SETN.

- 3) Use a ground plane.

#### Noise and Ripple Measurement

Accurately measuring output noise and ripple can be difficult. Brief differences in ground potential between the circuit and the oscilloscope (which result from the charge pump's switching action) cause ground currents in the probe's wires, inducing sharp voltage spikes. For best results, measure directly across output capacitor C3, C4, C5, or C6. Do not use the oscilloscope probe's ground lead; instead, remove the cover's ground lead and touch the ground ring on the probe directly to the ground terminal of C3, C4, C5, or C6. Or, use a Tektronix chassis-mount test jack (part no. 131-0258) to connect your scope probe directly. This direct connection provides the most accurate noise and ripple measurement.

\_\_Chip Information

TRANSISTOR COUNT: 657 SUBSTRATE CONNECTED TO GND

Package Information

**NOTES**