Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

#### **General Description**

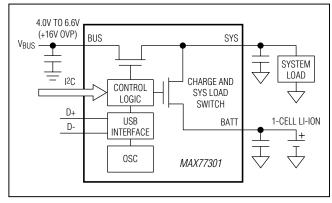

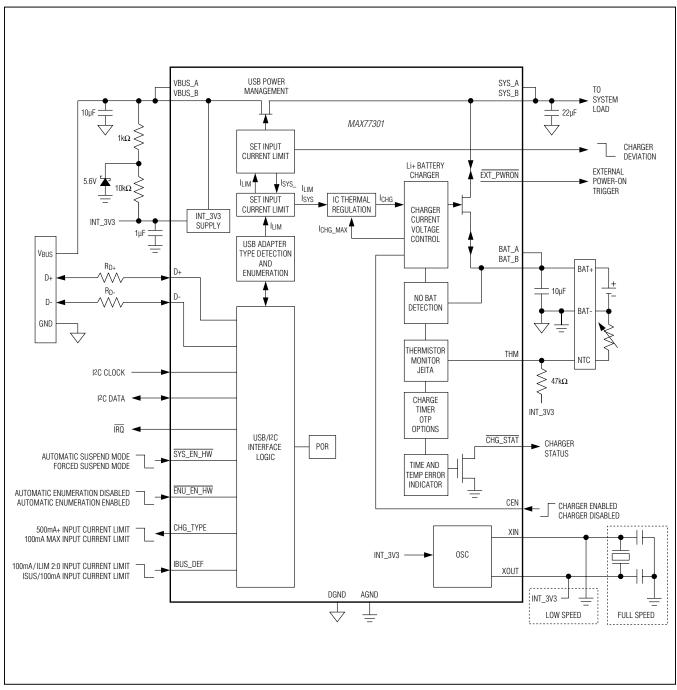

The MAX77301 is a JEITA-compliant\* lithium-ion linear battery charger that operates from a USB port, a dedicated charger, or universal adapter. The IC provides automatic adapter-type detection and enumeration with a USB host or hub. The IC integrates independent battery charge switch, current sense circuit, MOSFET pass elements, thermal regulation circuitry, and eliminates the external reverse-blocking Schottky diode to create the simplest and smallest USB-compliant charging solution.

The IC includes automated detection of charge adapter type, making it possible to distinguish USB 2.0 device, USB charger, dedicated charger devices as well as standard input adapters. See Table 2. When enumeration is enabled, the IC automatically negotiates with a USB host, making it possible to achieve the highest-charging current available from a USB 2.0 device or USB charger without processor intervention. The adapter type detection is compliant with USB 2.0 as well as battery charging Specification Revision 1.1.

The IC controls the charging sequence for single-cell Li+ batteries from battery detection, prequalification, fast charge, top-off, and charge termination. Charging is controlled using constant current, constant voltage and constant die-temperature (CCCVCTj) regulation for safe operation under all conditions. The IC is also compliant with JEITA battery charging requirements.

The Smart Power Selector feature makes the best use of limited USB or adapter power. Battery charge current is set independent of the input current limit. Power not used by the system charges the battery. The battery assists the input source when needed. System voltage is maintained by allowing the application to operate without a battery, a discharged battery, or a dead battery. Automatic input selection switches the system from battery to external power.

The I<sup>2</sup>C interface provides full programmability of battery charge characteristics, input current limit, and protection features. This provides flexibility for use with a wide range of adapter and battery sizes.

Other features include undervoltage lockout (UVLO), overvoltage protection (OVP), charge status flag, charge fault flag, input power-OK monitor, battery detection, JEITA-compliant charging, charge timer, 3.3V/10mA auxiliary output, and an external power-on switch.

#### **Benefits and Features**

- ♦ Enables Charging from a USB Port

- **♦** Automatic Detection of Adapter Type

- ♦ Input Current Up to 1500mA and Charging Current Up to 900mA

- **♦ Enumeration Without Processor Intervention**

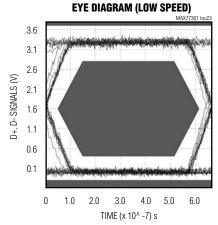

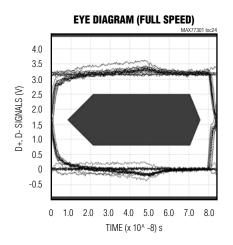

- ♦ Supports USB Low-Speed and Full-Speed

- ♦ Compliant with USB 2.0 Specification and Battery Charging Specification (Revision 1.1)

- ♦ Compliant with Next Generation Low-Voltage Li-lon Battery Profiles

- ◆ Input Overvoltage Protection Up to 16V

- ♦ Smart Power Selector™ Allows Power Path Operation with Discharged or No Battery

- Battery Detection Including Packs with Open Protectors

- **♦ Thermal Regulation Prevents Overheating**

- ♦ LED Indicator for Charge Done, Precharge, and Time/Temperature Error

- ♦ Serial (400kHz) I<sup>2</sup>C-Compatible Interface

- ♦ 6µA (typ) Shutdown Current

- ♦ 2.44mm x 2.44mm, 25-Bump WLP Package

#### **Applications**

Bluetooth Headsets, PDAs, and MP3 Players Other Portable Devices

#### Simplified Operating Circuit

Ordering Information appears at end of data sheet.

Smart Power Selector is a trademark of Maxim Integrated Products, Inc.

\*U.S. Patent # 6,507,172.

For related parts and recommended products to use with this part, refer to <a href="https://www.maximintegrated.com/MAX77301.related">www.maximintegrated.com/MAX77301.related</a>.

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

#### **TABLE OF CONTENTS**

| General Description                 |    |

|-------------------------------------|----|

| Benefits and Features               |    |

| Applications                        |    |

| Simplified Operating Circuit        |    |

| Absolute Maximum Ratings            |    |

| Package Thermal Characteristics     |    |

| Electrical Characteristics          |    |

| Typical Operating Characteristics   |    |

| Bump Configuration                  |    |

| Bump Description                    |    |

| Detailed Description                |    |

| Data Contact Detection              |    |

| Power-On Reset                      |    |

| Interrupt Request ( <i>IRQ</i> )    |    |

| USB Interface                       |    |

| D+ and D                            |    |

| Low/Full Speed                      |    |

| Adapter Detection                   | 27 |

| Low-Power Mode                      | 27 |

| USB Suspend                         | 27 |

| Keyboard Test Mode                  |    |

| Wake-Up and USB Resume              | 30 |

| USB Enumeration                     |    |

| Smart Power Selector                |    |

| System Load Switch                  |    |

| Input Limiter                       |    |

| Setting Input Current Limit         |    |

| Minimum V <sub>SYS</sub> Threshold  |    |

| Input Current Limit                 |    |

| Power Monitor Output ( <i>UOK</i> ) |    |

| 0. (1.0)                            |    |

### JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

### **TABLE OF CONTENTS (continued)**

Maxim Integrated 3

### JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

### **LIST OF FIGURES**

Figure 23. I²C Write Operations46Figure 24. I²C Read Operations47Figure 25. Recommended PCB Layout for Full Speed66Figure 26. Recommended PCB Layout for Low Speed67

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

| LIST OF TABLES                           |    |

|------------------------------------------|----|

| Table 1. Status Registers                |    |

| Table 2. Adapter Type                    |    |

| Table 3. Device Descriptor               |    |

| Table 4. VBUS Valid Input Range (Rising) |    |

| Table 5. UOK States                      |    |

| Table 6. CHG_TYPE                        |    |

| Table 7. IBUS_DEF                        |    |

| Table 8. CHG_STAT Output                 |    |

| Table 9. I <sup>2</sup> C Register Map   | 48 |

| Table 10. CHIP_ID (Register 0x00)        | 49 |

| Table 11. CHIP_REV (Register 0x01)       | 49 |

| Table 12. STATUS_A (Register 0x02)       |    |

| Table 13. STATUS_B (Register 0x03)       | 51 |

| Table 14. STATUS_C (Register 0x04)       |    |

| Table 15. EVENT_A (Register 0x05)        |    |

| Table 16. EVENT_B (Register 0x06)        |    |

| Table 17. IRQ_MASK_A (Register 0x07)     |    |

| Table 18. IRQ_MASK_B (Register 0x08)     |    |

| Table 19. USB_CNTL (Register 0x09)       |    |

| Table 20. BAT_CNTL (Register 0x10)       |    |

| Table 21. IBUS_CNTL (Register 0x0A)      |    |

| Table 22. CHARGER_CNTL_A (Register 0x0B) |    |

| Table 23. CHARGER_CNTL_B (Register 0x0C) | 60 |

| Table 24. CHARGER_TMR (Register 0x0D)    | 61 |

| Table 25. CHARGER_VSET (Register 0x0E)   | 62 |

| Table 26. CHARGER_JEITA (Register 0x0F)  | 63 |

| Table 27. PRODUCT_ID_A (Register 0x11)   | 64 |

| Table 28. PRODUCT_ID_B (Register 0x12)   | 64 |

| Table 29. VENDOR_ID_A (Register 0x13)    | 65 |

| Table 30. VENDOR_ID_B (Register 0x14)    |    |

### JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

#### **ABSOLUTE MAXIMUM RATINGS**

| BUS_ to AGND0.3V to +16.0V INT_3V3 to AGND0.3V to +6V CHG_TYPE, IBUS_DEF, ENU_EN_HW, IRQ, D+, D-, UOK, CHG_STAT, BAT_, SYS_,                                                                    | $I_{BUS}$ and $I_{SYS}$ Continuous Current (Note 1) |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| CEN, <u>STDB_EN_HW</u> to AGND0.3V to +6.0V XIN, THM, XOUT, to AGND0.3V to (V <sub>INT_3V3</sub> + 0.3V) EXT_PWRON, SDA, SCL to AGND0.3V to (V <sub>SYS</sub> + 0.3V) DGND to AGND0.3V to +0.3V | Operating Temperature                               |

Note 1: IBUS = IBUS A + IBUS B; ISYS = ISYS A + ISYS B; IBAT = IBAT A + IBAT B

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **PACKAGE THERMAL CHARACTERISTICS (Note 2)**

WLP

Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>) .......52°C/W

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **ELECTRICAL CHARACTERISTICS**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT}$ -PWRON,  $\overline{UOK}$ ,  $\overline{IRQ}$ , CHG\_TYPE, and  $\overline{CHG}$ -STAT are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                               | SYMBOL                                                         | CONDITIONS                                                   |                                                                | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|------|------|------|-------|

| USB-TO-SYS PREREGULAT                   | ΓOR                                                            |                                                              |                                                                |      |      |      |       |

| USB Operating Range                     | V <sub>BUS</sub>                                               | Initial V <sub>BUS</sub> voltage charger                     | 4.0                                                            |      | 6.6  | V    |       |

| USB Standoff Voltage                    |                                                                | $V_{BAT} = V_{SYS} = 0V$ ,                                   | I <sub>BUS</sub> < 800μA                                       |      |      | 14   | V     |

| USB_OK Debounce Timer                   | t <sub>USB_DB</sub>                                            | Time from BUS with UOK goes high imp                         | nin valid range until<br>pedance                               |      | 30   | 50   | ms    |

|                                         | UOK logic-low,<br>V <sub>BUS</sub> rising,<br>100mV hysteresis | Before initial detection of external device                  | 3.85                                                           | 4.0  | 4.15 |      |       |

| USB Undervoltage Lockout<br>Threshold   |                                                                | UOK logic-low,<br>V <sub>BUS</sub> falling,<br>customer UVLO | For > 500mA adapter<br>and except for ILIM<br>[2:0] = 000, 111 | 3.40 | 3.55 | 3.70 | V     |

|                                         |                                                                | UOK logic-low,<br>V <sub>BUS</sub> falling                   | USB 2.0 low-power device                                       | 3.75 | 3.9  | 4.05 |       |

|                                         |                                                                | UOK logic-low,<br>V <sub>BUS</sub> falling                   | USB 2.0 high-power device                                      | 3.95 | 4.1  | 4.25 |       |

| USB Overvoltage Protection<br>Threshold |                                                                | UOK logic-low, V <sub>BUS</sub> rising, 100mV hysteresis     |                                                                | 6.7  | 6.9  | 7.1  | V     |

## JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

### **ELECTRICAL CHARACTERISTICS (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT\_PWRON}$ ,  $\overline{UOK}$ ,  $\overline{IRQ}$ , CHG\_TYPE, and  $\overline{CHG\_STAT}$  are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                                     | SYMBOL                 | CON                                                             | DITIONS                                       | MIN                        | TYP                         | MAX                         | UNITS |

|---------------------------------------------------------------|------------------------|-----------------------------------------------------------------|-----------------------------------------------|----------------------------|-----------------------------|-----------------------------|-------|

|                                                               | I <sub>DETECT</sub>    | Charge type detection I <sub>SYS</sub> = I <sub>BAT</sub> = 0mA | on,                                           |                            |                             | 0.5                         |       |

|                                                               | I <sub>ENUMERATE</sub> | USB 2.0 enumeration I <sub>SYS</sub> = I <sub>BAT</sub> = 0mA   | on in progress,                               |                            |                             | 100                         |       |

| USB Input Supply Current (Notes 3, 4)                         | ISUSPEND               | Suspended mode, I<br>VSTDB_EN_HW = 0V                           |                                               |                            |                             | 0.5                         | mA    |

|                                                               |                        | USB 2.0 low-power                                               | $T_A = 0$ °C to +85°C                         |                            |                             | 100                         |       |

|                                                               | I <sub>USB_100mA</sub> | device detected                                                 | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |                            |                             | 102.5                       |       |

|                                                               | I <sub>USB_500mA</sub> | USB 2.0 high-power                                              | r device detected                             |                            |                             | 500                         |       |

|                                                               | I <sub>SUS</sub>       | During suspend                                                  |                                               |                            | 0                           |                             |       |

|                                                               | I <sub>ENU</sub>       | During USB enumer                                               | ration, $T_A = +25^{\circ}C$                  | 80                         | 90                          | 98                          |       |

|                                                               | I <sub>USB_LP</sub>    | USB 2.0 low-power $T_A = +25^{\circ}C$                          | device detected,                              | 80                         | 90                          | 98                          |       |

|                                                               | I <sub>USB_HP</sub>    | USB 2.0 high-power                                              | r device detected                             | 460                        | 475                         | 490                         |       |

|                                                               |                        | ILIM = 000, T <sub>A</sub> = +25°C                              |                                               | 80                         | 90                          | 98                          |       |

| USB Input Current Limit                                       |                        | ILIM = 001 (default)                                            |                                               | 460                        | 475                         | 490                         | mA    |

|                                                               |                        | ILIM = 010<br>ILIM = 011<br>ILIM = 100<br>ILIM = 101            |                                               |                            | 600                         |                             |       |

|                                                               | I                      |                                                                 |                                               |                            | 700                         |                             |       |

|                                                               | ILIMIT                 |                                                                 |                                               |                            | 900                         |                             |       |

|                                                               |                        |                                                                 |                                               |                            | 1000                        |                             |       |

|                                                               |                        | $ILIM = 110, T_A = +2$                                          | 25°C (Note 3)                                 | 1344                       | 1500                        | 1650                        |       |

|                                                               |                        | $ILIM = 110, T_A = -40$                                         | 1324                                          | 1500                       | 1700                        |                             |       |

| V <sub>BUS_</sub> to V <sub>SYS_</sub><br>On-Resistance       |                        | V <sub>BUS</sub> = 5V, I <sub>SYS</sub> = 4                     | 100mA                                         |                            | 200                         | 320                         | mΩ    |

| V <sub>SYS</sub> _to V <sub>BAT</sub> _ Reverse<br>Regulation |                        | When SYS is in regulators, V <sub>SYS</sub> falling, hysteresis | ulation and charging<br>50mV typical          | V <sub>BAT</sub> -<br>80mV | V <sub>BAT</sub> -<br>50mV  | V <sub>BAT</sub> -<br>20mV  |       |

| Input Limiter Soft-Start Time                                 |                        | Input current ramp t                                            | ime                                           |                            | 50                          | 100                         | μs    |

|                                                               |                        | THERM_REG = 00                                                  |                                               |                            | 90                          |                             |       |

| Thermal-Limit Start                                           | <b>-</b>               | THERM _REG = 01                                                 |                                               |                            | 100                         |                             |       |

| Temperature                                                   | T <sub>DIE_LIM</sub>   | THERM _REG = 10                                                 |                                               |                            | 110                         |                             | °C    |

|                                                               |                        | THERM _REG = 11                                                 |                                               |                            |                             |                             |       |

| Thermal-Limit Triggers IRQ                                    |                        |                                                                 |                                               | T <sub>D</sub>             | IE_LIM + 1                  | 0°C                         | °C    |

| Thermal-Limit Gain                                            |                        | I <sub>SYS</sub> reduction/die te                               | emperature                                    |                            | 5                           |                             | %/°C  |

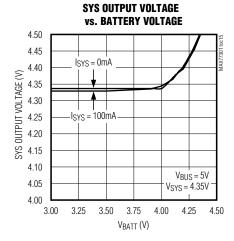

| SYS Regulation Voltage                                        |                        | V <sub>BAT</sub> > 3.45V, I <sub>SYS</sub>                      | = 1mA to 1.6A                                 |                            | 140mV<br>+ V <sub>BAT</sub> | 210mV<br>+ V <sub>BAT</sub> | V     |

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

### **ELECTRICAL CHARACTERISTICS (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT\_PWRON}$ ,  $\overline{UOK}$ ,  $\overline{IRQ}$ , CHG\_TYPE, and  $\overline{CHG\_STAT}$  are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                         | SYMBOL                              |                                           | CONDITIONS                                         |                                 | MIN   | TYP  | MAX     | UNITS     |  |

|-----------------------------------|-------------------------------------|-------------------------------------------|----------------------------------------------------|---------------------------------|-------|------|---------|-----------|--|

|                                   |                                     |                                           | V_SYS = 00                                         |                                 |       | 3.4  |         |           |  |

|                                   |                                     |                                           |                                                    | T <sub>A</sub> = 25°C           | 4.2   | 4.35 | 4.524   |           |  |

| Minimum SYS Regulation<br>Voltage | V <sub>SYS_MIN</sub> I <sub>S</sub> | $V_{BUS} = 6V$ , $I_{SYS} = 1$ mA to 1.6A | V_SYS = 01                                         | T <sub>A</sub> = -40°C to +85°C | 4.185 | 4.35 | 4.524   | V         |  |

|                                   |                                     |                                           | V_SYS = 10                                         |                                 |       | 4.4  |         | ]         |  |

|                                   |                                     |                                           | V_SYS = 11                                         |                                 |       | 4.5  |         |           |  |

| Lindaryoltaga Lagikayit           | V                                   | V <sub>BUS_</sub> = 5.5V r                | rising                                             |                                 |       | 3.0  |         | V         |  |

| Undervoltage Lockout              | V <sub>SYS_UVLO</sub>               | $V_{BUS} = 5.5V f$                        | falling                                            |                                 | 2.6   | 2.85 | 3.1     | ]         |  |

| CHARGER                           |                                     |                                           |                                                    |                                 |       |      |         |           |  |

| BAT-to-SYS On-Resistance          |                                     | $V_{BAT} = 4.2V, I_{S}$                   | SYS = 200mA                                        |                                 |       | 55   | 80      | mΩ        |  |

|                                   | V <sub>BAT_UVLO_F</sub>             | V <sub>BAT</sub> falling                  | BAT_UVLO_VP                                        |                                 | 2.15  | 2.40 | 2.65    |           |  |

| BAT Undervoltage Lockout          | V <sub>BAT_UVLO_R</sub>             | V <sub>BAT</sub> rising                   | (Register 0x10h                                    | 1)                              | 2.45  | 2.70 | 70 2.95 | V         |  |

| (Register $0x10h$ , Bit $7 = 0$ ) | V <sub>BAT_UVLO_F</sub>             | V <sub>BAT</sub> falling                  | BAT_UVLO_VPREQ = 0<br>(default, Register 0x10h)    |                                 | 1.60  | 1.85 | 2.10    | _         |  |

|                                   | V <sub>BAT_UVLO_R</sub>             | V <sub>BAT</sub> rising                   |                                                    |                                 | 1.85  | 2.10 | 2.35    |           |  |

| Charger Soft-Start Time           |                                     |                                           |                                                    |                                 |       | 1    |         | ms        |  |

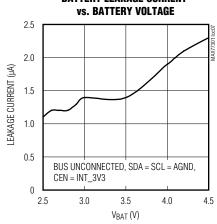

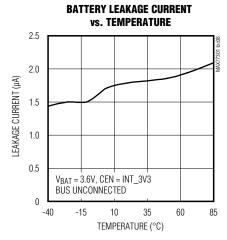

|                                   |                                     | $V_{BAT} = 4.2V$                          | V <sub>BUS</sub> not conne                         | ected                           |       | 2    | 6       |           |  |

| BAT Leakage Current               |                                     |                                           | V <sub>BUS</sub> connecte<br>V <sub>CEN</sub> = 0V | d,                              |       | 6    | 15      | μA        |  |

| PRECHARGE MODE                    |                                     |                                           |                                                    |                                 |       |      |         |           |  |

| BAT Precharge Current             | l <sub>PCHG</sub>                   | V <sub>BAT</sub> > 1.4V (N                | Note 5)                                            |                                 |       | 50*  |         | mA        |  |

|                                   | V <sub>BAT_PCHG_F</sub>             | V <sub>BAT</sub> falling                  | BAT_UVLO_VP                                        | REQ = 1                         | 2.60  | 2.70 | 2.80    |           |  |

| BAT Prequalification              | V <sub>BAT_PCHG_R</sub>             | V <sub>BAT</sub> rising                   | (Register 0x10h                                    | 1)                              | 2.70  | 2.80 | 2.95    | V         |  |

| Threshold                         | V <sub>BAT_PCHG_F</sub>             | V <sub>BAT</sub> falling                  | BAT_UVLO_VP                                        | REQ = 0                         | 2.05  | 2.15 | 2.25    | ]         |  |

|                                   | V <sub>BAT_PCHG_R</sub>             | V <sub>BAT</sub> rising                   | (default, Regist                                   | er 0x10h)                       | 2.15  | 2.25 | 2.40    |           |  |

| FAST-CHARGE MODE                  |                                     |                                           |                                                    |                                 |       |      |         |           |  |

|                                   |                                     | I <sub>FCHG</sub> = 000                   |                                                    |                                 |       | 100  |         |           |  |

|                                   |                                     | I <sub>FCHG</sub> = 010 (d                | default)                                           |                                 |       | 200  |         |           |  |

|                                   |                                     | I <sub>FCHG</sub> = 001                   |                                                    |                                 |       | 300  |         |           |  |

| BAT Charge-Current Set            | l==                                 | I <sub>FCHG</sub> = 110                   |                                                    |                                 |       | 370  |         | , ma ^    |  |

| Range                             | I <sub>FCHG</sub>                   | I <sub>FCHG</sub> = 111                   |                                                    |                                 |       | 450  |         | - mA<br>- |  |

|                                   |                                     | I <sub>FCHG</sub> = 011                   |                                                    |                                 |       | 600  |         |           |  |

|                                   |                                     | I <sub>FCHG</sub> = 100                   |                                                    |                                 |       | 800  |         |           |  |

|                                   |                                     | I <sub>FCHG</sub> = 101                   |                                                    |                                 |       | 900  |         |           |  |

## JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

### **ELECTRICAL CHARACTERISTICS (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT\_PWRON}$ ,  $\overline{UOK}$ ,  $\overline{IRQ}$ , CHG\_TYPE, and  $\overline{CHG\_STAT}$  are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                 | SYMBOL               | CON                                                    | DITIONS                 |                               | MIN               | TYP                        | MAX   | UNITS |  |

|---------------------------|----------------------|--------------------------------------------------------|-------------------------|-------------------------------|-------------------|----------------------------|-------|-------|--|

|                           |                      | V <sub>BAT</sub> rising                                | BAT_FCHG                | G = 00                        |                   | 3.8                        |       |       |  |

|                           |                      | threshold, where                                       | BAT_FCHO                | G = 01                        |                   | 3.9                        |       |       |  |

|                           | VBAT_FCHG_R          | charging current I <sub>FCHG</sub> is reduced          | BAT_FCH0<br>(default)   | G = 10                        | 3.88              | 4                          | 4.12  | V     |  |

|                           |                      | to I <sub>TCHG</sub>                                   | BAT_FCHG                | G = 11                        |                   | 4.1                        |       |       |  |

| BAT Fast-Charge Threshold |                      | V <sub>BAT</sub> hysteresis,<br>the falling threshold  | BAT_FCHO                | 3_HYS                         |                   | 150                        |       |       |  |

|                           | V                    | where charging current is increased                    | BAT_FCHC                | G_HYS =                       |                   | 200                        |       |       |  |

|                           | VBAT_FCHG_HYS        | to I <sub>FCHG</sub> is:<br>VBAT_FCHG_HYS              | BAT_FCHO<br>= 10        | G_HYS                         |                   | 250                        |       | - mV  |  |

|                           |                      | = V <sub>BAT_FCHG_R</sub> -<br>V <sub>BAT_FCHG_F</sub> | BAT_FCHO<br>= 11        | G_HYS                         |                   | 300                        |       |       |  |

| TOP-OFF CHARGE MODE       | T                    |                                                        | <del></del>             |                               |                   |                            |       |       |  |

|                           |                      | V <sub>BAT</sub> > 1.4V<br>(Note 5)                    | TCHG = 00               | )                             |                   | 0.4 x                      |       |       |  |

|                           |                      |                                                        |                         |                               |                   | IFCHG                      |       | -     |  |

|                           |                      |                                                        | TCHG = 0                | 1                             |                   | 0.6 x<br>I <sub>FCHG</sub> |       |       |  |

| Top-Off Charge Current    | ITCHG                |                                                        |                         |                               |                   | 0.8 x                      |       | mA    |  |

|                           |                      |                                                        | TCHG = 10               | )                             | I <sub>FCHG</sub> |                            |       |       |  |

|                           |                      |                                                        | TOLIC 1:                | 1 (dofolt)                    |                   | 1.0 x                      |       |       |  |

|                           |                      |                                                        | TCHG = 1                | (delauit)                     |                   | I <sub>FCHG</sub>          |       |       |  |

|                           |                      | CHG_DONE = 000                                         |                         |                               |                   | 10                         |       |       |  |

|                           |                      | CHG_DONE = 001                                         |                         |                               |                   | 20                         |       |       |  |

|                           |                      | CHG_DONE = 010                                         |                         |                               | 30                | 40                         | 50    |       |  |

| Charge DONE Qualification |                      | CHG_DONE = 011                                         |                         |                               | 37.5              | 50                         | 62.5  |       |  |

| (Note 3)                  | ICHG_DONE            | CHG_DONE = 100                                         | (default)               |                               | 45                | 60                         | 75    | mA    |  |

|                           |                      | CHG_DONE = 101                                         |                         |                               |                   | 80                         |       | 1     |  |

|                           |                      | CHG_DONE = 110                                         |                         |                               |                   | 100                        |       | 1     |  |

|                           |                      | CHG_DONE = 111                                         |                         |                               |                   | 120                        |       |       |  |

|                           |                      | В                                                      | AT_REG = 00             | )                             |                   | 4.05                       |       |       |  |

|                           |                      | В                                                      | AT_REG = 01             | 1                             |                   | 4.10                       |       |       |  |

|                           |                      | В                                                      | $AT_REG = 10$           | )                             |                   | 4.15                       |       |       |  |

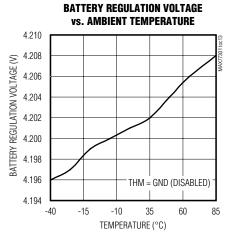

| BAT Regulation Voltage    | V <sub>BAT_REG</sub> | I <sub>BAT</sub> = 0mA                                 | AT DEC                  | T <sub>A</sub> = +25°C        | 4.179             | 4.200                      | 4.221 | V     |  |

|                           |                      |                                                        | AT_REG =<br>1 (default) | T <sub>A</sub> = 0°C to +85°C | 4.158             | 4.200                      | 4.242 |       |  |

## JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

### **ELECTRICAL CHARACTERISTICS (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT\_PWRON}$ ,  $\overline{UOK}$ ,  $\overline{IRQ}$ , CHG\_TYPE, and  $\overline{CHG\_STAT}$  are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                 | SYMBOL                  | C                                                                                  | OND                      | ITIONS                                                 | MIN   | TYP  | MAX   | UNITS   |

|---------------------------|-------------------------|------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------|-------|------|-------|---------|

|                           |                         |                                                                                    |                          | T_RECHG = 00<br>fault)                                 |       | -350 |       |         |

| BAT Recharge Threshold    | V <sub>BAT_REC</sub> HG | With respect to VBAT_REG                                                           | BA                       | Γ_RECHG = 10                                           |       | -300 |       | mV      |

|                           |                         |                                                                                    | BA                       | Γ_RECHG = 01                                           |       | -250 |       | 1       |

|                           |                         |                                                                                    | BA                       | Γ_RECHG = 11                                           |       | -200 |       |         |

| CHARGE TIMER              |                         |                                                                                    |                          |                                                        |       |      |       | •       |

|                           |                         | From start of                                                                      |                          | PCHG_TMR = 00                                          |       | 30   |       |         |

|                           |                         | precharge until                                                                    | end                      | PCHG_TMR = 01                                          |       | 60   |       |         |

| Prequalification Timer    | <sup>t</sup> PCHG       | of prequalification charge model                                                   | n                        | PCHG_TMR = 10<br>(default)                             |       | 120  |       | Minutes |

|                           |                         | (Figure 10)                                                                        |                          | PCHG_TMR = 11                                          |       | 240  |       |         |

|                           |                         |                                                                                    |                          | FCHG_TMR = 00                                          |       | 75   |       |         |

|                           |                         | From start of                                                                      |                          | FCHG_TMR = 01                                          |       | 150  |       |         |

| Fast-Charge Timer         | t <sub>FCHG</sub>       | fast charge until maintains charge                                                 |                          | FCHG_TMR = 10                                          |       | 300  |       | Minutes |

|                           |                         | , ,                                                                                | FCHG_TMR = 11<br>Default |                                                        | 600   |      |       |         |

|                           |                         |                                                                                    |                          | MTCHG_TMR = 10 (default)                               |       | 0    |       |         |

| Maintain-Charge Timer     | <sup>t</sup> MTCHG      | (Figure 11)                                                                        |                          | MTCHG_TMR = 01                                         |       | 15   |       | Minutes |

| _                         |                         |                                                                                    |                          | MTCHG_TMR = 00                                         |       | 30   |       |         |

|                           |                         |                                                                                    |                          | MTCHG_TMR = 11                                         |       | 60   |       | ]       |

| Timer Accuracy            |                         |                                                                                    |                          |                                                        | -30   |      | +30   | %       |

| Timer Extend Threshold    |                         | Percentage of cl                                                                   |                          | e current below which at half speed                    |       | 50   |       | %       |

| Timer Suspend Threshold   |                         | Percentage of cl<br>timer clock paus                                               |                          | e current below which                                  |       | 20   |       | %       |

| INSERTION AND REMOVAL     | DETECTION               | •                                                                                  |                          |                                                        |       |      | ,     |         |

| BAT Discharge Current     | I <sub>DIS</sub>        | $1V \le V_{BAT} \le 4.2V_{BAT}$                                                    | √, C <sub>B</sub>        | <sub>AT</sub> ≤ 10μF                                   | 0.375 |      | 1.125 | mA      |

| BAT Discharge Time        | t <sub>DIS</sub>        |                                                                                    |                          | res if V <sub>BAT</sub> drop ><br>, battery cap ≤ 10µF |       | 150  |       | ms      |

| Charge Debounce Timer     | t <sub>DB</sub>         | Delay before checking charge done                                                  |                          | 100                                                    | 150   | 200  | ms    |         |

| Battery Detecting Current | I <sub>BAT</sub> DET    | Charging in proc<br>charge or mainta<br>if I <sub>BAT</sub> < I <sub>BAT</sub> _DE | ain ch                   |                                                        | 1     | 3    | 5     | mA      |

| ADAPTER TYPE DETECTION    | N                       |                                                                                    |                          |                                                        |       |      |       |         |

| D- Current Sink           | I <sub>DM_SINK</sub>    |                                                                                    |                          |                                                        | 50    | 100  | 150   | μΑ      |

| D+ Current source         | I <sub>DP_SRC</sub>     |                                                                                    |                          |                                                        | 7     |      | 13    | μΑ      |

## JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

### **ELECTRICAL CHARACTERISTICS (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT\_PWRON}$ ,  $\overline{UOK}$ ,  $\overline{IRQ}$ , CHG\_TYPE, and  $\overline{CHG\_STAT}$  are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                | SYMBOL                 | CONDITIONS                                                                                                                                        | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| D- Weak Current Sink                     | I <sub>DM_CD_PD</sub>  |                                                                                                                                                   |       |       | 0.1   | μΑ    |

| D+ Source Voltage                        | V <sub>DP_SRC</sub>    | I <sub>DP_SRC</sub> = 200μA                                                                                                                       | 0.5   | 0.6   | 0.7   | V     |

| D+ Detection Threshold                   | V <sub>DAT_REF</sub>   |                                                                                                                                                   | 0.25  | 0.32  | 0.40  | V     |

| D- Logic-High Threshold                  | V <sub>DM_IH</sub>     |                                                                                                                                                   | 0.8   |       | 2.0   | V     |

| D+ Logic-High Threshold                  | V <sub>DP_IH</sub>     |                                                                                                                                                   | 0.8   |       | 2.0   | V     |

|                                          | DP_25%<br>DM_25%       |                                                                                                                                                   | 23.75 | 25.0  | 26.25 |       |

|                                          | DM_34%                 | Detection threshold for custom                                                                                                                    | 32.3  | 34    | 35.7  | ]     |

| D+/D- Detection Threshold                | DP_47%<br>DM_47%       | chargers as % of V <sub>BUS</sub>                                                                                                                 | 44.65 | 47.00 | 49.4  | %     |

|                                          | DP_60%<br>DM_60%       |                                                                                                                                                   | 57    | 60    | 63    |       |

| D- Pulldown Resistor                     | R <sub>DM_DWN</sub>    |                                                                                                                                                   | 14.25 |       | 24.8  | kΩ    |

| D- Pullup Resistor                       | R <sub>DM_PU</sub>     | External resistor = $33\Omega$ , low speed only                                                                                                   | 1.425 | 1.500 | 1.575 | kΩ    |

| D+ Pullup Resistor                       | R <sub>DP_PU</sub>     | External resistor = $33\Omega$ , full speed only                                                                                                  | 1.425 | 1.500 | 1.575 | kΩ    |

| D+ Charger Detection<br>Pullup Resistor  | R <sub>DP_CD_PU</sub>  | R <sub>DP_CD_PU</sub> connected to INT_3V3                                                                                                        | 200   | 330   | 600   | kΩ    |

| Data Contact Detection<br>Debounce Timer | tDCD_DBNC              |                                                                                                                                                   |       | 30    |       | ms    |

| D+ Source On Time                        | t <sub>DP_SRC_ON</sub> |                                                                                                                                                   | 100   |       |       | ms    |

| D+ Source to High-Current<br>Time        | <sup>t</sup> DP_SRC_HC |                                                                                                                                                   | 40    |       |       | ms    |

| Enumeration Time Limit                   | <sup>t</sup> ENUM      | Time from start of enumeration process until enumeration                                                                                          |       | 10    |       | S     |

| Reenumeration Timer                      | <sup>t</sup> RE_ENUM   | Time from suspend mode until it re-<br>enumerates, RWU_EN = 1                                                                                     |       | 100   |       | ms    |

| Reconnect Timer                          | <sup>†</sup> FAULT     | Time from failed enumeration to adapter type detection reenabled, nENU_EN = 0                                                                     |       | 3     |       | S     |

| Detecting Time                           |                        | D+/D- open power source nENU_EN = 1                                                                                                               |       | 100   |       | ms    |

| Enumeration Fail to<br>Reconnect Timer   | <sup>†</sup> ENU_FAULT | Time from enumeration fail at 500mA until enumeration is retried at 100mA or time from enumeration fail at 100mA until reconnect timer is started |       | 87    |       | ms    |

| XIN, XOUT PINS                           |                        |                                                                                                                                                   |       |       |       |       |

| Oscillator Frequency<br>Accuracy         |                        | Internal oscillator (low speed),<br>T <sub>A</sub> = +25°C                                                                                        | 5.91  | 6.00  | 6.09  | MHz   |

| XIN, XOUT Input<br>Capacitance           |                        | With external crystal (full speed)                                                                                                                |       | 3     |       | pF    |

## JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

### **ELECTRICAL CHARACTERISTICS (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT\_PWRON}$ ,  $\overline{UOK}$ ,  $\overline{IRQ}$ , CHG\_TYPE, and  $\overline{CHG\_STAT}$  are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                                 | SYMBOL                     | CONDITIONS                                               |                                               | MIN                             | TYP   | MAX                  | UNITS                |

|-----------------------------------------------------------|----------------------------|----------------------------------------------------------|-----------------------------------------------|---------------------------------|-------|----------------------|----------------------|

| XIN Input Current                                         |                            | With external crystal                                    | (full speed)                                  |                                 |       | 10                   | μΑ                   |

| XIN Logic-High Input<br>Voltage                           |                            |                                                          |                                               | 0.667 x<br>V <sub>INT_3V3</sub> |       | V <sub>INT_3V3</sub> | V                    |

| XIN Logic-Low Input<br>Voltage                            |                            |                                                          |                                               |                                 |       | 0.4                  | V                    |

| THERMISTOR MONITOR (T                                     | НМ)                        |                                                          |                                               |                                 |       |                      |                      |

| THM Hot Threshold                                         | T <sub>4</sub>             | V <sub>THM</sub> raising, 2% hys                         | steresis                                      |                                 | 32.2  |                      |                      |

| THM Warm Threshold                                        | T <sub>3</sub>             | V <sub>THM</sub> raising, 2% hys                         | steresis                                      |                                 | 46.5  |                      | % of                 |

| THM Cool Threshold                                        | T <sub>2</sub>             | V <sub>THM</sub> falling, 2% hys                         | teresis                                       |                                 | 81.9  |                      | V <sub>INT_3V3</sub> |

| THM Cold Threshold                                        | T <sub>1</sub>             | V <sub>THM</sub> falling, 2% hys                         | teresis                                       |                                 | 88.7  |                      |                      |

| THM Disable Threshold                                     |                            | V <sub>THM</sub> falling, 2% hys                         | teresis                                       |                                 | 3.4   |                      |                      |

| THM Input Impedance                                       | THM <sub>ZIN</sub>         | High impedance who                                       | en no BUS or THM is                           | 500                             |       |                      | kΩ                   |

| T. 18.4.1                                                 |                            | THM = AGND                                               | $T_A = +25^{\circ}C$                          | -1                              | 0.001 | +1                   |                      |

| THM Input Leakage                                         |                            | THERM_EN = 0                                             | T <sub>A</sub> = +85°C                        |                                 | 0.01  |                      | μΑ                   |

| EXT_PWRON                                                 | I                          | <u> </u>                                                 |                                               |                                 |       |                      | Į.                   |

| Logic-Low Output Voltage                                  |                            | Sinking 10mA                                             |                                               |                                 | 35    | 100                  | mV                   |

| High-Impedance Time                                       | <sup>t</sup> EXT_PWR_RESET | Time where EXT_PW impedance during tra EXT_PWRON low sta | ansition between two                          |                                 | 63    |                      | ms                   |

| CHARGER STATUS (CHG_S                                     | STAT)                      |                                                          |                                               | 1                               |       |                      | L                    |

| Logic-Low Output Voltage                                  | ,                          | Sinking 10mA                                             |                                               |                                 | 35    | 100                  | mV                   |

| Blink Period for<br>Temperature Suspend<br>Mode           |                            | 50% duty cycle, batte                                    | ery present                                   |                                 | 1.5   |                      | S                    |

| Blink Period for Timeout<br>Mode                          |                            | 50% duty cycle, batte                                    | ery present                                   |                                 | 0.15  |                      | S                    |

| LOGIC I/O: UOK, CEN, ENU                                  | _EN_HW, CHG_T              | YPE, IBUS_DEF, IRQ                                       | , SDA, SCL, STDB_E                            | N_HW                            |       |                      |                      |

|                                                           |                            | High level                                               |                                               | 1.3                             |       |                      |                      |

| Logic Input Voltage                                       |                            | High level for SDA and SCL                               |                                               | 1.4                             |       |                      | V                    |

|                                                           |                            | Low level                                                |                                               |                                 |       | 0.4                  |                      |

| Logic Input-Leakage                                       |                            | $V_{BUS} = 0V \text{ to } 5.5V$                          | $T_{A} = +25^{\circ}C$ $T_{A} = +85^{\circ}C$ |                                 | 0.001 | 1                    | μΑ                   |

| Current                                                   |                            | AROS - 04 (0.9.94                                        | $T_A = +85^{\circ}C$                          |                                 | 0.01  |                      | μΑ                   |

| Logic-Low Output Voltage<br>(CHG_TYPE, IRQ, UOK,<br>Only) |                            | Sinking 10mA                                             |                                               |                                 | 35    | 100                  | mV                   |

## JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

### **ELECTRICAL CHARACTERISTICS (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT\_PWRON}$ ,  $\overline{UOK}$ ,  $\overline{IRQ}$ , CHG\_TYPE, and  $\overline{CHG\_STAT}$  are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                    | SYMBOL                               | CONE                                                    | DITIONS                                                             | MIN | TYP   | MAX | UNITS |

|----------------------------------------------|--------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------|-----|-------|-----|-------|

| Logic-High Output-Leakage                    |                                      |                                                         | $T_A = +25^{\circ}C$                                                |     | 0.001 | 1   |       |

| Current (CHG_TYPE, IRQ, UOK, Only)           |                                      | $V_{SYS} = 5.5V$                                        | T <sub>A</sub> = +85°C                                              |     | 0.01  |     | μΑ    |

| UOK Blink Period During                      |                                      | Only for USB automa                                     |                                                                     |     | 1.5   |     | s     |

| USB Suspend                                  |                                      | suspend mode, 50%                                       | duty cycle                                                          |     |       |     |       |

| UOK Blink Period with Open D+/D- Detected    |                                      | 50% duty cycle                                          |                                                                     |     | 0.15  |     | S     |

| I <sup>2</sup> C INTERFACE (See Figure       | e 19) (Note 3)                       |                                                         |                                                                     |     |       |     |       |

| Clock Frequency                              |                                      |                                                         |                                                                     |     |       | 400 | kHz   |

| Bus-Free Time Between<br>START and STOP      | t <sub>BUF</sub>                     |                                                         |                                                                     | 1.3 |       |     | μs    |

| Hold Time Repeated START Condition           |                                      |                                                         |                                                                     | 0.6 |       |     | μs    |

| SCL Low Period                               | t <sub>LOW</sub>                     |                                                         |                                                                     | 1.3 |       |     | μs    |

| SCL High Period                              | tHIGH                                |                                                         |                                                                     | 0.6 |       |     | μs    |

| Setup Time Repeated<br>START Condition       | t <sub>SU_STA</sub>                  |                                                         |                                                                     | 0.6 |       |     | μs    |

| SDA Hold Time                                | tHD_DAT                              |                                                         |                                                                     | 0   |       | ,   | μs    |

| SDA Setup Time                               | t <sub>SU_DAT</sub>                  |                                                         |                                                                     | 100 |       |     | ns    |

| Maximum Suppressed<br>Pulse Width            | -                                    | Width of spikes that by the input filter of the signals |                                                                     |     | 50    |     | ns    |

| Setup Time for STOP<br>Condition             | tsu_sto                              |                                                         |                                                                     | 0.6 |       |     | μs    |

| USB DATA INTERFACE                           |                                      |                                                         |                                                                     |     |       |     |       |

| Differential-Receiver Input<br>Sensitivity   | IV <sub>D+</sub> - V <sub>D-</sub> I |                                                         |                                                                     | 0.2 |       |     | V     |

| Differential-Receiver<br>Common-Mode Voltage |                                      |                                                         |                                                                     | 0.8 |       | 2.5 | V     |

| D+, D- Input Impedance                       |                                      |                                                         |                                                                     | 300 |       |     | kΩ    |

| D+, D- Output Low Voltage                    | V <sub>OL</sub>                      | $R_{LOAD} = 1.5k\Omega$ from                            | 1 V <sub>D-</sub> to 3.6V                                           |     |       | 0.3 | V     |

| D+, D- Output High Voltage                   | V <sub>OH</sub>                      | $R_{LOAD} = 15k\Omega$ from                             | D+ and D- to AGND                                                   | 2.8 |       | 3.6 | V     |

| Driver Output Impedance                      |                                      | Excludes external re                                    | sistor                                                              | 2   | 7     | 11  | Ω     |

| BUS Idle Time                                | <sup>†</sup> IDLE                    |                                                         | adapter type is<br>2.0 device; time BUS is<br>ng current is reduced |     | 3     |     | ms    |

### JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

#### **ELECTRICAL CHARACTERISTICS (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT\_PWRON}$ ,  $\overline{UOK}$ ,  $\overline{IRQ}$ , CHG\_TYPE, and  $\overline{CHG\_STAT}$  are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                          | SYMBOL            | CONDITIONS                                                                   | MIN TYP MAX |        | UNITS |     |  |

|------------------------------------|-------------------|------------------------------------------------------------------------------|-------------|--------|-------|-----|--|

| USB Host Remote Wake-Up Timer      | t <sub>RWU</sub>  | Time delay from suspend mode until it requests the host for a remote wake-up |             | 100    |       | ms  |  |

| D. D. Dina Tima (Nata 2)           |                   | $C_L = 50pF$ to 600pF, low speed only                                        | 75          |        | 250   |     |  |

| D+, D- Rise Time (Note 3)          | t <sub>RISE</sub> | C <sub>L</sub> = 50pF, full speed only                                       | 4           |        | 20    | ns  |  |

| D. D. F-II Time - (NI-t- 0)        |                   | C <sub>L</sub> = 50pF to 600pF, low speed only                               | 75          | 75 250 |       |     |  |

| D+, D- Fall Time (Note 3)          | t <sub>FALL</sub> | C <sub>L</sub> = 50pF to 600pF, full speed only                              | 4           |        | 20    | ns  |  |

| Rise/Fall-Time Matching            |                   | C <sub>L</sub> = 50pF to 600pF, low speed only                               | 80          |        | 120   | 0/  |  |

| (Note 3)                           |                   | C <sub>L</sub> = 50pF to 600pF, full speed only                              | 90          |        | 110   | - % |  |

| Output-Signal Crossover<br>Voltage |                   | C <sub>L</sub> = 50pF to 600pF, low speed only                               | 1.3         |        | 2.0   | V   |  |

| INT_3V3 REGULATOR                  |                   |                                                                              |             |        |       |     |  |

| INT_3V3 Voltage                    |                   | $V_{BUS} = 5V$ , $I_{INT\_3V3} = 0$ to 10mA                                  | 3.0         | 3.3    | 3.6   | V   |  |

| ESD PROTECTION (D+, D-, I          | BUS_)             |                                                                              |             |        |       |     |  |

| Human Body Model                   |                   | BUS bypassed with 1µF to AGND                                                |             | ±8     | ·     | kV  |  |

- Note 2: Specifications are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design and characterization.

- Note 3: Guaranteed by design. Limits not production tested.

- Note 4: Sum of input current limit and current used for INT\_3V3.

- Note 5: Maximum charging current is adaptively regulated to IILIM ISYS though maximum ICHG.

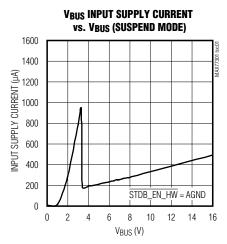

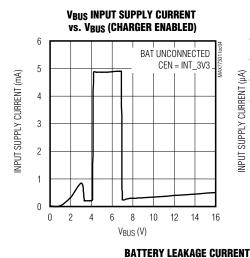

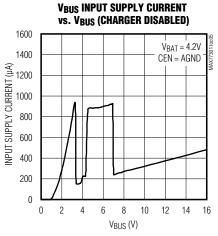

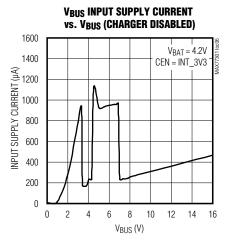

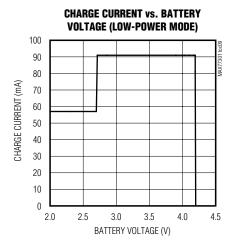

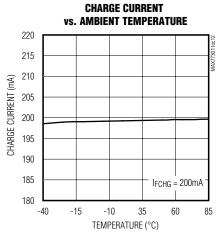

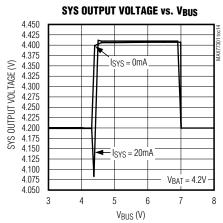

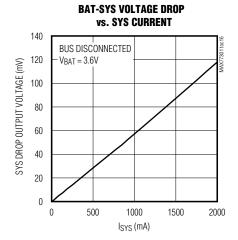

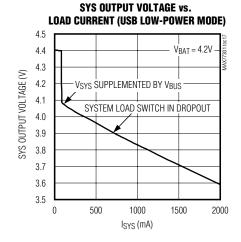

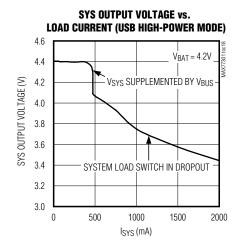

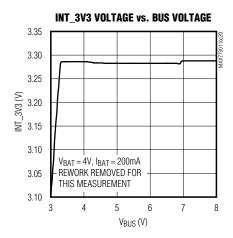

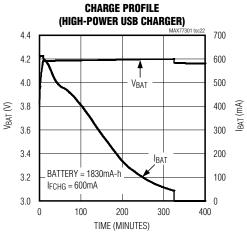

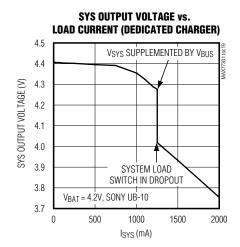

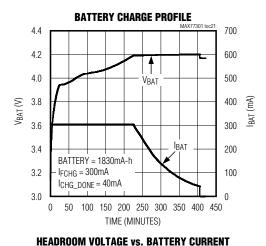

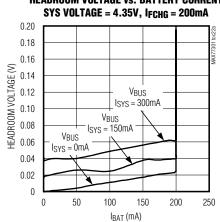

#### **Typical Operating Characteristics**

(Circuit of Figure 1,  $T_A = +25$ °C unless otherwise noted.)

### JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

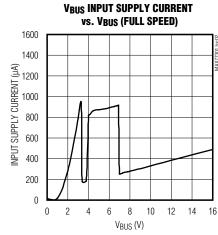

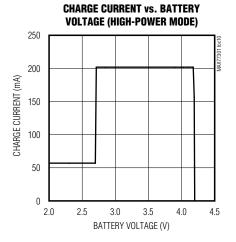

#### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $T_A = +25$ °C unless otherwise noted.)

### JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

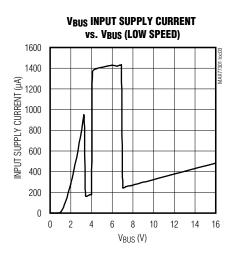

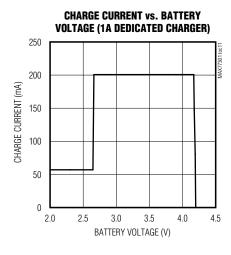

#### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $T_A = +25$ °C unless otherwise noted.)

### JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

#### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $T_A = +25$ °C unless otherwise noted.)

## JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

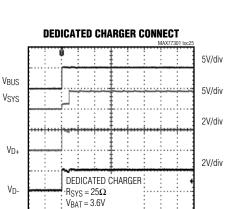

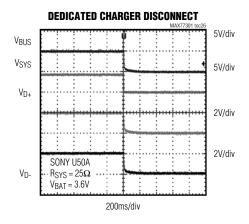

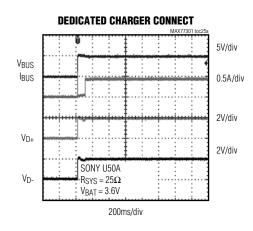

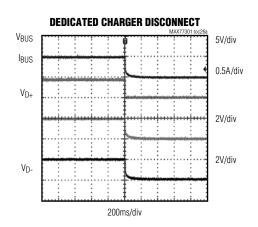

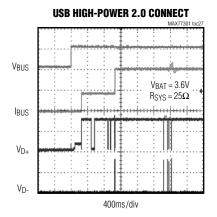

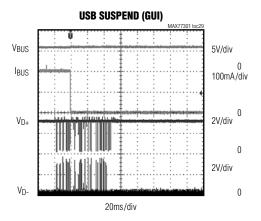

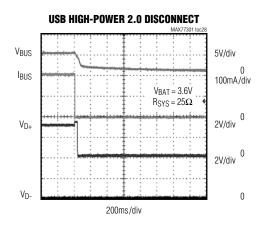

#### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $T_A = +25$ °C unless otherwise noted.)

200ms/div

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

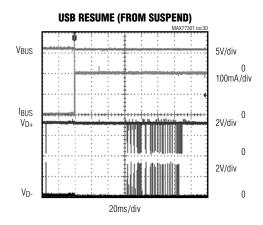

#### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $T_A = +25$ °C unless otherwise noted.)

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

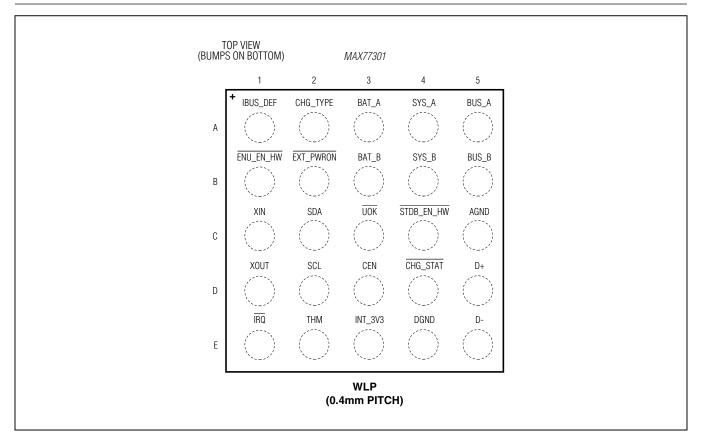

#### **Bump Configuration**

#### **Bump Description**

| BUMP   | NAME           | FUNCTION                                                                                                                                                                                                                                             |                                                   |

|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| A1     | IBUS_DEF       | Logic Input that Sets Input Current Limit. Only valid when enumeration is disabled or D+/D- are open. Logic-high programs the ILIM[2:0] register value. Logic-low sets the input current limit at 100mA.                                             |                                                   |

|        |                | Low                                                                                                                                                                                                                                                  | Input current limit = 100mA                       |

|        |                | High                                                                                                                                                                                                                                                 | Input current limit = ILIM[2:0] (default = 500mA) |

| A2     | CHG_TYPE       | Open-drain Output. Used to signal to the processor the current capability of the external adapter. Connect this pin to ground if not used.                                                                                                           |                                                   |

|        |                | CHG_TYPE                                                                                                                                                                                                                                             | ADPATER TYPE                                      |

|        |                | Low                                                                                                                                                                                                                                                  | USB 2.0 host 100mA or ILIM = 100mA                |

|        |                | High impedance                                                                                                                                                                                                                                       | ILIMIT≥ 500mA                                     |