Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **MAX86160**

# Integrated Heart-Rate Sensor for In-Ear Applications

## **General Description**

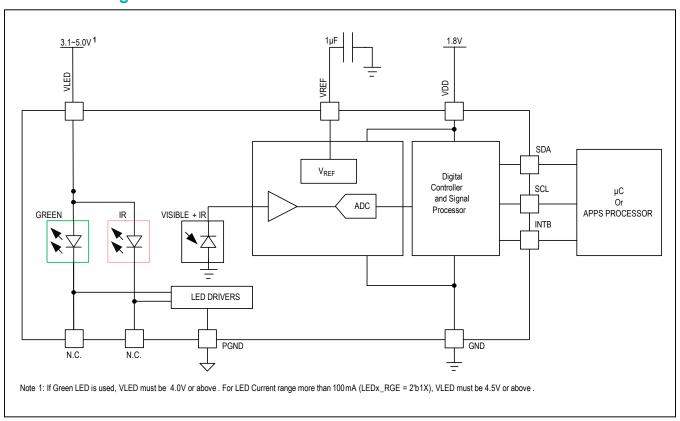

The MAX86160 is an integrated heart rate monitor sensor module designed for the demanding requirements of mobile, wearable, and hearable devices. It includes internal LEDs, photo-detector, and low-noise electronics with high-dynamic-range ambient light rejection. This integrated product is a complete system solution, and comes with plug-and-play software and robust algorithms to give meaningful outputs to the user with minimal additional design effort. The MAX86160 sensor module takes care of the most challenging parts of the design for fast time-to-market in mobile and wearable devices.

The MAX86160 operates on a 1.8V supply voltage, with a separate 3.3V/5.0V power supply for the internal LEDs. Communication to and from the module occurs entirely through a standard I<sup>2</sup>C-compatible interface. The module can be shut down through software with near zero standby current, allowing the power rails to remain powered at all times.

#### **Benefits and Features**

- Miniature 4.3mm x 2.8mm x 1.45mm 18-pin Optical Module

- Optical-Grade, Robust Glass Eliminates Customer Cover Glass

- High In-Band 13Hz Signal-to-Noise Ratio (SNR) Reflective Heart Rate Monitor and Medical-Grade Pulse Oximeter

- Ultra Low-Power Operation for Mobile Device

- Zero-Power Shutdown Current (0.7μA, typ)

- -40°C to +85°C Operating Temperature Range

## **Applications**

- Wearable and Hearable Devices

- Smartphones/Tablets

- Disposable Patch Sensors

- Fitness Assistant Devices

Ordering Information appears at end of data sheet.

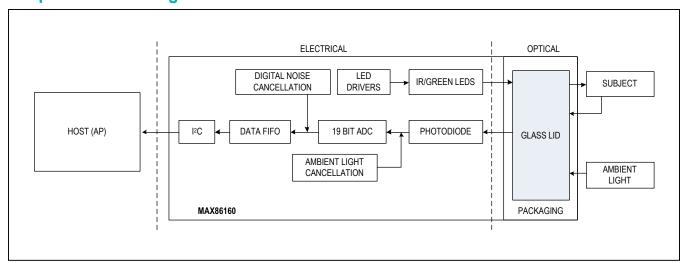

## **Simplified Block Diagram**

## **TABLE OF CONTENTS**

| General Description                                                    | 1  |

|------------------------------------------------------------------------|----|

| Benefits and Features                                                  | 1  |

| Applications                                                           | 1  |

| Simplified Block Diagram                                               | 1  |

| Absolute Maximum Ratings                                               | 6  |

| Package Information                                                    | 6  |

| 18-Lead OESIP                                                          | 6  |

| Electrical Characteristics                                             | 7  |

| Typical Operating Characteristics                                      | 10 |

| Pin Configurations                                                     |    |

| Pin Description                                                        |    |

| Functional Diagram                                                     | 12 |

| Detailed Description                                                   | 13 |

| HRM Subsystem                                                          | 13 |

| LED Driver                                                             | 13 |

| Proximity Function                                                     | 13 |

| Register Map                                                           | 13 |

| Interrupt Status 1 (0x00)                                              | 15 |

| A_FULL: FIFO Almost Full Flag                                          | 15 |

| PPG_RDY: New PPG FIFO Data Ready                                       | 15 |

| ALC_OVF: Ambient Light Cancellation Overflow                           | 15 |

| PROX_INT: Proximity interrupt                                          | 15 |

| PWR_RDY: Power Ready Flag                                              | 15 |

| Interrupt Status 2 (0x01)                                              | 16 |

| VDD_OOR: VDD Out-of-Range flag                                         | 16 |

| Interrupt Enable 1 (0x02)                                              | 16 |

| A_FULL_EN: FIFO Almost Full Flag enable                                | 16 |

| PPG_RDY_EN: New PPG FIFO Data Ready Interrupt enable                   | 16 |

| ALC_OVF_EN: Ambient Light Cancellation (ALC) Overflow Interrupt enable | 16 |

| PROX_INT_EN: Proximity Interrupt enable                                | 17 |

| Interrupt Enable 2 (0x03)                                              | 17 |

| VDD_OOR_EN: VDD Out-of-Range Indicator enable                          | 17 |

| FIFO Write Pointer (0x04)                                              | 17 |

| FIFO_WR_PTR: FIFO Write Pointer                                        | 17 |

| OVF_COUNTER: FIFO Overflow Counter                                     | 18 |

| FIFO Read Pointer (0x06)                                               | 18 |

| FIFO_RD_PTR: FIFO Read Pointer                                         | 18 |

## **TABLE OF CONTENTS (CONTINUED)**

| FIFO Data Register (0x07)                                                   | 18 |

|-----------------------------------------------------------------------------|----|

| FIFO_DATA: FIFO Data Register                                               | 18 |

| FIFO Configuration (0x08)                                                   | 18 |

| A_FULL_CLR: FIFO Almost Full Interrupt Options                              | 18 |

| A_FULL_TYPE: FIFO Almost Full Flag Options                                  | 19 |

| FIFO_ROLLS_ON_FULL: FIFO Rolls on Full Options                              | 19 |

| FIFO_A_FULL: FIFO Almost Full Value                                         | 19 |

| FIFO Data Control Register 1 (0x09)                                         | 19 |

| FD2: FIFO Data Time Slot 2                                                  | 20 |

| FD1: FIFO Data Time Slot 1                                                  | 20 |

| FD4: FIFO Data Time Slot 4                                                  | 20 |

| FD3: FIFO Data Time Slot 3                                                  | 21 |

| System Control (0x0D)                                                       | 21 |

| FIFO_EN: FIFO Enable                                                        | 21 |

| SHDN: Shutdown Control                                                      | 21 |

| RESET: Reset Control                                                        | 22 |

| PPG Configuration 1 (0x0E)                                                  | 22 |

| PPG_ADC_RGE: PPG ADC Range Control                                          | 22 |

| PPG_SR: PPG Sample Rate Control                                             |    |

| PPG Sample Rate Control                                                     | 22 |

| Maximum Sample rates Supported for all the Pulse Widths and Number of LEDs: |    |

| PPG_LED_PW: LED Pulse Width Control                                         | 23 |

| PPG Configuration 2 (0x0F)                                                  | 23 |

| SMP_AVE: Sample Averaging Options                                           | 23 |

| Prox Interrupt Threshold (0x10)                                             | 24 |

| PROX_INT_THRESH: Proximity Mode Interrupt Threshold                         | 24 |

| LED1 PA (0x11)                                                              | 24 |

| LED1_PA: LED 1 (IR) Current Pulse Amplitude                                 | 24 |

| LED3 PA (0x13).                                                             |    |

| LED3_PA: LED 3 (Green) Current Pulse Amplitude                              | 25 |

| LED Range (0x14).                                                           | 25 |

| LED3_PA: LED 3 (Green) Current Pulse Amplitude                              | 25 |

| LED1_RGE: LED 1 (IR) Current Control                                        | 26 |

| LED PILOT PA (0x15)                                                         | 26 |

| PILOT_PA: Proximity Mode LED Pulse Amplitude                                | 26 |

| Part ID (0xFF)                                                              | 26 |

| PART_ID: Part Identifier                                                    | 26 |

# TABLE OF CONTENTS (CONTINUED)

| Applications Information.                    |    |

|----------------------------------------------|----|

| Power Sequencing and Requirements            |    |

| Power-Up Sequencing                          |    |

| Power-Down Sequencing                        |    |

| I <sup>2</sup> C Interface                   |    |

| Bit Transfer                                 |    |

| START and STOP Conditions                    |    |

| Early STOP Conditions                        |    |

| Slave Address                                |    |

| Write Data Format                            |    |

| Read Data Format                             |    |

| FIFO Description                             |    |

| Overview                                     |    |

| FIFO Data Types                              |    |

| FIFO Data Control Registers                  |    |

| Write Pointer to the FIFO, FIFO_WR_PTR[4:0]: |    |

| Read Pointer to the FIFO, FIFO_RD_PTR[4:0]:  |    |

| FIFO Data Read, FIFO_DATA[7:0]:              |    |

| Reading from the FIFO                        |    |

| FIFO Flush                                   |    |

| FIFO Organization                            |    |

| Typical Application Circuits                 |    |

| Ordering Information                         |    |

| Revision History                             | Δ1 |

# Integrated Heart-Rate Sensor for In-Ear Applications

| LIST OF FIGURES                                                   |      |

|-------------------------------------------------------------------|------|

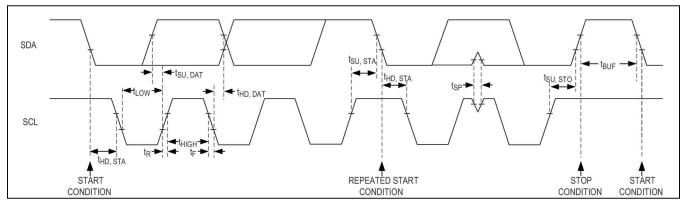

| Figure 1. I <sup>2</sup> C-Compatible Interface Timing Diagram    | <br> |

| Figure 2: Power-Up Sequence of the Power Supply Rails             | 27   |

| Figure 3. START, STOP, and REPEATED START Conditions              | 28   |

| Figure 4. I <sup>2</sup> C Acknowledge                            | 29   |

| Figure 5. Writing One Data Byte to MAX86160                       | 29   |

| Figure 6. Reading One Byte of Data from MAX86160                  | 30   |

| Figure 7. Reading Multiple Bytes of Data from the MAX86160        |      |

| Figure 8. Example of FIFO Organization with Four Active Elements  |      |

| Figure 9. Example of FIFO Organization with Two Active Elements   |      |

| LIST OF TABLES                                                    |      |

| Table 1: MAX86160 I <sup>2</sup> C Slave Address                  | 28   |

| Table 2. FIFO Data Control Registers                              |      |

| Table 3. FDx Format Configurations                                |      |

| Table 4. FIFO Data Format                                         |      |

| Example 1: Configurations for 2 elements: PPG (LED1) + PPG (LED3) |      |

| Example 2: Configurations for 1 elements: PPG (LED1)              |      |

| Table 5. Sample of FIFO Data Index                                |      |

| Table 6. FIFO Handling Registers                                  |      |

| Table 7. FIFO Sample Elements Order with Four Active Elements     |      |

| Table 8 FIFO Sample Flements Order with Two Active Flements       | 35   |

# Integrated Heart-Rate Sensor for In-Ear Applications

## **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND                | 0.3V to +2.2V | Continuous Power Dissipation        | 440mW          |

|---------------------------------------|---------------|-------------------------------------|----------------|

| PGND to GND                           | 0.3V to +0.3V | SDA, SCL, INTB, GPIO to GND         | 0.3V to +6.0V  |

| LED_DRVx, VLED to PGND                | 0.3V to +6.0V | OESIP (derate 5.5mW/°C above +70°C) | 40°C to +85°C  |

| V <sub>REF</sub> to GND               | 0.3V to +2.2V | Operating Temperature Range         | 40°C to +85°C  |

| Output Short-Circuit Duration         | Continuous    | Junction Temperature                | +150°C         |

| Continuous Input Current Into Any Pin |               | Storage Temperature Range           | 40°C to +105°C |

| (Except LED_DRVx Pins)                |               | Soldering Temperature (Reflow)      | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### 18-Lead OESIP

| Package Code                                           | F182A4+1         |  |  |  |

|--------------------------------------------------------|------------------|--|--|--|

| Outline Number                                         | 21-100099        |  |  |  |

| Land Pattern Number                                    | 90-100030        |  |  |  |

| Thermal Resistance, Four Layer Board:                  |                  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 174°C/W (Note 1) |  |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 150°C/W (Note 1) |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

## **Electrical Characteristics**

(( $V_{DD}$  = 1.8V,  $V_{LED}$  = 3.3V(IR),  $V_{LED}$  = 5.0V (GREEN), GND = PGND = 0V,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2) )

| PARAMETER                                      | SYMBOL           | CONDITIONS                                                                                                                                           | MIN     | TYP     | MAX     | UNITS   |  |

|------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|--|

| POWER SUPPLY                                   |                  |                                                                                                                                                      |         |         |         |         |  |

| Power Supply Voltage                           | $V_{DD}$         |                                                                                                                                                      | 1.7     | 1.8     | 2.0     | V       |  |

| LED Supply Voltage for IR                      | V <sub>LED</sub> |                                                                                                                                                      | 3.1     | 3.3     | 5.5     | V       |  |

| LED Supply Voltage for Green                   | V <sub>LED</sub> |                                                                                                                                                      | 4.0     | 5.0     | 5.5     | V       |  |

| V. Committee Committee                         |                  | Heart Rate Mode; PW = 50μs; SPS = 100;<br>LED Driver = 0mA                                                                                           |         | 400     | 750     |         |  |

| V <sub>DD</sub> Supply Current                 | I <sub>DD</sub>  | Heart Rate Mode; PW = 50μs; SPS = 10;<br>LED Driver = 0mA                                                                                            |         | 400     | 750     | μA      |  |

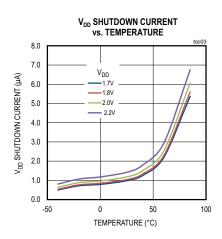

| V <sub>DD</sub> Current in Shutdown            |                  | T <sub>A</sub> = 25°C                                                                                                                                |         | 0.5     | 12      | μA      |  |

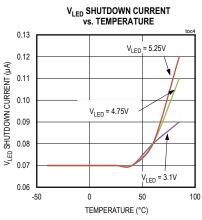

| V <sub>LED</sub> Current in Shutdown           |                  | T <sub>A</sub> = 25°C                                                                                                                                |         | 0       | 1       | μA      |  |

| Internal Voltage Reference (Note 3)            | V <sub>REF</sub> | Bypass to GND with 1μF                                                                                                                               | 1.192   | 1.204   | 1.215   | ٧       |  |

| PULSE OXIMETRY/HEART                           | RATE SENSO       | R CHARACTERISTICS                                                                                                                                    |         |         |         |         |  |

| ADC Resolution                                 |                  |                                                                                                                                                      |         | 19      |         | bits    |  |

| IR ADC Count                                   | IR_C             | Proprietary ATE Setup. IR_PA = 0x13,<br>PW = 50µS, SPS = 1000, T <sub>A</sub> = +25°C                                                                | 121,072 | 131,072 | 141,072 | Counts  |  |

| Green ADC Count                                | GREEN_C          | Proprietary ATE Setup. GREEN_PA = $0x80$ ,<br>PW = $50\mu$ S, SPS = $1000$ , $T_A$ = $+25^{\circ}$ C                                                 | 111,072 | 131,072 | 151,072 | Counts  |  |

| Dark Current Counts                            | DC_C             | ALC = ON, IR_PA = 0x00, PW = 50μS, SPS<br>= 1000, PPG_ADC_RGE<1:0> = 8μA,<br>T <sub>A</sub> = +25°C                                                  |         | 0.0001  | 0.02    | % of FS |  |

| IR/GREEN ADC Count -<br>PSRR (VDD)             | PSRR_VDD         | Propriety ATE setup, 1.7V < V <sub>DD</sub> < 2.0V, IR_PA = 0x12, GREEN_PA = 0x80, PW = 50µS, SPS = 1000                                             |         | 0.5     | 1       | % of FS |  |

| IR/GREEN ADC Count - PSRR (LED Driver Outputs) | PSRR_LED         | Propriety ATE setup, $3.1V < V_{LED} < 5V(IR)$ , $4V < V_{LED} < 5.5V$ (GREEN), $IR\_PA = 0x12$ , $GREEN\_PA = 0x80$ , $PW = 50\mu S$ , $SPS = 1000$ |         | 0.05    | 0.5     | % of FS |  |

| ADC Clock Frequency                            | CLK              |                                                                                                                                                      | 9.649   | 9.846   | 10.043  | MHz     |  |

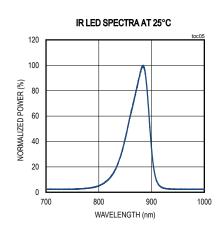

| IR LED CHARACTERISTICS (Note 5)                |                  |                                                                                                                                                      |         |         |         |         |  |

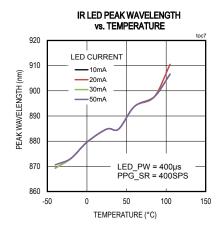

| LED Peak Wavelength                            | λ <sub>P</sub>   | I <sub>LED</sub> = 20mA, T <sub>A</sub> = +25°C                                                                                                      | 870     | 880     | 900     | nm      |  |

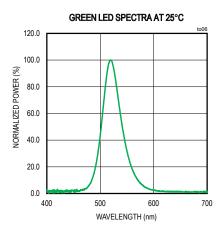

| GREEN LED CHARACTERISTICS (Note 5)             |                  |                                                                                                                                                      |         |         |         |         |  |

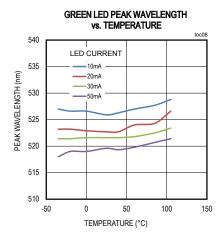

| LED Peak Wavelength                            | λ <sub>P</sub>   | I <sub>LED</sub> = 20mA, T <sub>A</sub> = +25°C                                                                                                      | 520     | 527     | 540     | nm      |  |

## **Electrical Characteristics (continued)**

(( $V_{DD}$  = 1.8V,  $V_{LED}$  = 3.3V(IR),  $V_{LED}$  = 5.0V (GREEN), GND = PGND = 0V,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2) )

| PARAMETER                                             | SYMBOL              | CONDITIONS                                                                                                     | MIN | TYP  | MAX    | UNITS |

|-------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------|-----|------|--------|-------|

| LED DRIVERS                                           |                     |                                                                                                                | '   |      |        | ,     |

| LED Current Resolution                                |                     |                                                                                                                |     | 8    |        | bits  |

|                                                       |                     | $V_{LED}$ = 5.0V (for GREEN), $V_{LED}$ = 3.3V (for IR ONLY), LEDx_PA = 0xFF, LEDx_RGE[1:0] = 00               |     | 50   |        |       |

| LED Drive Current Range                               |                     | $V_{LED}$ = 5.0V (for GREEN), $V_{LED}$ = 3.3V (for IR ONLY), LEDx_PA = 0xFF, LEDx_RGE[1:0] = 01               |     | 100  |        | - mA  |

| (Note 4)                                              | I <sub>LED</sub>    | V <sub>LED</sub> = 5.0V (for GREEN), V <sub>LED</sub> = 3.3V (for IR ONLY), LEDx_PA = 0xFF, LEDx_RGE[1:0] = 10 |     | 150  |        |       |

|                                                       |                     | VLED = 5.0V (for GREEN), V <sub>LED</sub> = 3.3V (for IR ONLY), LEDx_PA = 0xFF, LEDx_RGE[1:0] = 11             |     | 200  |        |       |

| DIGITAL CHARACTERISTIC                                | CS (SDA, SCL,       | INT)                                                                                                           |     |      |        | •     |

| Output Low Voltage SDA, INTB                          | V <sub>OL</sub>     | I <sub>SINK</sub> = 6mA                                                                                        |     |      | 0.4    | V     |

| I <sup>2</sup> C Input Voltage Low                    | V <sub>IL_I2C</sub> | SDA, SCL                                                                                                       |     |      | 0.4    | V     |

| I <sup>2</sup> C Input Voltage High                   | V <sub>IH_I2C</sub> | SDA, SCL                                                                                                       | 1.4 |      |        | V     |

| Input Hysteresis (Note 5)                             | V <sub>HYS</sub>    | SDA, SCL                                                                                                       |     | 200  |        | mV    |

| Input Capacitance (Note 5)                            | C <sub>IN</sub>     | SDA, SCL                                                                                                       |     | 10   |        | pF    |

| Input Leakage Current                                 | 1                   | V <sub>IN</sub> = 0V, T <sub>A</sub> = +25°C (SDA, SCL)                                                        |     | 0.01 | 1      |       |

| input Leakage Current                                 | I <sub>IN</sub>     | $V_{IN} = V_{DD}$ , $T_A = +25$ °C (SDA, SCL)                                                                  |     | 0.01 | 0.01 1 | μA    |

| I <sup>2</sup> C TIMING CHARACTERIS                   | TICS (SDA, S        | CL) (Note 5, Figure 1)                                                                                         |     |      |        |       |

| I <sup>2</sup> C Write Address                        |                     |                                                                                                                |     | ВС   |        | Hex   |

| I <sup>2</sup> C Read Address                         |                     |                                                                                                                |     | BD   |        | Hex   |

| Serial Clock Frequency                                | f <sub>SCL</sub>    |                                                                                                                | 0   |      | 400    | kHz   |

| Bus Free Time Between<br>STOP and START<br>Conditions | t <sub>BUF</sub>    |                                                                                                                | 1.3 |      |        | μs    |

| Hold Time (Repeated)<br>START Condition               | <sup>t</sup> HD,STA |                                                                                                                | 0.6 |      |        | μs    |

| SCL Pulse-Width Low                                   | t <sub>LOW</sub>    |                                                                                                                | 1.3 |      |        | μs    |

| SCL Pulse-Width High                                  | t <sub>HIGH</sub>   |                                                                                                                | 0.6 |      |        | μs    |

| Setup Time for a Repeated START Condition             | <sup>t</sup> su,sta |                                                                                                                | 0.6 |      |        | μs    |

| Data Hold Time                                        | t <sub>HD,DAT</sub> |                                                                                                                | 0   |      | 900    | ns    |

## **Electrical Characteristics (continued)**

(( $V_{DD}$  = 1.8V,  $V_{LED}$  = 3.3V(IR),  $V_{LED}$  = 5.0V (GREEN), GND = PGND = 0V,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                          | SYMBOL              | CONDITIONS | MIN                       | TYP | MAX | UNITS |

|------------------------------------|---------------------|------------|---------------------------|-----|-----|-------|

| Data Setup Time                    | t <sub>SU,DAT</sub> |            | 100                       |     |     | ns    |

| Setup Time for STOP<br>Condition   | t <sub>SU,STO</sub> |            | 0.6                       |     |     | μs    |

| Pulse Width of Suppressed Spike    | t <sub>SP</sub>     |            | 0                         |     | 50  | ns    |

| Bus Capacitance                    | СВ                  |            |                           |     | 400 | pF    |

| SDA and SCL Receiving<br>Rise Time | t <sub>R</sub>      |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA and SCL Receiving Fall Time    | t <sub>F</sub>      |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA Transmitting Fall Time         | t <sub>F</sub>      |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

**Note 2:** All devices are 100% production tested at  $T_A = +25$ °C. Specifications over temperature limits are guaranteed by Maxim Integrated's bench or proprietary automated test equipment (ATE) characterization.

Note 3: Internal Reference Voltage only.

Note 4: Whenever Green LED is used, V<sub>LED</sub> must be 4.0V or above. For LED Current range more than 100mA (LEDx\_RGE = 2'b1X), V<sub>LED</sub> must be 4.5V or above.

**Note 5:** For design guidance only. Not production tested.

Figure 1. I<sup>2</sup>C-Compatible Interface Timing Diagram

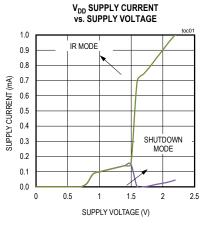

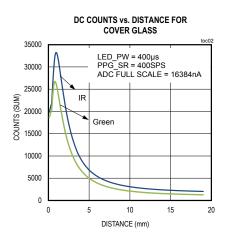

## **Typical Operating Characteristics**

$(V_{DD} = 1.8V, V_{LED} = 3.3V(IR), V_{LED} = 5.0V (GREEN), GND = PGND = 0V, T_A = +25^{\circ}C, unless otherwise noted.)$

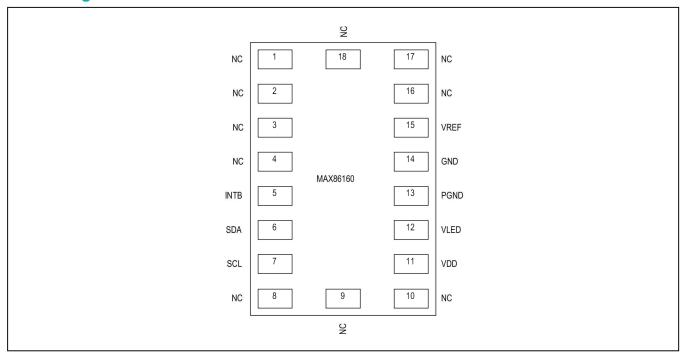

## **Pin Configurations**

## **Pin Description**

| PIN        | NAME             | FUNCTION                                                                                                                                        |

|------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER      |                  |                                                                                                                                                 |

| 11         | V <sub>DD</sub>  | Analog Supply. Connect to externally-regulated supply. Bypass to GND                                                                            |

| 12         | V <sub>LED</sub> | LED Power Supply Input. Connect to external battery supply. Bypass to PGND.                                                                     |

| 13         | PGND             | LED Power Return. Connect to GND.                                                                                                               |

| 14         | GND              | Analog Power Return. Connect to GND.                                                                                                            |

| CONTROL IN | TERFACE          |                                                                                                                                                 |

| 5          | INTB             | Open-Drain Interrupt                                                                                                                            |

| 6          | SDA              | I <sup>2</sup> C Data                                                                                                                           |

| 7          | SCL              | I <sup>2</sup> C Clock                                                                                                                          |

| REFERENCE  |                  |                                                                                                                                                 |

| 15         | VREF             | Internal Reference Decoupling Point. Bypass to GND.                                                                                             |

| N.C.       |                  |                                                                                                                                                 |

| 1          | N.C.             | No Connection. Connect to unconnected PCB pad for mechanical stability. N.C. pins should not be connected to any signal, power, or ground pins. |

| 2          | N.C.             | No Connection. Connect to unconnected PCB pad for mechanical stability. N.C. pins should not be connected to any signal, power, or ground pins. |

| PIN      | NAME | FUNCTION                                                                                                                                        |  |  |  |  |  |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MAX86160 |      | FUNCTION                                                                                                                                        |  |  |  |  |  |

| 3        | N.C. | No Connection. Connect to unconnected PCB pad for mechanical stability. N.C. pins should not be connected to any signal, power, or ground pins. |  |  |  |  |  |

| 4        | N.C. | No Connection. Connect to unconnected PCB pad for mechanical stability. N.C. pins should not be connected to any signal, power, or ground pins. |  |  |  |  |  |

| 8        | N.C. | No Connection. Connect to unconnected PCB pad for mechanical stability. N.C. pins should not be connected to any signal, power, or ground pins. |  |  |  |  |  |

| 9        | N.C. | No Connection. Connect to unconnected PCB pad for mechanical stability. N.C. pins should not be connected to any signal, power, or ground pins. |  |  |  |  |  |

| 10       | N.C. | No Connection. Connect to unconnected PCB pad for mechanical stability. N.C. pins should not be connected to any signal, power, or ground pins. |  |  |  |  |  |

| 16       | N.C. | No Connection. Connect to unconnected PCB pad for mechanical stability. N.C. pins should not be connected to any signal, power, or ground pins. |  |  |  |  |  |

| 17       | N.C. | No Connection. Connect to unconnected PCB pad for mechanical stability. N.C. pins should not be connected to any signal, power, or ground pins. |  |  |  |  |  |

| 18       | N.C. | No Connection. Connect to unconnected PCB pad for mechanical stability. N.C. pins should not be connected to any signal, power, or ground pins. |  |  |  |  |  |

## **Functional Diagram**

## **Detailed Description**

The MAX86160 is a heart rate sensor system solution module designed for the demanding requirements of mobile and wearable devices. The MAX86160 maintains a very small total solution size without sacrificing optical or electrical performance. Minimal external hardware components are necessary for integration into a mobile device. The device is fully adjustable through software registers, and the digital output data is stored in a 32-deep FIFO within the device. The FIFO allows the device to be connected to a micro-controller or processor on a shared bus, where the data is not being read continuously from the MAX86160's registers.

## **HRM Subsystem**

The HRM subsystem in the MAX86160 is composed of ambient light cancellation (ALC), a continuous-time sigma delta ADC, and proprietary discrete time filter. The ALC has an internal DAC to cancel ambient light and increase the effective dynamic range. The internal ADC is a continuous time oversampling sigma delta converter with 19-bit resolution. The ADC output data rate can be programmed from10sps (samples per second) to 3200sps. The MAX86160 includes a proprietary discrete time filter to reject 50Hz/60Hz interference and slow moving residual ambient noise.

#### **LED Driver**

The MAX86160 integrates green and infrared LED drivers to modulate LED pulses for HR measurements. The LED current can be programmed from 0mA to 200mA with proper  $V_{LED}$  supply voltage. The LED pulse width can be programmed from  $50\mu s$  to  $400\mu s$  to allow the algorithm to optimize HR accuracy and power consumption based on use cases.

## **Proximity Function**

The MAX86160 includes a proximity function to save power and reduce visible light emission when the user's finger is not on the sensor. Proximity function is enabled by setting PROX\_INT\_EN to 1. When the HR function is initiated, the IR LED is turned on in proximity mode with a drive current set by the PILOT\_PA register. When an object is detected by exceeding the IR ADC count threshold (set in the PROX\_INT\_ THRESH register), PROX\_INT interrupt is asserted and the part transitions automatically to the normal HR Mode. To reenter PROX mode, a new HR reading must be initiated (even if the value is the same). The proximity function can be disabled by resetting PROX\_INT\_EN to 0. In that case, when the HR function is initiated in the FIFO Data Control registers, the HR mode begins immediately.

## **Register Map**

| ADDRESS          | NAME                    | MSB                 |                     |                     |                  |   |   |   | LSB          |

|------------------|-------------------------|---------------------|---------------------|---------------------|------------------|---|---|---|--------------|

| STATUS REGISTERS |                         |                     |                     |                     |                  |   |   |   |              |

| 0x00             | Interrupt Status 1[7:0] | A_FULL_             | PPG_<br>RDY_        | ALC_<br>OVF_        | PROX_<br>INT_    | - | _ | _ | PWR_<br>RDY_ |

| 0x01             | Interrupt Status 2[7:0] | VDD_<br>OOR_        | _                   | _                   | _                | _ | _ | _ | _            |

| 0x02             | Interrupt Enable 1[7:0] | A_FULL_<br>EN_      | PPG_<br>RDY_<br>EN_ | ALC_<br>OVF_<br>EN_ | PROX_<br>INT_EN_ | ı | - | _ | _            |

| 0x03             | Interrupt Enable 2[7:0] | VDD_<br>OOR_<br>EN_ | -                   | _                   | _                | - | _ | _ | _            |

## **Register Map (continued)**

| ERS                                  |                                                                                                                                                                                                                                                                                                        | l                                                                                                                                                                                                                                                                                                                                                                          |                        |                                |                        |                        |                        |                        |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------|------------------------|------------------------|------------------------|------------------------|

|                                      |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            |                        |                                |                        |                        | ,                      | <u> </u>               |

| FIFO Write Pointer[7:0]              | _                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                          | _                      |                                | FIFC                   | WR_PTR                 | _[4:0]                 |                        |

| Overflow Counter[7:0]                | _                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                          | _                      |                                | OVF_                   | COUNTER                | R_[4:0]                |                        |

| FIFO Read Pointer[7:0]               | _                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                          | _                      |                                | FIFC                   | RD_PTR_                | _[4:0]                 |                        |

| FIFO Data<br>Register[7:0]           |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            |                        | FIFO_DAT                       | ΓA_[7:0]               |                        |                        |                        |

| FIFO Configuration[7:0]              | _                                                                                                                                                                                                                                                                                                      | A_FULL_<br>CLR_                                                                                                                                                                                                                                                                                                                                                            | A_FULL_<br>TYPE_       | FIFO_<br>ROLLS_<br>ON_<br>FULL |                        |                        |                        |                        |

| ONTROL                               |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            |                        |                                |                        |                        |                        |                        |

| FIFO Data Control<br>Register 1[7:0] |                                                                                                                                                                                                                                                                                                        | FD2                                                                                                                                                                                                                                                                                                                                                                        | _[3:0]                 |                                |                        | FD1                    | _[3:0]                 |                        |

| FIFO Data Control<br>Register 2[7:0] |                                                                                                                                                                                                                                                                                                        | FD4                                                                                                                                                                                                                                                                                                                                                                        | _[3:0]                 |                                |                        | FD3                    | 3_[3:0]                |                        |

| System Control [7:0]                 | _                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                          | _                      | _                              | _                      | FIFO_                  | SHDN_                  | RESET_                 |

| , ,                                  |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            |                        |                                |                        | EN_                    | 0.1.5.1                |                        |

| 1                                    |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            |                        |                                |                        |                        | T                      |                        |

| [7:0]                                |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            |                        | PPG_SF                         | R_[3:0]                |                        | PPG_LED                | _PW_[1:0]              |

| PPG Configuration 2<br>[7:0]         | -                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                          | _                      | -                              | _                      | S                      | MP_AVE_[2              | :0]                    |

| Prox Interrupt<br>Threshold [7:0]    |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            | PF                     | ROX_INT_TH                     | IRESH_[7               | :0]                    |                        |                        |

| nplitude                             |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            |                        |                                |                        |                        |                        |                        |

| LED1 PA[7:0]                         |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            |                        | LED1_PA                        | A_[7:0]                |                        |                        |                        |

|                                      |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            | _                      |                                |                        |                        | -                      |                        |

|                                      |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            |                        |                                |                        |                        |                        |                        |

| LED Range[7:0]                       |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            |                        |                                |                        | GE_[1:0]               |                        |                        |

|                                      |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            |                        |                                |                        |                        |                        |                        |

|                                      |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            |                        |                                |                        |                        |                        |                        |

| Part ID[7:0]                         |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                            |                        | PART IF                        | 7:01                   |                        |                        |                        |

|                                      | FIFO Read Pointer[7:0] FIFO Data Register[7:0]  FIFO Configuration[7:0]  DNTROL  FIFO Data Control Register 1[7:0]  FIFO Data Control Register 2[7:0]  TROL  System Control [7:0]  ation  PPG Configuration 1 [7:0]  PPG Configuration 2 [7:0]  Prox Interrupt Threshold [7:0]  nplitude  LED1 PA[7:0] | FIFO Read Pointer[7:0] —  FIFO Data Register[7:0] —  FIFO Configuration[7:0] —  DNTROL  FIFO Data Control Register 1[7:0] —  FIFO Data Control Register 2[7:0] —  TROL  System Control [7:0] —  ation  PPG Configuration 1 PPG_AD [7:0] —  [1 PPG Configuration 2 [7:0] —  Prox Interrupt Threshold [7:0] —  pplitude  LED1 PA[7:0] —  LED Range[7:0] —  LED PILOT PA[7:0] | FIFO Read Pointer[7:0] | FIFO Read Pointer[7:0]         | FIFO Read Pointer[7:0] | FIFO Read Pointer[7:0] | FIFO Read Pointer[7:0] | FIFO Read Pointer[7:0] |

## Interrupt Status 1 (0x00)

| BIT         | 7         | 6         | 5         | 4         | 3 | 2 | 1 | 0         |

|-------------|-----------|-----------|-----------|-----------|---|---|---|-----------|

| Field       | A_FULL    | PPG_RDY   | ALC_OVF   | PROX_INT  | _ | _ | _ | PWR_RDY   |

| Reset       | 0x0       | 0x0       | 0x0       | 0x0       | - | _ | - | 0x0       |

| Access Type | Read Only | Read Only | Read Only | Read Only | _ | _ | _ | Read Only |

## A\_FULL: FIFO Almost Full Flag

| VALUE | ENUMERATION | DECODE                                                                                                                                                                                                                                         |

|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | OFF         | Normal Operation                                                                                                                                                                                                                               |

| 1     | ON          | Indicates that the FIFO buffer will overflow the threshold set by FIFO_A_FULL<3:0> on the next sample. This bit is cleared when the Interrupt Status 1 Register is read. It is also cleared when FIFO_DATA register is read, if A_FULL_CLR = 1 |

## PPG\_RDY: New PPG FIFO Data Ready

| VALUE | ENUMERATION | DECODE                                                                                                                                                                                              |

|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | OFF         | Normal Operation                                                                                                                                                                                    |

| 1     | ON          | In HR modes, this interrupt triggers when there is a new sample in the data FIFO. The interrupt is cleared by reading the Interrupt Status 1 register (0x00), or by reading the FIFO_DATA register. |

## ALC\_OVF: Ambient Light Cancellation Overflow

| VALUE | ENUMERATION | DECODE                                                                                                                                                                                                                                                                                |

|-------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | OFF         | Normal Operation                                                                                                                                                                                                                                                                      |

| 1     | ON          | This interrupt triggers when the ambient light cancellation function of the HR photodiode has reached its maximum limit due to overflow, and therefore, ambient light is affecting the output of the ADC. The interrupt is cleared by reading the Interrupt Status 1 register (0x00). |

## PROX\_INT: Proximity interrupt

If PROX\_INT is masked then the prox mode is disabled and the select PPG begins immediately. This bit is cleared when the Interrupt Status 1 Register is read.

| VALUE | ENUMERATION | DECODE                                                                          |

|-------|-------------|---------------------------------------------------------------------------------|

| 0     | OFF         | Normal Operation                                                                |

| 1     | ON          | Indicates that the proximity threshold has been crossed when in proximity mode. |

## PWR\_RDY: Power Ready Flag

| VALUE | ENUMERATION | DECODE                                                                                                                                                       |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | OFF         | Normal Operation                                                                                                                                             |

| 1     | ON          | Indicates that VBATT went below the UVLO threshold. This bit is not triggered by a soft reset. This bit is cleared when Interrupt Status 1 Register is read. |

## Interrupt Status 2 (0x01)

| BIT         | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|-----------|---|---|---|---|---|---|---|

| Field       | VDD_OOR   | _ | _ | _ | _ | _ | _ | _ |

| Reset       | 0x0       | - | - | - | - | - | - | _ |

| Access Type | Read Only | _ | - | - | - | - | - | _ |

## VDD\_OOR: VDD Out-of-Range flag

This flag checks if the VDD\_ANA supply voltage is outside supported range.

| VALUE | ENUMERATION | DECODE                                                                                                                                                                                                                                                               |

|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | OFF         | VDD_ANA between range.                                                                                                                                                                                                                                               |

| 1     | ON          | Indicated that VDD_ANA is greater than 2.05V or less than 1.65V. This bit is automatically cleared when the Interrupt Status 2 register is read. The detection circuitry has a 10ms delay time, and will continue to trigger as long as the VDD_ANA is out of range. |

## **Interrupt Enable 1 (0x02)**

| BIT         | 7           | 6              | 5              | 4               | 3 | 2 | 1 | 0 |

|-------------|-------------|----------------|----------------|-----------------|---|---|---|---|

| Field       | A_FULL_EN   | PPG_RDY_<br>EN | ALC_OVF_<br>EN | PROX_INT_<br>EN | - | _ | _ | _ |

| Reset       | 0x0         | 0x0            | 0x0            | 0x0             | - | _ | _ | _ |

| Access Type | Write, Read | Write, Read    | Write, Read    | Write, Read     | _ | _ | _ | _ |

## A\_FULL\_EN: FIFO Almost Full Flag enable

| VALUE | ENUMERATION | DECODE                       |

|-------|-------------|------------------------------|

| 0     | OFF         | A_FULL interrupt is disabled |

| 1     | ON          | A_FULL interrupt is enabled  |

## PPG\_RDY\_EN: New PPG FIFO Data Ready Interrupt enable

| VALUE | ENUMERATION | DECODE                        |

|-------|-------------|-------------------------------|

| 0     | OFF         | PPG_RDY interrupt is disabled |

| 1     | ON          | PPG_RDY interrupt is enabled. |

## ALC\_OVF\_EN: Ambient Light Cancellation (ALC) Overflow Interrupt enable

The ALC\_OVF flag will be triggered when the HRM photodiode has reached it's maximum limit due to overflow. At this point, the ADC output will be affected by the ambient light.

| VALUE | ENUMERATION | DECODE                        |  |

|-------|-------------|-------------------------------|--|

| 0     | OFF         | ALC_OVF interrupt is disabled |  |

| 1     | ON          | ALC_OVF interrupt is enabled  |  |

## PROX\_INT\_EN: Proximity Interrupt enable

When the HR function is initiated, the IR LED is turned on in proximity mode with a drive current set by the PILOT\_PA register. When an object is detected by exceeding the IR ADC count threshold (set in the PROX\_INT\_THRESH register), PROX\_INT interrupt is asserted and the part transitions automatically to the normal HR mode.

| VALUE | ENUMERATION | DECODE                         |  |  |

|-------|-------------|--------------------------------|--|--|

| 0     | OFF         | PROX_INT interrupt is disabled |  |  |

| 1     | ON          | PROX_INT interrupt is enabled  |  |  |

## **Interrupt Enable 2 (0x03)**

| BIT         | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|----------------|---|---|---|---|---|---|---|

| Field       | VDD_OOR_<br>EN | _ | _ | _ | _ | _ | _ | _ |

| Reset       | 0x0            | _ | _ | _ | _ | _ | _ | _ |

| Access Type | Write, Read    | _ | _ | _ | _ | _ | _ | _ |

## VDD\_OOR\_EN: VDD Out-of-Range Indicator enable

| , | VALUE | ENUMERATION | DECODE                         |

|---|-------|-------------|--------------------------------|

|   | 0     | OFF         | Disables the VDD_OVR interrupt |

|   | 1     | ON          | Enables the VDD_OVR interrupt  |

## FIFO Write Pointer (0x04)

| BIT         | 7 | 6 | 5 | 4 | 3   | 2           | 1    | 0 |

|-------------|---|---|---|---|-----|-------------|------|---|

| Field       | _ | _ | _ |   | FIF | O_WR_PTR[4  | l:0] |   |

| Reset       | _ | _ | _ |   |     | 0x00        |      |   |

| Access Type | _ | _ | _ |   |     | Write, Read |      |   |

## FIFO\_WR\_PTR: FIFO Write Pointer

This points to the location where the next sample will be written. This pointer advances for each sample pushed on to the FIFO.

| BIT         | 7 | 6 | 5 | 4 | 3  | 2          | 1    | 0 |

|-------------|---|---|---|---|----|------------|------|---|

| Field       | _ | _ | _ |   | OV | F_COUNTER[ | 4:0] |   |

| Reset       | _ | - | - |   |    | 0x00       |      |   |

| Access Type | _ | _ | _ |   |    | Read Only  |      |   |

#### **OVF\_COUNTER: FIFO Overflow Counter**

When FIFO is full any new samples will result in new or old samples getting lost depending on FIFO\_ROLLS\_ON\_FULL. OVF\_COUNTER counts the number of samples lost. It saturates at 0x1F.

## FIFO Read Pointer (0x06)

| BIT         | 7 | 6 | 5 | 4 | 3   | 2           | 1   | 0 |

|-------------|---|---|---|---|-----|-------------|-----|---|

| Field       | _ | _ | _ |   | FII | O_RD_PTR[4  | :0] |   |

| Reset       | _ | _ | _ |   |     | 0x00        |     |   |

| Access Type | - | _ | _ |   |     | Write, Read |     |   |

## FIFO\_RD\_PTR: FIFO Read Pointer

The FIFO Read Pointer points to the location from where the processor gets the next sample from the FIFO through the I<sup>2</sup>C interface. This advances each time a sample is popped from the FIFO. The processor may also write to this pointer after reading the samples. This allows rereading (or retrying) samples from the FIFO.

## FIFO Data Register (0x07)

| BIT         | 7 | 6              | 5 | 4      | 3    | 2 | 1 | 0 |

|-------------|---|----------------|---|--------|------|---|---|---|

| Field       |   | FIFO_DATA[7:0] |   |        |      |   |   |   |

| Reset       |   | 0x00           |   |        |      |   |   |   |

| Access Type |   |                |   | Write, | Read |   |   |   |

## FIFO\_DATA: FIFO Data Register

This is a read-only register and is used to get data from the FIFO. See FIFO Description for more details.

## FIFO Configuration (0x08)

| BIT         | 7 | 6              | 5               | 4                          | 3 | 2       | 1         | 0 |

|-------------|---|----------------|-----------------|----------------------------|---|---------|-----------|---|

| Field       | ı | A_FULL_<br>CLR | A_FULL_<br>TYPE | FIFO_<br>ROLLS_<br>ON_FULL |   | FIFO_A_ | FULL[3:0] |   |

| Reset       | _ | 0x0            | 0x0             | 0x0                        |   | 0:      | xF        |   |

| Access Type | - | Write, Read    | Write, Read     | Write, Read                |   | Write,  | Read      |   |

#### A\_FULL\_CLR: FIFO Almost Full Interrupt Options

This defines whether the A-FULL interrupt should get cleared by FIFO DATA register read.

| VALUE | ENUMERATION   | DECODE                                                                                                     |

|-------|---------------|------------------------------------------------------------------------------------------------------------|

| 0     | RD_DATA_NOCLR | A_FULL interrupt does not get cleared by FIFO_DATA register read. It gets cleared by status register read. |

| 1     | RD_DATA_CLR   | A_FULL interrupt gets cleared by FIFO_DATA register read or status register read.                          |

## A\_FULL\_TYPE: FIFO Almost Full Flag Options

This defines the behavior of the A\_FULL interrupt.

| VALUE | ENUMERATION | DECODE                                                                                                                                                                                                           |

|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | AFULL_RPT   | A_FULL interrupt gets asserted when the a_full condition is detected. It is cleared by status register read, but re-asserts for every sample if the a_full condition persists.                                   |

| 1     | AFULL_ONCE  | A_FULL interrupt gets asserted only when the a_full condition is detected. The interrupt gets cleared on status register read, and does not re-assert for every sample until a new a-full condition is detected. |

## FIFO\_ROLLS\_ON\_FULL: FIFO Rolls on Full Options

This bit controls the behavior of the FIFO when the FIFO becomes completely filled with data.

- When the device is in PROX mode, the FIFO always rolls on full.

- Push to FIFO is enabled when FIFO is full if FIFO\_ROLLS\_ON\_FULL = 1 and old samples are lost. Both FIFO\_WR PTR and FIFO RD PTR increment for each sample after the FIFO is full.

- Push to FIFO is disabled when FIFO is full if FIFO\_ROLLS\_ON\_FULL = 0 and new samples are lost. FIFO\_WR\_ PTR does not increment for each sample after the FIFO is full.

| VALUE | ENUMERATION                 | DECODE                                     |

|-------|-----------------------------|--------------------------------------------|

| 0     | OFF The FIFO stops on full. |                                            |

| 1     | ON                          | The FIFO automatically rolls over on full. |

#### FIFO\_A\_FULL: FIFO Almost Full Value

These bits indicate how many new samples can be written to the FIFO before the interrupt is asserted. For example, if set to 0xF, the interrupt triggers when there is 17 empty space left (15 data samples), and so on.

| FIFO_A_FULL<3:0> | FREE SPACE BEFORE INTERRUPT | # OF SAMPLES IN FIFO |

|------------------|-----------------------------|----------------------|

| 0000             | 0                           | 32                   |

| 0001             | 1                           | 31                   |

| 0010             | 2                           | 30                   |

| 0011             | 3                           | 29                   |

|                  |                             |                      |

| 1110             | 14                          | 18                   |

| 1111             | 15                          | 17                   |

## FIFO Data Control Register 1 (0x09)

| BIT         | 7 | 6      | 5          | 4 | 3           | 2 | 1 | 0 |  |

|-------------|---|--------|------------|---|-------------|---|---|---|--|

| Field       |   | FD2    | [3:0]      |   | FD1[3:0]    |   |   |   |  |

| Reset       |   | 0)     | <b>(</b> 0 |   | 0x0         |   |   |   |  |

| Access Type |   | Write, | Read       |   | Write, Read |   |   |   |  |

#### FD2: FIFO Data Time Slot 2

These bits set the data type for element 2 of the FIFO.

The FIFO can hold up to 32 samples. Each sample can hold up to four elements and each element is 3 bytes wide. The data type that gets stored in the 3 bytes is configured by FD1, FD2, FD3 and FD4 according to the table below. For restriction on data type sequences please see the FLEX FIFO document.

| FD2<3:0> | DATA TYPE | FD2<3:0> | DATA TYPE  | FD2<3:0> | DATA TYPE | FD2<3:0> | DATA TYPE |