Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

**Features**

# PMIC with Integrated Charger and Smart Power Selector for Handheld Devices

### **General Description**

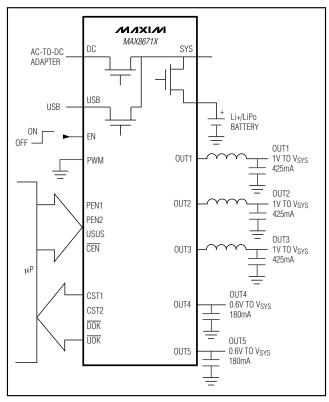

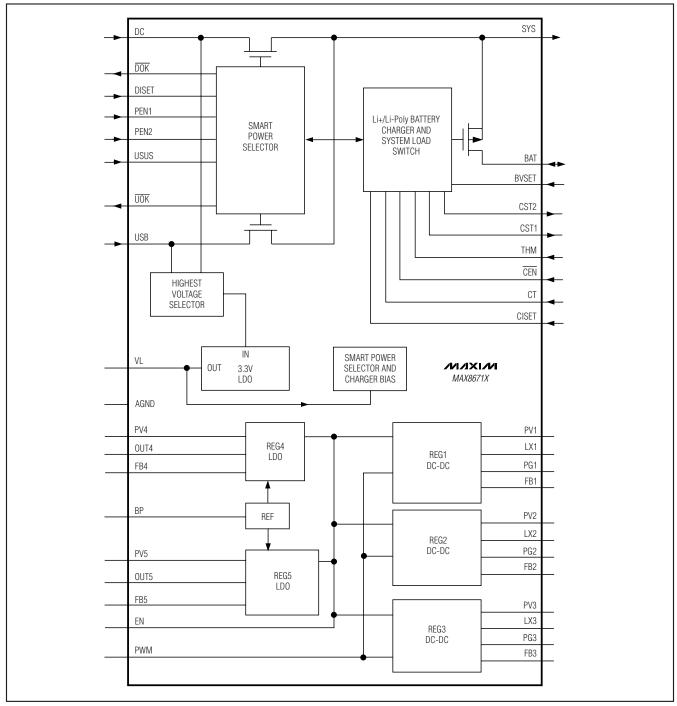

The MAX8671X integrated power-management IC (PMIC) is ideal for use in portable media players and other handheld devices. In addition to five regulated output voltages, the MAX8671X integrates a 1-cell lithium ion (Li+) or lithium polymer (Li-Poly) charger and Smart Power Selector™ with dual (AC-to-DC adapter and USB) power inputs. The dual-input Smart Power Selector supports end products with dual or single power connectors. All power switches for charging and switching the system load between battery and external power are included on-chip. No external MOSFETs are required.

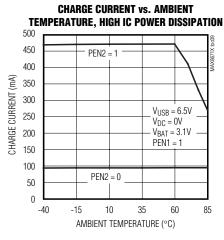

Maxim's Smart Power Selector makes the best use of limited USB or AC-to-DC adapter power. Battery charge current and input current limit are independently set. Input power not used by the system charges the battery. Charge current and DC current limit are programmable up to 1A while USB input current can be set to 100mA or 500mA. Automatic input selection switches the system load from battery to external power. Other features include overvoltage protection, charge status and fault outputs, power-OK monitors, charge timer, and battery thermistor monitor. In addition, on-chip thermal limiting reduces battery charge rate to prevent charger overheating.

The MAX8671X offers adjustable voltages for all outputs. Similar parts with factory-preset output voltages are also available (contact factory for availability).

#### **Applications**

Portable Audio Players GPS Portable Navigators ♦ 16V-Tolerant USB and DC Inputs

- ♦ Automatically Powers from External Power or Battery

- ♦ Operates with No Battery Present

- ♦ Single-Cell Li+/Li-Poly Charger

- ♦ Three 2MHz Step-Down Regulators Up to 96% Efficiency

- **♦ Two Low IQ Linear Regulators**

- ♦ Output Power-Up Sequencing

- **♦ Thermal-Overload Protection**

### Ordering Information

| PART         | TEMP RANGE     | PIN-PACKAGE                  | PKG<br>CODE |

|--------------|----------------|------------------------------|-------------|

| MAX8671XETL+ | -40°C to +85°C | 40 Thin QFN-EP*<br>5mm x 5mm | T4055-1     |

<sup>+</sup>Denotes a lead-free package.

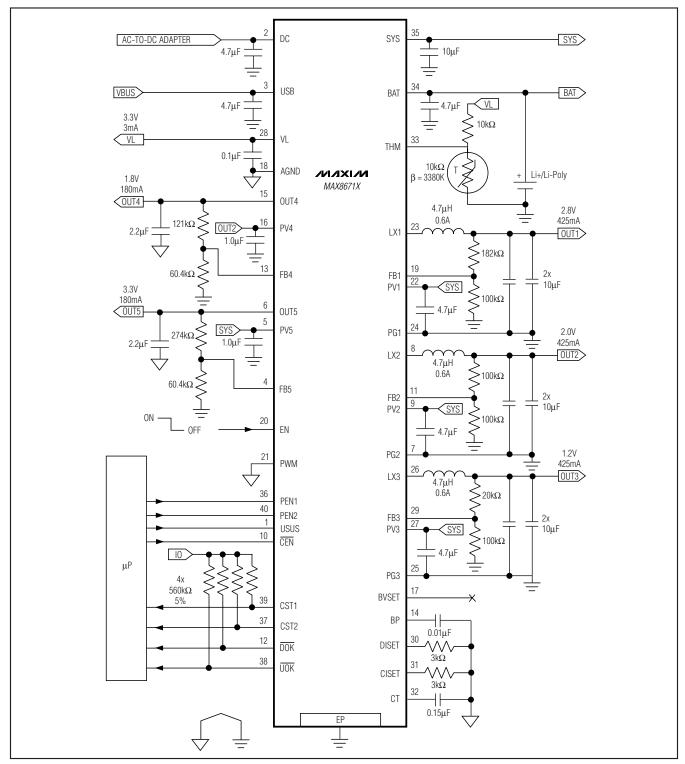

### Simplified Applications Circuit

Smart Power Selector is a trademark of Maxim Integrated Products, Inc.

<sup>\*</sup>EP = Exposed paddle.

| Iable of                                         | r Contents |

|--------------------------------------------------|------------|

| General Description                              | 1          |

| Applications                                     |            |

| Features                                         |            |

| Ordering Information                             |            |

| Simplified Applications Circuit                  |            |

| Table of Contents                                |            |

| Absolute Maximum Ratings                         |            |

| Electrical Characteristics                       |            |

| Typical Operating Characteristics                |            |

| Pin Description                                  |            |

| Detailed Description                             |            |

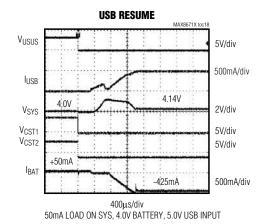

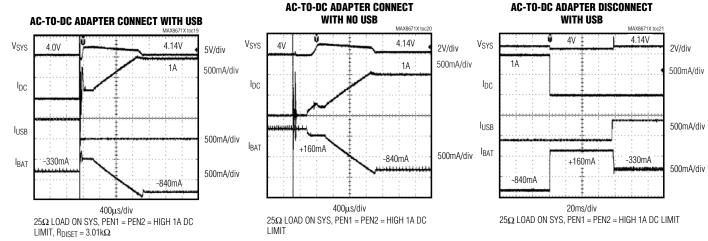

| Smart Power Selector                             |            |

| System Load Switch                               |            |

| USB Power Input (USB)                            |            |

| USB Power-OK Output (UOK)                        |            |

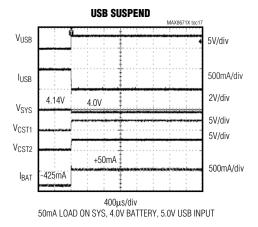

| USB Suspend (USUS)                               |            |

| DC Power Input (DC)                              |            |

| DC Power-OK Output (DOK)                         | 27         |

| Battery Charger                                  |            |

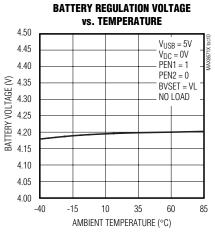

| Battery Regulation Voltage (BVSET)               | 28         |

| Charge Enable Input (CEN)                        | 28         |

| Charge Status Outputs (CST1, CST2)               | 30         |

| Charge Timer (CT)                                |            |

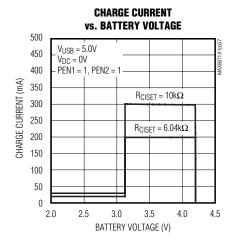

| Setting The Charger Currents (CISET)             |            |

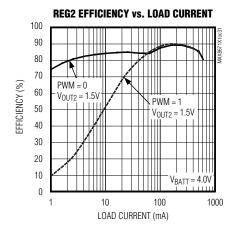

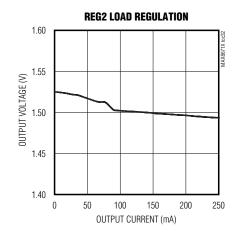

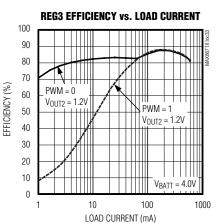

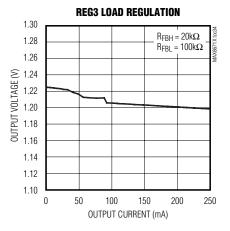

| Step-Down Converters (REG1, REG2, REG3)          |            |

| PWM                                              |            |

| Step-Down Dropout and Minimum Duty Cycle         |            |

| Step-Down Input Capacitors                       | 33         |

| Step-Down Output Capacitors                      |            |

| Step-Down Inductor                               |            |

| Step-Down Converter Output Current               |            |

| Linear Regulators (REG4, REG5)                   |            |

| VL Linear Regulator                              | 35         |

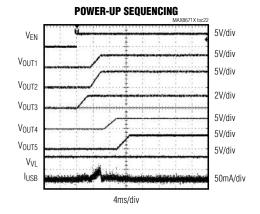

| Enable/Disable (EN) and Sequencing               | 36         |

| Soft-Start/Inrush Current                        |            |

| Active Discharge in Shutdown                     |            |

| Undervoltage and Overvoltage Lockout             |            |

| USB/DC UVLO                                      |            |

| USB/DC OVLO                                      |            |

| SYS UVLO                                         |            |

| REG4/REG5 UVLO                                   |            |

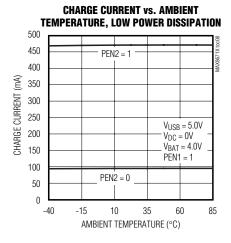

| Thermal Limiting and Overload Protection         | 39         |

| Smart Power Selector Thermal-Overload Protection |            |

| Regulator Thermal-Overload Shutdown              |            |

| Battery Charger Thermistor Input (THM)           |            |

| PCB Layout and Routing                           |            |

| Package Marking                                  |            |

| Chip Information                                 |            |

| Pin Configuration                                |            |

| Package Information                              | 43         |

# MAX8671X

# PMIC with Integrated Charger and Smart Power Selector for Handheld Devices

**Table of Contents (continued)**

| Tables                                                                              |    |

|-------------------------------------------------------------------------------------|----|

| Table 1. Input Limiter Control Logic                                                | 24 |

| Table 2. DC Current Limit for Standard Values of RDISET                             |    |

| Table 3. Charge Status Outputs                                                      |    |

| Table 4. Charge Times vs. C <sub>CT</sub>                                           |    |

| Table 5. Ideal Charge Currents vs. Charge Setting Resistor                          |    |

| Table 6. Suggested Inductors                                                        |    |

| Table 7. 5mm x 5mm x 0.8mm Thin QFN Thermal Characteristics                         | 39 |

| Table 8. Trip Temperatures for Different Thermistors                                | 40 |

| Figures                                                                             |    |

| Figure 1. MAX8671X Typical Application Circuit                                      | 22 |

| Figure 2. Functional Diagram                                                        |    |

| Figure 3. USB Power-OK Logic                                                        |    |

| Figure 4. Programming DC Current Limit                                              |    |

| Figure 5. DC Power-OK Logic                                                         |    |

| Figure 6. Li+/Li-Poly Charge Profile                                                |    |

| Figure 7. Charger State Diagram                                                     |    |

| Figure 8. Programming Charge Current                                                | 31 |

| Figure 9. Monitoring the Battery Charge Current with the Voltage from CISET to AGND | 32 |

| Figure 10. Step-Down Converter Maximum Output Current Example                       |    |

| Figure 11. Enable/Disable Logic                                                     | 36 |

| Figure 12. Enable and Disable Waveforms                                             | 37 |

| Figure 13. REG5 Disable Detail                                                      | 38 |

| Figure 14. Thermistor Input                                                         | 40 |

| Figure 15, Package Marking Example                                                  | 41 |

#### **ABSOLUTE MAXIMUM RATINGS**

**Note 1:** LX\_ has internal clamp diodes to PG\_ and PV\_. Applications that forward bias these diodes must take care not to exceed the package power dissipation limits.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected; V<sub>THM</sub> = V<sub>L</sub>/2, V<sub>PG</sub> = V<sub>AGND</sub> = 0V, V<sub>BAT</sub> = 4V,  $\overline{\text{CEN}}$  = low, USUS = low, EN = high, V<sub>PEN1</sub> = V<sub>PEN2</sub> = 3.3V, V<sub>PWM</sub> = 0V, C<sub>OUT4</sub> = 1µF, C<sub>OUT5</sub> = 1µF, C<sub>SYS</sub> = 10µF, PV1 = PV2 = PV3 = PV4 = PV5 = SYS, R<sub>DISET</sub> = 3k $\Omega$ , R<sub>CISET</sub> = 3k $\Omega$ , C<sub>VL</sub> = 0.1µF, C<sub>CT</sub> = 0.15µF, C<sub>BP</sub> = 0.01µF, V<sub>FB1</sub> = 1.1V, V<sub>FB2</sub> = 1.1V, V<sub>FB3</sub> = 1.1V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                 | SYMBOL             | COND                                                                                                    | ITIONS                                          | MIN  | TYP   | MAX   | UNITS |

|-------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------|------|-------|-------|-------|

| DC POWER INPUT (V <sub>DC</sub> = 5.0V, I | EN = low)          |                                                                                                         |                                                 |      |       |       |       |

| DC Voltage Bange                          | \/p.c              | Operating voltage                                                                                       |                                                 | 4.1  |       | 6.6   | V     |

| DC Voltage Range                          | V <sub>DC</sub>    | Withstand voltage                                                                                       |                                                 | 0    |       | 14    | V     |

| SYS Regulation Voltage                    | Vsys_reg           | V <sub>DC</sub> = 6V, USUS = lov<br>current is less than the                                            | w, CEN = high, system e input current limit     | 5.2  | 5.3   | 5.4   | V     |

| DC Undervoltage Threshold                 | V <sub>DCL</sub>   | V <sub>DC</sub> rising, 500mV typ                                                                       | oical hysteresis                                | 3.95 | 4.00  | 4.05  | V     |

| DC Overvoltage Threshold                  | V <sub>DCH</sub>   | V <sub>DC</sub> rising, 400mV typ                                                                       | oical hysteresis                                | 6.8  | 6.9   | 7.0   | V     |

| DC Current Limit                          |                    | V <sub>DC</sub> = 6V, V <sub>SYS</sub> = 5V<br>USB unconnected,                                         | PEN1 = low,<br>PEN2 = low,<br>USUS = low        | 90   | 95    | 100   |       |

|                                           | I <sub>DCLIM</sub> | $\overline{\text{CEN}} = \text{low},$ $T_A = +25^{\circ}\text{C},$ $VL = \text{no load}$                | PEN1 = low,<br>PEN2 = high,<br>USUS = low       | 450  | 475   | 500   | mA    |

|                                           |                    | (Note 3)                                                                                                | PEN1 = high,<br>R <sub>DISET</sub> = $3k\Omega$ | 950  | 1000  | 1050  |       |

| R <sub>DISET</sub> Resistance Range       |                    |                                                                                                         |                                                 | 3    |       | 6     | kΩ    |

|                                           |                    | PEN1 = low, USUS =                                                                                      | high                                            |      | 0.11  |       |       |

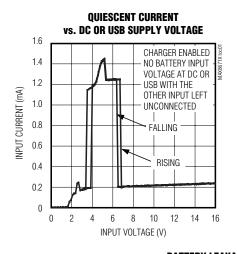

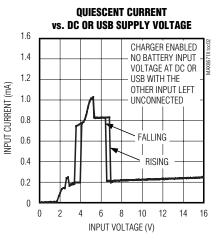

| DC Quiescent Current                      | I <sub>DCIQ</sub>  | USUS = low, $\overline{\text{CEN}}$ = low;<br>ISYS = 0mA, IBAT = 0mA, EN = low;<br>VL no load           |                                                 |      | 1.1   |       | mA    |

|                                           |                    | USUS = low, $\overline{\text{CEN}}$ = high;<br>I <sub>SYS</sub> = 0mA, V <sub>EN</sub> = 0V, VL no load |                                                 |      | 0.7   |       |       |

| Minimum DC-to-BAT Voltage<br>Headroom     |                    | V <sub>DC</sub> falling, 200mV hy                                                                       | V <sub>DC</sub> falling, 200mV hysteresis       |      | 15    | 30    | mV    |

| Minimum DC-to-SYS Voltage<br>Headroom     |                    | V <sub>DC</sub> falling, 200mV hy                                                                       | rsteresis                                       | 0    | 15    | 30    | mV    |

| DC-to-SYS Dropout Resistance              | R <sub>DS</sub>    | $V_{DC} = 5V$ , $I_{SYS} = 400$                                                                         | mA, USUS = low                                  |      | 0.325 | 0.600 | Ω     |

### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected; V<sub>THM</sub> = V<sub>L</sub>/2, V<sub>PG</sub> = V<sub>AGND</sub> = 0V, V<sub>BAT</sub> = 4V,  $\overline{\text{CEN}}$  = low, USUS = low, EN = high, V<sub>PEN1</sub> = V<sub>PEN2</sub> = 3.3V, V<sub>PWM</sub> = 0V, C<sub>OUT4</sub> = 1 $\mu$ F, C<sub>OUT5</sub> = 1 $\mu$ F, C<sub>SYS</sub> = 10 $\mu$ F, PV1 = PV2 = PV3 = PV4 = PV5 = SYS, R<sub>DISET</sub> = 3k $\Omega$ , R<sub>CISET</sub> = 3k $\Omega$ , C<sub>VL</sub> = 0.1 $\mu$ F, C<sub>CT</sub> = 0.15 $\mu$ F, C<sub>BP</sub> = 0.01 $\mu$ F, V<sub>FB1</sub> = 1.1V, V<sub>FB2</sub> = 1.1V, V<sub>FB3</sub> = 1.1V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                 | SYMBOL                | CONDITION                                                                         | IS                                                                                                      | MIN  | TYP   | MAX   | UNITS |

|-------------------------------------------|-----------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|-------|-------|-------|

| DO 1 0)/0 0 (1 0) 1 T                     |                       | Starting DC when no USB p                                                         | present                                                                                                 |      | 1.0   |       | ms    |

| DC-to-SYS Soft-Start Time                 | tss-D-s               | Starting DC with USB prese                                                        | ent                                                                                                     |      | 35    |       | μs    |

| DC Thermal-Limit Temperature              |                       | Die temperature at which coreduced                                                | urrent limit is                                                                                         |      | +100  |       | °C    |

| DC Thermal-Limit Gain                     |                       | Amount of input current red thermal-limit temperature                             | uction above                                                                                            |      | 5     |       | %/°C  |

| USB POWER INPUT (V <sub>USB</sub> = 5.0   | V, EN = low)          |                                                                                   |                                                                                                         |      |       |       |       |

| LICE Voltage Dongs                        | \/                    | Operating voltage                                                                 |                                                                                                         | 4.1  |       | 6.6   | V     |

| USB Voltage Range                         | Vusb                  | Withstand voltage                                                                 |                                                                                                         | 0    |       | 14    | V     |

| SYS Regulation Voltage                    | V <sub>SYS_REG</sub>  |                                                                                   | V <sub>USB</sub> = 6V, USUS = low, <del>CEN</del> = high, system current is less than the input current |      | 5.3   | 5.4   | V     |

| USB Undervoltage Threshold                | Vusbl                 | V <sub>USB</sub> rising, 500mV hystere                                            | sis                                                                                                     | 3.95 | 4.0   | 4.05  | V     |

| USB Overvoltage Threshold                 | Vusbh                 | V <sub>USB</sub> rising, 400mV hystere                                            | sis                                                                                                     | 6.8  | 6.9   | 7.0   | V     |

| USB Current Limit                         |                       | unconnected, $\overline{CEN} = low$ , $\overline{TA} = +25^{\circ}C$ ,            | PEN2 = low,<br>USUS = low                                                                               | 90   | 95    | 100   |       |

|                                           | lusblim               |                                                                                   | PEN2 = high,<br>USUS = low                                                                              | 450  | 475   | 500   | mA    |

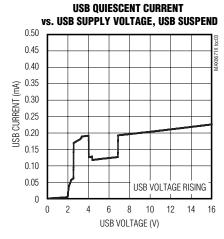

|                                           |                       | USUS = high                                                                       |                                                                                                         |      | 0.11  |       |       |

| USB Quiescent Current                     | lusbiq                | USUS = low, $\overline{\text{CEN}}$ = low;<br>ISYS = 0mA, IBAT = 0mA, VI          | _ no load                                                                                               |      | 1.1   | 2.0   | mA    |

|                                           |                       | USUS = low, $\overline{\text{CEN}}$ = high;<br>I <sub>SYS</sub> = 0mA, VL no load |                                                                                                         |      | 0.7   | 1.3   |       |

| Minimum USB-to-BAT Voltage<br>Headroom    |                       | V <sub>USB</sub> falling, 200mV hystere                                           | esis                                                                                                    | 0    | 15    | 30    | mV    |

| Minimum USB-to-SYS Voltage<br>Headroom    |                       | V <sub>USB</sub> falling, 200mV hystere                                           | esis                                                                                                    | 0    | 15    | 30    | mV    |

| USB-to-SYS Dropout Resistance             | Rus                   | VusB = 5V, Isys = 400mA,                                                          | USUS = low                                                                                              |      | 0.325 | 0.600 | Ω     |

| USB-to-SYS Soft-Start Time                | tss-u-s               |                                                                                   |                                                                                                         |      | 1.0   |       | ms    |

| USB Thermal-Limit Temperature             |                       | Die temperature at which current limit is reduced                                 |                                                                                                         |      | 100   |       | °C    |

| USB Thermal-Limit Gain                    |                       | Amount of input current red thermal-limit temperature                             | uction above                                                                                            |      | 5     |       | %/°C  |

| SYSTEM (V <sub>DC</sub> = 5.0V, EN = low) |                       |                                                                                   |                                                                                                         |      |       |       |       |

| System Operating Voltage Range            | V <sub>SYS</sub>      |                                                                                   |                                                                                                         | 2.6  |       | 5.5   | V     |

| System Undervoltage Threshold             | V <sub>UVLO_SYS</sub> | SYS falling, 100mV hysteres                                                       |                                                                                                         | 2.45 | 2.50  | 2.55  | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected; V<sub>THM</sub> = V<sub>L</sub>/2, V<sub>PG</sub>\_ = V<sub>AGND</sub> = 0V, V<sub>BAT</sub> = 4V,  $\overline{\text{CEN}}$  = low, USUS = low, EN = high, V<sub>PEN1</sub> = V<sub>PEN2</sub> = 3.3V, V<sub>PWM</sub> = 0V, C<sub>OUT4</sub> = 1µF, C<sub>OUT5</sub> = 1µF, C<sub>SYS</sub> = 10µF, PV1 = PV2 = PV3 = PV4 = PV5 = SYS, R<sub>DISET</sub> = 3k $\Omega$ , R<sub>CISET</sub> = 3k $\Omega$ , C<sub>VL</sub> = 0.1µF, C<sub>CT</sub> = 0.15µF, C<sub>BP</sub> = 0.01µF, V<sub>FB1</sub> = 1.1V, V<sub>FB2</sub> = 1.1V, V<sub>FB3</sub> = 1.1V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                               | SYMBOL                                                         | COND                                                                                                          | ITIONS                                              | MIN   | TYP   | MAX   | UNITS  |

|-----------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------|-------|-------|--------|

| BAT-to-SYS Reverse Regulation           | Vpoppo                                                         | DC or USB and BAT                                                                                             | BAT is sourcing 105mA                               | 65    | 82    | 115   | mV     |

| Voltage                                 | VBSREG                                                         | are sourcing current                                                                                          | BAT is sourcing 905mA                               |       | 130   |       | IIIV   |

|                                         |                                                                | DC and USB unconne<br>V <sub>BAT</sub> = 4V                                                                   | ected, EN = low,                                    |       | 0     | 10    |        |

| Quiescent Current                       |                                                                | V <sub>DC</sub> = V <sub>USB</sub> = 5V, US<br>PEN1 = low, EN = low                                           |                                                     |       | 0     | 10    |        |

|                                         | I <sub>PV1</sub> +<br>I <sub>PV2</sub> +<br>I <sub>PV3</sub> + | DC and USB unconned VBAT = 4V (step-down dropout), PWM = low                                                  | converters are not in                               |       | 155   | 285   | μΑ     |

|                                         | I <sub>PV4</sub> +<br>I <sub>PV5</sub> +<br>I <sub>SYS</sub>   | I <sub>PV5</sub> + V <sub>BAT</sub> = 2.8V (at least one step-down                                            |                                                     |       | 425   | 550   |        |

|                                         |                                                                | V <sub>DC</sub> = V <sub>USB</sub> = 5V, USUS = high, EN = high,<br>V <sub>BAT</sub> = 4V, PWM = low (Note 4) |                                                     |       | 180   | 320   |        |

|                                         |                                                                | DC and USB unconnected, EN = high, VBAT = 4.0V, PWM = high                                                    |                                                     |       | 9     |       | mA     |

| BATTERY CHARGER (V <sub>DC</sub> = 5.0) | V, EN = low)                                                   |                                                                                                               |                                                     |       |       |       |        |

| BAT-to-SYS On-Resistance                | R <sub>BS</sub>                                                | $V_{USB} = 0V, V_{BAT} = 4.3$                                                                                 | 2V, I <sub>SYS</sub> = 1A                           |       | 0.08  | 0.16  | Ω      |

|                                         |                                                                | BVSET = VL or                                                                                                 | T <sub>A</sub> = +25°C                              | 4.174 | 4.200 | 4.221 |        |

|                                         |                                                                | BVSET unconnected                                                                                             | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ | 4.145 | 4.200 | 4.242 |        |

| BAT Regulation Voltage                  | \/                                                             | BVSET = AGND                                                                                                  | T <sub>A</sub> = +25°C                              | 4.073 | 4.100 | 4.121 | -<br>- |

| (Figure 6)                              | VBATREG                                                        | DVSET = AGND                                                                                                  | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$       | 4.047 | 4.100 | 4.141 |        |

|                                         |                                                                | $R_{BVSET} = 49.9 k\Omega$ to                                                                                 | T <sub>A</sub> = +25°C                              | 4.325 | 4.350 | 4.376 |        |

|                                         |                                                                | AGND                                                                                                          | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$       | 4.297 | 4.350 | 4.398 | 1      |

| BAT Recharge Threshold                  | VBATRCHG                                                       | (Note 5)                                                                                                      |                                                     | -170  | -120  | -70   | mV     |

| BAT Prequalification Threshold          | VBATPRQ                                                        | V <sub>BAT</sub> rising, 180mV hy                                                                             | steresis, Figure 6                                  | 2.9   | 3.0   | 3.1   | V      |

| RCISET Resistance Range                 |                                                                | Guaranteed by BAT fa                                                                                          | ast-charge current                                  | 3     |       | 15    | kΩ     |

| CISET Voltage                           | VCISET                                                         | RCISET = $7.5$ k $\Omega$ , I <sub>BAT</sub>                                                                  | = 267mA, Figure 9                                   | 0.9   | 1.0   | 1.1   | V      |

### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected; V<sub>THM</sub> = V<sub>L</sub>/2, V<sub>PG</sub> = V<sub>AGND</sub> = 0V, V<sub>BAT</sub> = 4V,  $\overline{\text{CEN}}$  = low, USUS = low, EN = high, V<sub>PEN1</sub> = V<sub>PEN2</sub> = 3.3V, V<sub>PWM</sub> = 0V, C<sub>OUT4</sub> = 1µF, C<sub>OUT5</sub> = 1µF, C<sub>SYS</sub> = 10µF, PV1 = PV2 = PV3 = PV4 = PV5 = SYS, R<sub>DISET</sub> = 3k $\Omega$ , R<sub>CISET</sub> = 3k $\Omega$ , C<sub>VL</sub> = 0.1µF, C<sub>CT</sub> = 0.15µF, C<sub>BP</sub> = 0.01µF, V<sub>FB1</sub> = 1.1V, V<sub>FB2</sub> = 1.1V, V<sub>FB3</sub> = 1.1V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                     | SYMBOL   | CO                                                                                 | NDITIONS                                                                  | MIN | TYP  | MAX | UNITS |

|-------------------------------|----------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|------|-----|-------|

|                               |          | input, DC unconne<br>PEN2 = low, USUS                                              |                                                                           | 87  | 92   | 100 |       |

|                               |          | Low-power USB cl<br>input, R <sub>CISET</sub> = 3k<br>PEN2 = low, USUS             |                                                                           | 87  | 92   | 100 |       |

|                               |          |                                                                                    | charging from the USB exted, $R_{CISET} = 3k\Omega$ , $IS = Iow$          | 450 | 472  | 500 |       |

| BAT Fast-Charge Current Limit |          | High-power USB countries input, R <sub>CISET</sub> = 3k <sub>1</sub><br>USUS = low | charging from the DC $\Omega$ , PEN2 = high,                              | 450 | 472  | 500 | mA    |

|                               |          | AC-to-DC adapter input, R <sub>DISET</sub> = 3k PEN1 = high                        | charging from the DC $\Omega$ , R <sub>CISET</sub> = 15k $\Omega$ ,       | 170 | 200  | 230 |       |

|                               |          | PEN1 = high  AC-to-DC adapter charging from the DC                                 |                                                                           | 375 | 400  | 425 |       |

|                               |          |                                                                                    |                                                                           | 750 | 802  | 850 | -     |

| BAT Prequalification Current  |          | V <sub>BAT</sub> = 2.5V, R <sub>CISI</sub>                                         | $ET = 3.74k\Omega$                                                        | 65  | 82   | 100 | mA    |

| Top-Off Threshold             |          | T <sub>A</sub> = +25°C, R <sub>CISE</sub>                                          | $ET = 3.74$ k $\Omega$ (Note 6)                                           | 20  | 30   | 40  | mA    |

| DATI salas as Compart         |          | EN = low,<br>T <sub>A</sub> = +25°C                                                | No DC or USB power connected                                              |     | 0    | +5  |       |

| BAT Leakage Current           |          |                                                                                    | DC and/or USB power connected, CEN = high                                 | -5  | 1    | +5  | - μA  |

|                               |          | Slew rate                                                                          |                                                                           |     | 450  |     | mA/ms |

| Charger Soft-Start Time       | too 0110 | Time from 0mA to                                                                   | 500mA                                                                     |     | 1.10 |     |       |

| Charger Soit-Start Time       | tss_chg  | Time from 0mA to                                                                   | 100mA                                                                     |     | 0.22 |     | ms    |

|                               |          | Time from 100mA                                                                    | to 500mA                                                                  |     | 0.88 |     |       |

| Timer Accuracy                |          | $C_{CT} = 0.15 \mu F$                                                              |                                                                           | -20 |      | +20 | %     |

| Timer Suspend Threshold       |          |                                                                                    | en the fast-charge timer<br>translates to 20% of the<br>rge current limit | 250 | 300  | 350 | mV    |

| Timer Extend Threshold        |          |                                                                                    | en the fast-charge timer<br>translates to 50% of the<br>rge current limit | 700 | 750  | 800 | mV    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected; V<sub>THM</sub> = V<sub>L</sub>/2, V<sub>PG</sub>\_ = V<sub>AGND</sub> = 0V, V<sub>BAT</sub> = 4V,  $\overline{\text{CEN}}$  = low, USUS = low, EN = high, V<sub>PEN1</sub> = V<sub>PEN2</sub> = 3.3V, V<sub>PWM</sub> = 0V, C<sub>OUT4</sub> = 1µF, C<sub>OUT5</sub> = 1µF, C<sub>SYS</sub> = 10µF, PV1 = PV2 = PV3 = PV4 = PV5 = SYS, R<sub>DISET</sub> = 3k $\Omega$ , R<sub>CISET</sub> = 3k $\Omega$ , C<sub>VL</sub> = 0.1µF, C<sub>CT</sub> = 0.15µF, C<sub>BP</sub> = 0.01µF, V<sub>FB1</sub> = 1.1V, V<sub>FB2</sub> = 1.1V, V<sub>FB3</sub> = 1.1V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                            | SYMBOL            | CONDIT                             | TIONS                  | MIN    | TYP              | MAX              | UNITS                   |

|--------------------------------------|-------------------|------------------------------------|------------------------|--------|------------------|------------------|-------------------------|

| Prequalification Time                | tpQ               | C <sub>CT</sub> = 0.15µF           |                        |        | 33               |                  | min                     |

| Fast-Charge Time                     | t <sub>FC</sub>   | C <sub>CT</sub> = 0.15µF           |                        |        | 660              |                  | min                     |

| Top-Off Time                         | tTO               |                                    |                        |        | 15               |                  | S                       |

| THERMISTOR INPUT (THM) (VDC          | = 5.0V, EN =      | : low)                             |                        |        |                  |                  |                         |

| THM Threshold, Cold                  | VTHMC             | V <sub>THM</sub> rising, 65mV hyst | eresis                 | 73.0   | 74.0             | 75.5             | % of<br>V <sub>VL</sub> |

| THM Threshold, Hot                   | V <sub>THMH</sub> | V <sub>THM</sub> falling, 65mV hys | teresis                | 27.0   | 28.4             | 30.0             | % of<br>V <sub>VL</sub> |

| THM Input Leakage Current            | I <sub>THM</sub>  | THM = AGND or VL, TA               |                        | -0.100 | 0.001            | +0.200           | μΑ                      |

| POWER SEQUENCING (Figures 1          | <br> 1 and 12)    | THIN - ACIND OF VE, 14             | ( = +05 0              |        | 0.01             |                  |                         |

| EN to REG3 Enable Delay              | t <sub>D1</sub>   |                                    |                        |        | 120              |                  | μs                      |

| REG1 Soft-Start Time                 | tss1              |                                    |                        |        | 2.6              |                  | ms                      |

| REG3 to REG1/2 Delay                 | t <sub>D2</sub>   |                                    |                        |        | 0.4              |                  | ms                      |

| REG2 Soft-Start Time                 | tss2              |                                    |                        |        | 2.6              |                  | ms                      |

| REG3 Soft-Start Time                 | tss3              |                                    |                        |        | 2.6              |                  | ms                      |

| REG1/2 to REG4 Delay                 | t <sub>D3</sub>   |                                    |                        |        | 0.3              |                  | ms                      |

| REG4 Soft-Start Time                 | tss4              |                                    |                        |        | 3.0              |                  | ms                      |

| REG5 Soft-Start Time                 | tss5              |                                    |                        |        | 3.0              |                  | ms                      |

| REGULATOR THERMAL SHUTDO             | OWN               | ·                                  |                        | •      |                  |                  |                         |

| Thermal Shutdown Temperature         |                   | T <sub>J</sub> rising              |                        |        | +165             |                  | °C                      |

| Thermal Shutdown Hysteresis          |                   |                                    |                        |        | 15               |                  | °C                      |

| REG1—SYNCHRONOUS STEP-D              | OWN CONV          | ERTER                              |                        |        |                  |                  |                         |

| Input Voltage                        |                   | PV1 supplied from SYS              |                        |        | V <sub>SYS</sub> |                  | V                       |

| Maximum Output Current               |                   | $L = 4.7 \mu H, R_L = 0.13 \Omega$ | (Note 7)               | 425    |                  |                  | mA                      |

| FB1 Voltage                          |                   | (Note 8)                           |                        | 0.997  | 1.012            | 1.028            | V                       |

| Adjustable Output Voltage Range      |                   |                                    |                        | 1      |                  | V <sub>SYS</sub> | V                       |

| FB1 Leakage Current                  |                   | V <sub>FB1</sub> = 1.012V          | $T_A = +25^{\circ}C$   | -50    | -5               | +50              | nA                      |

| TBT Leakage Current                  |                   | VFB1 = 1.012V                      | T <sub>A</sub> = +85°C |        | -5               |                  | IIA                     |

| Load Regulation                      |                   | PWM mode                           | PWM mode               |        | 4.4              |                  | %/A                     |

| Line Regulation                      |                   | PWM mode (Note 9)                  |                        |        | 1                |                  | %/D                     |

| p-Channel On-Resistance              |                   | $V_{PV1} = 4V$ , $I_{LX1} = 180m$  | nA                     |        | 165              | 330              | mΩ                      |

| n-Channel On-Resistance              |                   | $V_{PV1} = 4V$ , $I_{LX1} = 180m$  | nA                     |        | 200              | 400              | mΩ                      |

| p-Channel Current-Limit<br>Threshold |                   |                                    |                        | 0.555  | 0.615            | 0.675            | А                       |

### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected; V<sub>THM</sub> = V<sub>L</sub>/2, V<sub>PG</sub> = V<sub>AGND</sub> = 0V, V<sub>BAT</sub> = 4V,  $\overline{\text{CEN}}$  = low, USUS = low, EN = high, V<sub>PEN1</sub> = V<sub>PEN2</sub> = 3.3V, V<sub>PWM</sub> = 0V, C<sub>OUT4</sub> = 1 $\mu$ F, C<sub>OUT5</sub> = 1 $\mu$ F, C<sub>SYS</sub> = 10 $\mu$ F, PV1 = PV2 = PV3 = PV4 = PV5 = SYS, R<sub>DISET</sub> = 3k $\Omega$ , R<sub>CISET</sub> = 3k $\Omega$ , C<sub>VL</sub> = 0.1 $\mu$ F, C<sub>CT</sub> = 0.15 $\mu$ F, C<sub>BP</sub> = 0.01 $\mu$ F, V<sub>FB1</sub> = 1.1V, V<sub>FB2</sub> = 1.1V, V<sub>FB3</sub> = 1.1V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                 | SYMBOL   | CON                             | IDITIONS                                            | MIN   | TYP              | MAX              | UNITS |

|-------------------------------------------|----------|---------------------------------|-----------------------------------------------------|-------|------------------|------------------|-------|

| Skip Mode Transition Current              |          | (Note 10)                       |                                                     |       | 60               |                  | mA    |

| n-Channel Zero-Crossing<br>Threshold      |          |                                 |                                                     |       | 10               |                  | mA    |

| Maximum Duty Cycle                        |          |                                 |                                                     |       | 100              |                  | %     |

| Minimum Duty Cycle                        |          | PWM mode                        |                                                     |       | 12.5             |                  | %     |

| Internal Oscillator Frequency             |          |                                 |                                                     | 1.8   | 2.0              | 2.2              | MHz   |

| Internal Discharge Resistance in Shutdown |          | EN = low, resistance            | EN = low, resistance from LX1 to PG1                |       | 1.0              | 2.0              | kΩ    |

| REG2—SYNCHRONOUS STEP-D                   | OWN CONV | ERTER                           |                                                     |       |                  |                  |       |

| Input Voltage                             |          | PV2 supplied from S             | SYS                                                 |       | V <sub>SYS</sub> |                  | V     |

| Maximum Output Current                    |          | $L = 4.7 \mu H, R_L = 0.1$      | 3Ω (Note 7)                                         | 425   |                  |                  | mA    |

| FB2 Voltage                               |          | (Note 8)                        |                                                     | 0.997 | 1.012            | 1.028            | V     |

| Adjustable Output Voltage Range           |          |                                 |                                                     | 1     |                  | V <sub>SYS</sub> | V     |

| EDO Lackago Current                       |          | V=== 1.010V                     | $T_A = +25$ °C                                      | -50   | -5               | +50              | nA    |

| FB2 Leakage Current                       |          | $V_{FB2} = 1.012V$              | T <sub>A</sub> = +85°C                              |       | -50              |                  | IIA   |

| Load Regulation                           |          | PWM mode                        |                                                     |       | 4.4              |                  | %/A   |

| Line Regulation                           |          | PWM mode (Note 9                | )                                                   |       | 1                |                  | %/D   |

| p-Channel On-Resistance                   |          | $V_{PV2} = 4V$ , $I_{LX2} = 18$ | 80mA                                                |       | 200              | 400              | mΩ    |

| n-Channel On-Resistance                   |          | $V_{PV2} = 4V$ , $I_{LX2} = 18$ | 80mA                                                |       | 150              | 265              | mΩ    |

| p-Channel Current-Limit<br>Threshold      |          |                                 |                                                     | 0.555 | 0.615            | 0.675            | А     |

| Skip Mode Transition Current              |          | (Note 10)                       |                                                     |       | 60               |                  | mA    |

| n-Channel Zero-Crossing<br>Threshold      |          |                                 |                                                     |       | 10               |                  | mA    |

| Maximum Duty Cycle                        |          |                                 |                                                     |       | 100              |                  | %     |

| Minimum Duty Cycle                        |          | PWM mode                        |                                                     |       | 12.5             |                  | %     |

| Internal Oscillator Frequency             |          |                                 |                                                     | 1.8   | 2.0              | 2.2              | MHz   |

| Internal Discharge Resistance in Shutdown |          | EN = low, resistance            | e from LX2 to PG2                                   | 0.5   | 1.0              | 2.0              | kΩ    |

| REG3—SYNCHRONOUS STEP-D                   | OWN CONV | ERTER                           |                                                     | '     |                  |                  | •     |

| Input Voltage                             |          | PV3 supplied from S             | SYS                                                 |       | V <sub>SYS</sub> |                  | V     |

| Maximum Output Current                    |          | $L = 4.7 \mu H, R_L = 0.1$      | $L = 4.7 \mu H, R_L = 0.13 \Omega \text{ (Note 7)}$ |       |                  |                  | mA    |

| FB3 Voltage                               |          | (Note 8)                        |                                                     | 0.997 | 1.012            | 1.028            | V     |

| Adjustable Output Voltage Range           |          |                                 |                                                     | 1     |                  | V <sub>SYS</sub> | V     |

| ED2 Lookaga Current                       |          | \/=pa = 1.012\/                 | $T_A = +25^{\circ}C$                                | -50   | -5               | +50              |       |

| FB3 Leakage Current                       |          | $V_{FB2} = 1.012V$              | $T_A = +85^{\circ}C$                                |       | -50              |                  | nA    |

| Load Regulation                           |          | PWM mode                        |                                                     |       | 4.4              |                  | %/A   |

|                                           |          |                                 |                                                     |       |                  |                  |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected; V<sub>THM</sub> = V<sub>L</sub>/2, V<sub>PG</sub> = V<sub>AGND</sub> = 0V, V<sub>BAT</sub> = 4V,  $\overline{\text{CEN}}$  = low, USUS = low, EN = high, V<sub>PEN1</sub> = V<sub>PEN2</sub> = 3.3V, V<sub>PWM</sub> = 0V, C<sub>OUT4</sub> = 1µF, C<sub>OUT5</sub> = 1µF, C<sub>SYS</sub> = 10µF, PV1 = PV2 = PV3 = PV4 = PV5 = SYS, R<sub>DISET</sub> = 3k $\Omega$ , R<sub>CISET</sub> = 3k $\Omega$ , C<sub>VL</sub> = 0.1µF, C<sub>CT</sub> = 0.15µF, C<sub>BP</sub> = 0.01µF, V<sub>FB1</sub> = 1.1V, V<sub>FB2</sub> = 1.1V, V<sub>FB3</sub> = 1.1V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                 | SYMBOL           | CONDITIONS                                                                                        |                                                                                              | MIN   | TYP   | MAX              | UNITS |

|-------------------------------------------|------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------|-------|------------------|-------|

| Line Regulation                           |                  | PWM mode (Note 9)                                                                                 |                                                                                              |       | 1     |                  | %/D   |

| p-Channel Current-Limit<br>Threshold      |                  |                                                                                                   |                                                                                              | 0.555 | 0.615 | 0.675            | А     |

| Skip Mode Transition Current              |                  | (Note 10)                                                                                         |                                                                                              |       | 60    |                  | mA    |

| n-Channel Zero-Crossing<br>Threshold      |                  |                                                                                                   |                                                                                              |       | 10    |                  | mA    |

| p-Channel On-Resistance                   |                  | $V_{PV3} = 4V$ , $I_{LX3} = 180r$                                                                 | V <sub>PV3</sub> = 4V, I <sub>LX3</sub> = 180mA                                              |       | 230   | 460              | mΩ    |

| n-Channel On-Resistance                   |                  | $V_{PV3} = 4V$ , $I_{LX3} = 180r$                                                                 | mA                                                                                           |       | 120   | 210              | mΩ    |

| Maximum Duty Cycle                        |                  |                                                                                                   |                                                                                              |       | 100   |                  | %     |

| Minimum Duty Cycle                        |                  | PWM mode                                                                                          |                                                                                              |       | 12.5  |                  | %     |

| Internal Oscillator Frequency             |                  |                                                                                                   |                                                                                              | 1.8   | 2.0   | 2.2              | MHz   |

| Internal Discharge Resistance in Shutdown |                  | EN = low, resistance fi                                                                           | rom LX3 to PG3                                                                               | 0.5   | 1.0   | 2.0              | kΩ    |

| REG4—LINEAR REGULATOR                     |                  | 1                                                                                                 |                                                                                              | · •   |       |                  | •     |

| PV4 Operating Range                       | V <sub>PV4</sub> |                                                                                                   |                                                                                              | 1.7   |       | V <sub>SYS</sub> | V     |

| PV4 Undervoltage Lockout<br>Threshold     |                  | V <sub>PV4</sub> rising, 100mV hysteresis                                                         |                                                                                              | 1.55  | 1.60  | 1.65             | V     |

| FB4 Voltage                               |                  | No load                                                                                           |                                                                                              | 0.582 | 0.600 | 0.618            | V     |

| EDAL calcaga Occurrent                    |                  |                                                                                                   | T <sub>A</sub> = +25°C                                                                       | -50   | -5    | +50              | A     |

| FB4 Leakage Current                       |                  | $V_{FB4} = 0.6V$                                                                                  | T <sub>A</sub> = +85°C                                                                       |       | -5    |                  | nA    |

| Draw Out Desistance                       |                  | PV4 to OUT4, V <sub>PV4</sub> = 3                                                                 | 3.3V                                                                                         |       | 0.45  |                  | 0     |

| Drop-Out Resistance                       |                  | PV4 to OUT4, V <sub>PV4</sub> = 2                                                                 | 2.0V                                                                                         |       | 0.75  | 1.8              | Ω     |

| Current Limit                             |                  | $V_{FB4} = 0.54V$                                                                                 |                                                                                              | 200   | 230   | 265              | mA    |

| Current Limit                             |                  | $V_{FB4} = 0V$                                                                                    |                                                                                              |       | 235   |                  | IIIA  |

| Output Noise                              |                  | 10Hz to 100kHz;<br>C <sub>OUT4</sub> = 3.3µF, I <sub>OUT4</sub><br>V <sub>OUT4</sub> set for 1.8V | = 10mA, V <sub>PV4</sub> = 2V,                                                               |       | 120   |                  | μVRMS |

| PSRR                                      |                  |                                                                                                   | f = 1kHz, I <sub>OUT4</sub> = 10mA, V <sub>PV4</sub> = 2V,<br>V <sub>OUT4</sub> set for 1.8V |       | 67    |                  | dB    |

| רווט ו                                    |                  | f = 10kHz, I <sub>OUT4</sub> = 10r<br>V <sub>OUT4</sub> set for 1.8V                              | $mA$ , $V_{PV4} = 2V$ ,                                                                      |       | 50    |                  | ub    |

| Internal Discharge Resistance in Shutdown |                  | EN = low, resistance for                                                                          | rom OUT4 to AGND                                                                             | 0.5   | 1.0   | 2.0              | kΩ    |

\_\_ /N/XI/N

### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected; V<sub>THM</sub> = V<sub>L</sub>/2, V<sub>PG</sub> = V<sub>AGND</sub> = 0V, V<sub>BAT</sub> = 4V,  $\overline{\text{CEN}}$  = low, USUS = low, EN = high, V<sub>PEN1</sub> = V<sub>PEN2</sub> = 3.3V, V<sub>PWM</sub> = 0V, C<sub>OUT4</sub> = 1 $\mu$ F, C<sub>OUT5</sub> = 1 $\mu$ F, C<sub>SYS</sub> = 10 $\mu$ F, PV1 = PV2 = PV3 = PV4 = PV5 = SYS, R<sub>DISET</sub> = 3k $\Omega$ , R<sub>CISET</sub> = 3k $\Omega$ , C<sub>VL</sub> = 0.1 $\mu$ F, C<sub>CT</sub> = 0.15 $\mu$ F, C<sub>BP</sub> = 0.01 $\mu$ F, V<sub>FB1</sub> = 1.1V, V<sub>FB2</sub> = 1.1V, V<sub>FB3</sub> = 1.1V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                 | SYMBOL           | CONDI                                                                                                                                                                                             | TIONS                        | MIN   | TYP   | MAX                   | UNITS    |

|-------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------|-------|-----------------------|----------|

| REG5—LINEAR REGULATOR                     | I                | •                                                                                                                                                                                                 |                              | ı     |       |                       | l        |

| PV5 Operating Range                       | V <sub>PV5</sub> |                                                                                                                                                                                                   |                              | 1.7   |       | Vsys                  | V        |

| PV5 Undervoltage Lockout<br>Threshold     |                  | V <sub>PV5</sub> rising, 100mV hys                                                                                                                                                                | steresis                     | 1.55  | 1.60  | 1.65                  | V        |

| FB5 Voltage                               |                  | No load                                                                                                                                                                                           |                              | 0.582 | 0.600 | 0.618                 | V        |

| FDE Lookaga Current                       |                  | V=== 0.6V                                                                                                                                                                                         | T <sub>A</sub> = +25°C       | -50   | -5    | +50                   |          |

| FB5 Leakage Current                       |                  | V <sub>FB5</sub> = 0.6V                                                                                                                                                                           | $T_A = +85^{\circ}C$         |       | -5    |                       | nA       |

| Drop-Out Resistance                       |                  | V <sub>PV5</sub> to OUT5, V <sub>PV5</sub> =                                                                                                                                                      | 3.3V                         |       | 0.45  |                       | Ω        |

| Drop-Out nesistance                       |                  | V <sub>PV5</sub> to OUT5, V <sub>PV5</sub> =                                                                                                                                                      | 2.0V                         |       | 0.75  | 1.8                   | 52       |

| Current Limit                             |                  | $V_{FB5} = 0.54V$                                                                                                                                                                                 |                              | 200   | 230   | 265                   | mA       |

| Current Limit                             |                  | $V_{FB5} = 0V$                                                                                                                                                                                    |                              |       | 235   |                       | IIIA     |

| Output Noise                              |                  | 10Hz to 100kHz,<br>Couts = 2.2µF, louts =<br>Vouts set for 3.3V                                                                                                                                   |                              | 180   |       | μV <sub>RMS</sub>     |          |

| PSRR                                      |                  | f = 1kHz, I <sub>OUT5</sub> = 10mA, V <sub>PV5</sub> = 3.5V,<br>V <sub>OUT5</sub> set for 3.3V<br>f = 10kHz, I <sub>OUT5</sub> = 10mA, V <sub>PV5</sub> = 3.5V,<br>V <sub>OUT5</sub> set for 3.3V |                              |       | 62    |                       | ٩D       |

| PORK                                      |                  |                                                                                                                                                                                                   |                              |       | 44    |                       | dB       |

| Internal Discharge Resistance in Shutdown |                  | EN = low, resistance from OUT5 to AGND                                                                                                                                                            |                              | 0.5   | 1.0   | 2.0                   | kΩ       |

| VL—LINEAR REGULATOR                       | I                | •                                                                                                                                                                                                 |                              | I     |       |                       | I        |

| VL Voltage                                | V <sub>V</sub> L | I <sub>VL</sub> = 0mA to 3mA                                                                                                                                                                      |                              | 3.0   | 3.3   | 3.6                   | V        |

| LOGIC (UOK, DOK, PEN1, PEN2,              | USUS, CEN        | CST1, CST2, EN, PWN                                                                                                                                                                               | 1)                           | •     |       |                       | •        |

| Logic Input-Voltage Low                   |                  | $V_{USB}$ or $V_{DC} = 4.1V$ to 5.5V                                                                                                                                                              | $6.6V$ , $V_{SYS} = 2.6V$ to |       |       | 0.6                   | V        |

| Logic Input-Voltage High                  |                  | $V_{USB}$ or $V_{DC} = 4.1V$ to 5.5V                                                                                                                                                              | 6.6V, $V_{SYS} = 2.6V$ to    | 1.3   |       |                       | V        |

|                                           |                  |                                                                                                                                                                                                   | T <sub>A</sub> = +25°C       |       | 0.001 | 1                     | <u> </u> |

| Logic Input Leakage Current               |                  | $V_{LOGIC} = 0V \text{ to } 5.5V$                                                                                                                                                                 | $T_A = +85^{\circ}C$         |       | 0.01  |                       | μΑ       |

| Logic Output-Voltage Low                  |                  | I <sub>SINK</sub> = 1mA                                                                                                                                                                           | ı                            | 1     | 10    | 30                    | mV       |

| Logic Output-High Leakage                 |                  |                                                                                                                                                                                                   | T <sub>A</sub> = +25°C       |       | 0.001 | 1                     |          |

| Current                                   |                  | V <sub>LOGIC</sub> = 5.5V                                                                                                                                                                         | T <sub>A</sub> = +85°C       |       | 0.01  |                       | μΑ       |

| TRI-STATE INPUT (BVSET)                   |                  |                                                                                                                                                                                                   |                              |       |       |                       |          |

| BVSET Input-Voltage Low                   |                  | $V_{USB}$ or $V_{DC} = 4.1V$ to                                                                                                                                                                   | 6.6V                         |       |       | 0.3                   | V        |

| BVSET Input-Voltage Mid                   |                  | V <sub>USB</sub> or V <sub>DC</sub> = 4.1V to                                                                                                                                                     | 6.6V                         | 1.2   |       | V <sub>VL</sub> - 1.2 | V        |

### **ELECTRICAL CHARACTERISTICS (continued)**

(DC, USB, BVSET,  $\overline{\text{UOK}}$ ,  $\overline{\text{DOK}}$ , LX\_ unconnected; V<sub>THM</sub> = V<sub>L</sub>/2, V<sub>PG</sub> = V<sub>AGND</sub> = 0V, V<sub>BAT</sub> = 4V,  $\overline{\text{CEN}}$  = low, USUS = low, EN = high, V<sub>PEN1</sub> = V<sub>PEN2</sub> = 3.3V, V<sub>PWM</sub> = 0V, C<sub>OUT4</sub> = 1µF, C<sub>OUT5</sub> = 1µF, C<sub>SYS</sub> = 10µF, PV1 = PV2 = PV3 = PV4 = PV5 = SYS, R<sub>DISET</sub> = 3k $\Omega$ , R<sub>CISET</sub> = 3k $\Omega$ , C<sub>VL</sub> = 0.1µF, C<sub>CT</sub> = 0.15µF, C<sub>BP</sub> = 0.01µF, V<sub>FB1</sub> = 1.1V, V<sub>FB2</sub> = 1.1V, V<sub>FB3</sub> = 1.1V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                                  | SYMBOL             | CONDITIONS                             | MIN                   | TYP  | MAX                   | UNITS |

|------------------------------------------------------------|--------------------|----------------------------------------|-----------------------|------|-----------------------|-------|

| BVSET Input-Voltage High                                   |                    | $V_{USB}$ or $V_{DC} = 4.1V$ to $6.6V$ | V <sub>VL</sub> - 0.3 |      | V <sub>VL</sub> + 0.3 | ٧     |

| Internal BVSET Pullup Resistance                           |                    |                                        |                       | 52.5 |                       | kΩ    |

| External BVSET Pulldown<br>Resistance for Midrange Voltage | R <sub>BVSET</sub> |                                        | 45                    | 50   | 55                    | kΩ    |

- **Note 2:** Limits are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed through correlation using statistical quality control (SQC) methods.

- Note 3: The USB/DC current limit does not include the VL output current. See the VL Linear Regulator section for more information.

- Note 4: Quiescent current excludes the energy needed for the REG1–REG5 external resistor-dividers. All typical operating characteristics include the energy for the REG1–REG5 external resistor-dividers. For the circuit of Figure 1, the typical quiescent current with DC and USB unconnected, EN = high, V<sub>BAT</sub> = 4V, and PWM = low is 175µA.

- Note 5: The charger transitions from done to fast-charge mode at this BAT recharge threshold (Figure 7).

- Note 6: The charger transitions from fast-charge to top-off mode at this top-off threshold (Figure 7).

- Note 7: The maximum output current is guaranteed by correlation to the p-channel current-limit threshold, p-channel on-resistance, n-channel on-resistance, oscillator frequency, input voltage range, and output voltage range. The parameter is stated for a 4.7μH inductor with 0.13Ω series resistance. See the *Step-Down Converter Output Current* section for more information.

- **Note 8:** The step-down output voltages are 1% high with no load due to the load-line architecture. When calculating the external resistor-dividers, use an FB\_ voltage of 1.000V.

- Note 9: Line regulation for the step-down converters is measured as ΔV<sub>OUT</sub>/ΔD, where D is the duty cycle (approximately V<sub>OUT</sub>/V<sub>IN</sub>).

- **Note 10:** The skip mode current threshold is the transition point between fixed-frequency PWM operation and skip mode operation. The specification is given in terms of output load current for inductor values shown in the typical application circuits.

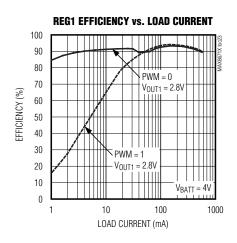

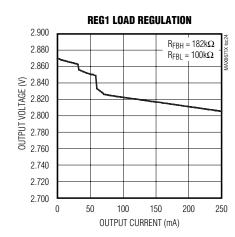

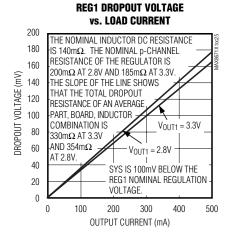

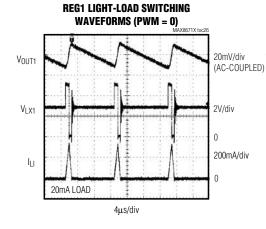

### Typical Operating Characteristics

(Circuit of Figure 1,  $I_{VL}$  = 0mA,  $T_A$  = +25°C, unless otherwise noted.)

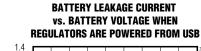

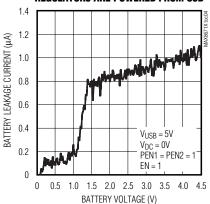

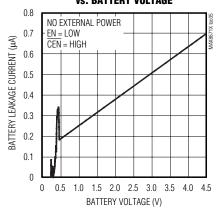

## BATTERY LEAKAGE CURRENT vs. BATTERY VOLTAGE

Typical Operating Characteristics (continued)

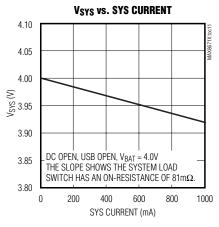

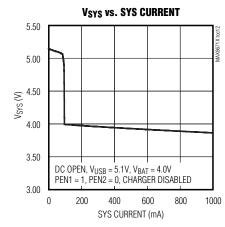

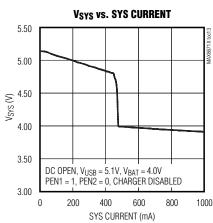

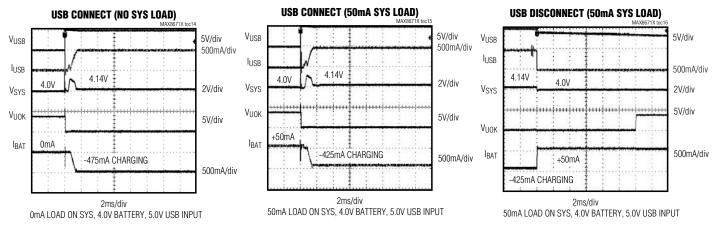

(Circuit of Figure 1, I<sub>VL</sub> = 0mA, T<sub>A</sub> = +25°C, unless otherwise noted.)

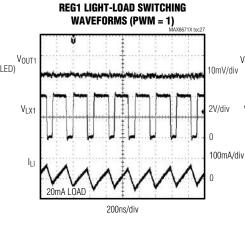

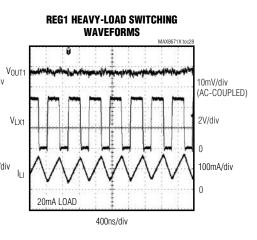

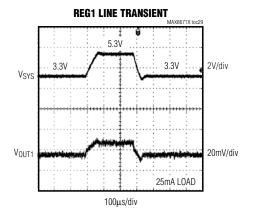

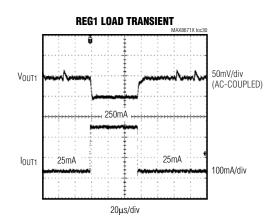

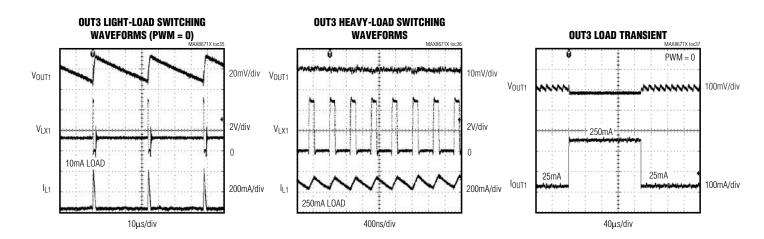

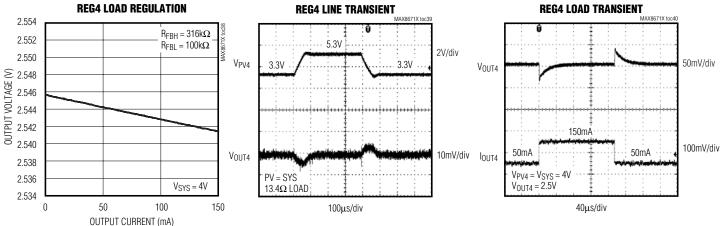

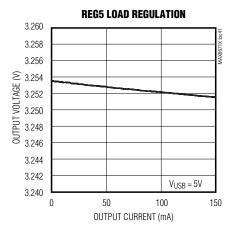

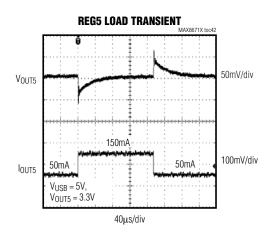

### Typical Operating Characteristics (continued)

### Typical Operating Characteristics (continued)

(Circuit of Figure 1, I<sub>VL</sub> = 0mA, T<sub>A</sub> = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

Typical Operating Characteristics (continued)

### Typical Operating Characteristics (continued)

### **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                      |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | USUS  | USB Suspend Digital Input. As shown in Table 1, driving USUS high suspends the DC or USB inputs if they are configured as a USB power input.                                                                                                                                  |

| 2   | DC    | DC Power Input. DC is capable of delivering 1A to SYS. DC supports both AC adaptors and USB inputs. As shown in Table 1, the DC current limit is controlled by PEN1, PEN2, USUS, and RDISET.                                                                                  |

| 3   | USB   | USB Power Input. USB is capable of delivering 0.5A to SYS. As shown in Table 1, the USB current limit is controlled by PEN1, PEN2, and USUS.                                                                                                                                  |

| 4   | FB5   | Feedback Input for REG5. Connect FB5 to the center of a resistor voltage-divider from OUT5 to AGND to set the REG5 output voltage from 0.6V to V <sub>PV5</sub> .                                                                                                             |

| 5   | PV5   | Power Input for REG5. Connect PV5 to SYS, or a supply between 1.7V and V <sub>SYS</sub> . Bypass PV5 to power ground with a 1µF ceramic capacitor.                                                                                                                            |

| 6   | OUT5  | Linear Regulator Power Output. OUT5 is internally pulled to AGND by $1k\Omega$ in shutdown.                                                                                                                                                                                   |

| 7   | PG2   | Power Ground for the REG2 Step-Down Regulator                                                                                                                                                                                                                                 |