# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **General Description**

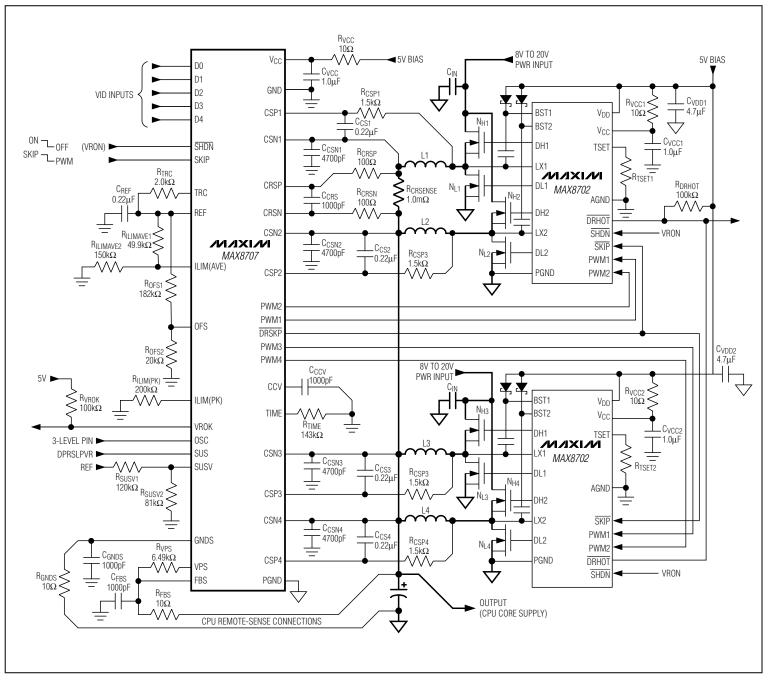

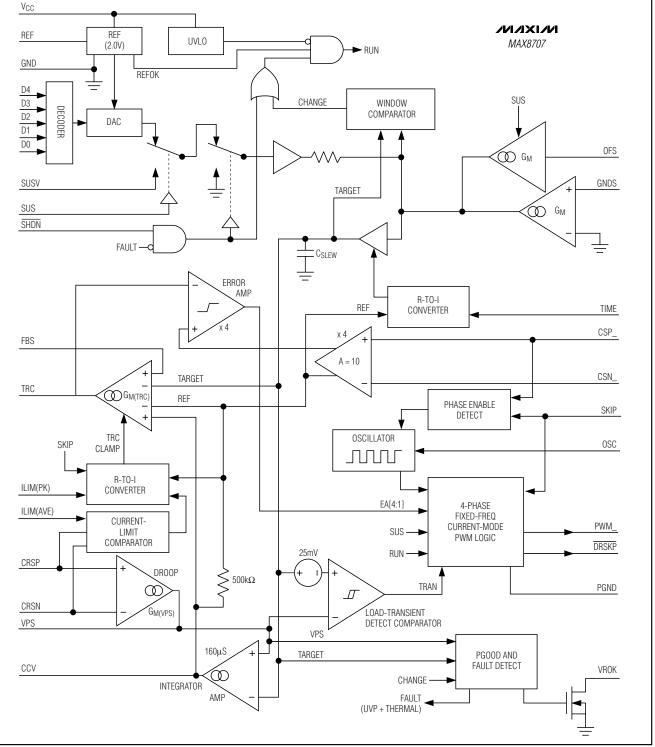

The MAX8707 is a multiphase (3-/4-phase), interleaved, fixed-frequency, step-down controller for AMD Hammer CPU core supplies. Interleaved multiphase operation reduces the input ripple current and output voltage ripple while easing component selection and layout placement. The MAX8707 includes active voltage positioning with adjustable gain and offset, reducing power dissipation and bulk output-capacitance requirements.

The MAX8707 is intended for two different notebook CPU core applications: stepping down the battery directly or stepping down the +5V system supply to create the core voltage. The single-stage conversion method allows these devices to directly step down high-voltage batteries for the highest possible efficiency. Alternatively, 2-stage conversion (stepping down the +5V system supply instead of the battery) at higher switching frequency provides the minimum possible physical size.

The MAX8707 features dedicated differential currentsense inputs for each phase and includes a fifth pair of current-sense inputs to provide an accurate voltagepositioning slope and average current-limit protection using a single current-sense resistor. The MAX8707 also has two dedicated inputs that provide differential remote voltage sensing.

The MAX8707 provides an analog input for setting the suspend voltage and a slew-rate controller for transitions between VID codes or the suspend voltage. The controllers reduce the transition slew rate during startup and shutdown, providing soft-start with minimal input surge current and damped soft-shutdown without negative output undershoot. The MAX8707 includes output fault protection—undervoltage, nonlatched overvoltage, and thermal overload—and an independent voltageregulator power-OK (VROK) output.

The MAX8707 has a selectable switching frequency, allowing 200kHz, 300kHz, or 600kHz per-phase operation. The MAX8707 is available in the low-profile, 40-pin, 6mm x 6mm thin QFN package. Refer to the MAX8702/ MAX8703 for compatible drivers.

### **Features**

- ♦ 3-/4-Phase Interleaved Fixed-Frequency Controller

- ♦ ±0.75% V<sub>OUT</sub> Accuracy Over Line, Load, and Temperature

- 5-Bit On-Board Digital-to-Analog Converter (DAC)—0.80V to 1.55V

- ♦ Adjustable Suspend Voltage Input

- Active Voltage Positioning with Adjustable Gain and Offset

- ♦ Accurate Lossless Current Balance

- ♦ Accurate Droop and Current Limit

- Remote Output and Ground Sense

- Output Slew-Rate Control

- Power-Good Window Comparator

- Selectable 200kHz/300kHz/600kHz Switching Frequency

- Output Overvoltage and Undervoltage Protection

- Thermal Fault Protection

- ♦ 2V ±0.7% Reference Output

- Soft-Startup and Shutdown

# Ordering Information

| PART       | TEMP RANGE     | PIN-PACKAGE           |

|------------|----------------|-----------------------|

| MAX8707ETL | -40°C to +85°C | 40 Thin QFN 6mm x 6mm |

### **Applications**

AMD Hammer Desknote Computers Multiphase CPU Core Supplies Voltage-Positioned Step-Down Converters Notebook/Desktop Computers Servers

Pin Configuration appears at end of data sheet.

###

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND<br>D0–D4 to GND |                                  |

|----------------------------------------|----------------------------------|

| SKIP, SUS, VROK, ILIM(AVE) to GND      |                                  |

| SUSV, OFS, OSC to GND                  | 0.3V to +6V                      |

| CSP_, CSN_, CRSP, CRSN to GND          | 0.3V to +6V                      |

| VPS, FBS, CCV, REF to GND              | 0.3V to (V <sub>CC</sub> + 0.3V) |

| ILIM(PK), TRC, TIME to GND             | 0.3V to $(V_{CC} + 0.3V)$        |

| PWM_, DRSKP to PGND                    | 0.3V to $(V_{CC} + 0.3V)$        |

| PGND, GNDS to GND                      | 0.3V to +0.3V                    |

| SHDN to GND (Note 1)                                  | 0.3V to +14V   |

|-------------------------------------------------------|----------------|

| REF Short-Circuit Duration                            |                |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| 40-Pin 6mm x 6mm Thin QFN                             |                |

| (derate 26.3mW/°C above +70°C)                        | 2.105W         |

| Operating Temperature Range                           |                |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 1: SHDN can be forced to 12V for debugging prototype boards using the no-fault test mode, which disables fault protection.

# **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1.  $V_{CC} = V_{\overline{SHDN}} = 5V$ , OSC = REF,  $V_{VPS} = V_{FBS} = V_{CRSN} = V_{CRSP} = V_{CSP} = 1.20V$ ,  $V_{SUSV} = 0.8V$ , OFS = SUS = GNDS = PGND = SKIP = GND, D0-D4 set for 1.20V (D0-D4 = 01110). **T<sub>A</sub> = 0°C to +85°C**, unless otherwise specified. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                   | SYMBOL                                                                     | CONDITIONS                                                                                |                                | MIN    | ТҮР    | MAX    | UNITS |

|---------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------|--------|--------|--------|-------|

| PWM CONTROLLER                              | •                                                                          |                                                                                           |                                |        |        |        |       |

| Input Voltage Range                         | V <sub>CC</sub>                                                            |                                                                                           |                                | 4.5    |        | 5.5    | V     |

|                                             |                                                                            | Includes load-                                                                            | DAC codes from 1.10V to 1.55V  | -0.75  |        | +0.75  | 01    |

| DC Output Voltage Accuracy                  | V <sub>OUT</sub>                                                           | regulation error<br>(VPS = FBS)                                                           | DAC codes from 0.80V to 1.075V | -2.0   |        | +2.0   | %     |

|                                             |                                                                            |                                                                                           | SUS = V <sub>CC</sub>          | -20    |        | +20    | mV    |

| SUSV Input Range                            | VSUSV                                                                      |                                                                                           |                                | 0.4    |        | 2.0    | V     |

| SUSV Input-Bias Current                     | ISUSV                                                                      | $V_{SUSV} = 0.4V$ to 2V                                                                   | 1                              | -0.1   |        | +0.1   | μA    |

|                                             |                                                                            | Negative offsets                                                                          |                                | 0      |        | 0.8    | V     |

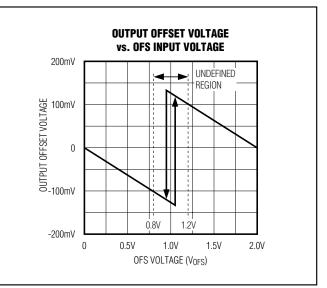

| OFS Input Range                             | VOFS                                                                       | Positive offsets                                                                          |                                | 1.2    |        | 2.0    | v     |

|                                             |                                                                            | $\Delta V_{OUT} / \Delta V_{OFS}, \Delta V_{OFS} = V_{OFS}, V_{OFS} = 0 \text{ to } 0.8V$ |                                | -0.131 | -0.125 | -0.118 |       |

| OFS GAIN                                    | AOFS $\Delta V_{OUT} / \Delta V_{OFS}, \Delta V_{OV}$<br>VOFS = 1.2V to 2V |                                                                                           | 'OFS = VOFS-VREF,              | -0.131 | -0.125 | -0.118 | V/V   |

| OFS Input-Bias Current                      | IOFS                                                                       | $V_{OFS} = 0$ to 2V                                                                       |                                | -0.1   |        | +0.1   | μA    |

| GNDS Input Range                            | VGNDS                                                                      |                                                                                           |                                | -200   |        | +200   | mV    |

| GNDS Gain                                   | AGNDS                                                                      | $\Delta V_{OUT} / \Delta V_{GNDS}$ ,<br>-200mV $\leq V_{GNDS} \leq$                       | +200mV                         | 0.95   | 1.00   | 1.05   | V/V   |

| GNDS Input-Bias Current                     | IGNDS                                                                      |                                                                                           |                                | -2     |        | +2     | μA    |

| FBS Input-Bias Current                      | I <sub>FBS</sub>                                                           | CRSP = CRSN, CSP_ = CSN_                                                                  |                                | -10    |        | +10    | μA    |

|                                             |                                                                            | OSC = GND                                                                                 |                                | 180    | 200    | 220    |       |

| Switching Frequency Accuracy<br>(Per Phase) | fsw                                                                        | OSC = REF                                                                                 |                                | 270    | 300    | 330    | kHz   |

|                                             |                                                                            | $OSC = V_{CC}$                                                                            |                                | 540    | 600    | 660    |       |

# **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1.  $V_{CC} = V_{\overline{SHDN}} = 5V$ , OSC = REF,  $V_{VPS} = V_{FBS} = V_{CRSN} = V_{CRSP} = V_{CSP} = 1.20V$ ,  $V_{SUSV} = 0.8V$ , OFS = SUS = GNDS = PGND = SKIP = GND, D0-D4 set for 1.20V (D0-D4 = 01110). **T<sub>A</sub> = 0°C to +85°C**, unless otherwise specified. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                                                                                                               | SYMBOL             | COND                                                                                                                 | DITIONS                                                                                                       | MIN   | ТҮР   | MAX   | UNITS |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

|                                                                                                                                         |                    | $R_{TIME} = 143 k\Omega (6.25 r$                                                                                     | mV/μs)                                                                                                        | -10   |       | +10   |       |

| TIME Slew-Rate Accuracy                                                                                                                 |                    | $\begin{array}{l} R_{TIME} = 47 \mathrm{k}\Omega ~(19 \mathrm{mV}) \\ (2.28 \mathrm{mV}/\mathrm{\mu s}) \end{array}$ | $R_{TIME} = 47k\Omega (19mV/\mu s)$ to $392k\Omega$ (2.28mV/µs)                                               |       |       | +15   | %     |

|                                                                                                                                         |                    | Startup and shutdowr<br>(4.75mV/μs) to 392kΩ                                                                         |                                                                                                               | -20   |       | +20   |       |

| BIAS AND REFERENCE                                                                                                                      |                    |                                                                                                                      |                                                                                                               |       |       |       |       |

| Quiescent Supply Current (V <sub>CC</sub> )                                                                                             | ICC                | Measured at V <sub>CC</sub> , VP<br>above the regulation                                                             |                                                                                                               |       | 7     | 12    | mA    |

| Shutdown Supply Current (V <sub>CC</sub> )                                                                                              | ICC(SHDN)          | Measured at V <sub>CC</sub> , $\overline{SH}$                                                                        | ĪDN = GND                                                                                                     |       | 0.05  | 10    | μA    |

| Reference Voltage                                                                                                                       | VREF               | $V_{CC} = 4.5V$ to 5.5V, I <sub>F</sub>                                                                              | REF = 0                                                                                                       | 1.986 | 2.000 | 2.014 | V     |

| Reference Load Regulation                                                                                                               |                    | $I_{REF} = 0$ to 500µA                                                                                               |                                                                                                               | -2    | -0.2  |       | m)/   |

| Reference Load Regulation                                                                                                               | $\Delta V_{REF}$   | $I_{REF} = -100\mu A \text{ to } 0$                                                                                  |                                                                                                               |       | 0.21  | 6.2   | mV    |

| FAULT PROTECTION                                                                                                                        |                    |                                                                                                                      |                                                                                                               |       |       |       |       |

| Output Overvoltage-Protection                                                                                                           |                    | Measured at VPS<br>with respect to<br>unloaded output                                                                | $\begin{array}{l} PWM \; (SKIP = GND) \\ or \; SKIP \; mode \; when \\ V_{OUT} \leq V_{TRIP} \end{array}$     | 150   | 200   | 250   | mV    |

| Threshold                                                                                                                               | Vovp               | voltage, rising edge,<br>8mV hysteresis                                                                              | SKIP = $V_{CC}$ and $V_{OUT} > V_{TRIP}$                                                                      | 1.70  | 1.75  | 1.80  | V     |

|                                                                                                                                         |                    | Minimum OVP level                                                                                                    |                                                                                                               |       | 1.1   |       |       |

| Output Overvoltage Propagation<br>Delay                                                                                                 | tovp               | VPS forced 25mV abo                                                                                                  | ove trip threshold                                                                                            |       | 10    |       | μs    |

| Output Undervoltage-Protection<br>Threshold                                                                                             | Vuvp               | Measured at VPS with unloaded nominal out                                                                            | n respect to 70% of the tput voltage                                                                          | -30   |       | +30   | mV    |

| Output Undervoltage<br>Propagation Delay                                                                                                | tuvp               | VPS forced 25mV bel                                                                                                  | ow trip threshold                                                                                             |       | 10    |       | μs    |

| VROK Transition Blanking Time                                                                                                           | <sup>t</sup> BLANK |                                                                                                                      | Measured from the time when VPS reaches<br>the target voltage, slew rate set by R <sub>TIME</sub><br>(Note 2) |       | 20    |       | μs    |

|                                                                                                                                         |                    | Undervoltage measur<br>respect to 87.5% unlo<br>falling edge, 15mV hy                                                | baded output voltage,                                                                                         | -30   |       | +30   |       |

| /ROK Threshold<br>Overvoltage measured at VPS with respect<br>to 112.5% of the unloaded output voltage,<br>rising edge, 15mV hysteresis |                    | -30                                                                                                                  |                                                                                                               | +30   | mV    |       |       |

| VROK Delay                                                                                                                              | <sup>t</sup> VROK  | VPS forced 25mV outside the VROK trip thresholds                                                                     |                                                                                                               |       | 10    |       | μs    |

| VROK Output Low Voltage                                                                                                                 |                    | I <sub>SINK</sub> = 3mA                                                                                              |                                                                                                               |       |       | 0.4   | V     |

| VROK Leakage Current                                                                                                                    |                    | High state, VROK for                                                                                                 | ced to 5.5V                                                                                                   |       |       | 1     | μA    |

# MAX8707

# **MAX8707**

# **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1.  $V_{CC} = V_{SHDN} = 5V$ , OSC = REF,  $V_{VPS} = V_{FBS} = V_{CRSN} = V_{CRSP} = V_{CSP} = 1.20V$ ,  $V_{SUSV} = 0.8V$ , OFS = SUS = GNDS = PGND = SKIP = GND, D0-D4 set for 1.20V (D0-D4 = 01110). **T<sub>A</sub> = 0°C to +85°C**, unless otherwise specified. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                                                   | SYMBOL              | CO                                                                                                        | NDITIONS                                                                           | MIN                       | ТҮР                      | MAX                       | UNITS |  |

|-----------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------|--------------------------|---------------------------|-------|--|

| V <sub>CC</sub> Undervoltage-Lockout<br>Threshold                           | VUVLO(VCC)          | 0 0 7                                                                                                     | Rising edge, hysteresis = 20mV, PWM_<br>disabled below this level                  |                           | 4.25                     | 4.45                      | V     |  |

| Thermal-Shutdown Threshold                                                  | T <sub>SHDN</sub>   | Rising edge hyster                                                                                        | esis = 15°C                                                                        |                           | +160                     |                           | °C    |  |

| DROOP AND TRANSIENT RESP                                                    | ONSE                |                                                                                                           |                                                                                    |                           |                          |                           |       |  |

| DC Droop Amplifier Offset                                                   |                     |                                                                                                           |                                                                                    | -1.5                      |                          | +1.5                      | mV    |  |

| DC Droop Amplifier<br>Transconductance<br>(CRS Sense Enabled)               | Gm(VPS)             | $\Delta I_{VPS} / (N \times \Delta V_{CRS})$<br>VCRSP - VCRSN = -6<br>N = number of pha                   |                                                                                    | 194                       | 200                      | 206                       | μS    |  |

| DC Droop Amplifier<br>Transconductance<br>(CRS Sense Disabled)              | G <sub>m(VPS)</sub> | $\Delta I_{VPS} / (\Sigma \Delta V_{CS}), V_{C}$ $V_{VPS} = V_{CSN\_} = 1.3$ $V_{CSP\_} - V_{CSN\_} = -6$ | 2V,                                                                                | 194                       | 200                      | 206                       | μS    |  |

| Transient-Droop Transresistance                                             | R <sub>TRANS</sub>  | by the voltage prea                                                                                       | (A <sub>CS</sub> = 10 typ) divided<br>amplifier<br>(G <sub>m(TRC)</sub> = 2ms typ) | 4.75                      | 5.0                      | 5.25                      | kΩ    |  |

| Transient Detection Threshold                                               |                     |                                                                                                           | vith respect to steady-<br>n voltage; falling edge,<br>yp)                         | -30                       | -25                      | -20                       | mV    |  |

| CURRENT LIMIT AND BALANCE                                                   |                     | •                                                                                                         |                                                                                    |                           |                          |                           |       |  |

| Current-Sense Input Preamplifier<br>Offsets                                 |                     | CSP CSN_                                                                                                  |                                                                                    | -2.0                      |                          | +2.0                      | mV    |  |

| ILIM(AVE) Input Range<br>(Adjustable Mode)                                  | VILIM(AVE)          |                                                                                                           |                                                                                    | V <sub>REF</sub><br>- 1.0 |                          | V <sub>REF</sub><br>- 0.2 | V     |  |

| ILIM(AVE) Average Current-Limit<br>Threshold Voltage<br>(Positive, Default) | VAVELIMIT           | CRSP - CRSN; ILIM                                                                                         | 1(AVE) = V <sub>CC</sub>                                                           | 22                        | 25                       | 28                        | mV    |  |

| ILIM(AVE) Average Current-Limit                                             |                     |                                                                                                           | VILIM(AVE) = VREF - 0.2V                                                           | 7                         | 10                       | 13                        |       |  |

| Threshold Voltage<br>(Positive, Adjustable)                                 | VAVELIMIT           | CRSP - CRSN                                                                                               | VILIM(AVE) = VREF - 1.0V                                                           | 46                        | 50                       | 54                        | mV    |  |

| ILIM(AVE) Average Current-Limit<br>Threshold Voltage (Negative)             |                     | CRSP - CRSN; ILIM                                                                                         | CRSP - CRSN; ILIM(AVE) = V <sub>CC</sub>                                           |                           | -25                      | -20                       | mV    |  |

| ILIM(AVE) Input Current                                                     | IILIM(AVE)          |                                                                                                           |                                                                                    | -0.1                      |                          | +0.1                      | μA    |  |

| ILIM(AVE) Current-Limit Default<br>Switchover Threshold                     |                     |                                                                                                           |                                                                                    | 3                         | V <sub>CC</sub><br>- 1.0 | V <sub>CC</sub><br>- 0.4  | V     |  |

| ILIM(PK) Peak Current-Limit                                                 |                     | CSP CSN_,<br>RILIM(PK) = RTRC X                                                                           | VPKLIMIT = 30mV                                                                    | 24                        | 30                       | 36                        | mV    |  |

| Threshold Voltage (Positive)                                                | Vpklimit            | $\frac{\text{REM}(\text{PK})}{\text{8V} / \text{V}_{\text{LIM}(\text{PK})}}$                              | VPKLIMIT = 50mV                                                                    | 40                        | 50                       | 60                        | 111V  |  |

| ILIM(PK) Peak Current-Limit<br>Threshold Voltage (Negative)                 |                     | CSP CSN_, RILIM(PK) = RTRC x 8V /<br>VPKLIMIT, VPKLIMIT = 50mV                                            |                                                                                    | -60                       | -50                      | -40                       | mV    |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1.  $V_{CC} = V_{\overline{SHDN}} = 5V$ , OSC = REF,  $V_{VPS} = V_{FBS} = V_{CRSN} = V_{CRSP} = V_{CSP} = 1.20V$ ,  $V_{SUSV} = 0.8V$ , OFS = SUS = GNDS = PGND = SKIP = GND, D0–D4 set for 1.20V (D0–D4 = 01110). **T<sub>A</sub> = 0°C to +85°C**, unless otherwise specified. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                                    | SYMBOL | CONDITION                                                                                                                                                                                                                                                                              | S                      | MIN                      | ТҮР                 | MAX                      | UNITS |

|--------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------|---------------------|--------------------------|-------|

| ILIM(PK) Idle Current-Limit<br>Threshold Voltage (Skip Mode) | VIDLE  | $\begin{split} & \text{CSP}\_\text{-}\text{CSN}\_\text{,} \ \text{V}_{\text{SKIP}} \geq 1.2\text{V}, \\ & \text{R}_{\text{ILIM}(\text{PK})} = \text{R}_{\text{TRC}} \times 8\text{V} \ \text{/} \ \text{V}_{\text{PKLIMIT}}, \\ & \text{V}_{\text{PKLIMIT}} = 50\text{mV} \end{split}$ |                        | 2                        | 5                   | 8                        | mV    |

| Current-Sense Input Current                                  |        | CSP_, CRSP                                                                                                                                                                                                                                                                             |                        | -0.2                     |                     | +0.2                     | μA    |

| Current-Sense input Current                                  |        | CSN_, CRSN                                                                                                                                                                                                                                                                             |                        | -1.0                     |                     | +1.0                     | μΑ    |

| Current-Sense Common-Mode<br>Input Range                     |        | CRSP, CRSN, CSP_, CSN_                                                                                                                                                                                                                                                                 |                        | 0                        |                     | 2                        | V     |

| Phase Disable Threshold                                      |        | CSP4                                                                                                                                                                                                                                                                                   |                        | 3                        | V <sub>CC</sub> - 1 | V <sub>CC</sub> -<br>0.4 | V     |

| CRS Sense Input Disable<br>Threshold                         |        | CRSP                                                                                                                                                                                                                                                                                   |                        | 3                        | V <sub>CC</sub> - 1 | V <sub>CC</sub> -<br>0.4 | V     |

| LOGIC AND I/O                                                | 1      |                                                                                                                                                                                                                                                                                        |                        |                          |                     |                          |       |

| Logic Input High Voltage                                     | VIH    | SHDN, SUS                                                                                                                                                                                                                                                                              |                        | 2.4                      |                     |                          | V     |

| Logic Input Low Voltage                                      | VIL    | SHDN, SUS                                                                                                                                                                                                                                                                              |                        |                          |                     | 0.8                      | V     |

| SHDN No-Fault Threshold                                      |        | To enable no-fault mode                                                                                                                                                                                                                                                                |                        | 11                       |                     | 13                       | V     |

| D0–D4 Logic Input High Voltage                               |        |                                                                                                                                                                                                                                                                                        |                        | 0.8                      |                     |                          | V     |

| D0–D4 Logic Input Low Voltage                                |        |                                                                                                                                                                                                                                                                                        |                        |                          |                     | 0.4                      | V     |

|                                                              |        | н                                                                                                                                                                                                                                                                                      | igh (V <sub>CC</sub> ) | V <sub>CC</sub> -<br>0.4 |                     |                          |       |

| OSC 3-Level Input Logic Levels                               | Vosc   | M                                                                                                                                                                                                                                                                                      | ledium (REF)           | 1.8                      |                     | 2.2                      | V     |

|                                                              |        | Lo                                                                                                                                                                                                                                                                                     | ow (GND)               |                          |                     | 0.4                      |       |

|                                                              | Marina | Н                                                                                                                                                                                                                                                                                      | igh                    | 1.2                      |                     |                          | V     |

| SKIP Input Logic Levels                                      | VSKIP  | Lo                                                                                                                                                                                                                                                                                     | ow (GND)               |                          |                     | 0.8                      | v     |

| Logic Input Current                                          |        | SHDN, SKIP, SUS, OSC, DO                                                                                                                                                                                                                                                               | -D4 = 0  to  5V        | -1                       |                     | +1                       | μA    |

| Logic Output High Voltage                                    | Voh    | PWM_, DRSKP; Isource = 3mA                                                                                                                                                                                                                                                             |                        | V <sub>CC</sub> - 0.4    |                     |                          | V     |

| Logic Output Low Voltage                                     | Vol    | PWM_, DRSKP; ISINK = 3mA                                                                                                                                                                                                                                                               | 4                      |                          |                     | 0.4                      | V     |

# **MAX8707**

# **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1.  $V_{CC} = V_{\overline{SHDN}} = 5V$ , OSC = REF,  $V_{VPS} = V_{FBS} = V_{CRSN} = V_{CRSP} = V_{CSP} = 1.20V$ ,  $V_{SUSV} = 0.8V$ , OFS = SUS = GNDS = PGND = SKIP = GND, D0–D4 set for 1.20V (D0–D4 = 01110). T<sub>A</sub> = -40°C to +85°C, unless otherwise specified.) (Note 3)

| PARAMETER                                   | SYMBOL           | COND                                                                                             | ITIONS                                                                                                                    | MIN    | MAX    | UNITS |

|---------------------------------------------|------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------|--------|-------|

| PWM CONTROLLER                              |                  |                                                                                                  |                                                                                                                           | 1      |        |       |

| Input Voltage Range                         | Vcc              |                                                                                                  |                                                                                                                           | 4.5    | 5.5    | V     |

|                                             |                  | Includes load-                                                                                   | DAC codes from<br>1.10V to 1.55V                                                                                          | -1.0   | +1.0   | 0(    |

| DC Output Voltage Accuracy                  | Vout             | regulation error<br>(VPS = FBS)                                                                  | DAC codes from<br>0.80V to 1.075V                                                                                         | -3.0   | +3.0   | %     |

|                                             |                  |                                                                                                  | SUS = V <sub>CC</sub>                                                                                                     | -25    | +25    | mV    |

| SUSV Input Range                            | VSUSV            |                                                                                                  |                                                                                                                           | 0.4    | 2.0    | V     |

| OFS Input Dange                             | Vere             | Negative offsets                                                                                 |                                                                                                                           | 0      | 0.8    | V     |

| OFS Input Range                             | VOFS             | Positive offsets                                                                                 |                                                                                                                           | 1.2    | 2.0    | v     |

|                                             | A 0.50           | $\Delta V_{OUT} / \Delta V_{OFS}; \Delta V_{OF}$<br>V <sub>OFS</sub> = 0 to 0.8V                 | $r_{\rm S} = V_{\rm OFS}$                                                                                                 | -0.131 | -0.118 |       |

| OFS GAIN                                    | Aofs             | $\Delta V_{OUT} / \Delta V_{OFS}$ ; $\Delta V_{OFS} = V_{OFS} - V_{REF}$ ,<br>V_OFS = 1.2V to 2V |                                                                                                                           | -0.131 | -0.118 | V/V   |

| GNDS Input Range                            | VGNDS            |                                                                                                  |                                                                                                                           | -200   | +200   | mV    |

| GNDS Gain                                   | Agnds            | $\Delta V_{OUT} / \Delta V_{GNDS}$ ,<br>-200mV $\leq V_{GNDS} \leq +2$                           | 200mV                                                                                                                     | 0.95   | 1.05   | V/V   |

|                                             |                  | OSC = GND                                                                                        |                                                                                                                           | 180    | 220    | kHz   |

| Switching Frequency Accuracy (Per Phase)    | fsw              | OSC = REF                                                                                        |                                                                                                                           | 270    | 330    |       |

| (rei rilase)                                |                  | $OSC = V_{CC}$                                                                                   |                                                                                                                           | 540    | 660    |       |

|                                             |                  | $R_{TIME} = 143 k\Omega (6.25 r$                                                                 | mV/µs)                                                                                                                    | -10    | +10    |       |

| TIME Slew-Rate Accuracy                     |                  | $R_{\text{TIME}} = 47 \text{k}\Omega (19 \text{mV})$ (2.28 mV/µs)                                | /µs) to 392k $\Omega$                                                                                                     | -15    | +15    | %     |

|                                             |                  | Startup and shutdowr<br>(4.75mV/μs) to 392kΩ                                                     |                                                                                                                           | -20    | +20    |       |

| BIAS AND REFERENCE                          |                  | •                                                                                                |                                                                                                                           |        |        |       |

| Quiescent Supply Current (V <sub>CC</sub> ) | ICC              | Measured at V <sub>CC</sub> , VP<br>above the regulation                                         |                                                                                                                           |        | 12     | mA    |

| Shutdown Supply Current (V <sub>CC</sub> )  | ICC(SHDN)        | Measured at V <sub>CC</sub> , SH                                                                 | DN = GND                                                                                                                  |        | 10     | μA    |

| Reference Voltage                           | VREF             | $V_{CC} = 4.5V$ to 5.5V, I <sub>F</sub>                                                          | REF = 0                                                                                                                   | 1.98   | 2.02   | V     |

| Deference Load Deputation                   | A)/              | $I_{REF} = 0$ to 500µA                                                                           |                                                                                                                           | -2     |        | mV    |

| Reference Load Regulation                   | $\Delta V_{REF}$ | $I_{\rm REF} = -100 \mu A \text{ to } 0$                                                         |                                                                                                                           |        | 6.2    | mV    |

| FAULT PROTECTION                            |                  |                                                                                                  |                                                                                                                           |        |        |       |

| Output Overvoltage-Protection               | Vovp             | Measured at VPS<br>with respect to<br>unloaded output                                            | $\begin{array}{l} \mbox{PWM (SKIP = GND)} \\ \mbox{or SKIP mode when} \\ \mbox{V}_{OUT} \leq \mbox{V}_{TRIP} \end{array}$ | 150    | 250    | mV    |

| Threshold                                   |                  | voltage, rising edge,<br>8mV hysteresis                                                          | SKIP = $V_{CC}$ and $V_{OUT} > V_{TRIP}$                                                                                  | 1.70   | 1.80   | V     |

# **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1.  $V_{CC} = V_{SHDN} = 5V$ , OSC = REF,  $V_{VPS} = V_{FBS} = V_{CRSN} = V_{CRSP} = V_{CSP} = 1.20V$ ,  $V_{SUSV} = 0.8V$ , OFS = SUS = GNDS = PGND = SKIP = GND, D0–D4 set for 1.20V (D0–D4 = 01110). **T<sub>A</sub> = -40°C to +85°C**, unless otherwise specified.) (Note 3)

| PARAMETER                                                                   | SYMBOL               | co                                                                                                    | ONDITIONS                                                                               | MIN                       | МАХ                      | UNITS |

|-----------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------|--------------------------|-------|

| Output Undervoltage-Protection<br>Threshold                                 | VUVP                 | Measured at VPS unloaded nominal                                                                      | with respect to 70% of the output voltage                                               | -40                       | +40                      | mV    |

| VDOK Threehold                                                              |                      | respect to 87.5%                                                                                      | asured at VPS with<br>of the unloaded output<br>ge, 15mV hysteresis                     | -40                       | +40                      | ~)/   |

| VROK Threshold                                                              |                      | 0                                                                                                     | sured at VPS with respect<br>inloaded output voltage,<br>/ hysteresis                   | -40                       | +40                      | mV    |

| VROK Output Low Voltage                                                     |                      | I <sub>SINK</sub> = 3mA                                                                               |                                                                                         |                           | 0.4                      | V     |

| V <sub>CC</sub> Undervoltage-Lockout<br>Threshold                           | VUVLO(VCC)           | Rising edge, hyste<br>disabled below th                                                               | eresis = 20mV, PWM_<br>is level                                                         | 4.10                      | 4.45                     | V     |

| DROOP AND TRANSIENT RESP                                                    | ONSE                 | 1                                                                                                     |                                                                                         |                           |                          |       |

| DC Droop Amplifier Offset                                                   |                      |                                                                                                       |                                                                                         | -2                        | +2                       | mV    |

| DC Droop Amplifier<br>Transconductance<br>(CRS Sense Enabled)               | G <sub>m(VPS)</sub>  | $\Delta I_{VPS}$ / (N x $\Delta V_{CR}$<br>VCRSP - VCRSN =<br>N = number of ph                        |                                                                                         | 190                       | 210                      | μS    |

| DC Droop Amplifier<br>Transconductance<br>(CRS Sense Disabled)              | G <sub>m</sub> (VPS) | $\Delta I_{VPS} / (\Sigma \Delta V_{CS}), V$<br>$V_{VPS} = V_{CSN_} = 1$<br>$V_{CSP_} - V_{CSN_} = -$ | .2V,                                                                                    | 190                       | 210                      | μS    |

| Transient-Droop Transresistance                                             | R <sub>TRANS</sub>   | by the voltage pre                                                                                    | n (A <sub>CS</sub> = 10 typ) divided<br>eamplifier<br>e (G <sub>m(TRC)</sub> = 2mS typ) | 4.50                      | 5.25                     | kΩ    |

| CURRENT LIMIT AND BALANCE                                                   |                      |                                                                                                       |                                                                                         |                           |                          |       |

| Current-Sense Input Preamplifier<br>Offsets                                 |                      | CSP CSN_                                                                                              |                                                                                         | -2.5                      | +2.5                     | mV    |

| ILIM(AVE) Input Range<br>(Adjustable Mode)                                  | VILIM(AVE)           |                                                                                                       |                                                                                         | V <sub>REF</sub><br>- 1.0 | VREF<br>- 0.2            | V     |

| ILIM(AVE) Average Current-Limit<br>Threshold Voltage<br>(Positive, Default) | Vavelimit            | CRSP - CRSN; ILIM(AVE) = V <sub>CC</sub>                                                              |                                                                                         | 20                        | 30                       | mV    |

| ILIM(AVE) Average Current-Limit                                             |                      |                                                                                                       | VILIM(AVE) = VREF - 0.2V                                                                | 5                         | 15                       |       |

| Threshold Voltage<br>(Positive, Adjustable)                                 | VAVELIMIT            | CRSP - CRSN<br>VILIM(AVE) = V <sub>REF</sub> - 1.0V                                                   |                                                                                         | 44                        | 56                       | mV    |

| ILIM(AVE) Average Current-Limit<br>Threshold Voltage (Negative)             |                      | CRSP - CRSN; ILIM(AVE) = V <sub>CC</sub>                                                              |                                                                                         | -31                       | -19                      | mV    |

| ILIM(AVE) Current-Limit Default<br>Switchover Threshold                     |                      |                                                                                                       |                                                                                         |                           | V <sub>CC</sub><br>- 0.4 | V     |

# **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1.  $V_{CC} = V_{SHDN} = 5V$ , OSC = REF,  $V_{VPS} = V_{FBS} = V_{CRSN} = V_{CRSP} = V_{CSP} = 1.20V$ ,  $V_{SUSV} = 0.8V$ , OFS = SUS = GNDS = PGND = SKIP = GND, D0–D4 set for 1.20V (D0–D4 = 01110). **TA = -40°C to +85°C**, unless otherwise specified.) (Note 3)

| PARAMETER                                                    | SYMBOL            | CON                                                                                                                                                                                                    | DITIONS                     | MIN                      | MAX                      | UNITS |

|--------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|--------------------------|-------|

| ILIM(PK) Peak Current-Limit                                  |                   | CSP CSN_,                                                                                                                                                                                              | V <sub>PKLIMIT</sub> = 30mV | 24                       | 36                       |       |

| Threshold Voltage (Positive)                                 | Vpklimit          | RILIM(PK) = RTRC X<br>8V / VLIM(PK)                                                                                                                                                                    | V <sub>PKLIMT</sub> = 50mV  | 40                       | 60                       | mV    |

| ILIM(PK) Peak Current-Limit<br>Threshold Voltage (Negative)  |                   | CSP CSN_,<br>RILIM(PK) = RTRC x 8<br>VPKLIMIT = 50mV                                                                                                                                                   | 3V / Vpklimit,              | -60                      | -40                      | mV    |

| ILIM(PK) Idle Current-Limit<br>Threshold Voltage (Skip Mode) | V <sub>IDLE</sub> | $\begin{array}{l} \text{CSP}\_\text{-}\text{CSN}\_\text{,}\text{V}_{\text{SKIP}}\\ \text{R}_{\text{ILIM}(\text{PK})}=\text{R}_{\text{TRC}}\times8\\ \text{V}_{\text{PKLIMIT}}=50\text{mV} \end{array}$ |                             | 2                        | 8                        | mV    |

| Current Canada Jacout Current                                |                   | CSP_, CRSP                                                                                                                                                                                             |                             | -0.2                     | +0.2                     |       |

| Current-Sense Input Current                                  |                   | CSN_, CRSN                                                                                                                                                                                             |                             | -1.0                     | +1.0                     | μA    |

| Current-Sense Common-Mode<br>Input Range                     |                   | CRSP, CRSN, CSP_, CSN_                                                                                                                                                                                 |                             | 0                        | 2                        | V     |

| Phase Disable Threshold                                      |                   | CSP4                                                                                                                                                                                                   |                             | 3                        | V <sub>CC</sub><br>- 0.4 | V     |

| CRS Sense Input Disable<br>Threshold                         |                   | CRSP                                                                                                                                                                                                   |                             | 3                        | V <sub>CC</sub><br>- 0.4 | V     |

| LOGIC AND I/O                                                |                   | •                                                                                                                                                                                                      |                             |                          |                          |       |

| Logic Input High Voltage                                     | VIH               | SHDN, SUS                                                                                                                                                                                              |                             | 2.4                      |                          | V     |

| Logic Input Low Voltage                                      | VIL               | SHDN, SUS                                                                                                                                                                                              |                             |                          | 0.8                      | V     |

| D0–D4 Logic Input High Voltage                               |                   |                                                                                                                                                                                                        |                             | 0.8                      |                          | V     |

| D0–D4 Logic Input Low Voltage                                |                   |                                                                                                                                                                                                        |                             |                          | 0.4                      | V     |

|                                                              |                   | High (V <sub>CC</sub> )                                                                                                                                                                                |                             | V <sub>CC</sub><br>- 0.4 |                          |       |

| OSC 3-Level Input Logic Levels                               | Vosc              | Medium (REF)                                                                                                                                                                                           |                             | 1.8                      | 2.2                      | V     |

|                                                              |                   | Low (GND)                                                                                                                                                                                              |                             |                          | 0.4                      |       |

|                                                              | Varia             | High                                                                                                                                                                                                   |                             | 1.2                      |                          | V     |

| SKIP Input Logic Levels                                      | VSKIP             | Low (GND)                                                                                                                                                                                              |                             |                          | 0.8                      | v     |

| Logic Output High Voltage                                    | V <sub>OH</sub>   | PWM_, DRSKP; Isource = 3mA                                                                                                                                                                             |                             | V <sub>CC</sub><br>- 0.4 |                          | V     |

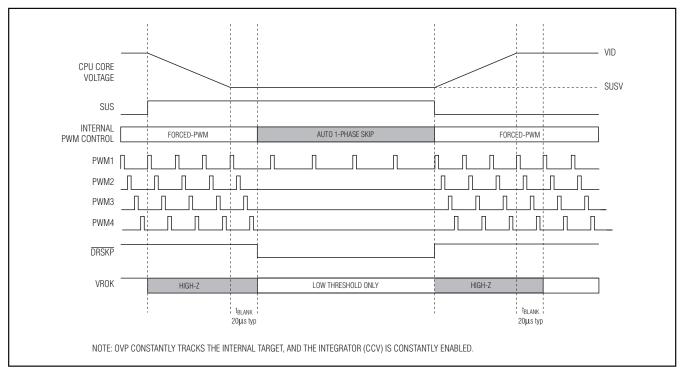

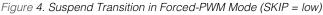

**Note 2:** VROK is blanked during the transitions, when the internal target is being slewed. See the *Output-Voltage Transition Timing* section. VROK is reenabled in t<sub>BLANK</sub> (20µs) after the transition is completed.

**Note 3:** Specifications to  $T_A = -40^{\circ}C$  are guaranteed by design and are not production tested.

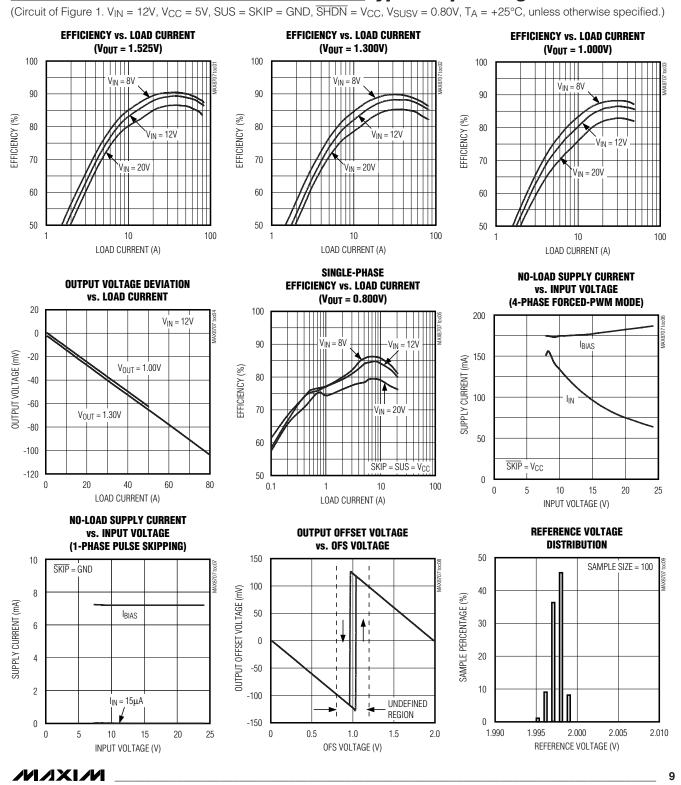

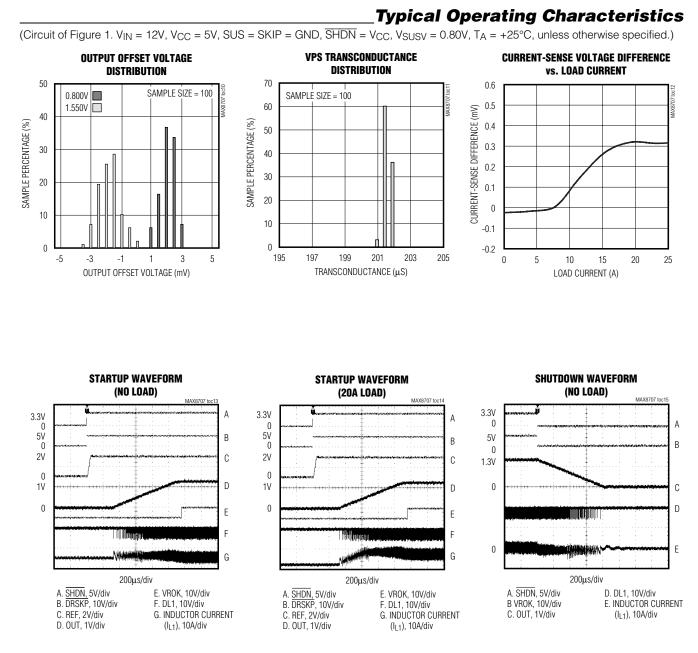

# **Typical Operating Characteristics**

**MAX8707**

(Circuit of Figure 1. V<sub>IN</sub> = 12V, V<sub>CC</sub> = 5V, SUS = SKIP = GND, SHDN = V<sub>CC</sub>, V<sub>SUSV</sub> = 0.80V, T<sub>A</sub> = +25°C, unless otherwise specified.)

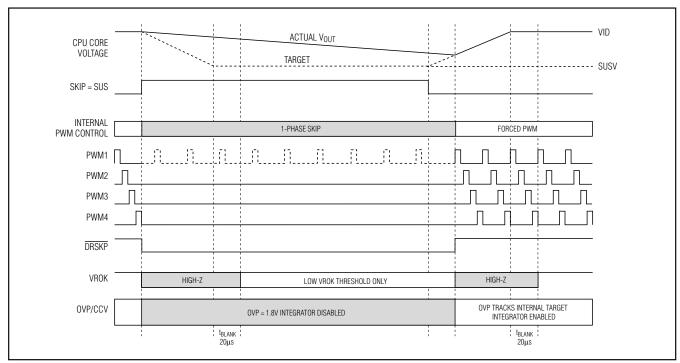

### LOAD TRANSIENT LOAD TRANSIENT **TRANSIENT PHASE REPEAT** $(V_{OUT} = 1.30V)$ $(V_{OUT} = 1.00V)$ MAX8707 toc16 MAX8707 toc17 AX8707 toc18 65A 70A 30A Α А Δ 0 0A 10A 1.30V 1.00V 1.30V B В В 12V 12V 20V С С С 0 0 0 20A 20A 10A NAMAMAMAMAMA D D 10A D WWWW 10A WWWWWW 0 0 WWWW $V_{IN}=20V$ MMMMM 0 20µs/div 2µs/div 20µs/div A. I<sub>OUT</sub> = 10A TO 65A, A. IOUT = 0 TO 70A, C. LX1. 10V/div A. $I_{OUT} = 0 \text{ TO } 30 \text{A},$ C. LX1, 10V/div C. LX1. 10V/div D. INDUCTOR CURRENT D. INDUCTOR CURRENT 100A/div D. INDUCTOR CURRENT 50A/div 50A/div (I<sub>L1</sub>), 10A/div (I<sub>L1</sub>), 10A/div B. V<sub>OUT</sub>, 100mV/div B. V<sub>OUT</sub>, 50mV/div B. V<sub>OUT</sub>, 100mV/div (IL1), 10A/div SUSPEND TRANSITION **DEEP-SLEEP TRANSITION** SUSPEND EXIT TRANSITION (SKIP = SUS)X8707 toc:19 MAX8707 toc21 3.3V 3.3V Α 3.3V A A 0 0 0 1.30V 1.30V 0.2V B В В 0 0.80V 0.80V С 5V 1.300V С 5V С 0 0 1.275V ..... D VWWWWWWWWWWWWWWWWWWWWWWWWWWWWWWWWWW D 5A D Ε Ε 5A F $I_{OUT} = 20A$ 20µs/div 20µs/div 200µs/div A. DPSLP, 5V/div D. INDUCTOR CURRENT A. SUS, 5V/div D. INDUCTOR CURRENT A. SUS, 5V/div D. INDUCTOR CURRENT B. OFS, 200mV/div (I<sub>L1</sub>), 10A/div B. V<sub>OUT</sub>, 500mV/div (I<sub>L1</sub>), 10A/div B. V<sub>OUT</sub>, 500mV/div (IL1), 10A/div C. V<sub>OUT</sub>, 25mV/div E. INDUCTOR CURRENT E. INDUCTOR CURRENT E. INDUCTOR CURRENT C. DRSKP, 5V/div C. DRSKP, 5V/div (I<sub>L3</sub>), 10A/div (IL3), 10A/div (IL3), 10A/div

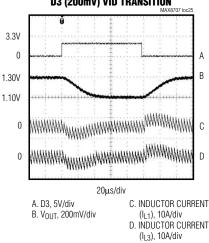

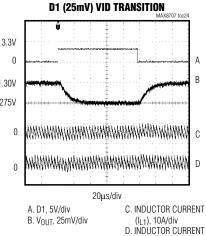

### Typical Operating Characteristics (continued)

(Circuit of Figure 1. V<sub>IN</sub> = 12V, V<sub>CC</sub> = 5V, SUS = SKIP = GND, SHDN = V<sub>CC</sub>, V<sub>SUSV</sub> = 0.80V, T<sub>A</sub> = +25°C, unless otherwise specified.)

SUSPEND TRANSITION SUSPEND TRANSITION (SKIP = SUS) (SKIP = GND)MAX8707 tor:22 MAX8707 toc23 3.3V 3.3V Α А 0 0 1.30V 1.30V В В 0.80V 0.80V 1.30V 5V 1.275V С 5V 0 С 0 D D Ε F 100µs/div 40µs/div A. SUS, 5V/div D. INDUCTOR CURRENT D. INDUCTOR CURRENT A. SUS, 5V/div B. V<sub>OUT</sub>, 500mV/div (IL1), 10A/div B. V<sub>OUT</sub>, 500mV/div (IL1), 10A/div E. INDUCTOR CURRENT E. INDUCTOR CURRENT C. DRSKP, 5V/div C. DRSKP, 5V/div (I<sub>L3</sub>), 10A/div (I<sub>L3</sub>), 10A/div D3 (200mV) VID TRANSITION

(I<sub>L3</sub>), 10A/div

Pin Description

|     |           | [                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1   | D2        | Low-Voltage VID DAC Code Input. The D0–D4 inputs do not have internal pullups. These 1.0V logic inputs are designed to interface directly with the CPU. In normal mode (Table 4, SUS = GND), the output voltage is set by the VID code indicated by the logic-level voltages on D0–D4. In suspend mode (SUS = high), the output voltage tracks the voltage at SUSV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2   | D3        | Low-Voltage VID DAC Code Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3   | D4        | Low-Voltage VID DAC Code Input (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |