Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **General Description**

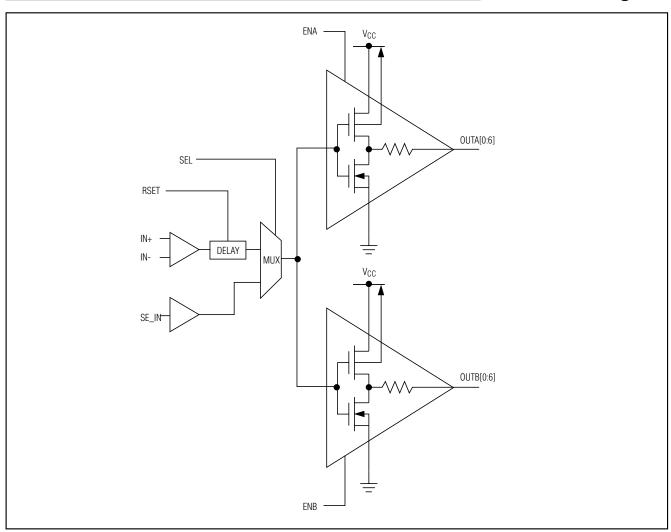

The MAX9160 125MHz, 14-port LVTTL/LVCMOS clock driver repeats the selected LVDS or LVTTL/LVCMOS input on two output banks. Each bank consists of seven LVTTL/LVCMOS series terminated outputs and a bank enable. The LVDS input has a fail-safe function. The MAX9160 has a propagation delay that can be adjusted using an external resistor to set the bias current for an internal delay cell. The LVTTL/LVCMOS outputs feature 200ps maximum output-to-output skew and ±100ps maximum added peak-to-peak jitter.

The MAX9160 is designed to operate with a 3.3V supply voltage over the extended temperature range of -40°C to +85°C. This device is available in 28-pin exposed- and nonexposed-pad TSSOP and 32-lead 5mm x 5mm QFN packages.

#### **Applications**

Cellular Base Stations Digital Cross-Connects

Servers **DSLAMs**

Add/Drop Multiplexers Networking Equipment

Typical Application Circuit and Functional Diagram appear at end of data sheet.

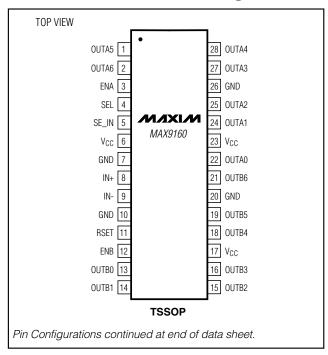

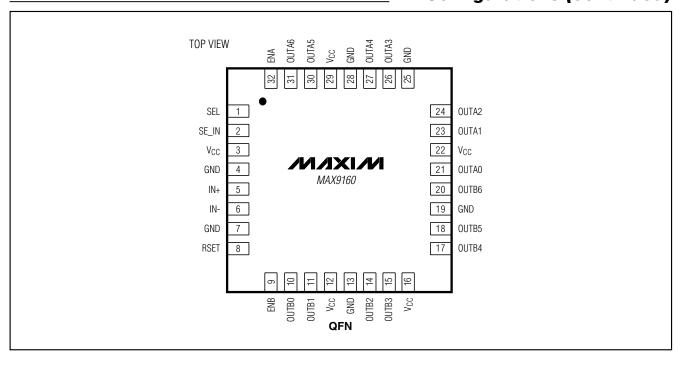

#### Pin Configurations

#### **Features**

- ♦ LVDS or LVTTL/LVCMOS Input Selection

- ♦ LVDS Input Fail-Safe Sets Outputs High for Open, **Undriven Short, or Undriven Parallel Termination**

- **♦ Two Output Banks with Separate Bank Enables**

- ♦ Integrated Output Series Termination for 60Ω

- ♦ 200ps (max) Output-to-Output Skew

- ♦ ±100ps (max) Peak-to-Peak Added Output Jitter

- ♦ 42% to 58% Output Duty Cycle at 125MHz

- ♦ Guaranteed 125MHz Operating Frequency

- ♦ LVDS Input Is High Impedance with V<sub>CC</sub> = 0V or Open (Hot Swappable)

- ◆ 28-Pin Exposed- and Nonexposed-Pad TSSOP or 32-Lead QFN Packages

- ♦ -40°C to +85°C Operating Temperature

- ♦ 3.0V to 3.6V Supply Voltage

#### Ordering Information

| PART        | TEMP RANGE     | PIN-PACKAGE   |

|-------------|----------------|---------------|

| MAX9160EUI  | -40°C to +85°C | 28 TSSOP      |

| MAX9160AEUI | -40°C to +85°C | 28 TSSOP-EP** |

| MAX9160EGJ* | -40°C to +85°C | 32 QFN-EP     |

<sup>\*</sup>Future product—contact factory for availability.

#### **Function Table**

| EN_          | SEL          | SE_IN        | V <sub>ID</sub>                                           | OUT_ |

|--------------|--------------|--------------|-----------------------------------------------------------|------|

| Н            | Н            | Н            | X                                                         | Н    |

| Н            | Н            | L or<br>open | X                                                         | L    |

| Н            | L or<br>open | X            | ≥ +50mV                                                   | Н    |

| Н            | L or<br>open | X            | ≤ -50mV                                                   | L    |

| Н            | L or open X  |              | Open, undriven short, or<br>undriven parallel termination | Н    |

| L or<br>Open | Х            | Х            | X                                                         | L    |

$V_{ID} = V_{IN+} - V_{IN-}$ H = high logic level

L = low logic level X = don't care

MIXIM

Maxim Integrated Products 1

<sup>\*\*</sup>Exposed pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND0.3V to IN+, IN- to GND0.3V to        |      |

|-------------------------------------------------------------|------|

| SE_IN, EN_, SEL, RSET, OUT_ to GND0.3V to V <sub>CC</sub> + |      |

| Output Short-Circuit Duration (OUT_) (Note 1)Continu        | Jous |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)       |      |

| 28-Pin TSSOP (derate 12.8mW/°C above +70°C)1024             | ₽mW  |

| 28-Pin TSSOP-EP (derate 23.8mW/°C above +70°C)1904          | ₽mW  |

| 32-Pin QFN (derate 21.2mW/°C above +70°C)1704               | ŀmW  |

| Storage Temperature Range   | 65°C to +150°C |

|-----------------------------|----------------|

| Junction Temperature        | +150°C         |

| Operating Temperature Range |                |

| ESD Protection              |                |

| Human Body Model (IN+, IN-) | ±16kV          |

| Human Body Model (SE_IN)    | ±8kV           |

| Soldering Temperature (10s) |                |

| , , ,                       |                |

Note 1: Short one output at a time. Do not exceed the absolute maximum junction temperature.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC}=3.0V\ to\ 3.6V,\ ENA=ENB=high,\ RSET=12k\Omega\pm1\%,\ differential\ input\ voltage\ IV_{ID}I=0.05V\ to\ 1.2V,\ input\ common-mode\ voltage\ V_{CM}=IV_{ID}/2\ I\ to\ 2.4V\ -\ IV_{ID}/2\ I,\ T_A=-40^{\circ}C\ to\ +85^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $V_{CC}=3.3V,\ IV_{ID}I=0.2V,\ V_{CM}=1.2V,\ T_A=+25^{\circ}C.)$  (Notes 2, 3)

| PARAMETER                         | SYMBOL                              | CONDIT                                             | TIONS                     | MIN                   | TYP   | MAX | UNITS |

|-----------------------------------|-------------------------------------|----------------------------------------------------|---------------------------|-----------------------|-------|-----|-------|

| SINGLE-ENDED INPUTS (SE_IN,       | ENA, ENB, S                         | SEL)                                               |                           |                       |       |     |       |

| Input High Voltage                | VIH                                 |                                                    |                           | 2.0                   |       | Vcc | V     |

| Input Low Voltage                 | VIL                                 |                                                    |                           | GND                   |       | 0.8 | V     |

| Input Clamp Voltage               | V <sub>CL</sub>                     | I <sub>CL</sub> = -18mA                            |                           | -1.5                  | -0.85 |     | V     |

| Input Current                     | I <sub>IN</sub>                     | V <sub>IN</sub> = high or low                      |                           | -20                   |       | +20 | μΑ    |

| SE_IN Capacitance (Note 4)        | CIN                                 | SE_IN to GND                                       |                           |                       |       | 6.1 | рF    |

| LVDS INPUT (IN+, IN-)             |                                     |                                                    |                           |                       |       |     |       |

| Differential Input High Threshold | V <sub>TH</sub>                     |                                                    |                           |                       |       | 50  | mV    |

| Differential Input Low Threshold  | V <sub>TL</sub>                     |                                                    |                           | -50                   |       |     | mV    |

| Learnest Original and             |                                     | $0.05V \le  V_{1D}  \le 0.6V$                      |                           | -15                   |       | +15 | ^     |

| Input Current                     | I <sub>IN+</sub> , I <sub>IN-</sub> | 0.6V < IV <sub>ID</sub> I ≤ 1.2V                   |                           | -20                   |       | +20 | μΑ    |

| Davier Off Invest Course          | I <sub>IN+(off)</sub>               | 0.05V ≤ IV <sub>ID</sub> I ≤ 0.6V, V <sub>C</sub>  | CC = 0V or open           | -15                   |       | +15 |       |

| Power-Off Input Current           | I <sub>IN-(off)</sub>               | 0.6V < IV <sub>ID</sub> I ≤ 1.2V, V <sub>C</sub> ( | C = 0V or open            | -20                   |       | +20 | μΑ    |

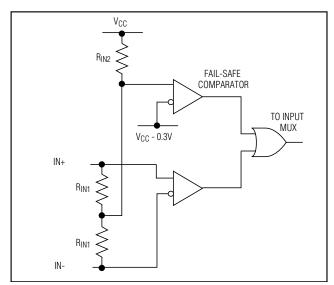

| Input Resistor 1                  | R <sub>IN1</sub>                    | V <sub>CC</sub> = 3.6V or 0V, Figure               | re 1                      | 51                    |       | 100 | kΩ    |

| Input Resistor 2                  | R <sub>IN2</sub>                    | V <sub>CC</sub> = 3.6V or 0 V, Figu                | ire 1                     | 200                   |       | 341 | kΩ    |

| Input Capacitance (Note 4)        | CIN                                 | IN+ or IN- to GND                                  |                           |                       |       | 6.0 | рF    |

| OUTPUTS (OUT_)                    |                                     |                                                    |                           |                       |       |     |       |

| Output Short-Circuit Current      | laa                                 | SEL = high, SE_IN = high                           | gh, V <sub>OUT</sub> = 0V | -115                  |       | 00  | mA    |

| (Note 1)                          | los                                 | SEL = low, V <sub>ID</sub> = 100m                  | V, V <sub>OUT</sub> = 0V  | -113                  |       | -30 | IIIA  |

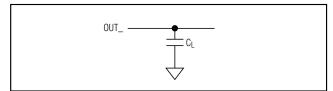

| Output Capacitance (Note 4)       | Co                                  | OUT_ to GND                                        |                           |                       |       | 9   | рF    |

|                                   | .,                                  | I <sub>OH</sub> = -100μA                           |                           | V <sub>CC</sub> - 0.2 |       |     |       |

| Output High Voltage               | Voн                                 | I <sub>OH</sub> = -4mA                             |                           | 2.4                   |       |     | V     |

|                                   |                                     | I <sub>OH</sub> = -8mA                             |                           |                       |       |     |       |

| 5 10 6 0 1 115 1 16 5             | .,                                  | SEL = low, inputs open, undriven short,            | I <sub>OH</sub> = -100μA  | V <sub>CC</sub> - 0.2 |       |     | .,    |

| Fail-Safe Output High Voltage     | VohFs                               | or undriven parallel                               | $I_{OH} = -4mA$           | 2.4                   |       |     | V     |

|                                   |                                     | terminated                                         | $I_{OH} = -8mA$           | 2.1                   | ·     |     |       |

#### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC}=3.0V\ to\ 3.6V,\ ENA=ENB=high,\ RSET=12k\Omega\pm1\%,\ differential\ input\ voltage\ IV_{ID}I=0.05V\ to\ 1.2V,\ input\ common-mode\ voltage\ V_{CM}=IV_{ID}/2\ I\ to\ 2.4V\ -\ IV_{ID}/2\ I,\ T_A=-40^{\circ}C\ to\ +85^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $V_{CC}=3.3V,\ IV_{ID}I=0.2V,\ V_{CM}=1.2V,\ T_A=+25^{\circ}C.)$  (Notes 2, 3)

| PARAMETER                | SYMBOL | CONDITIONS                                            | MIN | TYP | MAX | UNITS |

|--------------------------|--------|-------------------------------------------------------|-----|-----|-----|-------|

|                          |        | $I_{OL} = 100\mu A$                                   |     |     | 0.2 |       |

| Output Low Voltage       | VoL    | I <sub>OL</sub> = 4mA                                 |     |     | 0.4 | V     |

|                          |        | I <sub>OL</sub> = 8mA                                 |     |     | 0.8 |       |

| Supply Current           | loo    | SEL = high, SE_IN = high or low, no load              |     |     | 15  | μΑ    |

| Supply Current           | Icc    | SEL = low, V <sub>ID</sub> = -100mV or 100mV, no load |     | 7.0 | 10  | mA    |

| Output Series Resistance | Do     | Output switched high, V <sub>OUT</sub> = 1.65V        |     | 72  |     | 0     |

| (Note 5)                 | Rs     | Output switched low, V <sub>OUT</sub> = 1.65V         |     | 61  |     | Ω     |

#### **AC ELECTRICAL CHARACTERISTICS**

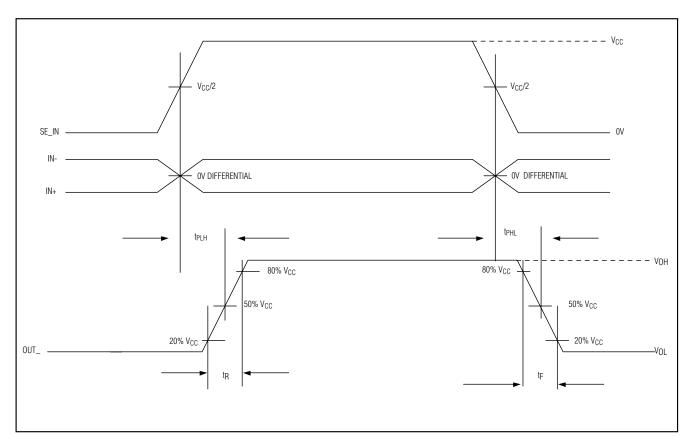

$(V_{CC}=3.0V\ to\ 3.6V,\ C_L=20pF,\ ENA=ENB=high,\ SEL=high\ or\ low,\ RSET=12k\Omega\pm1\%,\ differential\ input\ voltage\ IV_{ID}I=0.15V\ to\ 1.2V,\ input\ common-mode\ voltage\ V_{CM}=IV_{ID}/2I\ to\ 2.4V-IV_{ID}/2\ I,\ T_A=-40^{\circ}C\ to\ +85^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $V_{CC}=3.3V,\ IV_{ID}I=0.2V,\ V_{CM}=1.2V,\ T_A=+25^{\circ}C.)$  (Notes 6, 7, 8)

| PARAMETER                                      | SYMBOL             | со                                    | NDITIONS           | MIN   | TYP | MAX   | UNITS |  |

|------------------------------------------------|--------------------|---------------------------------------|--------------------|-------|-----|-------|-------|--|

| Rise Time                                      | t <sub>R</sub>     | Figures 2 and 3                       |                    | 1.4   |     | 2.95  | ns    |  |

| Fall Time                                      | tF                 | Figures 2 and 3                       |                    | 1.4   |     | 2.95  | ns    |  |

| Low-to-High Propagation Delay                  | tour               | SEL = low                             | $RSET = 12k\Omega$ | 5.3   | 6.5 | 8.0   | no    |  |

| IN+, IN- to OUT_                               | tPLH1              | 3EL = 10W                             | RSET = open        | 4.9   |     | 9.0   | ns    |  |

| High-to-Low Propagation Delay                  | tour               | SEL = low                             | $RSET = 12k\Omega$ | 5.3   | 6.4 | 8.0   | ns    |  |

| IN+, IN- to OUT_                               | <sup>t</sup> PHL1  | 3EL = 10W                             | RSET = open        | 4.9   |     | 9.0   | 115   |  |

| Low-to-High Propagation Delay<br>SE_IN to OUT_ | tPLH2              | SEL = high                            |                    | 2.2   | 2.9 | 3.8   | ns    |  |

| High-to-Low Propagation Delay SE_IN to OUT_    | tPHL2              | SEL = high                            |                    | 2.2   | 3.1 | 3.8   | ns    |  |

| Added Peak-to-Peak Output Jitter               | tJ                 | 100mV peak-to-pe<br>200kHz, 3.3V supp |                    |       |     | 100   | ps    |  |

| Outrout Duty Cycle                             | 000                | f <sub>IN</sub> = 125MHz              | 42                 |       | 58  | %     |       |  |

| Output Duty Cycle                              | ODC                | f <sub>IN</sub> = 35MHz               |                    | 48.75 |     | 51.25 | %     |  |

| Output-to-Output Skew (Note 9)                 | tskoo              |                                       |                    |       |     | 200   | ps    |  |

| Port to Port Claus (Note 10)                   | A                  | SE_IN to OUT_, SE                     |                    |       | 0.9 |       |       |  |

| Part-to-Part Skew (Note 10)                    | tskpp1             | IN+, IN- to OUT_, S                   | SEL = low          |       |     | 2.2   | ns    |  |

| Part to Part Skow (Note 11)                    | +                  | SE_IN to OUT_, SE                     |                    |       | 1.6 | 200   |       |  |

| Part-to-Part Skew (Note 11)                    | t <sub>SKPP2</sub> | IN+, IN- to OUT_, S                   | SEL = low          |       |     | 2.7   | ns    |  |

| Maximum Switching Frequency (Note 12)          | f <sub>MAX</sub>   |                                       |                    | 125   |     |       | MHz   |  |

Note 2: Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to ground except V<sub>TH</sub>, V<sub>TL</sub>, and V<sub>ID</sub>.

**Note 3:** Parameter limits over temperature are guaranteed by design and characterization. Devices are production tested at  $T_A = +25$ °C.

#### **AC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 3.0 \text{V to } 3.6 \text{V}, C_L = 20 \text{pF}, \text{ENA} = \text{ENB} = \text{high}, \text{SEL} = \text{high or low, RSET} = 12 \text{k}\Omega \pm 1\%$ , differential input voltage  $V_{CM} = |V_{ID}/2|$  to  $2.4 \text{V} - |V_{ID}/2|$ ,  $V_{CM} = 1.2 \text{V}$ , input common-mode voltage  $V_{CM} = |V_{ID}/2|$  to  $2.4 \text{V} - |V_{ID}/2|$ ,  $V_{CM} = 1.2 \text{V}$ ,  $V_$

- Note 4: Guaranteed by design and characterization.

- **Note 5:** Total of driver output resistance and integrated series resistor.

- Note 6: AC parameters are guaranteed by design and characterization and are not production tested. Limits are set at ±6 sigma.

- **Note 7:** C<sub>1</sub> includes scope probe and test jig capacitance.

- Note 8: Pulse generator conditions for SE\_IN input: frequency = 125MHz, 50% duty cycle,  $Z_O = 50\Omega$ ,  $t_R = 1.2$ ns, and  $t_F = 1.2$ ns (20% to 80%),  $V_{OH} = V_{CC}$ ,  $V_{OL} = 0$ V. Pulse generator conditions for IN+, IN- input: frequency = 125MHz, 50% duty cycle,  $Z_O = 50\Omega$ ,  $t_R = 1$ ns, and  $t_F = 1$ ns (20% to 80%).  $V_{ID}$ ,  $V_{CM}$  as specified in AC Electrical Characteristics general conditions.

- Note 9: Measured between outputs with identical loads at V<sub>CC</sub>/2 for a same-edge transition.

- Note 10: tskpp1 is the greatest difference in propagation delay between different parts operating under identical conditions within rated conditions.

- Note 11: t<sub>SKPP2</sub> is the greatest difference in propagation delay between different parts operating within rated conditions.

- Note 12: All AC specifications met at f<sub>MAX</sub>.

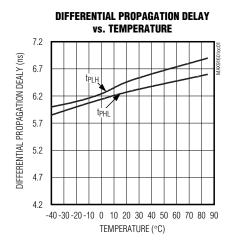

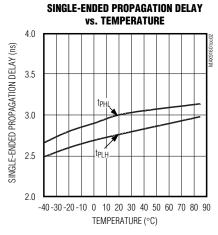

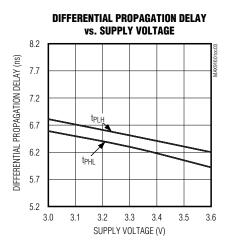

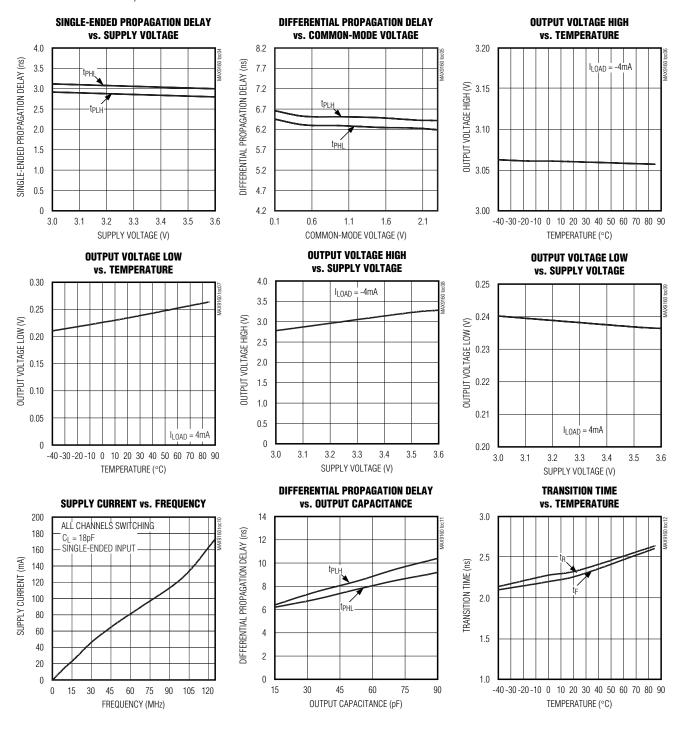

#### Typical Operating Characteristics

$(\text{MAX9160 with RSET} = 12\text{k}\Omega \pm 1\%, \text{V}_{CC} = 3.3\text{V}, \text{C}_{L} = 20\text{pF}, \text{ENA} = \text{ENB} = \text{high, IV}_{IDI} = 0.2, \text{V}_{CM} = 1.2\text{V}, \text{f}_{IN} = 125\text{MHz}, \text{T}_{A} = +25^{\circ}\text{C}, \text{unless otherwise noted.})$

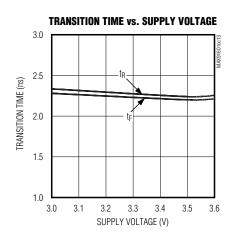

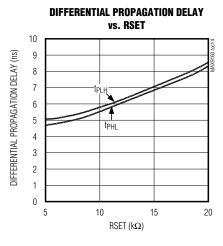

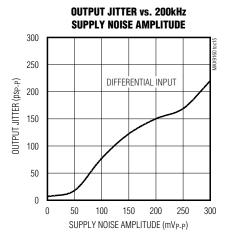

#### **Typical Operating Characteristics (continued)**

$(\text{MAX9160 with RSET} = 12\text{k}\Omega \pm 1\%, \text{V}_{CC} = 3.3\text{V}, \text{C}_{L} = 20\text{pF}, \text{ENA} = \text{ENB} = \text{high, IV}_{ID}\text{I} = 0.2, \text{V}_{CM} = 1.2\text{V}, \text{f}_{IN} = 125\text{MHz}, \text{T}_{A} = +25^{\circ}\text{C}, \text{unless otherwise noted.})$

### Typical Operating Characteristics (continued)

(MAX9160 with RSET = 12k $\Omega$  ±1%, V<sub>CC</sub> = 3.3V, C<sub>L</sub> = 20pF, ENA = ENB = high, IV<sub>ID</sub>I = 0.2, V<sub>CM</sub> = 1.2V, f<sub>IN</sub> = 125MHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

### **Pin Description**

| PI                            | PIN                  |       | FUNCTION                                                                                                                                                                                                      |  |  |  |  |  |  |

|-------------------------------|----------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| QFN                           | TSSOP                | NAME  | FUNCTION                                                                                                                                                                                                      |  |  |  |  |  |  |

| 1                             | 4                    | SEL   | LVCMOS/LVTTL Level Logic Input. SEL = high selects SE_IN. SEL = low or open selects IN+, IN SEL is pulled to GND by an internal resistor.                                                                     |  |  |  |  |  |  |

| 2                             | 5                    | SE_IN | LVCMOS/LVTTL Level Input. SE_IN is pulled to GND by an internal resistor.                                                                                                                                     |  |  |  |  |  |  |

| 3, 12, 16,<br>22, 29          | 6, 17, 23            | Vcc   | Positive Supply Voltage. Bypass with 0.1µF and 0.001µF capacitors to ground.                                                                                                                                  |  |  |  |  |  |  |

| 4, 7, 13,<br>19, 25, 28       | 7, 10, 20, 26        | GND   | Ground                                                                                                                                                                                                        |  |  |  |  |  |  |

| 5                             | 8                    | IN+   | Noninverting Input of Differential Input                                                                                                                                                                      |  |  |  |  |  |  |

| 6                             | 9                    | IN-   | Inverting Input of Differential Input                                                                                                                                                                         |  |  |  |  |  |  |

| 8                             | 11                   | RSET  | Connect a 12k $\Omega$ ±1% resistor to ground to decrease the minimum to maximum IN+, IN- to OUT_ propagation delay.                                                                                          |  |  |  |  |  |  |

| 9 12                          |                      | ENB   | LVCMOS/LVTTL Level Logic Input. When ENB = high, outputs OUTB_ are enabled and follow the selected input. When ENB = low or open, outputs OUTB_ are driven low. ENB is pulled to GND by an internal resistor. |  |  |  |  |  |  |

| 10, 11, 14, 15,<br>17, 18, 20 | 13–16, 18,<br>19, 21 | OUTB_ | Bank B LVCMOS/LVTTL Outputs                                                                                                                                                                                   |  |  |  |  |  |  |

#### Pin Description (continued)

| P                             | IN                          | NAME           | FUNCTION                                                                                                                                                                                                      |  |  |  |  |  |

|-------------------------------|-----------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| QFN                           | TSSOP                       | NAME           | FUNCTION                                                                                                                                                                                                      |  |  |  |  |  |

| 21, 23, 24, 26,<br>27, 30, 31 | 1, 2, 22, 24, 25,<br>27, 28 | OUTA_          | Bank A LVCMOS/LVTTL Outputs                                                                                                                                                                                   |  |  |  |  |  |

| 32                            | 3                           | ENA            | LVCMOS/LVTTL Level Logic Input. When ENA = high, outputs OUTA_ are enabled and follow the selected input. When ENA = low or open, outputs OUTA_ are driven low. ENA is pulled to GND by an internal resistor. |  |  |  |  |  |

| EP*                           |                             | Exposed<br>Pad | Solder to PC board                                                                                                                                                                                            |  |  |  |  |  |

<sup>\*</sup>MAX9160EGJ and MAX9160AEUI.

Figure 1. Fail-Safe Input Circuit

#### Detailed Description

The MAX9160 125MHz, 14-port LVTTL/LVCMOS clock driver repeats the selected LVDS or LVTTL/LVCMOS input on two output banks. Each bank consists of seven LVTTL/LVCMOS series terminated outputs and a bank enable. The LVDS input has a fail-safe function. The MAX9160 has a propagation delay that can be adjusted using an external resistor to set the bias current for an internal delay cell. The LVTTL/LVCMOS outputs feature 200ps maximum output-to-output skew and ±100ps maximum added peak-to-peak jitter.

The MAX9160 is designed to operate with a 3.3V supply voltage over the extended temperature range of

Figure 2. Output Load

-40°C to +85°C. This device is available in 28-pin exposed and nonexposed pad TSSOP and 32-lead 5mm x 5mm QFN packages.

#### Fail-Safe

A fail-safe circuit on the MAX9160 sets enabled outputs high when the LVDS input is:

- Open

- Undriven and shorted

- · Undriven and terminated

Without a fail-safe circuit, when the LVDS input is selected and undriven, noise may cause the enabled outputs to switch. Open or undriven terminated input conditions can occur when a cable is disconnected or cut, or when a driver output is in high impedance. A shorted input can occur because of a cable failure.

When the MAX9160 LVDS input is driven with a differential signal with a common-mode voltage between IV<sub>ID</sub>/2I and 2.4V - IV<sub>ID</sub>/2I, the fail-safe circuit is not activated. If the input is open, undriven and shorted, or undriven and parallel terminated, an internal resistor in the fail-safe circuit pulls both of the LVDS inputs above VCC - 0.3V, activating the fail-safe circuit and forcing the output high (Figure 1).

Figure 3. Transition Time and Propagation Delay Timing Diagram

#### **Propagation Delay and RSET**

The MAX9160 delay can be adjusted by connecting a resistor from RSET to ground. See *Typical Operating Characteristics* for a graph of delay vs. RSET.

#### **Output Enables**

Each bank of seven LVTTL/LVCMOS drivers is controlled by an output enable. Outputs follow the selected input when  $EN_{-}$  is high. Outputs are low (not high impedance) when  $EN_{-}$  = low.

#### **Power Dissipation and Package Type**

Power dissipation at high switching frequencies may exceed the power dissipation capacity of the standard TSSOP package (see the Supply Current vs. Frequency graph in the *Typical Operating Characteristics*). An EP version of the TSSOP package is available that dissipates higher power. Also, a space-saving QFN package with EP is available. The EP must be soldered to the PC board.

#### Supply Bypassing

Bypass each supply pin with high-frequency surface-mount ceramic  $0.1\mu F$  and  $0.001\mu F$  capacitors in parallel as close to the device as possible, with the smaller value capacitor closest to the device.

#### **Board Layout**

A four-layer PC board that provides separate power, ground, input, and output signals is recommended. Keep input and output signals separated to prevent coupling.

\_Chip Information

**TRANSISTOR COUNT: 756**

PROCESS: CMOS

### **Functional Diagram**

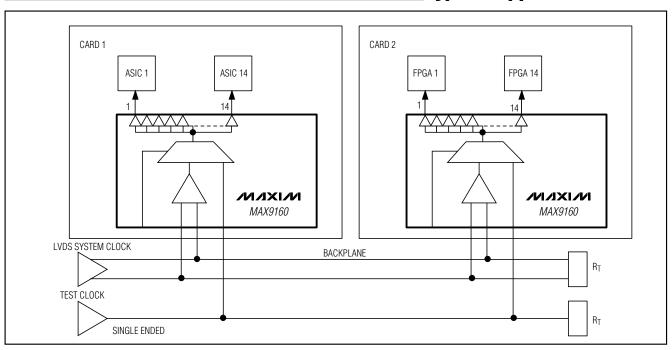

### **Typical Application Circuit**

### Pin Configurations (continued)

10 \_\_\_\_\_\_ /VIXI/VI

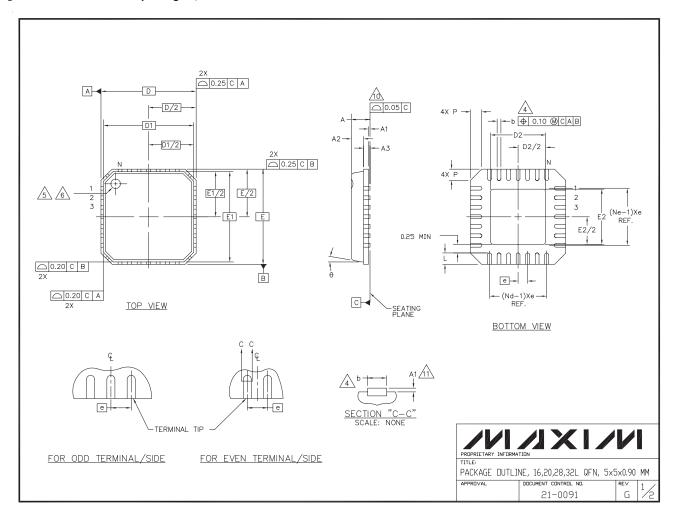

#### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

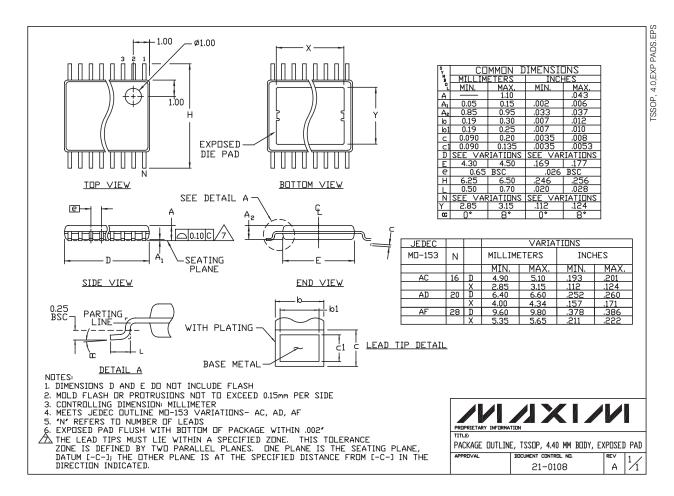

#### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

#### NOTES:

- 1. DIE THICKNESS ALLOWABLE IS 0.305mm MAXIMUM (.012 INCHES MAXIMUM)

- 2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. 1994.

- N IS THE NUMBER OF TERMINALS.

Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION & Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

- 4 DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

- THE PIN #1 IDENTIFIER MUST BE EXISTED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR INK/ LASER MARKED.

- 6. EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

- 7. ALL DIMENSIONS ARE IN MILLIMETERS.

- 8. PACKAGE WARPAGE MAX 0.05mm.

- APPLIED FOR EXPOSED PAD AND TERMINALS.

EXCLUDE EMBEDDED PART OF EXPOSED PAD FROM MEASURING.

- 10. MEETS JEDEC MO220.

- 11. THIS PACKAGE OUTLINE APPLIES TO ANVIL SINGULATION (STEPPED SIDES) AND TO SAW SINGULATION (STRAIGHT SIDES) QFN STYLES.

| S      |      | COMMON    |      |    |

|--------|------|-----------|------|----|

| SYMBO. | DII  | MENSION   | No.  |    |

| ို     | MIN. | NOM.      | MAX. | Tε |

| Α      | 0.80 | 0.90      | 1.00 |    |

| A1     | 0.00 | 0.01      | 0.05 |    |

| A2     | 0.00 | 0.65      | 1.00 |    |

| A3     |      | 0.20 REF. |      |    |

| D      |      | 5.00 BSC  |      |    |

| D1     |      | 4.75 BSC  |      |    |

| Ε      |      | 5.00 BSC  |      |    |

| E1     |      | 4.75 BSC  |      |    |

| θ      | 0,   | -         | 12°  |    |

| Р      | 0    |           | 0.60 |    |

| D2     | 1.25 | -         | 3.25 |    |

| E2     | 1.25 | _         | 3.25 |    |

| S   | DITCH | VARIAT   | ION B |                | S  | PITCH | VARIA1   | TION B |                | S  | PITCH | VARIAT   | IONI C |                | S  | PITCH | VARIAT   | ION D |                |

|-----|-------|----------|-------|----------------|----|-------|----------|--------|----------------|----|-------|----------|--------|----------------|----|-------|----------|-------|----------------|

| M B | FIICH | VARIAI   |       | N <sub>O</sub> | MB | FIICH | VARIA    |        | N <sub>O</sub> | MB | PITCH | VARIAI   | ION C  | N <sub>O</sub> | MB | PITCH | VARIAI   | ION D | N <sub>O</sub> |

| ို  | MIN.  | NOM.     | MAX.  | T <sub>E</sub> | ို | MIN.  | NOM.     | MAX.   | T <sub>E</sub> | ို | MIN.  | NOM.     | MAX.   | T <sub>E</sub> | ို | MIN.  | NOM.     | MAX.  | ΤE             |

| e   |       | 0.80 BSC |       |                | e  |       | 0.65 BSC |        |                | e  |       | 0.50 BSC |        |                | e  |       | 0.50 BSC |       |                |

| N   |       | 16       |       | 3              | N  |       | 20       |        | 3              | N  |       | 28       |        | 3              | N  |       | 32       |       | 3              |

| Nd  |       | 4        |       | 3              | Nd |       | 5        |        | 3              | Nd |       | 7        |        | 3              | Nd |       | 8        |       | 3              |

| Ne  |       | 4        |       | 3              | Ne |       | 5        |        | 3              | Ne |       | 7        |        | 3              | Ne |       | 8        |       | 3              |

| L   | 0.35  | 0.55     | 0.75  |                | L  | 0.35  | 0.55     | 0.75   |                | L  | 0.35  | 0.55     | 0.75   |                | L  | 0.30  | 0.40     | 0.50  |                |

| Ь   | 0.28  | 0.33     | 0.40  | 4              | Ь  | 0.23  | 0.28     | 0.35   | 4              | Ь  | 0.18  | 0.23     | 0.30   | 4              | Ь  | 0.18  | 0.23     | 0.30  | 4              |

#### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.