Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **General Description**

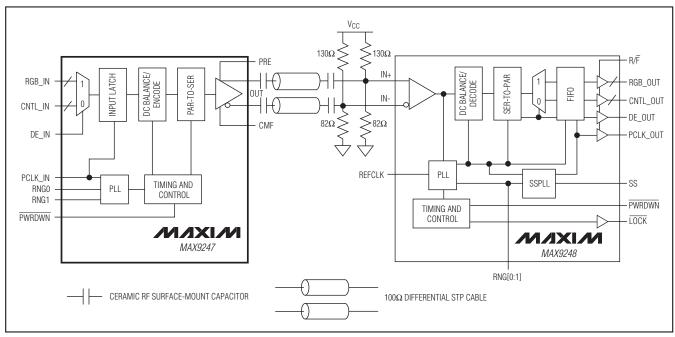

The MAX9247 digital video parallel-to-serial converter serializes 27 bits of parallel data into a serial-data stream. Eighteen bits of video data and 9 bits of control data are encoded and multiplexed onto the serial interface, reducing the serial-data rate. The data-enable input determines when the video or control data is serialized.

The MAX9247 pairs with the MAX9248/MAX9250 deserializers to form a complete digital video serial link. Interconnect can be controlled-impedance PCB traces or twisted-pair cable. Proprietary data encoding reduces EMI and provides DC balance. DC balance allows ACcoupling, providing isolation between the transmitting and receiving ends of the interface. The LVDS output is internally terminated with  $100\Omega$ . For operating frequencies less than 35MHz, the MAX9247 can also pair with the MAX9218 deserializer.

ESD tolerance is specified for ISO 10605 with ±10kV Contact Discharge and ±30kV Air-Gap Discharge.

The MAX9247 operates from a +3.3V core supply and features a separate input supply for interfacing to 1.8V to 3.3V logic levels. This device is available in a 48-lead LQFP package and is specified from -40°C to +85°C or -40°C to +105°C.

### **Applications**

Navigation System Displays In-Vehicle Entertainment Systems Video Cameras **LCDs**

#### Features

- ♦ Preemphasis Improves Eye Diagram and Signal Integrity at the Output

- Proprietary Data Encoding for DC Balance and Reduced ÉMI

- Control Data Sent During Video Blanking

- Five Control Data Inputs are Single-Bit-Error **Tolerant**

- ♦ Programmable Phase-Shifted LVDS Signaling Reduces EMI

- ♦ Output Common-Mode Filter Reduces EMI

- **Greater Than 10m STP Cable Drive**

- Wide ±2% Reference Clock Tolerance

- ISO 10605 and IEC 61000-4-2 Level 4 **ESD Protection**

- Separate Input Supply Allows Interface to 1.8V to 3.3V Logic

- ♦ +3.3V Core Supply

- Space-Saving LQFP Package

- -40°C to +85°C and -40°C to +105°C Operating **Temperature Ranges**

#### **Ordering Information**

| PART          | TEMP RANGE      | PIN-PACKAGE |

|---------------|-----------------|-------------|

| MAX9247ECM+   | -40°C to +85°C  | 48 LQFP     |

| MAX9247ECM/V+ | -40°C to +85°C  | 48 LQFP     |

| MAX9247GCM+   | -40°C to +105°C | 48 LQFP     |

| MAX9247GCM/V+ | -40°C to +105°C | 48 LQFP     |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package. N denotes an automotive qualified part.

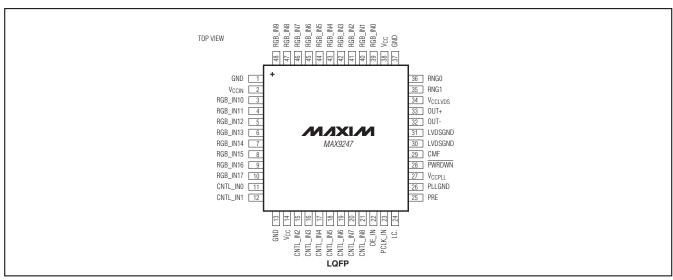

### Pin Configuration

MIXIM

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> _to _GND                           |                        |

|----------------------------------------------------|------------------------|

| Any Ground to Any Ground                           |                        |

| OUT+, OUT-, CMF to LVDSGND                         | 0.5V to +4.0V          |

| OUT+, OUT- Short Circuit to LVDSGND                |                        |

| or VCCLVDS                                         | Continuous             |

| OUT+, OUT- Short Through 0.125µF (or s             | maller),               |

| 25V Series Capacitor                               | 0.5V to +16V           |

| RGB_IN[17:0], CNTL_IN[8:0], DE_IN,                 |                        |

| RNG0, RNG1, PRE, PCLK_IN,                          |                        |

| PWRDWN to GND                                      | 0.5V to (VCCIN + 0.5V) |

| Continuous Power Dissipation ( $T_A = +70^{\circ}$ | C)                     |

| 48-Lead LQFP (derate 20.8mW/°C abov                | e +70°C)1666.7mW       |

| ESD Protection                                     |                        |

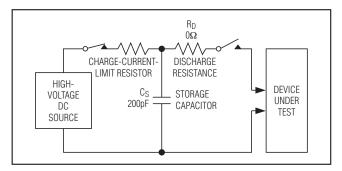

| Machine Model ( $R_D = 0\Omega$ , $C_S = 200pF$ )  |                        |

| All Pins to GND                                         | .±200V |

|---------------------------------------------------------|--------|

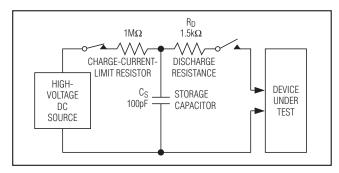

| Human Body Model ( $R_D = 1.5k\Omega$ , $C_S = 100pF$ ) |        |

| All Pins to GND                                         | ±3kV   |

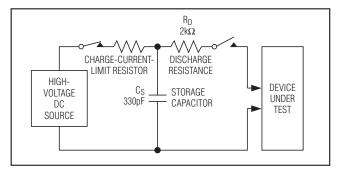

| ISO 10605 ( $R_D = 2k\Omega$ , $C_S = 330pF$ )          |        |

| Contact Discharge (OUT+, OUT-) to LVDSGND               | .±10kV |

| Air-Gap Discharge (OUT+, OUT-) to LVDSGND               | .±30kV |

| IEC 61000-4-2 ( $R_D = 330\Omega$ , $C_S = 150pF$ )     |        |

| Contact Discharge (OUT+, OUT-) to LVDSGND               | .±10kV |

| Air-Gap Discharge (OUT+, OUT-) to LVDSGND               | .±15kV |

| Storage Temperature Range65°C to 4                      | +150°C |

| Junction Temperature                                    |        |

| Lead Temperature (soldering, 10s)                       | +300°C |

| Soldering Temperature (reflow)                          | +260°C |

|                                                         |        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0V \text{ to } +3.6V, R_L = 100\Omega \pm 1\%, \overline{PWRDWN} = \text{high, PRE} = \text{low, TA} = -40^{\circ}\text{C} \text{ to } +105^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{CC} = +3.3V, T_A = +25^{\circ}\text{C.}) \text{ (Notes 1, 2)}$

| PARAMETER                                                        | SYMBOL           | CO                                                   | ONDITION                                                                                                                     | S                                                                              | MIN                      | TYP  | MAX                     | UNITS |

|------------------------------------------------------------------|------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------|------|-------------------------|-------|

| SINGLE-ENDED INPUTS (RGB                                         | _IN[17:0], C     | NTL_IN[8:0], DE                                      | IN, PCLK                                                                                                                     | _IN, PWRDWN,                                                                   | RNG_, PRE)               |      |                         |       |

| High-Level Input Voltage                                         | VIH              | $V_{CCIN} = 1.71V to$                                | o < 3V (No                                                                                                                   | te 3)                                                                          | 0.65 x V <sub>CCIN</sub> | V    | CCIN + 0.3              | V     |

| High-Level Input voltage                                         | VIH              | $V_{CCIN} = 3.0V$ to                                 | 3.6V                                                                                                                         |                                                                                | 2                        | 0    | .3 + V <sub>CCIN</sub>  | V     |

| Low-Level Input Voltage                                          | VIL              | $V_{CCIN} = 1.71V to$                                | o < 3V (No                                                                                                                   | te 3)                                                                          | -0.3                     | C    | 0.3 x V <sub>CCIN</sub> | V     |

| Low-Level Input Voltage                                          | VIL              | $V_{CCIN} = 3.0V$ to                                 | 3.6V                                                                                                                         |                                                                                | -0.3                     |      | +0.8                    | V     |

| Input Current                                                    | liN              | VCCIN = 1.71V<br>to 3.6V,<br>PWRDWN =<br>high or low | V <sub>CCIN</sub> = 1.71V<br>to 3.6V,<br>PWRDWN = V <sub>IN</sub> = -0.3V<br>(MAX9247<br>V <sub>IN</sub> = -0.15<br>(MAX9247 |                                                                                | -100                     | +20  |                         | μΑ    |

|                                                                  |                  | Tilgit of low                                        | $V_{IN} = 0V t$                                                                                                              | o (V <sub>CCIN</sub> + 0.3V)                                                   | -20                      |      | +20                     |       |

| Input Clamp Voltage                                              | V <sub>CL</sub>  | $I_{CL} = -18mA$                                     |                                                                                                                              |                                                                                |                          |      | -1.5                    | V     |

| LVDS OUTPUTS (OUT+, OUT-)                                        |                  |                                                      |                                                                                                                              |                                                                                |                          |      |                         |       |

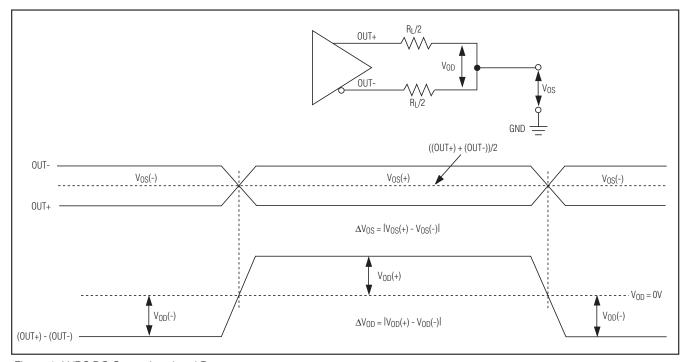

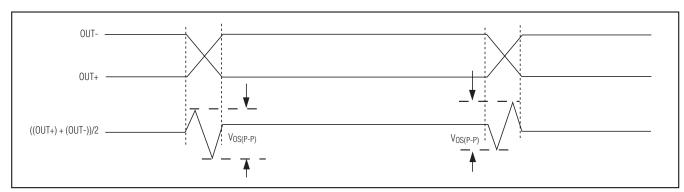

| Differential Output Voltage                                      | V <sub>OD</sub>  | Figure 1                                             |                                                                                                                              |                                                                                | 250                      | 335  | 450                     | mV    |

| Change in V <sub>OD</sub> Between<br>Complementary Output States | ΔV <sub>OD</sub> | Figure 1                                             |                                                                                                                              |                                                                                |                          |      | 20                      | mV    |

| Common-Mode Voltage                                              | Vos              | Figure 1                                             |                                                                                                                              |                                                                                | 1.125                    | 1.29 | 1.475                   | V     |

| Change in VOS Between<br>Complementary Output States             | ΔV <sub>OS</sub> | Figure 1                                             |                                                                                                                              |                                                                                |                          |      | 20                      | mV    |

| Output Short-Circuit Current                                     | los              | V <sub>OUT+</sub> or V <sub>OUT-</sub>               | = 0V or 3.6                                                                                                                  | 6V                                                                             | -15                      | ±8   | +15                     | mA    |

| Magnitude of Differential Output Short-Circuit Current           | I <sub>OSD</sub> | V <sub>OD</sub> = 0V                                 |                                                                                                                              |                                                                                |                          | 5.5  | 15                      | mA    |

| Output High-Impedance<br>Current                                 | loz              | PWRDWN = low<br>or V <sub>CC</sub> _ = 0V            |                                                                                                                              | $V_{OUT+} = 0V,$<br>$V_{OUT-} = 3.6V$<br>$V_{OUT+} = 3.6V,$<br>$V_{OUT-} = 0V$ | -1                       |      | +1                      | μА    |

### **DC ELECTRICAL CHARACTERISTICS (continued)**

$(\text{VCC}_- = +3.0 \text{V to } +3.6 \text{V}, \, \text{R}_L = 100 \Omega \, \pm 1\%, \, \overline{\text{PWRDWN}} = \text{high, PRE} = \text{low, TA} = -40 ^{\circ}\text{C} \, \, \text{to } +105 ^{\circ}\text{C}, \, \, \text{unless otherwise noted.}$  Typical values are at V<sub>CC</sub>\_ = +3.3 V, T<sub>A</sub> = +25 ^{\circ}\text{C}.) (Notes 1, 2)

| PARAMETER                      | SYMBOL         | CONDI                                                                  | TIONS     |         | MIN | TYP | MAX | UNITS   |

|--------------------------------|----------------|------------------------------------------------------------------------|-----------|---------|-----|-----|-----|---------|

| Differential Output Resistance | R <sub>O</sub> |                                                                        |           |         | 78  | 110 | 147 | Ω       |

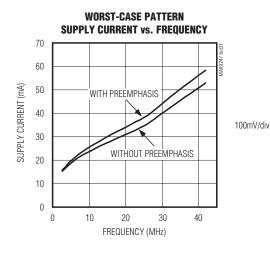

|                                |                |                                                                        | 2.5MHz    | PRE = 0 |     | 15  | 25  |         |

|                                |                |                                                                        | 2.5101112 | PRE = 1 |     |     | 27  |         |

|                                |                |                                                                        | 5MHz      | PRE = 0 |     | 18  | 25  |         |

|                                |                |                                                                        | SIVITZ    | PRE = 1 |     |     | 27  |         |

|                                | Iccw           | $R_L = 100\Omega \pm 1\%,$ $C_L = 5pF,$ continuous 10 transition words | 10MHz     | PRE = 0 |     | 23  | 28  | i<br>mA |

| Worst-Case Supply Current      |                |                                                                        | TOIVIE    | PRE = 1 |     |     | 30  |         |

|                                |                |                                                                        | 20MHz     | PRE = 0 |     | 33  | 39  | IIIA    |

|                                |                |                                                                        |           | PRE = 1 |     |     | 42  |         |

|                                |                |                                                                        | 051411    | PRE = 0 |     | 50  | 65  |         |

|                                |                |                                                                        | 35MHz     | PRE = 1 |     |     | 69  |         |

|                                |                |                                                                        | 40041.1-  | PRE = 0 |     | 60  | 70  |         |

|                                |                |                                                                        | 42MHz     | PRE = 1 |     |     | 75  |         |

| Power-Down Supply Current      | ICCZ           | (Note 4)                                                               |           |         |     |     | 50  | μΑ      |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC\_} = +3.0V \text{ to } +3.6V, \ R_L = 100\Omega \pm 1\%, \ C_L = 5pF, \ \overline{PWRDWN} = \text{high, PRE} = \text{low, T}_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}, \ \text{unless otherwise noted.}$  Typical values are at  $V_{CC\_} = +3.3V, \ T_A = +25^{\circ}\text{C.}$ ) (Note 3)

| PARAMETER                                                    | SYMBOL                          | CONDI                                                                   | ITIONS     |           | MIN  | TYP | MAX   | UNITS  |

|--------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------|------------|-----------|------|-----|-------|--------|

| PCLK_IN TIMING REQUIREMENT                                   | s                               |                                                                         |            |           |      |     |       | •      |

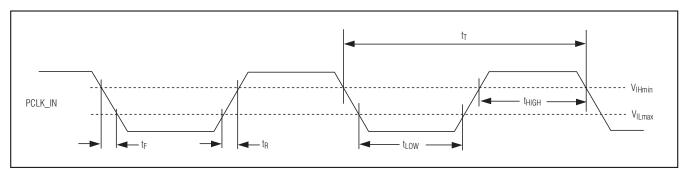

| Clock Period                                                 | +                               | Figure 0                                                                | MAX9247    | 'ECM      | 23.8 |     | 400.0 | 200    |

| Clock Feriod                                                 | t⊤                              | Figure 2                                                                | MAX9247GCM |           | 28.6 |     | 400.0 | ns     |

| Clask Fragues av                                             | f                               | MAX9247ECM                                                              |            |           | 2.5  |     | 42.0  | NAL I- |

| Clock Frequency                                              | fCLK                            | MAX9247GCM                                                              |            |           | 2.5  |     | 35.0  | MHz    |

| Clock Frequency Difference from Deserializer Reference Clock | Δf <sub>CLK</sub>               |                                                                         |            |           | -2   |     | +2    | %      |

| Clock Duty Cycle                                             | DC                              | t <sub>HIGH</sub> /t <sub>T</sub> or t <sub>LOW</sub> /t <sub>T</sub> , | Figure 2   |           | 35   | 50  | 65    | %      |

| Clock Transition Time                                        | t <sub>R</sub> , t <sub>F</sub> | Figure 2                                                                |            |           |      |     | 2.5   | ns     |

| SWITCHING CHARACTERISTICS                                    |                                 |                                                                         |            |           |      |     |       |        |

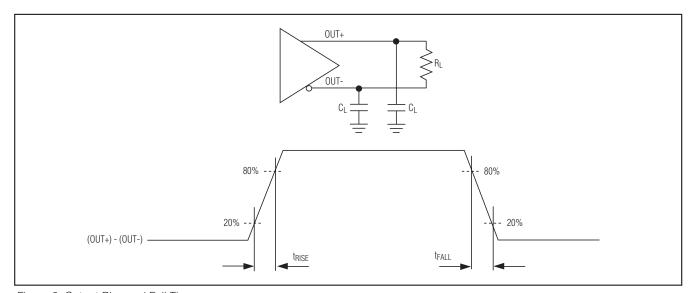

| Outrout Die e Tire e                                         |                                 | 20% to 80%,                                                             | PF         | RE = low  |      | 280 | 370   |        |

| Output Rise Time                                             | <sup>t</sup> RISE               | V <sub>OD</sub> ≥ 250mV, Figu                                           | re 3 PF    | RE = high |      | 240 | 320   | ps     |

| Outrout Fall Times                                           | <b>4</b>                        | 80% to 20%,                                                             | PF         | RE = low  |      | 280 | 370   |        |

| Output Fall Time                                             | tfall                           | V <sub>OD</sub> ≥ 250mV, Figu                                           | re 3 PF    | RE = high |      | 240 | 320   | ps     |

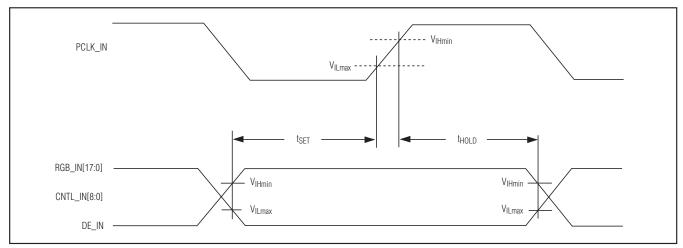

| Input Setup Time                                             | tset                            | Figure 4                                                                |            |           | 3    |     |       | ns     |

| Input Hold Time                                              | tHOLD                           | Figure 4                                                                | •          | ·         | 3    |     | •     | ns     |

### **AC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC_{-}} = +3.0V \text{ to } +3.6V, R_{L} = 100\Omega \pm 1\%, C_{L} = 5pF, \overline{PWRDWN} = high, PRE = low, T_{A} = -40^{\circ}C \text{ to } +105^{\circ}C, unless otherwise noted.}$  Typical values are at  $V_{CC_{-}} = +3.3V, T_{A} = +25^{\circ}C.$ ) (Note 3)

| PARAMETER                  | SYMBOL          | CONDITIONS                                            | MIN                            | TYP | MAX                            | UNITS |

|----------------------------|-----------------|-------------------------------------------------------|--------------------------------|-----|--------------------------------|-------|

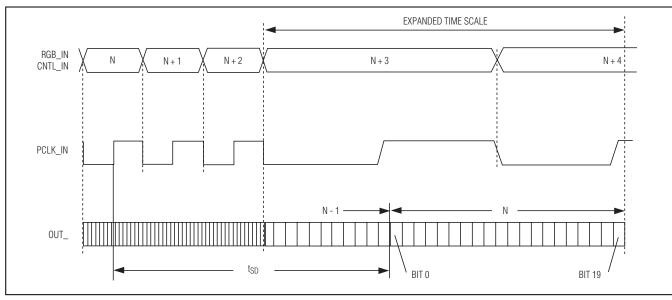

| Serializer Delay           | tsD             | Figure 5                                              | 3.10 x<br>t <sub>T</sub> + 2.0 |     | 3.10 x<br>t <sub>T</sub> + 8.0 | ns    |

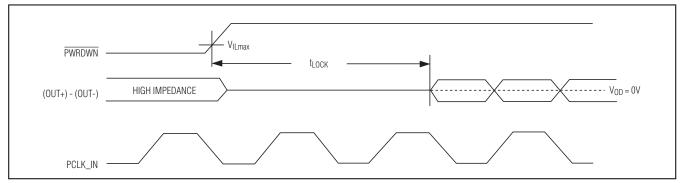

| PLL Lock Time              | tLOCK           | Figure 6                                              |                                |     | 17,100 x<br>t <sub>T</sub>     | ns    |

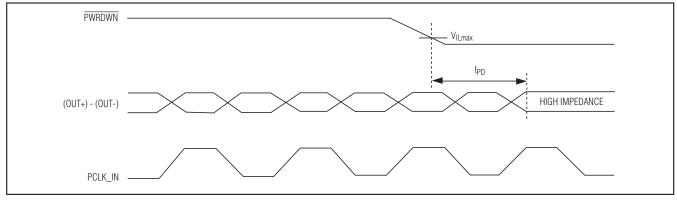

| Power-Down Delay           | t <sub>PD</sub> | Figure 7                                              |                                |     | 1                              | μs    |

| Peak-to-Peak Output Jitter | tuitt           | Measured with PRBS input pattern at 840Mbps data rate |                                |     | 150                            | ps    |

| Peak-to-Peak Output Offset | Maria           | 840Mbps data rate,<br>CMF open, Figure 8              |                                | 22  | 70                             | /     |

| Voltage                    | VOS(P-P)        | 840Mbps data rate,<br>CMF 0.1µF to ground, Figure 8   |                                | 12  | 50                             | mV    |

- Note 1: Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to ground, except Vop. ΔVop. and ΔVos.

- **Note 2:** Maximum and minimum limits over temperature are guaranteed by design and characterization. Devices are production tested at T<sub>A</sub> = +25°C.

- Note 3: Parameters are guaranteed by design and characterization and are not production tested. Limits are set at ±6 sigma.

- Note 4: All LVTTL/LVCMOS inputs, except PWRDWN at ≤ 0.3V or ≥ V<sub>CCIN</sub> 0.3V. PWRDWN is ≤ 0.3V.

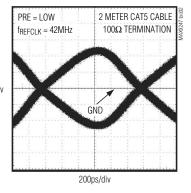

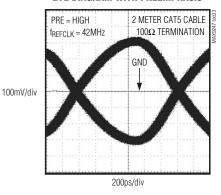

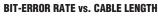

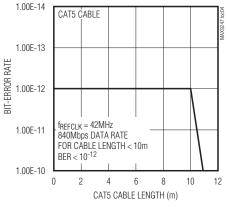

### **Typical Operating Characteristics**

$(V_{CC_{-}} = +3.3V, R_{L} = 100\Omega, T_{A} = +25^{\circ}C, unless otherwise noted.)$

#### **EYE DIAGRAM WITHOUT PREEMPHASIS**

FREQUENCY (MHz)

#### **EYE DIAGRAM WITH PREEMPHASIS**

## CABLE LENGTH vs. Frequency bit-error rate < 10<sup>-9</sup>

### **Pin Description**

| PIN            | NAME                                            | FUNCTION                                                                                                                                                                                                  |

|----------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 13, 37      | GND                                             | Input Buffer Supply and Digital Supply Ground                                                                                                                                                             |

| 2              | VCCIN                                           | Input Buffer Supply Voltage. Bypass to GND with 0.1µF and 0.001µF capacitors in parallel as close to the device as possible, with the smallest value capacitor closest to the supply pin.                 |

| 3–10,<br>39–48 | RGB_IN10-<br>RGB_IN17,<br>RGB_IN0-<br>RGB_IN9   | LVTTL/LVCMOS Red, Green, and Blue Digital Video Data Inputs. Eighteen data bits are loaded into the input latch on the rising edge of PCLK_IN when DE_IN is high. Internally pulled down to GND.          |

| 11, 12, 15–21  | CNTL_IN0,<br>CNTL_IN1,<br>CNTL_IN2-<br>CNTL_IN8 | LVTTL/LVCMOS Control Data Inputs. Control data are latched on the rising edge of PCLK_IN when DE_IN is low. Internally pulled down to GND.                                                                |

| 14, 38         | Vcc                                             | Digital Supply Voltage. Bypass to GND with 0.1µF and 0.001µF capacitors in parallel as close to the device as possible, with the smallest value capacitor closest to the supply pin.                      |

| 22             | DE_IN                                           | LVTTL/LVCMOS Data-Enable Input. Logic-high selects RGB_IN[17:0] to be latched. Logic-low selects CNTL_IN[8:0] to be latched. DE_IN must be switching for proper operation. Internally pulled down to GND. |

| 23             | PCLK_IN                                         | LVTTL/LVCMOS Parallel Clock Input. Latches data and control inputs and provides the PLL reference clock. Internally pulled down to GND.                                                                   |

| 24             | I.C.                                            | Internally Connected. Leave unconnected for normal operation.                                                                                                                                             |

| 25             | PRE                                             | Preemphasis Enable Input. Drive PRE high to enable preemphasis.                                                                                                                                           |

| 26             | PLLGND                                          | PLL Supply Ground                                                                                                                                                                                         |

| 27             | VCCPLL                                          | PLL Supply Voltage. Bypass to PLLGND with $0.1\mu F$ and $0.001\mu F$ capacitors in parallel as close to the device as possible, with the smallest value capacitor closest to the supply pin.             |

| 28             | PWRDWN                                          | LVTTL/LVCMOS Power-Down Input. Internally pulled down to GND.                                                                                                                                             |

| 29             | CMF                                             | Common-Mode Filter. Optionally connect a capacitor between CMF and LVDSGND to filter common-mode switching noise.                                                                                         |

| 30, 31         | LVDSGND                                         | LVDS Supply Ground                                                                                                                                                                                        |

| 32             | OUT-                                            | Inverting LVDS Serial-Data Output                                                                                                                                                                         |

| 33             | OUT+                                            | Noninverting LVDS Serial-Data Output                                                                                                                                                                      |

| 34             | VCCLVDS                                         | LVDS Supply Voltage. Bypass to LVDSGND with 0.1µF and 0.001µF capacitors in parallel as close to the device as possible, with the smallest value capacitor closest to the supply pin.                     |

| 35             | RNG1                                            | LVTTL/LVCMOS Frequency Range Select Input. Set to the frequency range that includes the PCLK_IN frequency as shown in Table 3. Internally pulled down to GND.                                             |

| 36             | RNG0                                            | LVTTL/LVCMOS Frequency Range Select Input. Set to the frequency range that includes the PCLK_IN frequency as shown in Table 3. Internally pulled down to GND.                                             |

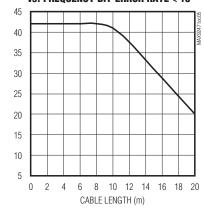

### **Functional Diagram**

Figure 1. LVDS DC Output Load and Parameters

Figure 2. Parallel Clock Requirements

Figure 3. Output Rise and Fall Times

Figure 4. Synchronous Input Timing

Figure 5. Serializer Delay

Figure 6. PLL Lock Time

Figure 7. Power-Down Delay

Figure 8. Peak-to-Peak Output Offset Voltage

#### **Detailed Description**

The MAX9247 DC-balanced serializer operates at a 2.5MHz-to-42MHz parallel clock frequency, serializing 18 bits of parallel video data RGB\_IN[17:0] when the data-enable input DE\_IN is high, or 9 bits of parallel control data CNTL\_IN[8:0] when DE\_IN is low. The RGB video input data are encoded using 2 overhead bits, EN0 and EN1, resulting in a serial word length of 20 bits (see Table 1). Control inputs are mapped to 19 bits and encoded with 1 overhead bit, EN0, also resulting in a 20-bit serial word. Encoding reduces EMI and

maintains DC balance across the serial cable. Two transition words, which contain a unique bit sequence, are inserted at the transition boundaries of video-to-control and control-to-video phases.

Control data inputs C0 to C4 are mapped to 3 bits each in the serial control word (see Table 2). At the deserializer, 2 or 3 bits at the same state determine the state of the recovered bit, providing single-bit-error tolerance for C0 to C4. Control data that may be visible if an error occurs, such as VSYNC and HSYNC, can be connected to these inputs. Control data inputs C5 to C8 are mapped to 1 bit each.

**Table 1. Serial Video Phase Word Format**

| ı | Λ   | 1   | 2  | 3  | 1  | 5  | 6  | 7  | Q  | Q  | 10 | 11  | 12  | 13  | 14  | 15  | 16  | 17  | 18  | 19  |

|---|-----|-----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| ı | U   |     | _  | 5  | 4  | )  | 0  | ,  | 0  | 9  | 10 | 1.1 | 12  | 10  | 14  | 15  | 10  | 17  | 10  | 13  |

|   | EN0 | EN1 | S0 | S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 | S9  | S10 | S11 | S12 | S13 | S14 | S15 | S16 | S17 |

Bit 0 is the LSB and is serialized first. EN[1:0] are encoding bits. S[17:0] are encoded symbols.

#### **Table 2. Serial Control Phase Word Format**

| ſ | 0   | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 |

|---|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| ſ | EN0 | C0 | C0 | C0 | C1 | C1 | C1 | C2 | C2 | C2 | СЗ | C3 | C3 | C4 | C4 | C4 | C5 | C6 | C7 | C8 |

Bit 0 is the LSB and is serialized first. C[8:0] are the control inputs.

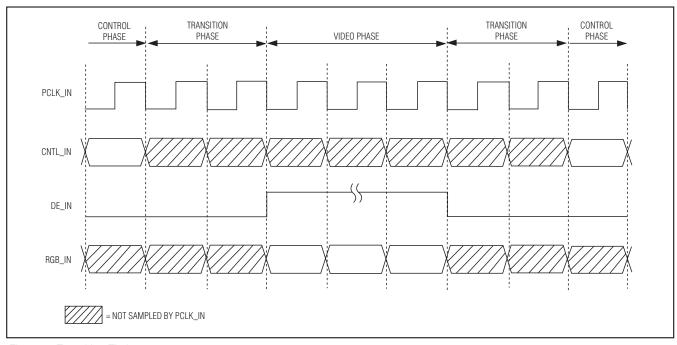

Figure 9. Transition Timing

#### **Transition Timing**

The transition words require interconnect bandwidth and displace control data. Therefore, control data is not sampled (see Figure 9):

- Two clock cycles before DE\_IN goes high

- During the video phase

- Two clock cycles after DE\_IN goes low

The last sampled control data are latched at the deserializer control data outputs during the transition and video phases. Video data are latched at the deserializer RGB data outputs during the transition and control phases.

### \_Applications Information

#### **AC-Coupling Benefits**

AC-coupling increases the common-mode voltage to the voltage rating of the capacitor. Two capacitors are sufficient for isolation, but four capacitors—two at the serializer output and two at the deserializer input—provide protection if either end of the cable is shorted to a high voltage. AC-coupling blocks low-frequency ground shifts and common-mode noise. The MAX9247 serializer can also be DC-coupled to the MAX9248/MAX9250 deserializers.

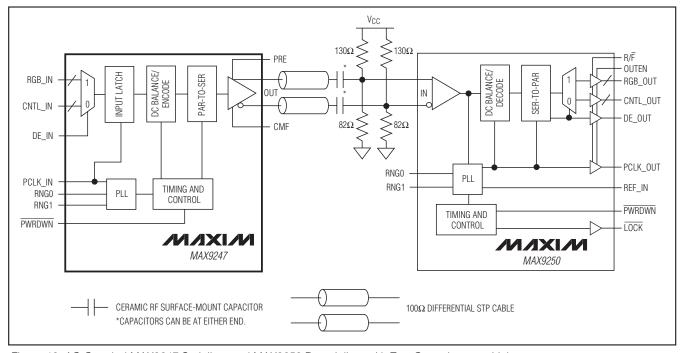

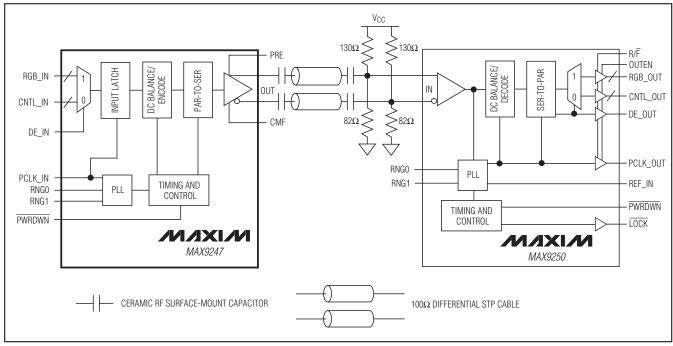

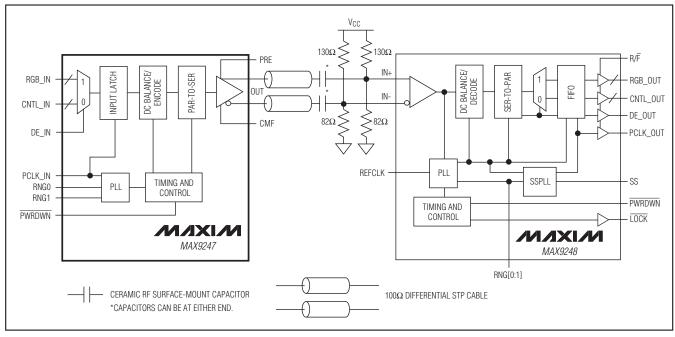

Figures 10 and 12 show an AC-coupled serializer and deserializer with two capacitors per link. Figures 11 and

13 show the AC-coupled serializer and deserializer with four capacitors per link.

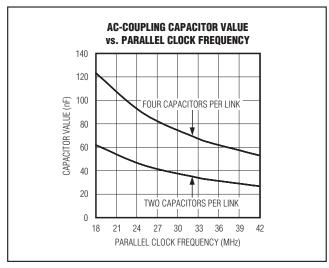

#### **Selection of AC-Coupling Capacitors**

See Figure 14 for calculating the capacitor values for AC-coupling depending on the parallel clock frequency. The plot shows capacitor values for two- and four-capacitor-per-link systems. For applications using less than 18MHz clock frequency, use 0.1µF capacitors.

#### Frequency-Range Setting RNG[1:0]

The RNG[1:0] inputs select the operating frequency range of the MAX9247 serializer. An external clock within this range is required for operation. Table 3 shows the selectable frequency ranges and corresponding data rates for the MAX9247

Table 3. Parallel Clock Frequency Range Select

| RNG1 | RNG0 | PARALLEL<br>CLOCK (MHz) | SERIAL-DATA RATE (Mbps) |

|------|------|-------------------------|-------------------------|

| 0    | 0    | 2.5 to 5                | 50 to 100               |

| 0    | 1    | 5 to 10                 | 100 to 200              |

| 1    | 0    | 10 to 20                | 200 to 400              |

| 1    | 1    | 20 to 42                | 400 to 840              |

Figure 10. AC-Coupled MAX9247 Serializer and MAX9250 Deserializer with Two Capacitors per Link

Figure 11. AC-Coupled MAX9247 Serializer and MAX9250 Deserializer with Four Capacitors per Link

Figure 12. AC-Coupled MAX9247 Serializer and MAX9248 Deserializer with Two Capacitors per Link

Figure 13. AC-Coupled MAX9247 Serializer and MAX9248 Deserializer with Four Capacitors per Link

Figure 14. AC-Coupling Capacitor Values vs. Clock Frequency of 18MHz to 42MHz

#### **Termination**

The MAX9247 has an integrated 100 $\Omega$  output-termination resistor. This resistor damps reflections from induced noise and mismatches between the transmission line impedance and termination resistors at the deserializer input. With  $\overline{\text{PWRDWN}}$  = low or with the supply off, the output termination is switched out and the LVDS output is high impedance.

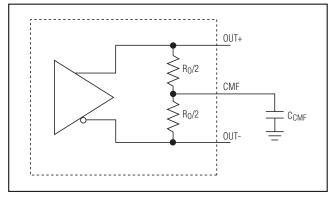

#### **Common-Mode Filter**

The integrated  $100\Omega$  output termination is made up of two  $50\Omega$  resistors in series. The junction of the resistors is connected to the CMF pin for connecting an optional common-mode filter capacitor. Connect the filter capacitor to ground close to the MAX9247 as shown in Figure 15. The capacitor shunts common-mode switching current to ground to reduce EMI.

Figure 15. Common-Mode Filter Capacitor Connection

#### LVDS Output Preemphasis (PRE)

The MAX9247 features a preemphasis mode where extra current is added to the output and causes the amplitude to increase by 40% to 50% at the transition point. Preemphasis helps to get a faster transition, better eye diagram, and improve signal integrity. See the *Typical Operating Characteristics*. The additional current is turned on for a short time (360ps, typ) during data transition, and then turned off. Enable preemphasis by driving PRE high.

#### Power-Down and Power-Off

Driving  $\overline{PWRDWN}$  low stops the PLL, switches out the integrated 100 $\Omega$  output termination, and puts the output in high impedance to ground and differential. With  $\overline{PWRDWN} \leq 0.3V$  and all LVTTL/LVCMOS inputs  $\leq 0.3V$  or  $\geq VCCIN-0.3V$ , supply current is reduced to  $50\mu A$  or less. Driving  $\overline{PWRDWN}$  high starts PLL lock to PCLK\_IN and switches in the  $100\Omega$  output termination resistor. The LVDS output is not driven until the PLL locks. The LVDS output is high impedance to ground and  $100\Omega$  differential. The  $100\Omega$  integrated termination pulls OUT+ and OUT- together while the PLL is locking so that  $V_{OD}=0V$ . If  $V_{CC}=0$ , the output resistor is switched out and the LVDS outputs are high impedance to ground and differential.

#### **PLL Lock Time**

The PLL lock time is set by an internal counter. The lock time is 17,100 PCLK\_IN cycles. Power and clock should be stable to meet the lock-time specification.

#### **Input Buffer Supply**

The single-ended inputs (RGB\_IN[17:0], CNTL\_IN[8:0], DE\_IN, RNG0, RNG1, PRE, PCLK\_IN, and PWRDWN) are powered from VCCIN. VCCIN can be connected to a 1.71V to 3.6V supply, allowing logic inputs with a nominal swing of VCCIN. If no power is applied to VCCIN when power is applied to VCC, the inputs are disabled and PWRDWN is internally driven low, putting the device in the power-down state.

## Power-Supply Sequencing of MAX9247 and MAX9248/MAX9250 Video Link

The MAX9247 and MAX9248/MAX9250 video link can be powered up in several ways. The best approach is to keep both MAX9247 and MAX9248 powered down while supplies are ramping up and PCLK\_IN of the MAX9247 and REFCLK of the MAX9248/MAX9250 are stabilizing. After all of the power supplies of the MAX9247 and MAX9248/MAX9250 are stable, including PCLK\_IN and REFCLK, do the following:

1) Power up the MAX9247 first

- Wait for at least t<sub>LOCK</sub> of MAX9247 (or 17100 x t<sub>T</sub>) to get activity on the link

- 3) Power up the MAX9248

#### **Power-Supply Circuits and Bypassing**

The MAX9247 has isolated on-chip power domains. The digital core supply (V<sub>CC</sub>) and single-ended input supply (V<sub>CCIN</sub>) are isolated but have a common ground (GND). The PLL has separate power and ground (V<sub>CCPLL</sub> and PLLGND) and the LVDS input also has separate power and ground (V<sub>CCLVDS</sub> and LVDSGND). The grounds are isolated by diode connections. Bypass each V<sub>CC</sub>, V<sub>CCIN</sub>, V<sub>CCPLL</sub>, and V<sub>CCLVDS</sub> pin with high-frequency, surface-mount ceramic  $0.1\mu\text{F}$  and  $0.001\mu\text{F}$  capacitors in parallel as close to the device as possible, with the smallest value capacitor closest to the supply pin.

#### **LVDS Output**

The LVDS output is a current source. The voltage swing is proportional to the termination resistance. The output is rated for a differential load of  $100\Omega \pm 1\%$ .

#### **Cables and Connectors**

Interconnect for LVDS typically has a differential impedance of  $100\Omega$ . Use cables and connectors that have matched differential impedance to minimize impedance discontinuities.

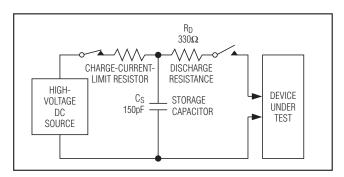

Figure 16. IEC 61000-4-2 Contact Discharge ESD Test Circuit

Figure 17. Human Body ESD Test Circuit

Twisted-pair and shielded twisted-pair cables offer superior signal quality compared to ribbon cable and tend to generate less EMI due to magnetic field canceling effects. Balanced cables pick up noise as common mode, which is rejected by the LVDS receiver.

#### **Board Layout**

Separate the LVTTL/LVCMOS inputs and LVDS output to prevent crosstalk. A four-layer PCB with separate layers for power, ground, and signals is recommended.

#### **ESD Protection**

The MAX9247 ESD tolerance is rated for IEC 61000-4-2, Human Body Model, Machine Model, and ISO 10605 standards. IEC 61000-4-2 and ISO 10605 specify ESD tolerance for electronic systems. The IEC 61000-4-2 discharge components are Cs = 150pF and Rp =  $330\Omega$  (Figure 16). For IEC 61000-4-2, the LVDS outputs are rated for ±8kV Contact Discharge and ±15kV Air-Gap Discharge. The Human Body Model discharge components are Cs = 100pF and RD =  $1.5k\Omega$  (Figure 17). For the Human Body Model, all pins are rated for ±3kV Contact Discharge. The ISO 10605 discharge components are Cs = 330pF and Rp =  $2k\Omega$  (Figure 18). For ISO 10605, the LVDS outputs are rated for ±10kV contact and ±30kV air discharge. The Machine Model discharge components are Cs = 200pF and  $R_D = 0\Omega$  (Figure 19).

Figure 18. ISO 10605 Contact Discharge ESD Test Circuit

Figure 19. Machine Model ESD Test Circuit

\_Chip Information

### \_Package Information

PROCESS: CMOS

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but

PACKAGE TYPE

PACKAGE CODE

OUTLINE NO.

LAND PATTERN NO.

48 LQFP

C48+5

21-0054

90-0093

the drawing pertains to the package regardless of RoHS status.

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                            | PAGES<br>CHANGED |

|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2                  | 5/08             | Corrected LQFP package, added +105°C part, changed temperature limits for +105°C rated part, and added Machine Model ESD text and diagram              | 1–6, 15–19       |

| 3                  | 4/09             | Added /V parts in the <i>Ordering Information</i> table and added new <i>Power-Supply Sequencing of MAX9247 and MAX9248/MAX9250 Video Link</i> section | 1, 14            |

| 4                  | 4/12             | Corrected errors in Absolute Maximum Ratings and Pin Description sections                                                                              | 2, 6             |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.