Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **Fully Programmable Serializer/Deserializer** with UART/I2C Control Channel

#### **General Description**

**Features**

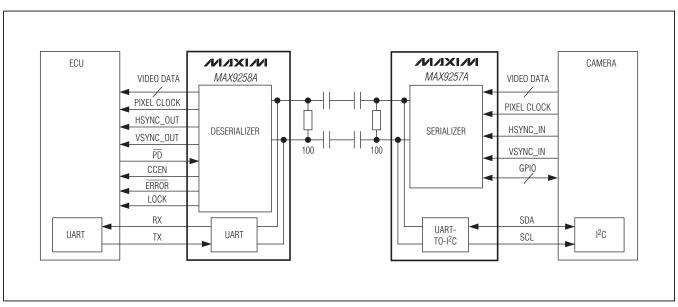

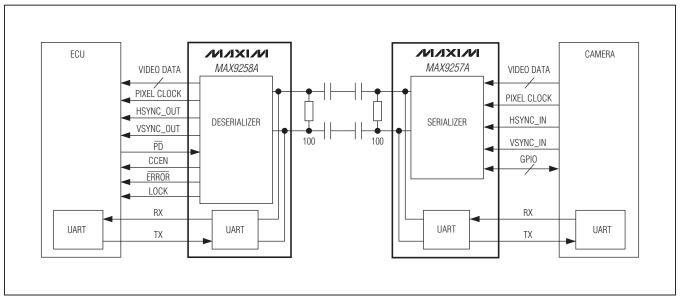

The MAX9257A serializer pairs with the MAX9258A deserializer to form a complete digital video serial link. The devices feature programmable parallel data width, parallel clock frequency range, spread spectrum, and preemphasis. An integrated control channel transfers data bidirectionally at power-up during video blanking over the same differential pair used for video data. This feature eliminates the need for external CAN or LIN interface for diagnostics or programming. The clock is recovered from input serial data at MAX9258A, hence eliminating the need for an external reference clock.

The MAX9257A serializes 10, 12, 14, 16, and 18 bits with the addition of two encoding bits for AC-coupling. The MAX9258A deserializer links with the MAX9257A to deserialize a maximum of 20 (data + encoding) bits per pixel/parallel clock period for a maximum serial-data rate of 840Mbps. The word length can be adjusted to accommodate a higher pixel/parallel clock frequency. The pixel clock can vary from 5MHz to 70MHz, depending on the serial-word length. Enabling parity adds two parity bits to the serial word. The encoding bits reduce ISI and allow AC-coupling.

The MAX9258A receives programming instructions from the electronic control unit (ECU) during the control channel and transmits to the MAX9257A over the serial video link. The instructions can program or update the MAX9257A, MAX9258A, or an external peripheral device, such as a camera. The MAX9257A communicates with the peripheral device with I2C or UART.

The devices operate from a +3.3V core supply and feature separate supplies for interfacing to +1.8V to +3.3V logic levels. These devices are available in 40-lead TQFN or 48-pin LQFP packages. These devices are specified over the -40°C to +105°C temperature range.

#### **Applications**

**Automotive Cameras** Industrial Cameras Navigation Systems Display In-Vehicle Entertainment Systems

- ♦ 10/12/14/16/18-Bit Programmable Parallel Data Width

- **♦ MAX9258A Does Not Require Reference Clock**

- **♦ Parity Protection for Video and Control Channels**

- **♦ Programmable Spread Spectrum**

- ◆ Programmable Rising or Falling Edge for HSYNC, **VSYNC**, and Clock

- ♦ Up to 10 Remotely Programmable GPIO on **MAX9257A**

- ♦ Automatic Resynchronization in Case of Loss of

- ♦ MAX9257A Parallel Clock Jitter Filter PLL with **Bypass**

- ♦ DC-Balanced Coding Allows AC-Coupling

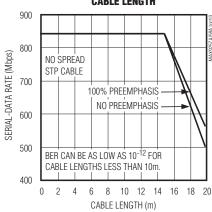

- ♦ Levels of Preemphasis for Up to 20m STP Cable **Drive**

- ♦ Integrity Test Using On-Chip Programmable PRBS **Generator and Checker**

- ♦ LVDS I/O Meet ISO 10605 ESD Protection (±10kV) Contact and ±30kV Air Discharge)

- ♦ LVDS I/O Meet IEC 61000-4-2 ESD Protection (±8kV Contact and ±20kV Air Discharge)

- ♦ LVDS I/O Meet ±200V Machine Model ESD **Protection**

- **♦** -40°C to +105°C Operating Temperature Range

- ♦ Space-Saving, 40-Pin TQFN (5mm x 5mm) with **Exposed Pad or 48-Pin LQFP Packages**

- ♦ 3.3V Core Supply and 1.8V to 3.3V I/O Supply

Ordering Information appears at end of data sheet.

Typical Operating Circuit and Pin Configurations appear at end of data sheet.

For related parts and recommended products to use with this part, refer to www.maxim-ic.com/MAX9257A.related.

## **Fully Programmable Serializer/Deserializer** with UART/I2C Control Channel

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND                                  | 0.5V to +4.0V                      | IEC 61000-4-2 (RD = $330\Omega$ , CS = $150pF$ ) |                |

|---------------------------------------------------------|------------------------------------|--------------------------------------------------|----------------|

| Any Ground to Any Ground                                | 0.5V to +0.5V                      | Contact Discharge                                |                |

| SDI+, SDI-, SDO+, SDO- to GND                           | 0.5V to +4.0V                      | (SDI+, SDI-, SDO+, SDO-) to GND                  | ±8kV           |

| SDO+, SDO- Short Circuit to GND or VCI                  | CLVDSContinuous                    | Air Discharge                                    |                |

| DIN[0:15], GPIO[0:9], PCLK_IN, HSYNC                    | _IN, VSYNC_IN,                     | (SDI+, SDI-, SDO+, SDO-) to GND                  | ±20kV          |

| SCL/TX, SDA/RX, REM to GND                              | 0.5V to (V <sub>CCIO</sub> + 0.5V) | ISO 10605 (RD = $2k\Omega$ , CS = 330pF)         |                |

| DOUT[0:15], PCLK_OUT, CCEN, HSYNC                       | C_OUT,                             | Contact Discharge                                |                |

| $VSYNC\_OUT$ , $RX$ , $LOCK$ , $TX$ , $\overline{PD}$ , |                                    | (SDI+, SDI-, SDO+, SDO-) to GND                  | ±10kV          |

| ERROR to GND0.5                                         | 5V to (V <sub>CCOUT</sub> + 0.5V)  | Air Discharge                                    |                |

| Continuous Power Dissipation (TA = +70                  | 0°C)                               | (SDI+, SDI-, SDO+, SDO-) to GND                  | ±30kV          |

| 40-Lead TQFN                                            |                                    | Machine Model (RD = $0\Omega$ , CS = $200pF$ )   |                |

| Multilayer PCB (derate 35.7mW/°C abo                    | ove +70°C)2857mW                   | All Pins to GND                                  | ±200V          |

| 48-Lead LQFP                                            |                                    | Storage Temperature Range                        | 65°C to +150°C |

| Multilayer PCB (derate 21.7mW/°C abo                    | ove +70°C)1739mW                   | Junction Temperature                             | +150°C         |

| ESD Protection                                          |                                    | Lead Temperature (soldering, 10s)                | +300°C         |

| Human Body Model (RD = $1.5k\Omega$ , CS                | = 100pF)                           | Soldering Temperature (reflow)                   | +260°C         |

| All Pins to GND                                         | ±3kV                               |                                                  |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### PACKAGE THERMAL CHARACTERISTICS (Note 1)

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) |        | Junction-to-Case Thermal F | lesistance ( $\theta_{JC}$ ) |

|----------------------------------------------------------|--------|----------------------------|------------------------------|

| 40-Pin TQFN                                              | 28°C/W | 40-Pin TQFN                | 1.7°C/W                      |

| 48-Pin LQFP                                              | 46°C/W | 48-Pin LQFP                | 10°C/W                       |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to www.maxim-ic.com/thermal-tutorial.

#### MAX9257A DC ELECTRICAL CHARACTERISTICS

$(V_{CC}=+3.0V\ to\ +3.6V,\ V_{CCIO}=+1.71V\ to\ +3.6V,\ R_L=50\Omega\pm1\%,\ T_A=-40^{\circ}C\ to\ +105^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $V_{CC} = +3.3V$ ,  $T_A = +25^{\circ}C$ .) (Notes 2, 3)

| PARAMETER                | SYMBOL          | CONDITIONS                          | MIN                         | TYP | MAX                        | UNITS |

|--------------------------|-----------------|-------------------------------------|-----------------------------|-----|----------------------------|-------|

| SINGLE-ENDED INPUTS      |                 |                                     |                             |     |                            |       |

| High-Level Input Voltage |                 | $V_{CCIO} = +1.71V \text{ to } +3V$ | 0.65 x<br>V <sub>CCIO</sub> |     | V <sub>CCIO</sub> + 0.3    |       |

|                          | VIH             | $V_{CCIO} = +3V \text{ to } +3.6V$  | 2                           |     | V <sub>CCIO</sub> + 0.3    | V     |

|                          |                 | REM input                           | 2                           |     | V <sub>CC</sub> + 0.3      |       |

|                          |                 | V <sub>CCIO</sub> = +1.71V to +3V   | 0                           |     | 0.3 x<br>V <sub>CCIO</sub> | .,    |

| Low-Level Input Voltage  | V <sub>IL</sub> | $V_{CCIO} = +3V \text{ to } +3.6V$  | 0                           |     | 0.8                        | V     |

|                          |                 | REM input                           | 0                           |     | 0.8                        | ]     |

# **Fully Programmable Serializer/Deserializer** with UART/I2C Control Channel

#### **MAX9257A DC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC\_} = +3.0V \text{ to } +3.6V, V_{CCIO} = +1.71V \text{ to } +3.6V, R_L = 50\Omega \pm 1\%, T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{CC\_} = +3.3V, T_A = +25^{\circ}\text{C.}) \text{ (Notes 2, 3)}$

| PARAMETER                                                        | SYMBOL                | cc                                       | ONDITIONS                           | MIN                        | TYP  | MAX                        | UNITS |

|------------------------------------------------------------------|-----------------------|------------------------------------------|-------------------------------------|----------------------------|------|----------------------------|-------|

| la act of Octobra and                                            | 1                     | $V_{IN} = 0$ to $V_{CCIO}$               |                                     | -20                        |      | +20                        |       |

| Input Current                                                    | I <sub>IN</sub>       | $V_{IN} = 0$ to $V_{CC}$ , R             | EM input                            | -20                        |      | +20                        | μA    |

| Input Clamp Voltage                                              | V <sub>CL</sub>       | I <sub>CL</sub> = -18mA                  |                                     |                            |      | -1.5                       | V     |

| SINGLE-ENDED OUTPUTS                                             |                       |                                          |                                     |                            |      |                            |       |

|                                                                  | .,                    | I <sub>OH</sub> = -100μA                 |                                     | V <sub>CCIO</sub> - 0.1    |      |                            | V     |

| High-Level Output Voltage                                        | V <sub>OH</sub>       | I <sub>OH</sub> = -2mA                   |                                     | V <sub>CCIO</sub> - 0.35   |      |                            | V     |

|                                                                  | .,                    | I <sub>OL</sub> = 100μA                  |                                     |                            |      | 0.1                        | .,    |

| Low-Level Output Voltage                                         | V <sub>OL</sub>       | $I_{OL} = 2mA$                           |                                     |                            |      | 0.3                        | V     |

|                                                                  |                       | Classita el tal CND                      | $V_{CCIO} = +1.71V \text{ to } +3V$ | -40                        |      | -4                         |       |

| Output Chart Circuit Current                                     |                       | Shorted to GND                           | $V_{CCIO} = +3V \text{ to } +3.6V$  | -50                        |      | -10                        | A     |

| Output Short-Circuit Current                                     | I <sub>OS</sub>       | Chartad to V                             | $V_{CCIO} = +1.71V \text{ to } +3V$ | 4                          |      | 40                         | mA mA |

|                                                                  |                       | Shorted to V <sub>CCIO</sub>             | $V_{CCIO} = +3V \text{ to } +3.6V$  | 10                         |      | 50                         |       |

| I <sup>2</sup> C/UART I/O                                        |                       |                                          |                                     |                            |      |                            |       |

| Input Leakage Current                                            | I <sub>ILKG</sub>     | $V_I = V_{CCIO}$                         |                                     | -1                         |      | +1                         | μΑ    |

| High-Level Input Voltage SDA/RX                                  | V <sub>IH2</sub>      |                                          |                                     | 0.7 x<br>V <sub>CCIO</sub> |      |                            | V     |

| Low-Level Input Voltage SDA/RX                                   | V <sub>IL2</sub>      |                                          |                                     |                            |      | 0.3 x<br>V <sub>CCIO</sub> | V     |

| Low-Level Output Voltage<br>SCL, SDA                             | V <sub>OL2</sub>      | R <sub>PULLUP</sub> = 1.6kΩ              | to V <sub>CCIO</sub>                |                            |      | 0.4                        | V     |

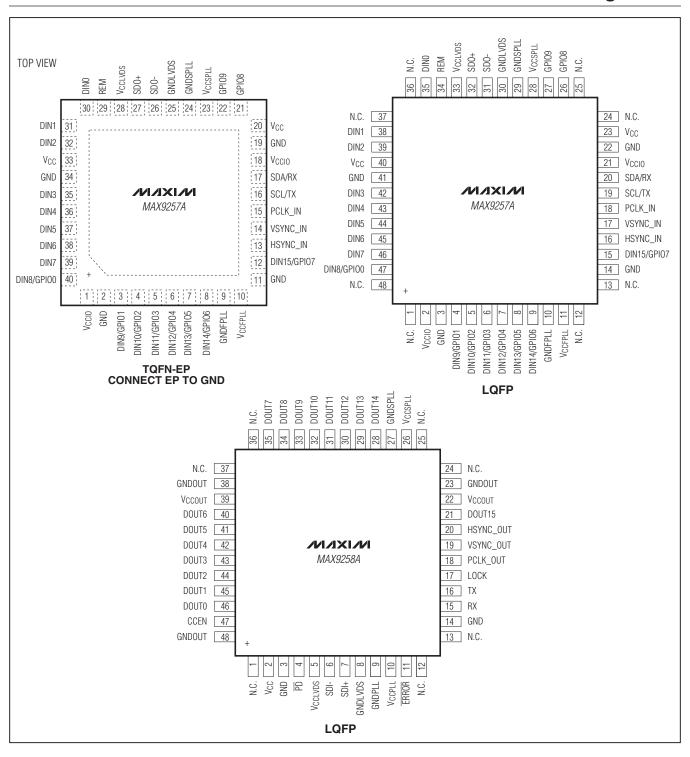

| LVDS OUTPUTS (SDO+, SDO-)                                        |                       | 1                                        |                                     |                            |      |                            |       |

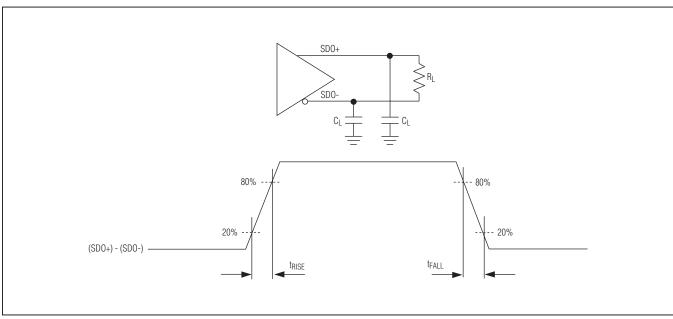

| Differential Output Voltage                                      | V <sub>OD</sub>       |                                          |                                     | 250                        | 350  | 460                        | mV    |

| Change in VOD Between<br>Complementary Output States             | $\Delta V_{	ext{OD}}$ | Preemphasis off                          |                                     |                            |      | 25                         | mV    |

| Common-Mode Voltage                                              | V <sub>OS</sub>       | (Figure 1)                               |                                     | 1.050                      | 1.25 | 1.375                      | V     |

| Change in V <sub>OS</sub> Between<br>Complementary Output States | ΔV <sub>OS</sub>      |                                          |                                     |                            |      | 30                         | mV    |

| Output Short-Circuit Current                                     | los                   | V <sub>SDO+</sub> or V <sub>SDO-</sub> = | = 0 or 3.6V                         | -15                        |      | +15                        | mA    |

| Magnitude of Differential Output<br>Short-Circuit Current        | I <sub>OSD</sub>      | V <sub>OD</sub> = 0V                     |                                     |                            |      | 15                         | mA    |

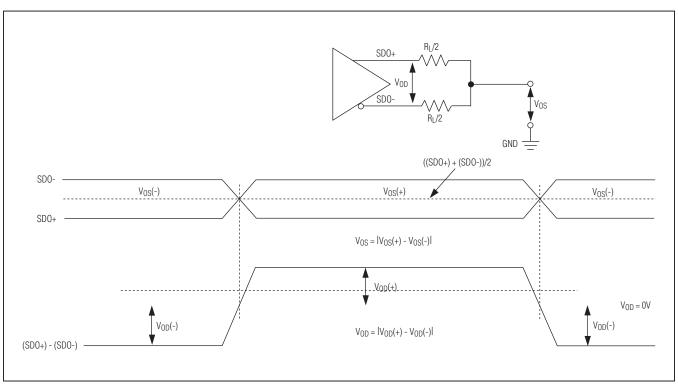

| CONTROL CHANNEL TRANSCE                                          | VER                   |                                          |                                     |                            |      |                            |       |

| Differential Output Voltage                                      | V <sub>OD</sub>       |                                          |                                     | 250                        | 350  | 460                        | mV    |

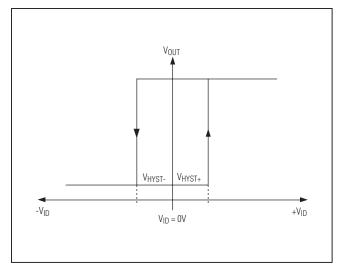

| Input Hysteresis                                                 | VHYST+                | Differential low-to-                     | high threshold                      | 25                         | 90   | 165                        | m\/   |

| (Figure 2)                                                       | V <sub>HYST</sub> -   | Differential high-to                     | o-low threshold                     | -25                        | -90  | -165                       | - mV  |

# **Fully Programmable Serializer/Deserializer** with UART/I2C Control Channel

#### **MAX9257A DC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC\_} = +3.0V \text{ to } +3.6V, V_{CCIO} = +1.71V \text{ to } +3.6V, R_L = 50\Omega \pm 1\%, T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{CC\_} = +3.3V, T_A = +25^{\circ}\text{C.}) \text{ (Notes 2, 3)}$

| PARAMETER                                                          | SYMBOL | CONDITIONS                                                          | MIN | TYP | MAX | UNITS |

|--------------------------------------------------------------------|--------|---------------------------------------------------------------------|-----|-----|-----|-------|

| POWER SUPPLY                                                       |        |                                                                     |     |     |     |       |

|                                                                    |        | ±2% spread, preemphasis off,<br>PRATE = 60MHz, SRATE = 840Mbps      |     | 102 | 138 |       |

|                                                                    |        | No spread, preemphasis off,<br>PRATE = 60MHz, SRATE = 840Mbps       |     | 101 | 130 |       |

|                                                                    |        | No spread, preemphasis = 20%,<br>PRATE = 60MHz, SRATE = 840Mbps     |     | 102 | 135 |       |

|                                                                    |        | No spread, preemphasis = 60%,<br>PRATE = 60MHz, SRATE = 840Mbps     |     | 111 | 137 |       |

|                                                                    |        | No spread, preemphasis = 100%,<br>PRATE = 60MHz, SRATE = 840Mbps    |     | 113 | 139 |       |

|                                                                    |        | ±2% spread, preemphasis off,<br>PRATE = 28.57MHz, SRATE = 400Mbps   |     | 80  | 104 |       |

|                                                                    |        | No spread, preemphasis off,<br>PRATE = 28.57MHz, SRATE = 400Mbps    |     | 79  | 100 |       |

|                                                                    |        | No spread, preemphasis = 100%,<br>PRATE = 28.57MHz, SRATE = 400Mbps |     | 88  | 111 |       |

| Worst-Case Supply Current (Figure 3) C <sub>L</sub> = 8pF, 12 bits | Iccw   | ±2% spread, preemphasis off,<br>PRATE = 14.29MHz, SRATE = 200Mbps   |     | 56  | 74  | mA    |

| 3 <u>.</u> 4pr, 12 and                                             |        | No spread, preemphasis off,<br>PRATE = 14.29MHz, SRATE = 200Mbps    |     | 55  | 72  |       |

|                                                                    |        | No spread, preemphasis = 100%,<br>PRATE = 14.29MHz, SRATE = 200Mbps |     | 61  | 78  |       |

|                                                                    |        | ±2% spread, preemphasis off,<br>PRATE = 7.14MHz, SRATE = 100Mbps    |     | 45  | 59  |       |

|                                                                    |        | No spread, preemphasis off,<br>PRATE = 7.14MHz, SRATE = 100Mbps     |     | 44  | 57  |       |

|                                                                    |        | No spread, preemphasis = 100%,<br>PRATE = 7.14MHz, SRATE = 100Mbps  |     | 47  | 61  |       |

|                                                                    |        | ±2% spread, preemphasis off,<br>PRATE = 5MHz, SRATE = 70Mbps        |     | 34  | 45  |       |

|                                                                    |        | No spread, preemphasis off,<br>PRATE = 5MHz, SRATE = 70Mbps         |     | 34  | 44  |       |

|                                                                    |        | No spread, preemphasis = 100%,<br>PRATE = 5MHz, SRATE = 70Mbps      |     | 36  | 47  |       |

| Sleep Mode Supply Current                                          | Iccs   | Sleep mode                                                          |     |     | 92  | μΑ    |

# **Fully Programmable Serializer/Deserializer** with UART/I2C Control Channel

#### **MAX9257A AC ELECTRICAL CHARACTERISTICS**

$(V_{CC\_} = +3.0V \text{ to } +3.6V, V_{CCIO} = +1.71V \text{ to } +3.6V, R_L = 50\Omega \pm 1\%, T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{CC\_} = +3.3V, T_A = +25^{\circ}\text{C.}) \text{ (Notes 5, 9)}$

| PARAMETER                           | SYMBOL                              | CONDI                                                                 | TIONS                       | MIN   | TYP  | MAX                              | UNITS       |

|-------------------------------------|-------------------------------------|-----------------------------------------------------------------------|-----------------------------|-------|------|----------------------------------|-------------|

| PCLK_IN TIMING REQUIREMENT          | rs                                  |                                                                       |                             |       |      |                                  |             |

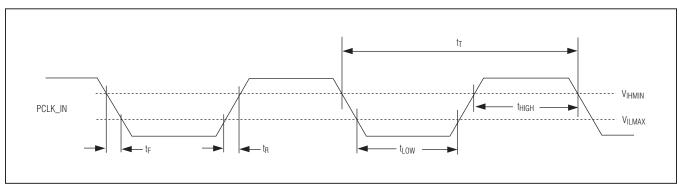

| Clock Period                        | t <sub>T</sub>                      |                                                                       |                             | 14.28 |      | 200.00                           | ns          |

| Clock Frequency                     | f <sub>CLK</sub>                    | 1/t <sub>T</sub>                                                      |                             | 5     |      | 70                               | MHz         |

| Clock Duty Cycle                    | DC                                  | t <sub>HIGH</sub> /t <sub>T</sub> or t <sub>LOW</sub> /t <sub>T</sub> |                             | 35    | 50   | 65                               | %           |

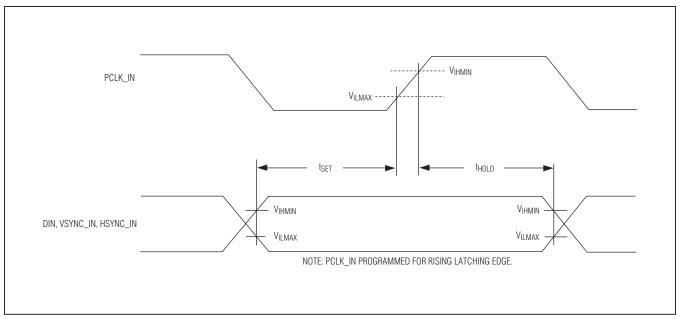

| Clock Transition Time               | t <sub>R</sub> , t <sub>F</sub>     | (Figure 7)                                                            |                             |       |      | 4                                | ns          |

| SWITCHING CHARACTERISTICS           | <b>,</b>                            |                                                                       |                             |       |      |                                  |             |

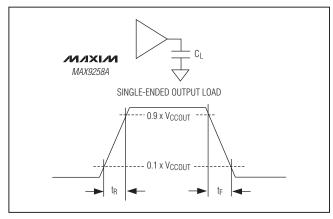

| LVDS Output Rise Time               | t <sub>R</sub>                      | 20% to 80% (Figure 4)                                                 |                             |       | 315  | 370                              | ps          |

| LVDS Output Fall Time               | t <sub>F</sub>                      | 20% to 80% (Figure 4)                                                 |                             |       | 315  | 370                              | ps          |

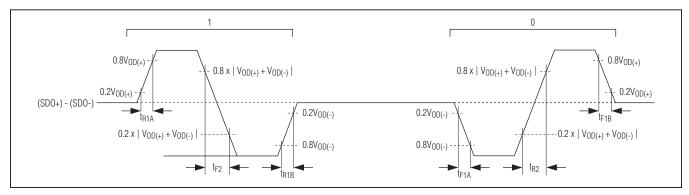

|                                     | t <sub>R1A</sub> , t <sub>F1A</sub> |                                                                       |                             | 642   | 970  | 1390                             |             |

| Control Transceiver Transition Time | t <sub>R2</sub> , t <sub>F2</sub>   | 20% to 80% (Figure 16                                                 | 6)                          | 810   | 1140 | 1420                             | ps          |

| Time                                | t <sub>R1B</sub> , t <sub>F1B</sub> |                                                                       |                             | 290   | 386  | 490                              |             |

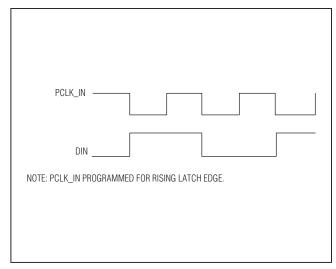

| Input Setup Time                    | t <sub>S</sub>                      | (Figure 5)                                                            |                             | 0     |      |                                  | ns          |

| Input Hold Time                     | t <sub>H</sub>                      | (Figure 5)                                                            | 3                           |       |      | ns                               |             |

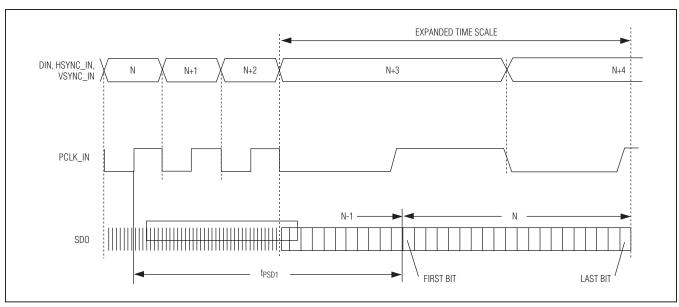

|                                     | t <sub>PSD1</sub>                   | Spread off (Figure 6)                                                 |                             |       | (4   | 4.55 x t <sub>T)</sub><br>+ 11   |             |

| Parallel-to-Serial Delay            | t <sub>PSD2</sub>                   | ±4% spread                                                            |                             |       | (3   | (36.55 x t <sub>T)</sub><br>+ 11 |             |

| PLL Lock Time                       | t <sub>LOCK</sub>                   | Combined FPLL and SPLL; PCLK_IN stable                                |                             |       |      | 32,768<br>x t <sub>T</sub>       | ns          |

| Random Jitter                       | t <sub>RJ</sub>                     | 420MHz LVDS output,<br>FPLL = bypassed                                | spread off,                 |       |      | 12                               | ps<br>(RMS) |

| Deterministic Jitter                | t <sub>DJ</sub>                     | 2 <sup>18</sup> - 1 PRBS, SRATE :<br>no spread                        | = 840Mbps, 18 bits,         |       |      | 142                              | ps (P-P)    |

| SCL/TX, SDA/RX                      |                                     |                                                                       |                             |       |      |                                  |             |

| Rise Time                           | +                                   | 0.3 x V <sub>CCIO</sub> to 0.7 x                                      | $R_{PULLUP} = 10k\Omega$    |       |      | 400                              | 20          |

| Alse Time                           | t <sub>RS</sub>                     | $V_{CCIO}$ , $C_L = 30pF$                                             | $R_{PULLUP} = 1.6k\Omega$   |       |      | 60                               | ns          |

| Fall Time                           | t <sub>FS</sub>                     | 0.7 x V <sub>CCIO</sub> to 0.3 x V <sub>0</sub>                       | CCIO, C <sub>L</sub> = 30pF |       |      | 40                               | ns          |

|                                     |                                     | 95kbps to 400kbps                                                     |                             | 100   |      |                                  |             |

| Pulse Width of Spike Suppressed     |                                     | 400kbps to 1000kbps                                                   |                             | 50    |      |                                  | 20          |

| in SDA                              | t <sub>SPK</sub>                    | 1000kbps to 4250kbps                                                  | 6                           | 10    |      |                                  | ns          |

|                                     |                                     | DC to 10Mbps (bypass mode)                                            |                             | 10    |      |                                  |             |

| D. C. C. T.                         |                                     | 400kbps                                                               |                             | 100   |      |                                  |             |

| Data Setup Time                     | t <sub>SETUP</sub>                  | 4.25Mbps, C <sub>L</sub> = 10pF                                       |                             | 60    |      |                                  | ns          |

| D. I. II. II. T                     | 4                                   | 400kbps                                                               |                             | 100   |      |                                  |             |

| Data Hold Time                      | t <sub>HOLD</sub>                   | 4.25Mbps, C <sub>L</sub> = 10pF                                       |                             | 0     |      |                                  | ns          |

## **Fully Programmable Serializer/Deserializer** with UART/I2C Control Channel

#### MAX9257A AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, V_{CCIO} = +1.71 \text{V to } +3.6 \text{V}, R_L = 50 \Omega \pm 1\%, T_A = -40 ^{\circ}\text{C}$  to  $+105 ^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_{CC}^- = +3.3V$ ,  $T_A = +25^{\circ}C$ .) (Notes 5, 9)

| PARAMETER                              | SYMBOL              | CONDITIONS  | MIN | TYP  | MAX | UNITS |

|----------------------------------------|---------------------|-------------|-----|------|-----|-------|

| I <sup>2</sup> C TIMING (Note 8)       |                     |             |     |      |     |       |

| Maximum SCL Clock Frequency            | f <sub>SCL</sub>    |             |     | 4.25 |     | MHz   |

| Minimum SCL Clock Frequency            | f <sub>SCL</sub>    |             |     | 95   |     | kHz   |

| Start Condition Hold Time              | t <sub>HD:STA</sub> | (Figure 30) | 0.6 |      |     | μs    |

| Low Period of SCL Clock                | t <sub>LOW</sub>    | (Figure 30) | 1.1 |      |     | μs    |

| High Period of SCL Clock               | tHIGH               | (Figure 30) | 0.6 |      |     | μs    |

| Repeated START Condition<br>Setup Time | <sup>t</sup> SU:STA | (Figure 30) | 0.5 |      |     | μs    |

| Data Hold Time                         | thd:dat             | (Figure 30) | 0   |      | 0.9 | μs    |

| Data Setup Time                        | tsu:dat             | (Figure 30) | 100 |      |     | ns    |

| Setup Time for STOP Condition          | t <sub>SU:STO</sub> | (Figure 30) | 0.5 |      |     | μs    |

| Bus Free Time                          | t <sub>BUF</sub>    | (Figure 30) | 1.1 |      |     | μs    |

#### MAX9258A DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, V_{CCIO} = +1.71 \text{V to } +3.6 \text{V}, R_L = 50 \Omega \pm 1 \%$ , differential input voltage  $|V_{ID}| = 0.05 \text{V to } 1.2 \text{V}$ , input commonmode voltage  $V_{CM} = IV_{ID}/2I$  to  $V_{CC} - IV_{ID}/2I$ ,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{CC} = +3.3V$ ,  $IV_{ID}I$ = 0.2V,  $V_{CM}$  = 1.2V,  $T_A$  = +25°C) (Notes 2, 3)

| PARAMETER                | SYMBOL          | CONDITIONS                           |      | MIN                          | TYP N | IAX         | UNITS |  |

|--------------------------|-----------------|--------------------------------------|------|------------------------------|-------|-------------|-------|--|

| SINGLE-ENDED INPUTS      |                 |                                      |      |                              |       |             |       |  |

| High-Level Input Voltage | V               | $V_{CCOUT} = +1.71V \text{ to } +3V$ |      | 0.65 x<br>V <sub>CCOUT</sub> |       | OUT<br>0.3  | V     |  |

|                          | V <sub>IH</sub> | $V_{CCOUT} = +3V \text{ to } +3.6V$  |      | 2.0                          |       | OUT<br>0.3  | V     |  |

| Low-Level Input Voltage  | V <sub>IL</sub> | $V_{CCOUT} = +1.71V \text{ to } +3V$ |      | 0                            |       | 3 x<br>COUT | V     |  |

|                          |                 | $V_{CCOUT} = +3V \text{ to } +3.6V$  |      | 0                            | (     | 0.8         |       |  |

| Input Current            | 1               | \/                                   | TXIN | -60                          | +     | -60         |       |  |

| Input Current            | I <sub>IN</sub> | $V_{IN} = 0$ to $V_{CCOUT}$          | PD   | -20                          | +     | -20         | - μΑ  |  |

| Input Clamp Voltage      | V <sub>CL</sub> | I <sub>CL</sub> = -18mA              |      |                              | -     | 1.5         | V     |  |

## **Fully Programmable Serializer/Deserializer** with UART/I2C Control Channel

### MAX9258A DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC\_} = +3.0 \text{V to } +3.6 \text{V}, V_{CC|O} = +1.71 \text{V to } +3.6 \text{V}, R_L = 50 \Omega \pm 1\%, \text{ differential input voltage } |V_{|D}| = 0.05 \text{V to } 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_} = |V_{|D}/2|, T_A = -40 ^{\circ} \text{C to } +105 ^{\circ} \text{C}, \text{ unless otherwise noted.} |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2 \text{V}, \text{ input common-mode voltage } |V_{CC\_}| = 1.2$ = 0.2V,  $V_{CM}$  = 1.2V,  $T_A$  = +25°C) (Notes 2, 3)

| PARAMETER                         | SYMBOL                                |                                       | CONDITIONS                             | MIN                         | TYP | MAX   | UNITS |

|-----------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|-----------------------------|-----|-------|-------|

| SINGLE-ENDED OUTPUTS              |                                       |                                       |                                        |                             |     |       |       |

| High-Level Output Voltage         |                                       | I <sub>OH</sub> = -100μ               | I <sub>OH</sub> = -100μA               |                             |     |       | V     |

| nigh-Level Output voltage         | V <sub>OH</sub>                       | $I_{OH} = -2mA$                       |                                        | V <sub>CCOUT</sub><br>-0.35 |     |       | V     |

| Low Lovel Output Valtage          | \/                                    | I <sub>OL</sub> = 100µA               | 4                                      |                             |     | 0.1   | V     |

| Low-Level Output Voltage          | V <sub>OL</sub>                       | I <sub>OL</sub> = 2mA                 |                                        |                             |     | 0.3   | V     |

| High-Impedance Output Current     | I <sub>OZ</sub>                       | $\overline{PD} = low, V$              | $_{O}$ = 0 to $V_{CCOUT}$              | -1                          |     | +1    | μΑ    |

|                                   |                                       | $V_O = 0V$                            | $V_{CCOUT} = +1.71V \text{ to } +3V$   | -4                          |     | -44   |       |

| Outside Chart Circuit Comment     | los                                   | (Note 4)                              | $V_{CCOUT} = +3V \text{ to } +3.6V$    | -16                         |     | -65   |       |

| Output Short-Circuit Current      |                                       | PCLK_OUT,                             | $V_{CCOUT} = +1.71V \text{ to } +3.6V$ | -5                          |     | -55.1 | mA    |

|                                   |                                       | $V_O = 0V$                            | $V_{CCOUT} = +3V \text{ to } +3.6V$    | -22                         |     | -80   |       |

| OPEN-DRAIN OUTPUTS                |                                       |                                       |                                        | •                           |     |       |       |

| Output Law Valtage                | 1 Val E                               | $V_{CCOUT} = +3V$ , $I_{OL} = 6.4$ mA |                                        |                             |     | 0.55  | V     |

| Output Low Voltage                |                                       | $V_{CCOUT} = +1.71V, I_{OL} = 1.95mA$ |                                        |                             |     | 0.3   | V     |

| Leakage Current                   | I <sub>LEAK</sub>                     | $V_O = 0V \text{ or } V$              | √ccout                                 |                             |     | 1     | μΑ    |

| LVDS INPUTS (SDI+, SDI-)          |                                       |                                       |                                        |                             |     |       |       |

| Differential Input High Threshold | V <sub>TH</sub>                       |                                       |                                        |                             |     | 50    | mV    |

| Differential Input Low Threshold  | V <sub>TL</sub>                       |                                       |                                        | -50                         |     |       | mV    |

| Input Current                     | I <sub>IN+</sub> , I <sub>IN-</sub>   |                                       |                                        | -60                         |     | +60   | μΑ    |

| Power-Off Input Current           | I <sub>INO+</sub> , I <sub>INO-</sub> | $V_{CC} = 0$ or                       | open                                   | -70                         |     | +70   | μΑ    |

|                                   |                                       | ACTOFFSE                              | T = 00                                 |                             | 23  |       |       |

| A 11 11 D 1 1 1 1 0 1 1           | .,                                    | ACTOFFSE                              | ET = 01                                |                             | 11  |       |       |

| Activity-Detector Input Offset    | V <sub>OFFSET</sub>                   | ACTOFFSE                              | ET = 10                                |                             | 59  |       | mV    |

|                                   |                                       | ACTOFFSET = 11                        |                                        |                             | 75  |       |       |

| CONTROL CHANNEL TRANSCE           | IVER                                  |                                       |                                        |                             |     |       |       |

| Differential Output Voltage       | V <sub>OD</sub>                       |                                       |                                        | 250                         |     | 460   | mV    |

| Input Hysteresis                  | V <sub>HYST+</sub>                    | Differential I                        | ow-to-high threshold                   | 25                          | 90  | 165   | \/    |

| (Figure 2)                        | V <sub>HYST</sub> -                   | Differential h                        | nigh-to-low threshold                  | -25                         | -90 | -165  | mV    |

## **Fully Programmable Serializer/Deserializer** with UART/I2C Control Channel

#### MAX9258A DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC_{-}} = +3.0 \text{V to } +3.6 \text{V}, V_{CCIO} = +1.71 \text{V to } +3.6 \text{V}, R_{L} = 50 \Omega \pm 1 \%$ , differential input voltage  $|V_{ID}| = 0.05 \text{V to } 1.2 \text{V}$ , input commonmode voltage  $V_{CM} = IV_{ID}/2I$  to  $V_{CC} - IV_{ID}/2I$ ,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{CC} = +3.3V$ ,  $IV_{ID}I$ = 0.2V,  $V_{CM}$  = 1.2V,  $T_A$  = +25°C) (Notes 2, 3)

| PARAMETER                                   | SYMBOL           | CONDITIONS                                       | MIN | TYP | MAX   | UNITS |

|---------------------------------------------|------------------|--------------------------------------------------|-----|-----|-------|-------|

| POWER SUPPLY                                | ,                |                                                  |     |     |       |       |

| Worst-Case Supply Current                   |                  | ±4% spread, PRATE = 60MHz,<br>SRATE = 840Mbps    |     | 95  | 135   |       |

|                                             |                  | Spread off, PRATE = 60MHz,<br>SRATE = 840Mbps    |     | 80  | 120   |       |

|                                             |                  | ±4% spread, PRATE = 28.57MHz,<br>SRATE = 400Mbps |     | 67  | 102   |       |

|                                             |                  | Spread off, PRATE = 28.57MHz,<br>SRATE = 400Mbps |     | 57  | 84 mA |       |

| C <sub>L</sub> = 8pF, 12 bits<br>(Figure 8) | ICCW             | ±4% spread, PRATE = 14.29MHz,<br>SRATE = 200Mbps |     | 55  | 82    | mA    |

|                                             |                  | Spread off, PRATE = 14.29MHz,<br>SRATE = 200Mbps |     | 46  | 67    |       |

|                                             |                  | ±4% spread, PRATE = 5MHz,<br>SRATE = 70Mbps      |     | 42  | 57    |       |

|                                             |                  | Spread off, PRATE = 5MHz,<br>SRATE = 70Mbps      |     | 34  | 49    |       |

| Power-Down Supply Current                   | I <sub>CCZ</sub> | PD = low                                         |     | 10  | 50    | μΑ    |

#### MAX9258A AC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, V_{CCIO} = +1.71 \text{V to } +3.6 \text{V}, R_L = 50 \Omega \pm 1 \%, C_L = 8 pF, differential input voltage } IV_{ID}I = 0.1 \text{V to } 1.2 \text{V}, input IV_{CCIO} = +1.71 \text{V to } +3.6 \text{V}, R_L = 50 \Omega \pm 1 \%, C_L = 8 pF, differential input voltage } IV_{ID}I = 0.1 \text{V to } 1.2 \text{V}, input IV_{ID}I = 0.1 \text{V}$ common-mode voltage  $V_{CM} = IV_{ID}/2I$  to  $V_{CC}$  - IVID/2I,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{CC}$  = +3.3V,  $|V_{ID}| = 0.2V$ ,  $V_{CM} = 1.2V$ ,  $T_A = +25^{\circ}C$ ) (Notes 5, 6 and 7)

| PARAMETER                        | SYMBOL                                                                       | CONDITIONS                            | MIN                  | TYP | MAX                  | UNITS |

|----------------------------------|------------------------------------------------------------------------------|---------------------------------------|----------------------|-----|----------------------|-------|

| SWITCHING CHARACTERISTICS        | <b>;</b>                                                                     |                                       |                      |     |                      |       |

| Output Transition Time           | t <sub>R,</sub> t <sub>F</sub>                                               | (Figure 9)                            | 0.7                  |     | 2.2                  | ns    |

| Output Transition Time, PCLK_OUT | t <sub>R,</sub> t <sub>F</sub>                                               | (Figure 9)                            | 0.5                  |     | 1.5                  | ns    |

| Output Transition Time           | t <sub>R,</sub> t <sub>F</sub>                                               | V <sub>CCOUT</sub> = 1.71V (Figure 9) | 1.0                  |     | 2.8                  | ns    |

| Output Transition Time, PCLK_OUT | t <sub>R,</sub> t <sub>F</sub>                                               | V <sub>CCOUT</sub> = 1.71V (Figure 9) | 0.7                  |     | 2.2                  | ns    |

| Control Channel Transition Time  | t <sub>R1A</sub> , t <sub>F1A</sub> ,<br>t <sub>R1B</sub> , t <sub>F1B</sub> | (Figure 16)                           | 0.5                  |     | 1.2                  | ns    |

| Control Channel Transition Time  | t <sub>R2,</sub> t <sub>F2</sub>                                             | (Figure 16)                           | 0.6                  |     | 1.3                  | ns    |

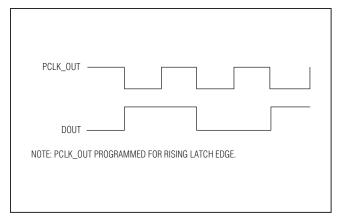

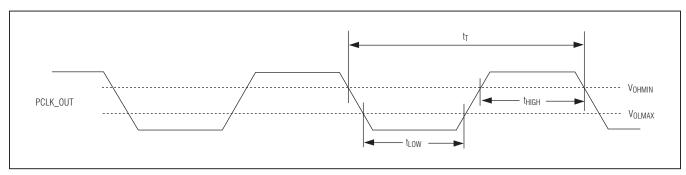

| PCLK_OUT High Time               | tHIGH                                                                        | (Figure 10)                           | 0.4 x t <sub>T</sub> |     | 0.6 x t <sub>T</sub> | ns    |

| PCLK_OUT Low Time                | t <sub>LOW</sub>                                                             | (Figure 10)                           | 0.4 x t <sub>T</sub> |     | 0.6 x t <sub>T</sub> | ns    |

## Fully Programmable Serializer/Deserializer with UART/I2C Control Channel

#### MAX9258A AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, V_{CCIO} = +1.71 \text{V to } +3.6 \text{V}, R_L = 50 \Omega \pm 1 \%, C_L = 8 pF, differential input voltage } IV_{ID}I = 0.1 \text{V to } 1.2 \text{V}, input IV_{CCIO} = +1.71 \text{V to } +3.6 \text{V}, R_L = 50 \Omega \pm 1 \%, C_L = 8 pF, differential input voltage } IV_{ID}I = 0.1 \text{V to } 1.2 \text{V}, input IV_{ID}I = 0.1 \text{V}$ common-mode voltage  $V_{CM} = |V_{ID}/2|$  to  $V_{CC} - |V|D/2|$ ,  $T_{A} = -40^{\circ}$ C to  $+105^{\circ}$ C, unless otherwise noted. Typical values are at  $V_{CC} = |V_{ID}/2|$ +3.3V,  $|V_{ID}| = 0.2V$ ,  $V_{CM} = 1.2V$ ,  $T_A = +25$ °C) (Notes 5, 6 and 7)

| PARAMETER                    | SYMBOL            | CONDITION                                                                    | S         | MIN                   | TYP  | MAX              | UNITS |

|------------------------------|-------------------|------------------------------------------------------------------------------|-----------|-----------------------|------|------------------|-------|

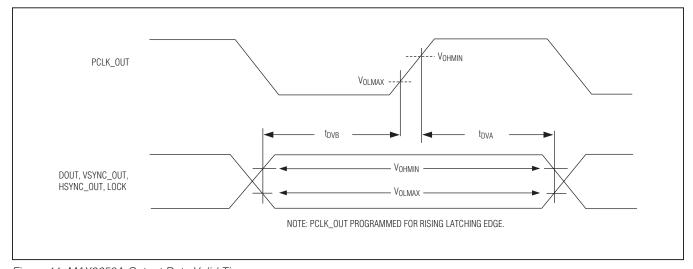

| Data Valid Before PCLK_ OUT  | t <sub>DVB</sub>  | (Figure 11)                                                                  |           | 0.35 x t <sub>T</sub> |      |                  | ns    |

| Data Valid After PCLK_OUT    | t <sub>DVA</sub>  | (Figure 11)                                                                  |           | 0.35 x t <sub>T</sub> |      |                  | ns    |

| Carial to Darallal Dalay     | t <sub>SPD1</sub> | Spread off (Figure 14)                                                       |           |                       |      | 8t <sub>T</sub>  | no    |

| Serial-to-Parallel Delay     | t <sub>SPD2</sub> | ±4% spread                                                                   |           |                       |      | 40t <sub>T</sub> | ns    |

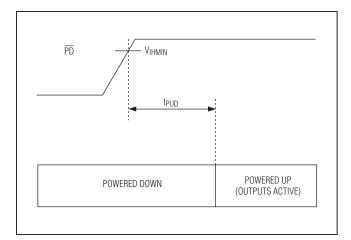

| Power-Up Delay               | t <sub>PUD</sub>  | (Figure 12)                                                                  |           |                       |      | 100              | ns    |

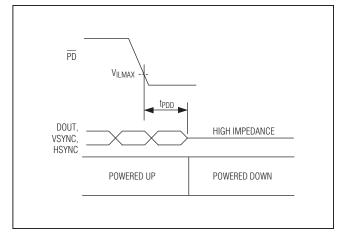

| Power-Down to High Impedance | t <sub>PDD</sub>  | (Figure 13)                                                                  |           |                       |      | 100              | ns    |

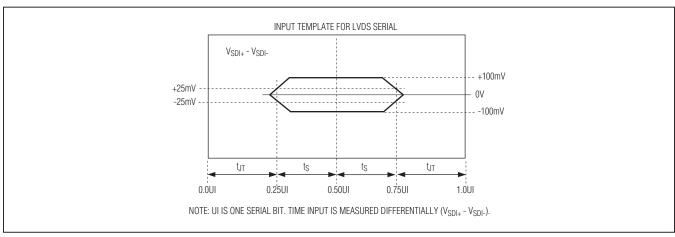

| Jitter Tolerance             | t <sub>JT</sub>   | Each half of the UI, 12 bit,<br>SRATE = 840Mbps, PRBS<br>pattern (Figure 15) | No spread | 0.25                  | 0.30 |                  | UI    |

- Note 2: Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to ground except V<sub>TH</sub> and V<sub>TL</sub>.

- Note 3: Maximum and minimum limits over temperature are guaranteed by design and characterization. Devices are production tested at  $T_A = +105$ °C.

- Note 4: One output at a time.

- Note 5: AC parameters are guaranteed by design and characterization, and are not production tested.

- Note 6: C<sub>I</sub> includes probe and test jig capacitance.

- **Note 7:** t<sub>T</sub> is the period of the PCLK\_OUT.

- Note 8: For high-speed mode timing, see the Detailed Description section.

- Note 9: 12°C timing parameters are specified for fast-mode 12°C. Max data rate = 400kbps.

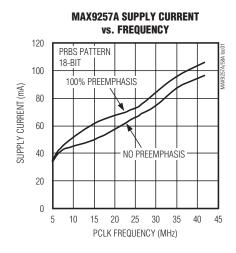

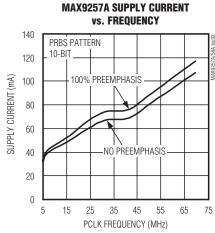

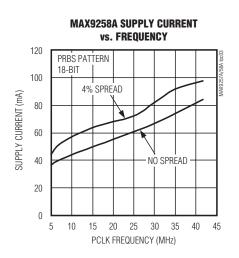

#### **Typical Operating Characteristics**

$(V_{CC} = +3.3V, R_L = 500, C_L = 8pF, T_A = +25^{\circ}C, unless otherwise noted.)$

## **Fully Programmable Serializer/Deserializer** with UART/I2C Control Channel

#### **Typical Operating Characteristics (continued)**

( $V_{CC}$  = +3.3V,  $R_L$  = 50O,  $C_L$  = 8pF,  $T_A$  = +25°C, unless otherwise noted.)

#### **MAX9258A SUPPLY CURRENT** vs. FREQUENCY 120 PRBS PATTERN 10-BIT 100 4% SPREAD SUPPLY CURRENT (mA) 80 60 NO SPREAD 40 20 0 10 15 5 20 25 30 PCLK FREQUENCY (MHz)

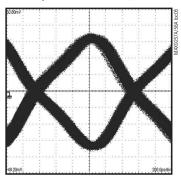

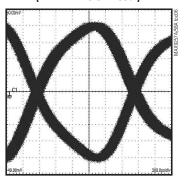

**SERIAL LINK SWITCHING PATTERN WITHOUT** PREEMPHASIS (BIT RATE = 840MHz, 2m STP CABLE)

SERIAL LINK SWITCHING PATTERN WITH PREEMPHASIS (BIT RATE = 840MHz, 2m STP CABLE) (PREEMPHASIS = 100%)

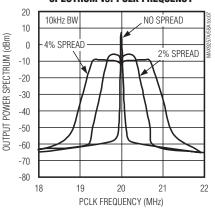

**MAX9257A OUTPUT POWER** SPECTRUM vs. PCLK FREQUENCY

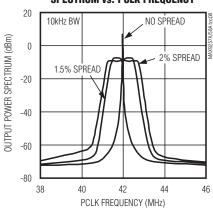

**MAX9257A OUTPUT POWER** SPECTRUM vs. PCLK FREQUENCY

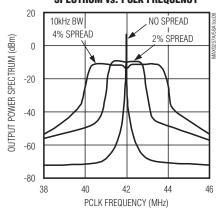

**MAX9258A OUTPUT POWER** SPECTRUM vs. PCLK FREQUENCY

BIT ERROR RATE (< 10<sup>-9</sup>) vs. **CABLE LENGTH**

BIT ERROR RATE (< 10<sup>-9</sup>) vs.

## Fully Programmable Serializer/Deserializer with UART/I2C Control Channel

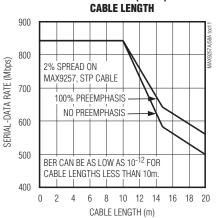

**Pin Configuration**

# **Fully Programmable Serializer/Deserializer** with UART/I2C Control Channel

### **MAX9257A Pin Description**

| P                | IN               |                         |                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|------------------|------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| TQFN             | LQFP             | NAME                    | FUNCTION                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| 1, 18            | 2, 21            | VCCIO                   | Single-Ended Input/Output Buffer Supply Voltage. Bypass V <sub>CCIO</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close as possible to the device with the smallest value capacitor closest to V <sub>CCIO</sub> . |  |  |  |  |  |  |  |  |

| 2, 11,<br>19, 34 | 3, 14,<br>22, 41 | GND                     | Digital Supply Ground                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 3–8              | 4–9              | DIN[9:14]/<br>GPIO[1:6] | Data Input/General Purpose Input/Output. When a serial-data word is less than 18 bits word length, DIN_ not programmed as data inputs becomes GPIO (Table 22). DIN[9:14] are internally pulled down to ground.                     |  |  |  |  |  |  |  |  |

| 9                | 10               | GNDFPLL                 | Filter PLL Ground                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| 10               | 11               | V <sub>CCFPLL</sub>     | Filter PLL Supply Voltage. Bypass $V_{CCFPLL}$ to GNDFPLL with 0.1 $\mu$ F and 0.001 $\mu$ F capacitors in parallel as close as possible to the device with the smallest value capacitor closest to $V_{CCFPLL}$ .                 |  |  |  |  |  |  |  |  |

| 12               | 15               | DIN15/GPIO7             | Data Input/General Purpose Input/Output. When a serial-data word is less than 18 bits word length, DIN_ not programmed as data input becomes GPIO (Table 22). DIN15 is internally pulled down to ground.                           |  |  |  |  |  |  |  |  |

| 13               | 16               | HSYNC_IN                | Horizontal SYNC Input. HSYNC_IN is internally pulled down to ground.                                                                                                                                                               |  |  |  |  |  |  |  |  |

| 14               | 17               | VSYNC_IN                | Vertical SYNC Input. VSYNC_IN is internally pulled down to ground.                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| 15               | 18               | PCLK_IN                 | Parallel Clock Input. PCLK_IN latches data and sync inputs and provides the PLL reference clock. PCLK_IN is internally pulled down to ground.                                                                                      |  |  |  |  |  |  |  |  |

| 16               | 19               | SCL/TX                  | Open-Drain Control Channel Output. SCL/TX becomes SCL output when UART-to-I2C is active. SCL/TX becomes TX output when UART-to-I2C is bypassed. Externally pull up to VCC.                                                         |  |  |  |  |  |  |  |  |

| 17               | 20               | SDA/RX                  | Open-Drain Control Channel Input/Output. SDA/RX becomes bidirectional SDA when UART-to- $^{12}$ C is active. SDA/RX becomes RX input when UART-to- $^{12}$ C is bypassed. SDA output requires a pullup to $^{12}$ C.               |  |  |  |  |  |  |  |  |

| 20, 33           | 23, 40           | V <sub>CC</sub>         | Digital Supply Voltage. Bypass $V_{CC}$ to ground with $0.1\mu F$ and $0.001\mu F$ capacitors in parallel as close as possible to the device with the smallest value capacitor closest to $V_{CC}$ .                               |  |  |  |  |  |  |  |  |

| 21               | 26               | GPIO8                   | General Purpose Input/Output                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| 22               | 27               | GPIO9                   | General Purpose Input/Output                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| 23               | 28               | VCCSPLL                 | Spread PLL Supply Voltage. Bypass $V_{CCSPLL}$ to GNDSPLL with $0.1\mu F$ and $0.001\mu F$ capacitors in parallel as close as possible to the device with the smallest value capacitor closest to $V_{CCSPLL}$ .                   |  |  |  |  |  |  |  |  |

| 24               | 29               | GNDSPLL                 | SPLL Ground                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| 25               | 30               | GNDLVDS                 | LVDS Ground                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| 26               | 31               | SDO-                    | Serial LVDS Inverting Output                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| 27               | 32               | SDO+                    | Serial LVDS Noninverting Output                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| 28               | 33               | V <sub>CCLVDS</sub>     | LVDS Supply Voltage. Bypass V <sub>CCLVDS</sub> to GNDLVDS with 0.1µF and 0.001µF capacitors in parallel as close as possible to the device with the smallest value capacitor closest to V <sub>CCLVDS</sub> .                     |  |  |  |  |  |  |  |  |

# **Fully Programmable Serializer/Deserializer** with UART/I2C Control Channel

### **MAX9257A Pin Description (continued)**

| Р                    | IN                                 | NAME       | FUNCTION                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|----------------------|------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| TQFN                 | LQFP                               | INAIVIE    | TONOTION                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 29                   | 34                                 | REM        | Remote Power-Up/Power-Down Select Input. Connect REM to ground for power-up to follow $V_{CC}.$ Connect REM high to $V_{CC}$ through $10k\Omega$ resistor for remote power-up. REM is internally pulled down to GND. |  |  |  |  |  |  |  |

| 30, 31, 32,<br>35–39 | 35, 38, 39,<br>42–46               | DIN[0:7]   | Data Inputs. DIN[0:7] are internally pulled down to ground.                                                                                                                                                          |  |  |  |  |  |  |  |

| 40                   | 47                                 | DIN8/GPIO0 | Data Input/General Purpose Input/Output. When a serial-data word is less than 18 bits word length, DIN_ not programmed as data input becomes GPIO (Table 22). DIN8 is internally pulled down to ground.              |  |  |  |  |  |  |  |

| _                    | 1, 12, 13<br>24, 25, 36,<br>37, 48 | N.C.       | No Connection. Not internally connected.                                                                                                                                                                             |  |  |  |  |  |  |  |

| _                    | _                                  | EP         | Exposed Pad for TQFN Package Only. Connect EP to ground.                                                                                                                                                             |  |  |  |  |  |  |  |

### **MAX9258A Pin Description**

| PIN                          | NAME                | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 12, 13, 24,<br>25, 36, 37 | N.C.                | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                   |

| 2                            | V <sub>CC</sub>     | Digital Supply Voltage. Bypass $V_{CC}$ to GND with 0.1 $\mu$ F and 0.001 $\mu$ F capacitors in parallel as close as possible to the device with the smallest value capacitor closest to $V_{CC}$ .                                                                                                                                                                                        |

| 3, 14                        | GND                 | Digital Supply Ground                                                                                                                                                                                                                                                                                                                                                                      |

| 4                            | PD                  | LVCMOS/LVTTL Power-Down Input. Drive $\overline{PD}$ high to power up the device and enable all outputs. Drive $\overline{PD}$ low to put all outputs in high impedance and reduce supply current. $\overline{PD}$ is internally pulled down to ground.                                                                                                                                    |

| 5                            | V <sub>CCLVDS</sub> | LVDS Supply Voltage. Bypass $V_{CCLVDS}$ to GNDLVDS with 0.1 $\mu$ F and 0.001 $\mu$ F capacitors in parallel as close as possible to the device with the smallest value capacitor closest to $V_{CCLVDS}$ .                                                                                                                                                                               |

| 6                            | SDI-                | Serial LVDS Inverting Input                                                                                                                                                                                                                                                                                                                                                                |

| 7                            | SDI+                | Serial LVDS Noninverting Input                                                                                                                                                                                                                                                                                                                                                             |

| 8                            | GNDLVDS             | LVDS Supply Ground                                                                                                                                                                                                                                                                                                                                                                         |

| 9                            | GNDPLL              | PLL Supply Ground                                                                                                                                                                                                                                                                                                                                                                          |

| 10                           | V <sub>CCPLL</sub>  | PLL Supply Voltage. Bypass V <sub>CCPLL</sub> to GNDPLL with 0.1µF and 0.001µF capacitors in parallel as close to the device as possible with the smallest value capacitor closest to V <sub>CCPLL</sub> .                                                                                                                                                                                 |

| 11                           | ERROR               | Active-Low, Open-Drain Error Output. ERROR asserts low to indicate a data transfer error was detected (parity, PRBS, or UART control channel error). ERROR is high to indicate no error detected. ERROR resets when the error registers are read for parity, control channel errors, and when PRBS enable bit is reset for PRBS errors. Pull up to $V_{CCOUT}$ with a $1k\Omega$ resistor. |

| 15                           | RX                  | LVCMOS/LVTTL Control Channel UART Output                                                                                                                                                                                                                                                                                                                                                   |

# **Fully Programmable Serializer/Deserializer** with UART/I2C Control Channel

#### **MAX9258A Pin Description (continued)**

| PIN                 | NAME                | FUNCTION                                                                                                                                                                                                                                                                                |

|---------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16                  | TX                  | LVCMOS/LVTTL Control Channel UART Input. TX is internally pulled up to V <sub>CCOUT</sub> .                                                                                                                                                                                             |

| 17                  | LOCK                | Open-Drain Lock Output. LOCK asserts high to indicate PLLs are locked with correct serial-word boundary alignment. LOCK asserts low to indicate PLLs are not locked or incorrect serial-word boundary alignment was detected. Pull up to $V_{\mbox{CCOUT}}$ with a $1k\Omega$ resistor. |

| 18                  | PCLK_OUT            | LVCMOS/LVTTL Recovered Clock Output                                                                                                                                                                                                                                                     |

| 19                  | VSYNC_OUT           | LVCMOS/LVTTL Vertical SYNC Output                                                                                                                                                                                                                                                       |

| 20                  | HSYNC_OUT           | LVCMOS/LVTTL Horizontal SYNC Output                                                                                                                                                                                                                                                     |

| 21, 28–35,<br>40–46 | DOUT[15:0]          | LVCMOS/LVTTL Data Outputs                                                                                                                                                                                                                                                               |

| 22, 39              | V <sub>CCOUT</sub>  | Output Supply Voltage. $V_{CCOUT}$ is the supply for all output buffers. Bypass $V_{CCOUT}$ to GNDOUT with $0.1\mu F$ and $0.001\mu F$ capacitors in parallel as close as possible to the device with the smallest value capacitor closest to $V_{CCOUT}$ .                             |

| 23, 38, 48          | GNDOUT              | Output Supply Ground                                                                                                                                                                                                                                                                    |

| 26                  | V <sub>CCSPLL</sub> | Spread-Spectrum PLL Supply Voltage. Bypass $V_{CCSPLL}$ to GNDSPLL with $0.1\mu F$ and $0.001\mu F$ capacitors in parallel as close as possible to the device with the smallest value capacitor closest to $V_{CCSPLL}$ .                                                               |

| 27                  | GNDSPLL             | SPLL Ground                                                                                                                                                                                                                                                                             |

| 47                  | CCEN                | LVCMOS/LVTTL Control Channel Enabled Output. CCEN asserts high to indicate that control channel is enabled.                                                                                                                                                                             |

Figure 1. MAX9257A LVDS DC Output Parameters

Figure 2. Input Hysteresis

Figure 3. MAX9257A Worst-Case Pattern Input

Figure 4. MAX9257A LVDS Control Channel Output Load and Output Rise/Fall Times

Figure 5. MAX9257A Input Setup and Hold Times

Figure 6. MAX9257A Parallel-to-Serial Delay

Figure 7. MAX9257A Parallel Input Clock Requirements

Figure 8. MAX9258A Worst-Case Pattern Output

Figure 9. MAX9258A Output Rise and Fall Times

Figure 10. MAX9258A Clock Output High and Low Time

Figure 11. MAX9258A Output Data Valid Times

Figure 12. MAX9258A Power-Up Delay

Figure 13. MAX9258A Power-Down Delay

Figure 14. MAX9258A Serial-to-Parallel Delay

Figure 15. MAX9258A Jitter Tolerance

Figure 16. Control Channel Transition Time

Figure 17. Serial Link with I2C Camera Programming Interface (Base Mode)

Figure 18. Serial Link with UART Camera Programming Interface (Bypass Mode)

## Fully Programmable Serializer/Deserializer with UART/I2C Control Channel

#### **Detailed Description**

The MAX9257A serializer pairs with the MAX9258A deserializer to form a complete digital video serial link. The electronic control unit (ECU) programs the registers in the MAX9257A, MAX9258A, and peripheral devices, such as a camera, during the control channel phase that occurs at startup or during the vertical blanking time. All control channel communication is half-duplex. The UART communication between the MAX9258A and the MAX9257A is encoded to allow transmission through AC-coupling capacitors. The MAX9257A communicates to the peripheral device through UART or I2C.

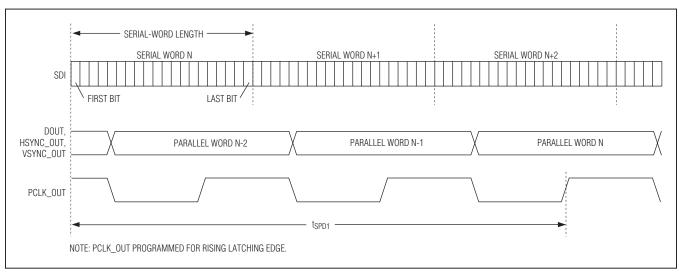

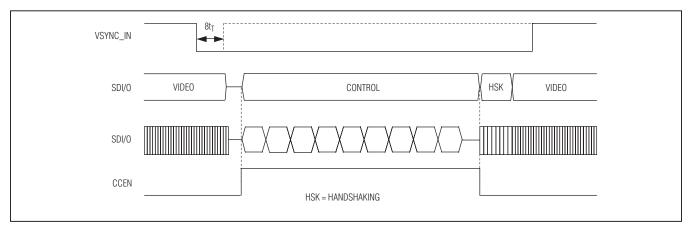

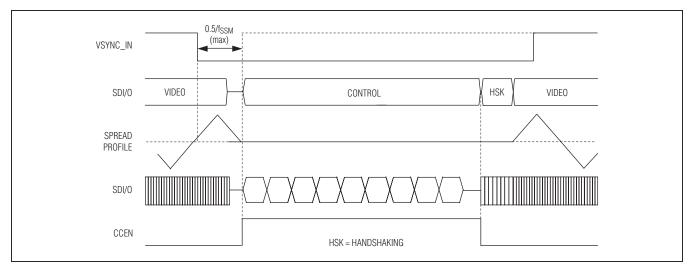

The MAX9257A/MAX9258A DC-balanced serializer and deserializer operate from a 5MHz-to-70MHz parallel clock frequency, and are capable of serializing and deserializing programmable 10, 12, 14, 16, and 18 bits parallel data during the video phase. The devices have two phases of operation: video and control channel (Figure 19 and 20). During the video phase, the MAX9257A accepts parallel video data and transmits serial encoded data over the LVDS link. The MAX9258A accepts the encoded serial LVDS data and converts it back to parallel output data. The MAX9257A has dedicated inputs for HSYNC and VSYNC. The selected VSYNC edge causes the MAX9257A/MAX9258A to enter the control channel phase. Nonactive VSYNC edge can be asserted after eight pixel clock cycles.

Figure 19. Video and Control Channel Phases (Spread Off)

Figure 20. Video and Control Channel Phases (MAX9257A Spread is Enabled)

## **Fully Programmable Serializer/Deserializer** with UART/I2C Control Channel

The video data are coded using two overhead bits (ENO and EN1) resulting in a serial-word length of N+2 bits. The devices feature programmable parity encoding that adds two parity bits to the serial word. Bit 0 (EN0) is the LSB that is serialized first without parity enabled. The parity bits are serialized first when parity is enabled.

The ECU programs the MAX9258A, MAX9257A, and peripheral devices at startup and during the control channel phase. In a digital video system, the control channel phase occurs during the vertical blanking time and synchronizes to the VSYNC signal. The programmable active edge of VSYNC initiates the control channel phase. Nonactive edge of VSYNC can transition at any time after 8 x t<sub>T</sub> if MAX9257A spread is not enabled and 0.5/fssm when enabled. At the end of video phase, the MAX9258A drives CCEN high to indicate to the ECU that the control channel is open. Programmable timers and ECU signal activity determine how long the control channel stays open. The timers are reset by ECU signal activity. ECU programming must not exceed the vertical blanking time to avoid loss of video data.

After the control channel phase closes, the MAX9257A sends a 546 or 1090 word pattern as handshaking (HSK) to synchronize the MAX9258A's internal clock recovery circuit to the MAX9257A's transmitted data. Following the handshaking, the control channel is closed and the video phase begins. The serial LVDS data is recovered and parallel data is valid on the programmed edge of the recovered pixel clock.

Table 1 and 2 show the default power-up values for the MAX9257A/MAX9258A registers. Tables 3 and 4 show the input and output supply references.