# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **General Description**

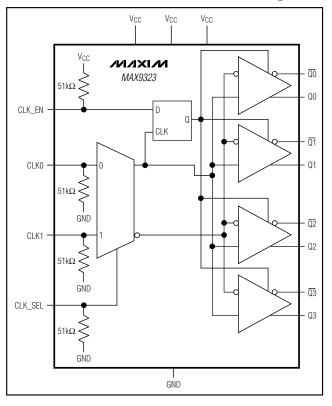

The MAX9323 low-skew, low-jitter, clock and data driver distributes one of two single-ended LVCMOS inputs to four differential LVPECL outputs. A single logic control signal (CLK\_SEL) selects the input signal to distribute to all outputs. The device operates from 3.0V to 3.6V, making the device ideal for 3.3V systems, and consumes only 25mA (max) of supply current.

The MAX9323 features low 150ps part-to-part skew, low 11ps output-to-output skew, and low 1.7ps RMS jitter, making the device ideal for clock and data distribution across a backplane or board. All outputs are enabled and disabled synchronously with the clock input to prevent partial output clock pulses.

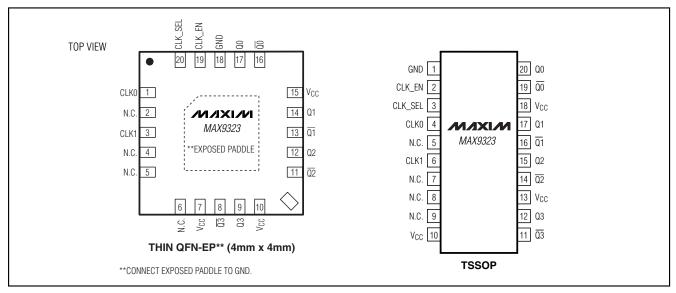

The MAX9323 is available in space-saving 20-pin TSSOP and ultra-small 20-pin 4mm × 4mm thin QFN packages and operates over the extended (-40°C to +85°C) temperature range. The MAX9323 is pin compatible with Integrated Circuit Systems' ICS8535-01.

#### Applications

Precision Clock Distribution Low-Jitter Data Repeater Data and Clock Driver and Buffer Central-Office Backplane Clock Distribution DSLAM Backplane Base Station Hubs

### Features

- 1.7ps<sub>RMS</sub> Added Random Jitter

- 150ps (max) Part-to-Part Skew

- 11ps Output-to-Output Skew

- 450ps Propagation Delay

- Pin Compatible with ICS8535-01

- Consumes Only 25mA (max) Supply Current (50% Less than ICS8535-01)

- Synchronous Output Enable/Disable

- Two Selectable LVCMOS Inputs

- ♦ 3.0V to 3.6V Supply Voltage Range

- -40°C to +85°C Operating Temperature Range

## Ordering Information

| PART        | TEMP RANGE     | PIN-PACKAGE      |

|-------------|----------------|------------------|

| MAX9323EUP  | -40°C to +85°C | 20 TSSOP         |

| MAX9323ETP* | -40°C to +85°C | 20 Thin QFN-EP** |

\*Future product—Contact factory for availability. \*\*EP = Exposed paddle.

Functional Diagram and Typical Operating Circuit appear at end of data sheet.

### Pin Configurations

###

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND0.3V to +4.0\                   | / |

|-------------------------------------------------------|---|

| $Q_{,}$ , $\overline{Q}_{,}$ , CLK_, CLK_SEL,         |   |

| CLK_EN to GND0.3V to (V <sub>CC</sub> + 0.3V          | ) |

| Continuous Output Current                             | ł |

| Surge Output Current100mA                             | 4 |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |   |

| 20-Pin TSSOP (derate 11mW/°C)879.1mW                  | V |

| 20-Pin 4mm × 4mm Thin QFN (derate 16.9mW/°C)1349.1mW  | V |

| Junction-to-Ambient Thermal Resistance in Still Air   |   |

| 20-Pin TSSOP+91°C/W                                   | V |

| 20-Pin 4mm × 4mm Thin QFN+59.3°C/M                    | V |

| 20-Pin TSSOP                | +20°C/W        |

|-----------------------------|----------------|

| 20-Pin 4mm × 4mm Thin QFN   | +2°C/W         |

| Operating Temperature Range | 40°C to +85°C  |

| Junction Temperature        | +150°C         |

| Storage Temperature Range   | 65°C to +150°C |

| Soldering Temperature (10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 3.0V \text{ to } 3.6V, \text{ outputs terminated with } 50\Omega \pm 1\% \text{ to } (V_{CC} - 2V), \text{ CLK}_SEL = V_{CC} \text{ or GND}, \text{ CLK}_EN = V_{CC}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}.$  Typical values are at  $V_{CC} = 3.3V$ ,  $T_A = +25^{\circ}\text{C}.$ ) (Notes 1, 2, and 3)

| PARAMETER                           | SYMBOL          | CO                                                            | MIN                   | ТҮР                      | MAX | UNITS                    |    |

|-------------------------------------|-----------------|---------------------------------------------------------------|-----------------------|--------------------------|-----|--------------------------|----|

| INPUTS (CLK0, CLK1, CLK_SE          | , CLK_EN)       |                                                               |                       |                          |     |                          |    |

| Input High Voltage                  | Mar.            | Figure 1                                                      | CLK0, CLK1            | 2                        |     | V <sub>CC</sub>          | V  |

| Input High Voltage                  | VIH             | Figure 1                                                      | CLK_EN, CLK_SEL       | 2                        |     | V <sub>CC</sub>          |    |

| Input Low Voltage                   | Ma              | Figure 1                                                      | CLK0, CLK1            | 0                        |     | 1.3                      | V  |

|                                     | VIL             | Figure 1                                                      | CLK_EN, CLK_SEL       | 0                        |     | 0.8                      | V  |

| Input High Current                  | lu i            | CLK0, CLK1, CLK_                                              | SEL = V <sub>CC</sub> |                          |     | 150                      |    |

| Input High Current                  | Ιн              | $CLK_EN = V_{CC}$                                             |                       | -5                       |     | +5                       | μA |

|                                     | Lu.             | CLK0, CLK1, CLK_SEL = GND                                     |                       | -5                       |     | +5                       | μA |

| Input Low Current                   | Ι <sub>ΙΣ</sub> | CLK_EN = GND                                                  | -150                  |                          |     |                          |    |

| Input Capacitance                   | CIN             | CLK0, CLK1, CLK_                                              | SEL, CLK_EN (Note 4)  |                          |     | 4                        | pF |

| OUTPUTS (Q_, $\overline{Q_}$ )      |                 |                                                               |                       |                          |     |                          |    |

| Single-Ended Output High<br>Voltage | V <sub>OH</sub> | Figure 1                                                      |                       | V <sub>CC</sub> -<br>1.4 |     | V <sub>CC</sub> -<br>1.0 | V  |

| Single-Ended Output Low<br>Voltage  | V <sub>OL</sub> | Figure 1                                                      |                       | V <sub>CC</sub> - 2.0    |     | V <sub>CC</sub> -<br>1.7 | V  |

| Differential Output Voltage         | V <sub>OD</sub> | Figure 1, V <sub>OD</sub> = V <sub>OH</sub> - V <sub>OL</sub> |                       | 0.6                      |     | 0.85                     | V  |

| SUPPLY                              |                 |                                                               |                       |                          |     |                          |    |

| Supply Current (Note 5)             | ICC             |                                                               |                       |                          |     | 25                       | mA |

### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 3.0V \text{ to } 3.6V, \text{ outputs terminated with } 50\Omega \pm 1\% \text{ to } (V_{CC} - 2V), f_{IN} < 266MHz, \text{ input duty cycle} = 50\%, \text{ input transition time} = 1.1ns (20\% to 80\%), V_{IH} = V_{CC}, V_{IL} = GND, CLK_SEL = V_{CC} \text{ or } GND, CLK_EN = V_{CC}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}.$  Typical values are at V<sub>CC</sub> = 3.3V, T<sub>A</sub> = +25^{\circ}\text{C}.) (Note 4)

| PARAMETER             | SYMBOL                              | CONDITIONS                                                               | MIN  | ТҮР | MAX | UNITS   |

|-----------------------|-------------------------------------|--------------------------------------------------------------------------|------|-----|-----|---------|

| Switching Frequency   | factory                             | $V_{OH} - V_{OL} \ge 0.6V$                                               | 266  | 800 |     | MHz     |

| Switching Frequency   | fmax                                | V <sub>OH</sub> - V <sub>OL</sub> ≥ 0.3V                                 | 1500 |     |     | IVILITZ |

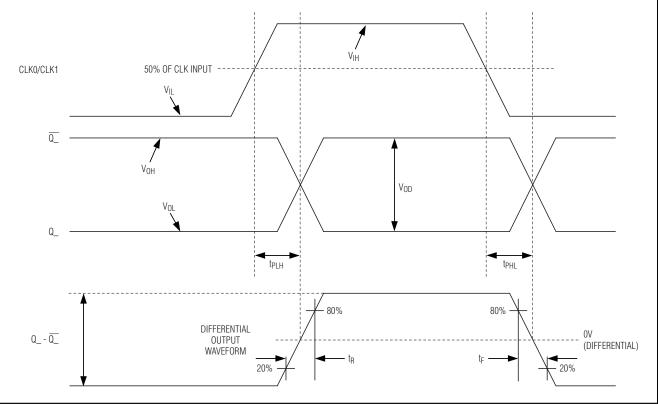

| Propagation Delay     | t <sub>PHL</sub> , t <sub>PLH</sub> | CLK0 or CLK1 to Q_, $\overline{Q}$ , Figure 1 (Note 6)                   | 100  | 450 | 600 | ps      |

| Output-to-Output Skew | tskoo                               | (Note 7)                                                                 |      |     | 30  | ps      |

| Part-to-Part Skew     | <b>t</b> SKPP                       | (Note 8)                                                                 |      |     | 150 | ps      |

| Output Rise Time      | t <sub>R</sub>                      | 20% to 80%, Figure 1                                                     | 100  | 203 | 300 | ps      |

| Output Fall Time      | tF                                  | 80% to 20%, Figure 1                                                     | 100  | 198 | 300 | ps      |

| Output Duty Cycle     | ODC                                 |                                                                          | 48   | 50  | 52  | %       |

| Added Random Jitter   | t <sub>RJ</sub>                     | f <sub>IN</sub> = 266MHz, clock pattern (Note 9)                         |      | 1.7 | 3   | ps(RMS) |

| Added Jitter (Note 9) | t <sub>AJ</sub>                     | V <sub>CC</sub> = 3.3V with 25mV superimposed sinusoidal noise at 100kHz |      |     | 10  | PS(P-P) |

**Note 1:** Measurements are made with the device in thermal equilibrium.

Note 2: Positive current flows into a pin. Negative current flows out of a pin.

Note 3: DC parameters are production tested at  $T_A = +25^{\circ}C$  and guaranteed by design over the full operating temperature range.

Note 4: Guaranteed by design and characterization. Limits are set at ±6 sigma.

Note 5: All pins open except V<sub>CC</sub> and GND.

Note 6: Measured from the 50% point of the input to the crossing point of the differential output signal.

Note 7: Measured between outputs of the same part at the differential signal crosspoint for a same-edge transition.

**Note 8:** Measured between outputs of different parts at the differential signal crosspoint under identical conditions for a same-edge transition.

Note 9: Jitter added to the input signal.

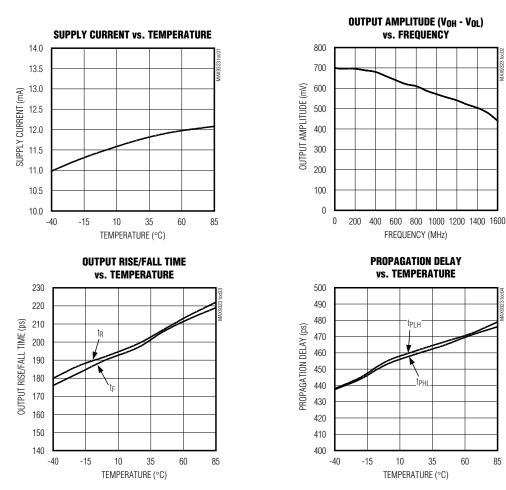

# **Typical Operating Characteristics**

$(V_{CC} = 3.3V, outputs terminated to (V_{CC} - 2V) through 50\Omega, CLK_SEL = V_{CC} or GND, CLK_EN = V_{CC}, T_A = +25^{\circ}C.)$

**MAX9323**

# **Pin Description**

| P          | IN         |                 | FUNCTION                                                                                                                                                                                                                                                                                                                                      |

|------------|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP      | QFN        | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                      |

| 1          | 18         | GND             | Ground. Provide a low-impedance connection to the ground plane.                                                                                                                                                                                                                                                                               |

| 2          | 19         | CLK_EN          | Synchronous Output Enable. Connect CLK_EN to V <sub>CC</sub> or leave floating to enable the differential outputs. Connect CLK_EN to GND to disable the differential outputs. When disabled, Q_ asserts low and $\overline{Q}$ asserts high. An internal 51k $\Omega$ pullup resistor to V <sub>CC</sub> allows CLK_EN to be left floating.   |

| 3          | 20         | CLK_SEL         | Clock Select Input. Connect CLK_SEL to V <sub>CC</sub> to select the CLK1 input. Connect CLK_SEL to GND or leave floating to select the CLK0 input. Only the selected CLK_ signal is reproduced at each output. An internal $51k\Omega$ pulldown resistor to GND allows CLK_SEL to be left floating.                                          |

| 4          | 1          | CLK0            | LVCMOS Clock Input. When CLK_SEL = GND, each set of outputs differentially reproduces CLK0. An internal 51k $\Omega$ pulldown resistor to GND forces the outputs (Q_, Q_) to differential low when CLK0 is left open or at GND, CLK_SEL = GND, and the outputs are enabled.                                                                   |

| 5, 7, 8, 9 | 2, 4, 5, 6 | N.C.            | No Connect. Not internally connected.                                                                                                                                                                                                                                                                                                         |

| 6          | 3          | CLK1            | LVCMOS Clock Input. When CLK_SEL = V <sub>CC</sub> , each set of outputs differentially reproduces CLK1. An internal 51k $\Omega$ pulldown resistor to GND forces the outputs (Q_, Q_) to differential low when CLK1 is left open or at GND, CLK_SEL = V <sub>CC</sub> , and the outputs are enabled.                                         |

| 10, 13, 18 | 7, 10, 15  | V <sub>CC</sub> | Positive Supply Voltage. Bypass V <sub>CC</sub> to GND with three $0.01\mu$ F and one $0.1\mu$ F ceramic capacitors. Place the $0.01\mu$ F capacitors as close to each V <sub>CC</sub> input as possible (one per V <sub>CC</sub> input). Connect all V <sub>CC</sub> inputs together, and bypass to GND with a $0.1\mu$ F ceramic capacitor. |

| 11         | 8          | $\overline{Q3}$ | Inverting Differential LVPECL Output. Terminate $\overline{Q3}$ to (V <sub>CC</sub> - 2V) with a 50 $\Omega$ ±1% resistor.                                                                                                                                                                                                                    |

| 12         | 9          | Q3              | Noninverting Differential LVPECL Output. Terminate Q3 to (V <sub>CC</sub> - 2V) with a 50 $\Omega$ ±1% resistor.                                                                                                                                                                                                                              |

| 14         | 11         | Q2              | Inverting Differential LVPECL Output. Terminate $\overline{\text{Q2}}$ to (V <sub>CC</sub> - 2V) with a 50 $\Omega$ ±1% resistor.                                                                                                                                                                                                             |

| 15         | 12         | Q2              | Noninverting Differential LVPECL Output. Terminate Q2 to (V <sub>CC</sub> - 2V) with a 50 $\Omega$ ±1% resistor.                                                                                                                                                                                                                              |

| 16         | 13         | Q1              | Inverting Differential LVPECL Output. Terminate $\overline{Q1}$ to (V <sub>CC</sub> - 2V) with a 50 $\Omega$ ±1% resistor.                                                                                                                                                                                                                    |

| 17         | 14         | Q1              | Noninverting Differential LVPECL Output. Terminate Q1 to (V <sub>CC</sub> - 2V) with a 50 $\Omega$ ±1% resistor.                                                                                                                                                                                                                              |

| 19         | 16         | QO              | Inverting Differential LVPECL Output. Terminate $\overline{\text{Q0}}$ to (V <sub>CC</sub> - 2V) with a 50 $\Omega$ ±1% resistor.                                                                                                                                                                                                             |

| 20         | 17         | Q0              | Noninverting Differential LVPECL Output. Terminate Q0 to (V <sub>CC</sub> - 2V) with a 50 $\Omega$ ±1% resistor.                                                                                                                                                                                                                              |

### **Detailed Description**

The MAX9323 low-skew, low-jitter, clock and data driver distributes one of two single-ended LVCMOS input signals to four differential LVPECL outputs. An input multiplexer allows selection of one of the two input signals. The output drivers operate at frequencies up to 1.5GHz. The MAX9323 operates from 3.0V to 3.6V, making it ideal for 3.3V systems.

### Data Inputs

#### Single-Ended LVCMOS Inputs

The MAX9323 accepts two single-ended LVCMOS inputs (CLK0 and CLK1, Figure 1). An internal reference (V<sub>CC</sub>/2) provides the input thresold voltage for CLK0 and CLK1. CLK\_SEL selects the CLK0 input or CLK1 input to be converted to four differential LVPECL signals (see Table 1). Connect CLK\_SEL to GND to

select CLK0. Connect CLK\_SEL to V<sub>CC</sub> to select CLK1. CLK0 and CLK1 are pulled to GND through internal  $51k\Omega$  resistors, when not connected.

#### CLK\_EN Input

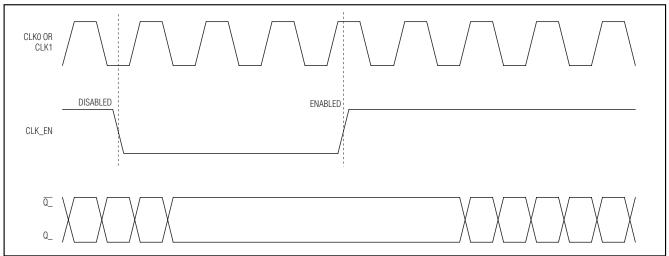

CLK\_EN enables/disables the differential outputs of the MAX9323. Connect CLK\_EN to V<sub>CC</sub> to enable the differential outputs. The (Q\_,  $\overline{Q}$ ) outputs are driven to a differential low condition when CLK\_EN = GND. Each differential output pair disables following successive rising and falling edges on CLK\_, after CLK\_EN connects to GND. Both a rising and falling edge on CLK\_ are required to complete the enable/disable function (Figure 2).

#### **CLK\_SEL** Input

CLK\_SEL selects which single-ended LVCMOS input signal is output differentially as four LVPECL signals. Connect CLK\_SEL to GND to select the CLK0 input.

Figure 1. MAX9323 Clock Input-to-Output Delay and Rise/Fall Time

Figure 2. MAX9323 CLK\_EN Timing Diagram

### **Table 1. Control Input Table**

| INPUTS |                             |      | OUTPUTS                       |                                                     |  |

|--------|-----------------------------|------|-------------------------------|-----------------------------------------------------|--|

| CLK_EN | _EN CLK_SEL SELECTED SOURCE |      | Q0–Q3                         | $\overline{\mathbf{Q0}}$ – $\overline{\mathbf{Q3}}$ |  |

| 0      | 0                           | CLK0 | Disabled, pulled to logic low | Disabled, pulled to logic high                      |  |

| 0      | 1                           | CLK1 | Disabled, pulled to logic low | Disabled, pulled to logic high                      |  |

| 1      | 0                           | CLK0 | Enabled                       | Enabled                                             |  |

| 1      | 1                           | CLK1 | Enabled                       | Enabled                                             |  |

Connect CLK\_SEL to V<sub>CC</sub> to select the CLK1 input. An internal  $51k\Omega$  pulldown resistor to GND allows CLK\_SEL to be left floating.

### \_Applications Information

#### **Output Termination**

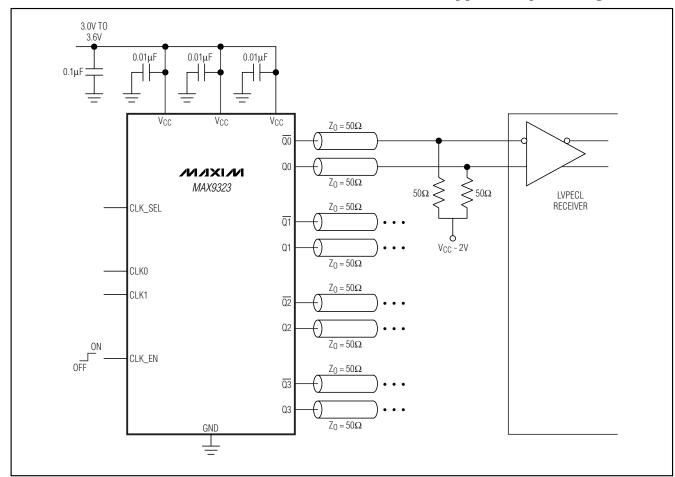

Terminate both outputs of each differential pair through  $50\Omega$  to (V<sub>CC</sub> - 2V) or use an equivalent Thevenin termination. Use identical termination on each output for the lowest output-to-output skew. Terminate both outputs when deriving a single-ended signal from a differential output. For example, using Q0 as a single-ended output requires termination for both Q0 and Q0.

Ensure that the output currents do not violate the current limits as specified in the *Absolute Maximum Ratings* table. Observe the device's total thermal limits under all operating conditions.

#### **Power-Supply Bypassing**

Bypass V<sub>CC</sub> to GND using three  $0.01\mu$ F ceramic capacitors and one  $0.1\mu$ F ceramic capacitor. Place the  $0.01\mu$ F capacitors (one per V<sub>CC</sub> input) as close to V<sub>CC</sub> as possible (see the *Typical Operating Circuit*). Use multiple bypass vias to minimize parasitic inductance.

#### **Circuit Board Traces**

Input and output trace characteristics affect the performance of the MAX9323. Connect each input and output to a 50 $\Omega$  characteristic impedance trace to minimize reflections. Avoid discontinuities in differential imped-

ance and maximize common-mode noise immunity by maintaining the distance between differential traces and avoiding sharp corners. Minimize the number of vias to prevent impedance discontinuities. Minimize skew by matching the electrical length of the traces.

### Chip Information

**MAX9323**

TRANSISTOR COUNT: 4430 PROCESS: BICMOS

### **Functional Diagram**

7

\_Typical Operating Circuit

**MAX9323**

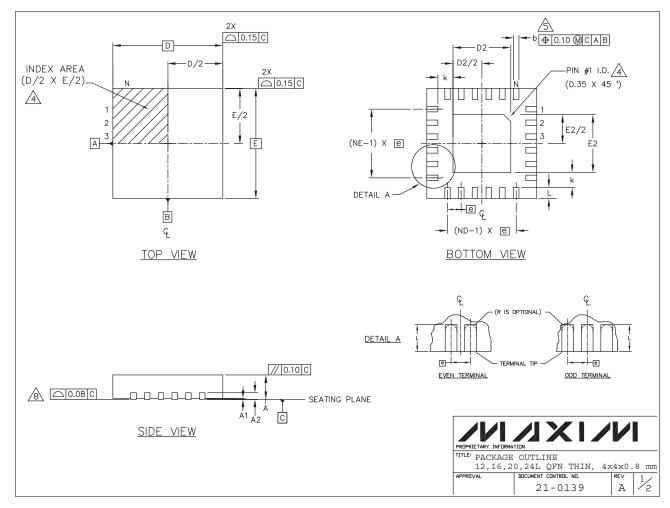

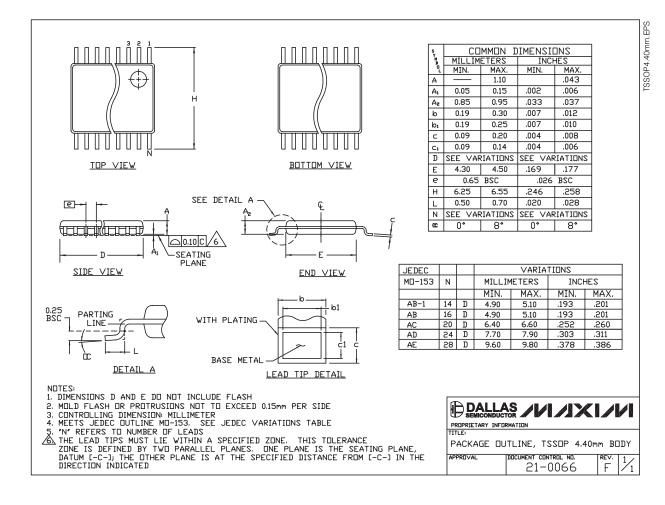

# Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

# Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

|               | COMMON DIMENSIONS |          |      |         |          |         |           |          |           |        |          |      |

|---------------|-------------------|----------|------|---------|----------|---------|-----------|----------|-----------|--------|----------|------|

| PKG           | 1                 | 2L 4×4   | ł    | 16L 4×4 |          | 20L 4×4 |           | 24L 4×4  |           |        |          |      |

| REF.          | MIN.              | NDM.     | MAX. | MIN.    | NDM.     | MAX.    | MIN.      | NDM.     | MAX.      | MIN.   | NDM.     | MAX. |

| Α             | 0.70              | 0.75     | 0.80 | 0.70    | 0.75     | 0.80    | 0.70      | 0.75     | 0.80      | 0.70   | 0.75     | 0.80 |

| A1            | 0.0               | 0.02     | 0.05 | 0.0     | 0.02     | 0.05    | 0.0       | 0.02     | 0.05      | 0.0    | 0.02     | 0.05 |

| A2            | 0.20 REF          |          |      |         | 0.20 REF |         | (         | 0.20 REF |           |        | 0.20 REF |      |

| ю             | 0.25              | 0.30     | 0.35 | 0.25    | 0.30     | 0.35    | 0.20      | 0.25     | 0.30      | 0.18   | 0.23     | 0.30 |

| D             | 3.90              | 4.00     | 4.10 | 3.90    | 4.00     | 4.10    | 3.90      | 4.00     | 4.10      | 3.90   | 4.00     | 4.10 |

| E             | 3.90              | 4.00     | 4.10 | 3.90    | 4.00     | 4.10    | 3.90      | 4.00     | 4.10      | 3.90   | 4.00     | 4.10 |

| e             |                   | 0.80 BSC | 2.   |         | 0.65 BSC |         | 0.50 BSC. |          | 0.50 BSC. |        |          |      |

| ĸ             | 0.25              | -        | -    | 0.25    | -        | -       | 0.25      | -        | -         | 0.25   | -        | -    |

| L             | 0.45              | 0.55     | 0.65 | 0.45    | 0.55     | 0.65    | 0.45      | 0.55     | 0.65      | 0.30   | 0.40     | 0.50 |

| N             |                   | 12       |      | 16      |          |         | 20        |          |           | 24     |          |      |

| ND            |                   | 3        |      | 4       |          | 5       |           | 6        |           |        |          |      |

| NE            |                   | З        |      | 4       |          | 5       |           | 6        |           |        |          |      |

| Jedec<br>Var. |                   | WGGB     |      |         | WGGC     |         |           | WGGD-    | 1         | WGGD-2 |          |      |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |  |

|------------------------|------|------|------|------|------|------|--|

| PKG. D2                |      |      |      |      | E2   |      |  |

| CODES                  | MIN. | NDM. | MAX. | MIN. | NDM. | MAX. |  |

| T1244-2                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |

| T1644-2                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |

| T2044-1                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |

| T2444-1                | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 |  |

#### NOTES:

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

- A THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- BIMENSION & APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- 6. ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- 7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- & COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- 9. DRAWING CONFORMS TO JEDEC MO220.

**MAX9323**

M \X | M

# Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2002 Maxim Integrated Products

Printed USA

**MAXIM** is a registered trademark of Maxim Integrated Products.

**MAX9323**

\_ 11