### imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

#### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **General Description**

The MAX9325 low-skew, 2:8 differential driver features extremely low output-to-output skew (50ps max) and part-to-part skew (225ps max). These features make the device ideal for clock and data distribution across a backplane or board. The device selects one of the two differential HSTL or LVECL/LVPECL inputs and repeats them at eight differential outputs. Outputs are compatible with LVECL and LVPECL, and can directly drive  $50\Omega$  terminated transmission lines.

The differential inputs can be configured to accept a single-ended signal when the unused complementary input is connected to the on-chip reference output voltage V<sub>BB</sub>. All inputs have internal pulldown resistors to V<sub>EE</sub>. The internal pulldowns and a fail-safe circuit ensure differential low default outputs when the inputs are left open or at V<sub>EE</sub>.

The MAX9325 operates over a 2.375V to 3.8V supply range for interfacing to differential HSTL and LVPECL signals. This allows high-performance clock or data distribution in systems with a nominal +2.5V or +3.3V supply. For LVECL operation, the device operates with a -2.375V to -3.8V supply.

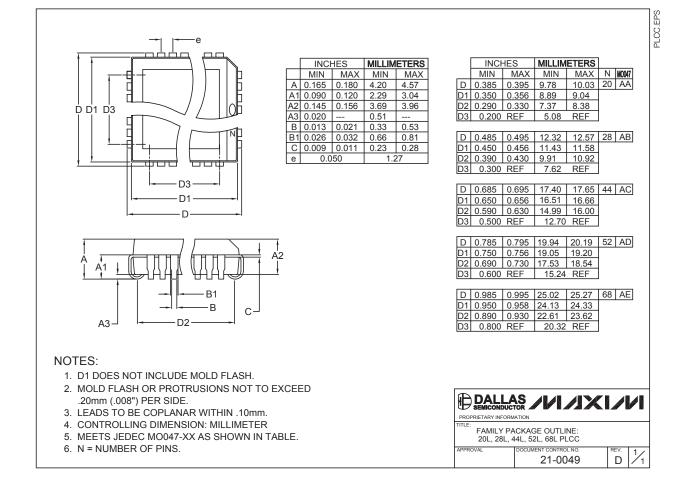

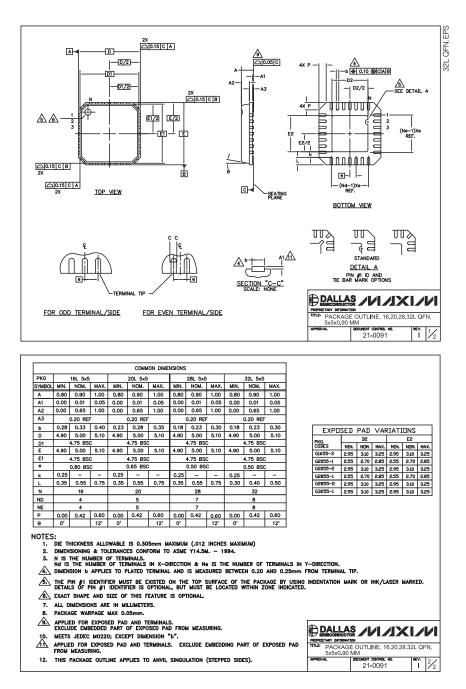

The MAX9325 is offered in 28-lead PLCC and spacesaving 28-lead QFN packages. The MAX9325 is specified for operation from -40°C to +85°C.

Applications

Precision Clock Distribution Low-Jitter Data Repeaters

#### \_Features

- ♦ 50ps (max) Output-to-Output Skew

- 1.5ps<sub>RMS</sub> (max) Random Jitter

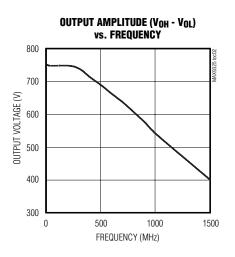

- Guaranteed 300mV Differential Output at 700MHz

- +2.375V to +3.8V Supplies for Differential HSTL/LVPECL

- ♦ -2.375V to -3.8V Supplies for Differential LVECL

- Two Selectable Differential Inputs

- On-Chip Reference for Single-Ended Inputs

- ♦ Outputs Low for Inputs Open or at VEE

- Pin Compatible with MC100LVE310

#### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE      |

|------------|----------------|------------------|

| MAX9325EQI | -40°C to +85°C | 28 PLCC          |

| MAX9325EGI | -40°C to +85°C | 28 QFN 5mm x 5mm |

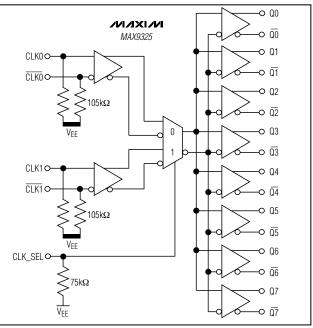

Functional Diagram appears at end of data sheet.

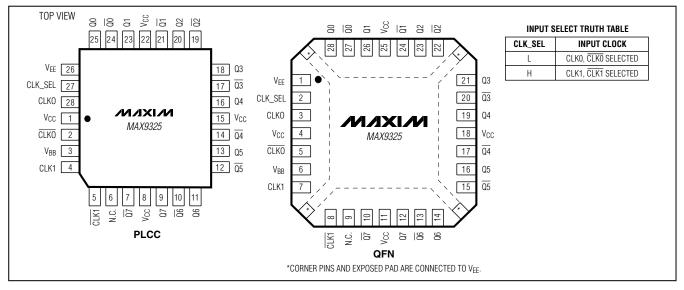

#### **Pin Configurations**

####

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# **MAX9325**

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> - V <sub>EE</sub> 0.3V to -           | +4.1V |

|-------------------------------------------------------|-------|

| Inputs (CLK_, CLK_, CLK_SEL) to VEE0.3V to (VCC +     | 0.3V) |

| CLK_ to CLK_                                          | ±3.0V |

| Continuous Output Current                             | 50mA  |

| Surge Output Current10                                | 00mA  |

| VBB Sink/Source Current±0.0                           | 65mA  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |       |

| 28-Lead PLCC (derate 10.5mW/°C above +70°C)84         | l2mW  |

| θJA in Still Air+95                                   | °C/W  |

| θ <sub>JC</sub> +25                                   | °C/W  |

| 28-Lead QFN (derate 20.8mW/°C above +70°C)1667mW |

|--------------------------------------------------|

| θ <sub>JA</sub> in Still Air+48°C/W              |

| θ <sub>JC</sub> +2°C/W                           |

| Operating Temperature Range40°C to +85°C         |

| Junction Temperature+150°C                       |

| Storage Temperature Range65°C to +150°C          |

| ESD Protection                                   |

| Human Body Model (CLK_, CLK_, Q_, Q_)≥2kV        |

| Soldering Temperature (10s)+300°C                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$((V_{CC} - V_{EE}) = 2.375V \text{ to } 3.8V, R_L = 50\Omega \pm 1\% \text{ to } V_{CC} - 2V. \text{ Typical values are at } (V_{CC} - V_{EE}) = 3.3V, V_{IH} = (V_{CC} - 1V), V_{IL} = (V_{CC} - 1.5V).)$ (Notes 1–4)

| PARAMETER                             |                 |                   |                            | -40°C |                            |                            | +25°C |                            | +85°C                      |     |                            |       |

|---------------------------------------|-----------------|-------------------|----------------------------|-------|----------------------------|----------------------------|-------|----------------------------|----------------------------|-----|----------------------------|-------|

| PARAMETER                             | SYMBOL          | CONDITIONS        | MIN                        | TYP   | МАХ                        | MIN                        | ТҮР   | MAX                        | MIN                        | TYP | MAX                        | UNITS |

| SINGLE-ENDED                          | INPUT (CLI      | K_SEL)            |                            |       |                            |                            |       |                            |                            |     |                            |       |

| Single-Ended<br>Input High<br>Voltage | VIH             | Figure 1          | V <sub>CC</sub><br>- 1.165 |       | V <sub>CC</sub>            | V <sub>CC</sub><br>- 1.165 |       | V <sub>CC</sub>            | V <sub>CC</sub><br>- 1.165 |     | V <sub>CC</sub>            | V     |

| Single-Ended<br>Input Low<br>Voltage  | VIL             | Figure 1          | VEE                        |       | V <sub>CC</sub><br>- 1.475 | VEE                        |       | V <sub>CC</sub><br>- 1.475 | VEE                        |     | V <sub>CC</sub><br>- 1.475 | V     |

| Input Current                         | l <sub>IN</sub> | VIH, VIL          | -10.0                      |       | +150                       | -10.0                      |       | +150                       | -10.0                      |     | +150                       | μA    |

| DIFFERENTIAL I                        | NPUT (CLK       | (_, <u>CLK_</u> ) |                            |       |                            |                            |       |                            |                            |     |                            |       |

| Single-Ended<br>Input High<br>Voltage | VIH             | Figure 1          | V <sub>CC</sub><br>- 1.165 |       | V <sub>CC</sub>            | V <sub>CC</sub><br>- 1.165 |       | V <sub>CC</sub>            | V <sub>CC</sub><br>- 1.165 |     | Vcc                        | V     |

| Single-Ended<br>Input Low<br>Voltage  | VIL             | Figure 1          | VEE                        |       | V <sub>CC</sub><br>- 1.475 | VEE                        |       | V <sub>CC</sub><br>- 1.475 | VEE                        |     | VCC<br>- 1.475             | V     |

| Differential Input<br>High Voltage    | VIHD            | Figure 1          | V <sub>EE</sub><br>+ 1.2   |       | V <sub>CC</sub>            | V <sub>EE</sub><br>+ 1.2   |       | Vcc                        | V <sub>EE</sub><br>+ 1.2   |     | V <sub>CC</sub>            | V     |

#### DC ELECTRICAL CHARACTERISTICS (continued)

$((V_{CC} - V_{EE}) = 2.375V \text{ to } 3.8V, R_L = 50\Omega \pm 1\% \text{ to } V_{CC} - 2V. \text{ Typical values are at } (V_{CC} - V_{EE}) = 3.3V, V_{IH} = (V_{CC} - 1V), V_{IL} = (V_{CC} - 1.5V).)$ (Notes 1–4)

| PARAMETER SYMBO                        |                                   |                                                          | -40°C                      |                            |                                      |                            | +25°C                      |                                      | +85°C                      |                            |                            | UNITS |

|----------------------------------------|-----------------------------------|----------------------------------------------------------|----------------------------|----------------------------|--------------------------------------|----------------------------|----------------------------|--------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| PARAMETER                              | STINDUL                           | CONDITIONS                                               | MIN                        | ТҮР                        | MAX                                  | MIN                        | ТҮР                        | MAX                                  | MIN                        | TYP                        | MAX                        | UNITS |

| Differential Input<br>Low Voltage      | VILD                              | Figure 1                                                 | VEE                        |                            | V <sub>CC</sub><br>- 0.095           | VEE                        |                            | V <sub>CC</sub><br>- 0.095           | VEE                        |                            | V <sub>CC</sub><br>- 0.095 | V     |

| Differential Input                     | V <sub>IHD</sub> -                | (V <sub>CC</sub> - V <sub>EE</sub> ) <<br>3.0V, Figure 1 | 0.095                      |                            | V <sub>CC</sub><br>- V <sub>EE</sub> | 0.095                      |                            | V <sub>CC</sub><br>- V <sub>EE</sub> | 0.095                      |                            | V <sub>CC</sub><br>- VEE   |       |

| Voltage                                | VILD                              | $(V_{CC} - V_{EE}) \ge$<br>3.0V, Figure 1                | 0.095                      |                            | 3.0                                  | 0.095                      |                            | 3.0                                  | 0.095                      |                            | 3.0                        | V     |

| Input Current                          | lın                               | Vih, Vil, Vihd,<br>Vild                                  | -10.0                      |                            | +150.0                               | -10.0                      |                            | +150.0                               | -10.0                      |                            | +150.0                     | μA    |

| OUTPUT (Q_, $\overline{Q}$             | _)                                |                                                          |                            |                            |                                      |                            |                            |                                      |                            |                            |                            |       |

| Single-Ended<br>Output High<br>Voltage | V <sub>OH</sub>                   | Figure 2                                                 | V <sub>CC</sub><br>- 1.085 | V <sub>CC</sub><br>- 0.977 | V <sub>CC</sub><br>- 0.880           | V <sub>CC</sub><br>- 1.025 | V <sub>CC</sub><br>- 0.949 | V <sub>CC</sub><br>- 0.88            | V <sub>CC</sub><br>- 1.025 | V <sub>CC</sub><br>- 0.929 | V <sub>CC</sub><br>- 0.88  | V     |

| Single-Ended<br>Output Low<br>Voltage  | V <sub>OL</sub>                   | Figure 2                                                 | V <sub>CC</sub><br>- 1.810 | V <sub>CC</sub><br>- 1.695 | V <sub>CC</sub><br>- 1.620           | V <sub>CC</sub><br>- 1.810 | V <sub>CC</sub><br>- 1.697 | V <sub>CC</sub><br>- 1.62            | V <sub>CC</sub><br>- 1.810 | V <sub>CC</sub><br>- 1.698 | V <sub>CC</sub><br>- 1.62  | V     |

| Differential<br>Output Voltage         | V <sub>OH</sub> - V <sub>OL</sub> | Figure 2                                                 | 535                        | 718                        |                                      | 595                        | 749                        |                                      | 595                        | 769                        |                            | mV    |

| REFERENCE VOLTAGE OUTPUT (VBB)         |                                   |                                                          |                            |                            |                                      |                            |                            |                                      |                            |                            |                            |       |

| Reference<br>Voltage Output            | $V_{BB}$                          | IBB = ±0.5mA<br>(Note 5)                                 | V <sub>CC</sub><br>- 1.38  | V <sub>CC</sub><br>- 1.318 | V <sub>CC</sub><br>- 1.26            | V <sub>CC</sub><br>- 1.38  | V <sub>CC</sub><br>- 1.325 | V <sub>CC</sub><br>- 1.26            | V <sub>CC</sub><br>- 1.38  | V <sub>CC</sub><br>- 1.328 | V <sub>CC</sub><br>- 1.26  | V     |

| SUPPLY                                 |                                   |                                                          |                            |                            |                                      |                            |                            |                                      |                            |                            |                            |       |

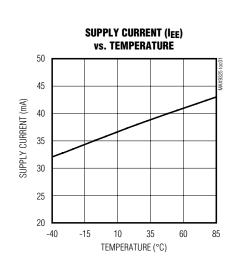

| Supply Current                         | I <sub>EE</sub>                   | (Note 6)                                                 |                            | 35                         | 50                                   |                            | 39                         | 55                                   |                            | 42                         | 65                         | mA    |

#### AC ELECTRICAL CHARACTERISTICS—PLCC Package

$((V_{CC} - V_{EE}) = 2.375V \text{ to } 3.8V, R_L = 50\Omega \pm 1\% \text{ to } V_{CC} - 2V, f_{IN} \le 500MHz, \text{ input transition time} = 125ps (20\% \text{ to } 80\%). Typical values are at (V_{CC} - V_{EE}) = 3.3V, V_{IH} = (V_{CC} - 1V), V_{IL} = (V_{CC} - 1.5V).) (Note 7)$

|                                          |                                 |                                                                              |     | -40°C |     |     | +25°C |     |     | +85°C |     | UNITS             |

|------------------------------------------|---------------------------------|------------------------------------------------------------------------------|-----|-------|-----|-----|-------|-----|-----|-------|-----|-------------------|

| PARAMETER                                | SYMBOL                          | CONDITIONS                                                                   | MIN | ТҮР   | MAX | MIN | ТҮР   | MAX | MIN | ТҮР   | MAX |                   |

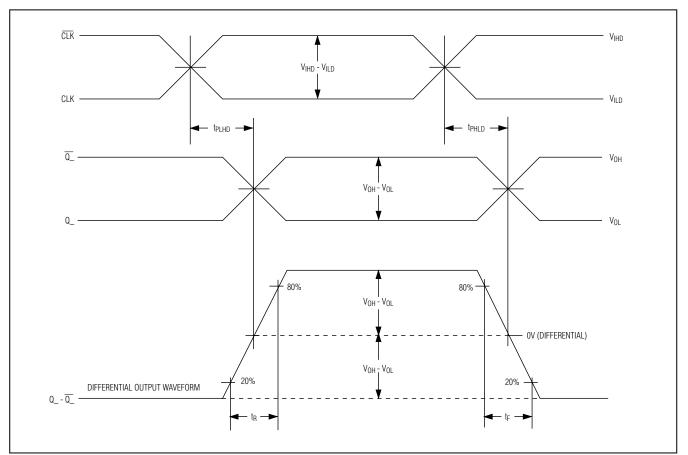

| Differential<br>Input-to-Output<br>Delay | tplhd<br>tphld                  | Figure 2                                                                     | 525 |       | 725 | 550 |       | 750 | 575 |       | 775 | ps                |

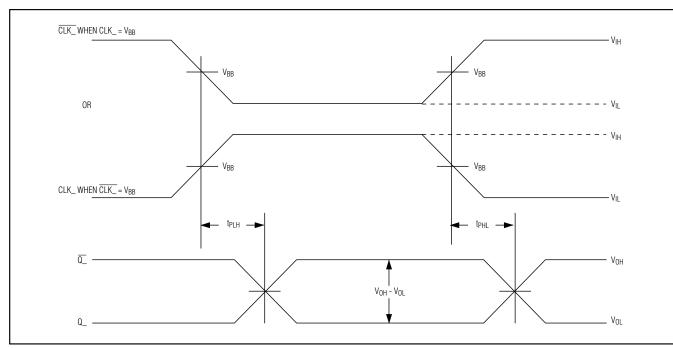

| Single-Ended<br>Input-to-Output<br>Delay | tplh<br>tphl                    | Figure 3 (Note 8)                                                            | 500 |       | 750 | 550 |       | 800 | 600 |       | 850 | ps                |

| Output-to-<br>Output Skew                | tskoo                           | (Note 9)                                                                     |     |       | 50  |     |       | 50  |     |       | 50  | ps                |

| Part-to-Part<br>Skew                     | t <sub>SKPP</sub>               | Differential input<br>(Note 10)                                              |     |       | 160 |     |       | 190 |     |       | 225 | ps                |

| Added Random<br>Jitter                   | t <sub>RJ</sub>                 | f <sub>IN</sub> = 0.5GHz<br>clock pattern<br>(Note 11)                       |     |       | 1.5 |     |       | 1.5 |     |       | 1.5 | ps <sub>RMS</sub> |

| Added<br>Deterministic<br>Jitter         | t <sub>DJ</sub>                 | f <sub>IN</sub> = 1.0Gbps,<br>2E <sup>23</sup> - 1 PRBS<br>pattern (Note 11) |     |       | 100 |     |       | 100 |     |       | 100 | psp-p             |

| Switching<br>Frequency                   | fMAX                            | V <sub>OH</sub> - V <sub>OL</sub> ≥<br>300mV clock<br>pattern                | 1.5 |       |     | 1.5 |       |     | 1.5 |       |     | GHz               |

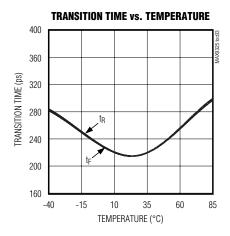

| Output Rise/Fall<br>Time (20% to<br>80%) | t <sub>R</sub> , t <sub>F</sub> | Figure 2                                                                     | 140 |       | 440 | 140 |       | 440 | 140 |       | 440 | ps                |

#### AC ELECTRICAL CHARACTERISTICS—QFN Package

$((V_{CC} - V_{EE}) = 2.375V \text{ to } 3.8V, R_L = 50\Omega \pm 1\% \text{ to } V_{CC} - 2V, f_{IN} \le 500MHz$ , input transition time = 125ps (20% to 80%). Typical values are at (V<sub>CC</sub> - V<sub>EE</sub>) = 3.3V, V<sub>I</sub>H = (V<sub>CC</sub> - 1V), V<sub>I</sub>L = (V<sub>CC</sub> - 1.5V).) (Note 7)

| DADAMETED                                |                                 |                                                                              |     | -40°C |     |     | +25°C |     |     | +85°C |     | UNITS             |

|------------------------------------------|---------------------------------|------------------------------------------------------------------------------|-----|-------|-----|-----|-------|-----|-----|-------|-----|-------------------|

| PARAMETER                                | SYMBOL                          | CONDITIONS                                                                   | MIN | ТҮР   | MAX | MIN | ТҮР   | MAX | MIN | ТҮР   | MAX |                   |

| Differential<br>Input-to-Output<br>Delay | tplhd<br>tphld                  | Figure 2                                                                     | 250 |       | 575 | 298 |       | 553 | 309 |       | 576 | ps                |

| Single-Ended<br>Input-to-Output<br>Delay | tplh<br>tphl                    | Figure 3 (Note 8)                                                            | 253 |       | 581 | 310 |       | 586 | 324 |       | 606 | ps                |

| Output-to-<br>Output Skew                | tskoo                           | (Note 9)                                                                     |     |       | 50  |     |       | 50  |     |       | 50  | ps                |

| Part-to-Part<br>Skew                     | tskpp                           | Differential input<br>(Note 10)                                              |     |       | 192 |     |       | 215 |     |       | 218 | ps                |

| Added Random<br>Jitter                   | t <sub>RJ</sub>                 | f <sub>IN</sub> = 0.5GHz<br>clock pattern<br>(Note 11)                       |     |       | 1.5 |     |       | 1.5 |     |       | 1.5 | ps <sub>RMS</sub> |

| Added<br>Deterministic<br>Jitter         | tDJ                             | f <sub>IN</sub> = 1.0Gbps,<br>2E <sup>23</sup> - 1 PRBS<br>pattern (Note 11) |     |       | 95  |     |       | 95  |     |       | 95  | psp-p             |

| Switching<br>Frequency                   | fmax                            | V <sub>OH</sub> - V <sub>OL</sub> ≥<br>300mV clock<br>pattern                | 1.5 |       |     | 1.5 |       |     | 1.5 |       |     | GHz               |

| Output Rise/Fall<br>Time (20% to<br>80%) | t <sub>R</sub> , t <sub>F</sub> | Figure 2                                                                     | 97  |       | 411 | 104 |       | 210 | 111 |       | 232 | ps                |

Note 1: Measurements are made with the device in thermal equilibrium.

**Note 2:** Current into a pin is defined as positive. Current out of a pin is defined as negative.

**Note 3:** DC parameters production tested at  $T_A = +25$ °C and guaranteed by design over the full operating temperature range.

**Note 4:** Single-ended input operation using  $V_{BB}$  is limited to ( $V_{CC} - V_{EE}$ ) = 3.0V to 3.8V.

**Note 5:** Use  $V_{BB}$  only for inputs that are on the same device as the  $V_{BB}$  reference.

**Note 6:** All pins open except  $V_{CC}$  and  $V_{EE}$ .

**Note 7:** Guaranteed by design and characterization. Limits are set at ±6 sigma.

Note 8: Measured from the 50% point of the input signal with the 50% point equal to V<sub>BB</sub>, to the 50% point of the output signal.

Note 9: Measured between outputs of the same part at the signal crossing points for a same-edge transition. Differential input signal.

Note 10: Measured between outputs of different parts under identical condition for same-edge transition.

Note 11: Device jitter added to the input signal. Differential input signal.

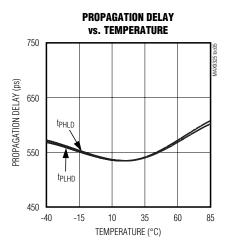

#### **Typical Operating Characteristics**

(PLCC package, typical values are at (V<sub>CC</sub> - V<sub>EE</sub>) = 3.3V, V<sub>IH</sub> = (V<sub>CC</sub> - 1V), V<sub>IL</sub> = (V<sub>CC</sub> - 1.5V), R<sub>L</sub> = 50 $\Omega$  ±1% to V<sub>CC</sub> - 2V, f<sub>IN</sub> = 500MHz, input transition time = 125ps (20% to 80%).)

#### \_\_\_\_\_Pin Description

| PIN          |                |                 |                                                                                                                                                                                                                                              |

|--------------|----------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLCC         | QFN            | NAME            | FUNCTION                                                                                                                                                                                                                                     |

| 1, 8, 15, 22 | 4, 11, 18, 25  | V <sub>CC</sub> | Positive Supply Voltage. Bypass each V <sub>CC</sub> to V <sub>EE</sub> with $0.1\mu$ F and $0.01\mu$ F ceramic capacitors. Place the capacitors as close to the device as possible, with the smaller value capacitor closest to the device. |

| 2            | 5              | <b>CLKO</b>     | Inverting Differential Clock Input 0. Internal 105k $\Omega$ pulldown to V <sub>EE</sub> .                                                                                                                                                   |

| 3            | 6              | V <sub>BB</sub> | Reference Output Voltage. Connect to the inverting or noninverting clock input to provide a reference for single-ended operation. When used, bypass $V_{BB}$ to $V_{CC}$ with a 0.01µF ceramic capacitor. Otherwise leave open.              |

| 4            | 7              | CLK1            | Noninverting Differential Clock Input 1. Internal 105k $\Omega$ pulldown to V <sub>EE</sub> .                                                                                                                                                |

| 5            | 8              | CLK1            | Inverting Differential Clock Input 1. Internal 105k $\Omega$ pulldown to V <sub>EE</sub> .                                                                                                                                                   |

| 6            | 9              | N.C.            | Not Connected                                                                                                                                                                                                                                |

| 7            | 10             | <u>Q7</u>       | Inverting Q7 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                                  |

| 9            | 12             | Q7              | Noninverting Q7 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                               |

| 10           | 13             | Q6              | Inverting Q6 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                                  |

| 11           | 14             | Q6              | Noninverting Q6 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                               |

| 12           | 15             | Q5              | Inverting Q5 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                                  |

| 13           | 16             | Q5              | Noninverting Q5 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                               |

| 14           | 17             | $\overline{Q4}$ | Inverting Q4 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                                  |

| 16           | 19             | Q4              | Noninverting Q4 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                               |

| 17           | 20             | Q3              | Inverting Q3 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                                  |

| 18           | 21             | Q3              | Noninverting Q3 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                               |

| 19           | 22             | Q2              | Inverting Q2 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                                  |

| 20           | 23             | Q2              | Noninverting Q2 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                               |

| 21           | 24             | Q1              | Inverting Q1 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                                  |

| 23           | 26             | Q1              | Noninverting Q1 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                               |

| 24           | 27             | QO              | Inverting Q0 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                                  |

| 25           | 28             | QO              | Noninverting Q0 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                               |

| 26           | 1              | VEE             | Negative Supply Voltage                                                                                                                                                                                                                      |

| 27           | 2              | CLK_SEL         | Clock Select Input. When driven low, the CLK0 input is selected. Drive high to select the CLK1 Input. The CLK_SEL threshold is equal to $V_{BB}$ . Internal 75k $\Omega$ pulldown to $V_{EE}$                                                |

| 28           | 3              | CLK0            | Noninverting Differential Clock Input 0. Internal 105k $\Omega$ pulldown to V <sub>EE</sub> .                                                                                                                                                |

| Exposed      | Exposed<br>Pad | _               | Internally Connected to V <sub>EE</sub>                                                                                                                                                                                                      |

**MAX9325**

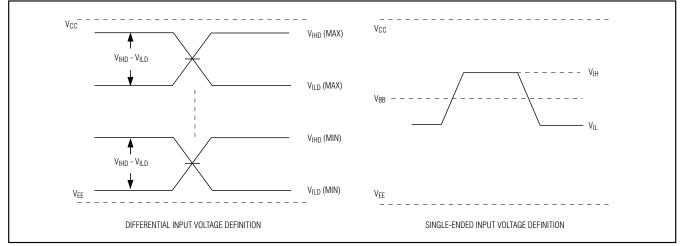

Figure 1. Input Voltage Definitions

Figure 2. Differential Input (CLK\_,  $\overline{CLK}$ ) to Output (Q\_,  $\overline{Q}$ ) Delay Timing Diagram

Figure 3. Single-Ended Input (CLK\_,  $\overline{\text{CLK}}$ ) to Output (Q\_,  $\overline{\text{Q}}$ ) Delay Timing Diagram

#### **Detailed Description**

The MAX9325 low-skew, 2:8 differential driver features extremely low output-to-output skew (50ps max) and part-to-part skew (225ps max). These features make the device ideal for clock and data distribution across a backplane or board. The device selects one of the two differential HSTL or LVECL/LVPECL inputs, and repeats them at eight differential outputs. Outputs are compatible with LVECL and LVPECL, and can directly drive  $50\Omega$  terminated transmission lines.

A 2:1 mux selects between the two differential inputs, CLK0, CLK0 and CLK1, CLK1. The 2:1 mux is switched by the single-ended CLK\_SEL input. A logic low selects the CLK0, CLK0 input. A logic high selects the CLK1, CLK1 input. The logic threshold for CLK\_SEL is set by an internal V<sub>BB</sub> voltage reference. The selected input is reproduced at eight differential outputs at speeds up to 700MHz.

The differential inputs can be configured to accept a single-ended signal when the unused complementary input is connected to the on-chip reference output voltage (V<sub>BB</sub>). A single-ended input of at least V<sub>BB</sub> ±95mV or a differential input of at least 95mV switches the outputs to the V<sub>OH</sub> and V<sub>OL</sub> levels specified in the *DC Electrical Characteristics.* The maximum magnitude of the differential input from CLK\_ to  $\overline{CLK}$  is ±3.0V or

$\pm(V_{CC}$  -  $V_{EE}),$  whichever is less. This limit also applies to the difference between a single-ended input and any reference voltage input.

The single-ended CLK\_SEL input has a 75k $\Omega$  pulldown to VEE that selects the default input, CLK0, CLK0, when CLK\_SEL is left open or at VEE. All the differential inputs have 105k $\Omega$  pulldowns to VEE. Internal pulldowns and a fail-safe circuit ensure differential low default outputs when the inputs are left open or at VEE.

Specifications for the high and low voltages of a differential input (V<sub>IHD</sub> and V<sub>ILD</sub>) and the differential input voltage (V<sub>IHD</sub> - V<sub>ILD</sub>) apply simultaneously.

For interfacing to differential HSTL and LVPECL signals, these devices operate over a +2.375V to +3.8V supply range, allowing high-performance clock or data distribution in systems with a nominal +2.5V or +3.3V supply. For differential LVECL operation, these devices operate from a -2.375V to -3.8V supply.

#### **Single-Ended Operation**

CLK\_SEL is a single-ended input with the input threshold internally set to V<sub>BB</sub>, and can be driven to V<sub>CC</sub> or V<sub>EE</sub> or by a single-ended LVPECL/LVECL signal. The CLK\_, CLK\_ are differential inputs but can be configured to accept single-ended inputs when operating at supply voltages greater than 2.58V. The recommended supply voltage for single-ended operation is 3.0V to 3.8V. A dif-

ferential input is configured for single-ended operation by connecting the on-chip reference voltage, V<sub>BB</sub>, to an unused complementary input as a reference. For example, the differential CLK0, CLK0 input is converted to a noninverting, single-ended input by connecting V<sub>BB</sub> to CLK0 and connecting the single-ended input to CLK0. Similarly, an inverting input is obtained by connecting V<sub>BB</sub> to CLK0 and connecting the single-ended input to CLK0. With a differential input configured as singleended (using V<sub>BB</sub>), the single-ended input can be driven to V<sub>CC</sub> or V<sub>EE</sub> or with a single-ended LVPECL/LVECL signal.

When configuring a differential input as a single-ended input, a user must ensure that the supply voltage (V<sub>CC</sub> - V<sub>EE</sub>) is greater than 2.58V. This is because the input high minimum level must be at (V<sub>EE</sub> + 1.2V) or higher for proper operation. The reference voltage V<sub>BB</sub> must be at least (V<sub>EE</sub> + 1.2V) or higher for the same reason because it becomes the high-level input when the other single-ended input swings below it. The minimum V<sub>BB</sub> output for the MAX9325 is (V<sub>CC</sub> - 1.38V). Substituting the minimum v<sub>BB</sub> output for (V<sub>BB</sub> = V<sub>EE</sub> + 1.2V) results in a minimum supply (V<sub>CC</sub> - V<sub>EE</sub>) of 2.58V. Rounding up to standard supplies gives the single-ended operating supply ranges (V<sub>CC</sub> - V<sub>EE</sub>) of 3.0V to 3.8V for the MAX9325.

When using the V<sub>BB</sub> reference output, bypass it with a  $0.01\mu$ F ceramic capacitor to V<sub>CC</sub>. If not used, leave it open. The V<sub>BB</sub> reference can source or sink 0.5mA, which is sufficient to drive two inputs.

#### **Applications Information**

#### **Output Termination**

Terminate the outputs through  $50\Omega$  to (V<sub>CC</sub> - 2V) or use equivalent Thevenin terminations. Terminate each Q and  $\overline{Q}$  output with identical termination on each for low output distortion. When a single-ended signal is taken from the differential output, terminate both Q\_ and  $\overline{Q}_{-}$ .

Ensure that output currents do not exceed the current limits as specified in the *Absolute Maximum Ratings* table. Under all operating conditions, the device's total thermal limits should be observed.

#### Supply Bypassing

Bypass each V<sub>CC</sub> to V<sub>EE</sub> with high-frequency surfacemount ceramic  $0.1\mu$ F and  $0.01\mu$ F capacitors. Place the capacitors as close to the device as possible with the  $0.01\mu$ F capacitor closest to the device pins.

Use multiple vias when connecting the bypass capacitors to ground. When using the V<sub>BB</sub> reference output, bypass it with a 0.01 $\mu$ F ceramic capacitor to V<sub>CC</sub>. If the V<sub>BB</sub> reference is not used, it can be left open.

#### Traces

Circuit board trace layout is very important to maintain the signal integrity of high-speed differential signals. Maintaining integrity is accomplished in part by reducing signal reflections and skew, and increasing common-mode noise immunity.

Signal reflections are caused by discontinuities in the  $50\Omega$  characteristic impedance of the traces. Avoid discontinuities by maintaining the distance between differential traces, not using sharp corners or using vias. Maintaining distance between the traces also increases common-mode noise immunity. Reducing signal skew is accomplished by matching the electrical length of the differential traces.

#### **Exposed-Pad Package**

The 28-lead QFN package (MAX9325EGI) has the exposed paddle on the bottom of the package that provides the primary heat removal path from the IC to the PC board, as well as excellent electrical grounding to the PC board. The MAX9325EGI's exposed pad is internally connected to VEE. Do not connect the exposed pad to a separate circuit ground plane unless VEE and the circuit ground are the same.

#### Chip Information

TRANSISTOR COUNT: 1030 PROCESS: Bipolar

#### \_Functional Diagram

#### \_Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

## **MAX9325**

#### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### \_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2004 Maxim Integrated Products

12

Printed USA

**MAXIM** is a registered trademark of Maxim Integrated Products.