# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **General Description**

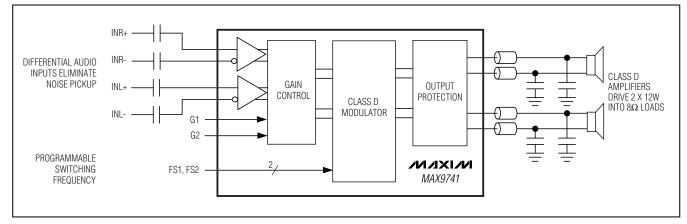

The MAX9741 stereo Class D audio power amplifier provides Class AB amplifier performance with Class D efficiency, conserving board space and eliminating the need for a bulky heatsink. Using a high-efficiency Class D architecture, it delivers 12W continuous output power into  $8\Omega$  loads. Proprietary modulation and switching schemes render the traditional Class D EMI suppression output filter unnecessary.

The MAX9741 offers two modulation schemes: a fixed-frequency mode (FFM), and a spread-spectrum mode (SSM) that reduces EMI-radiated emissions. The device utilizes a fully differential architecture, a full bridged output, and offers comprehensive click-and-pop suppression.

The MAX9741 features high 80dB PSRR, low 0.1% THD+N, and SNR in excess of 100dB. Short-circuit and thermal-overload protection prevent the device from being damaged during a fault condition. The MAX9741 is available in a 56-pin TQFN (8mm x 8mm x 0.8mm) package. The MAX9741 is specified over the extended -40°C to +85°C temperature range.

# \_Applications

LCD/PDP TVs CRT TVs PC Speakers

# **Features**

- Low-EMI Class D Amplifier

- Spread-Spectrum Mode Reduces EMI

- Passes FCC EMI Limits with Ferrite Bead Filters with 0.5m Cables

- ♦ 12W+12W Continuous Output Power into 8Ω

- Low 0.1% THD+N

- High PSRR (80dB at 1kHz)

- ♦ 10V to 25V Single-Supply Operation

- Differential Inputs Minimize Common-Mode Noise

- Pin-Selectable Gain Reduces Component Count

- Industry-Leading Click-and-Pop Suppression

- Short-Circuit and Thermal-Overload Protection

- Available in Thermally Efficient, Space-Saving 56-Pin TQFN (8mm x 8mm x 0.8mm) Package

# **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE | PKG<br>CODE |

|-------------|----------------|-------------|-------------|

| MAX9741ETN+ | -40°C to +85°C | 56 TQFN-EP* | T5688-3     |

+Denotes lead-free package.

\*EP = Exposed paddle.

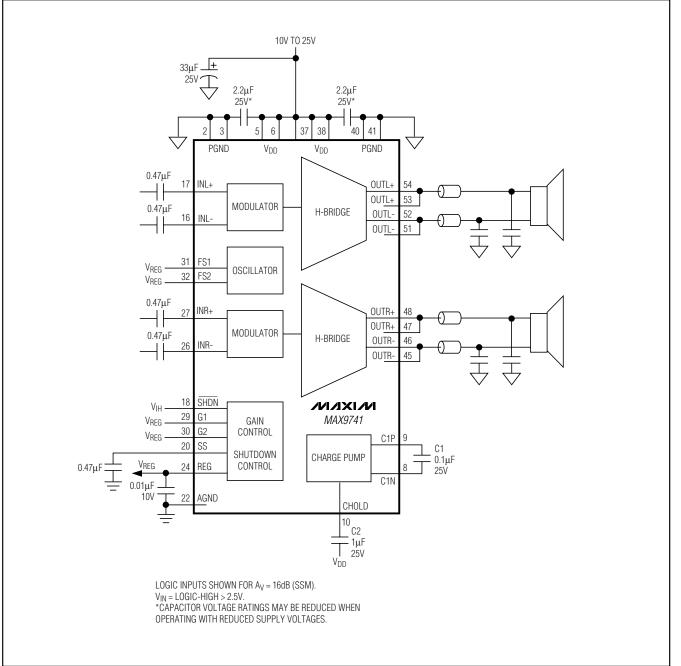

# \_Simplified Block Diagram

Pin Configuration appears at end of data sheet.

#

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# **ABSOLUTE MAXIMUM RATINGS**

(All voltages referenced to GND.)

| (All voltages referenced to GIVD.)        |                                  |

|-------------------------------------------|----------------------------------|

| V <sub>DD</sub> to PGND, AGND             |                                  |

| OUTR_, OUTL_, C1N                         | 0.3V to (V <sub>DD</sub> + 0.3V) |

| C1P(V <sub>DD</sub> - 0                   | .3V) to (CHOLD + 0.3V)           |

| CHOLD                                     | (V <sub>DD</sub> - 0.3V) to +40V |

| SHDN, FS_, G                              | 6.3V to 8V                       |

| All Other Pins to GND                     | 0.3V to +12V                     |

| Duration of OUTR_/OUTL_                   |                                  |

| Short Circuit to GND, VDD                 | Continuous                       |

| Continuous Input Current (VDD, PGND) .    | 2A                               |

| Continuous Input Current (all other pins) | ±20mA                            |

| Thermal Limits (Note 1)                   |                                  |

|                                           |                                  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )<br>Single-Laver PC Board |                                    |

|--------------------------------------------------------------------------------|------------------------------------|

| 56-Pin TQFN (derate 28.6mW/°C above +70                                        | °C)2.29W                           |

| θJA                                                                            |                                    |

| θJC                                                                            |                                    |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                          |                                    |

| Multiple-Layer PC Board                                                        |                                    |

| 56-Pin TQFN (derate 47.6mW/°C above +70                                        | °C)                                |

|                                                                                |                                    |

| θja                                                                            |                                    |

| θJA<br>θJC                                                                     |                                    |

|                                                                                | 0.6°C/W                            |

| θJC<br>Junction Temperature<br>Operating Temperature Range                     | 0.6°C/W<br>+150°C<br>40°C to +85°C |

| θ <sub>JC</sub><br>Junction Temperature                                        | 0.6°C/W<br>+150°C<br>40°C to +85°C |

Note 1: Thermal performance of this device is highly dependant on PC board layout. See the *Applications Information* for more detail.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 18V, GND = PGND = 0V, \overline{SHDN} \ge V_{IH}, A_V = 16dB, C_{SS} = C_{IN} = 0.47\mu$ F,  $C_{REG} = 0.01\mu$ F, C1 = 100nF,  $C2 = 1\mu$ F, FS1 = FS2 = GND (f<sub>S</sub> = 670kHz), R<sub>L</sub> connected between OUTL+ and OUTL- and OUTR+ and OUTR-, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Notes 1, 2)

| PARAMETER                                | SYMBOL          | CONDITIONS                             |                            | MIN  | ТҮР  | МАХ  | UNITS |

|------------------------------------------|-----------------|----------------------------------------|----------------------------|------|------|------|-------|

| GENERAL                                  | ·               | ·                                      |                            |      |      |      |       |

| Supply Voltage Range                     | V <sub>DD</sub> | Inferred from PSRR te                  | est                        | 10   |      | 25   | V     |

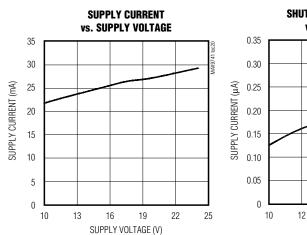

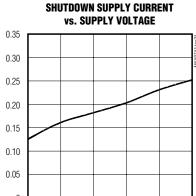

| Quiescent Current                        | IDD             | R <sub>L</sub> = Open                  |                            |      | 26   | 37   | mA    |

| Shutdown Current                         | ISHDN           |                                        |                            |      | 0.2  | 1.5  | μΑ    |

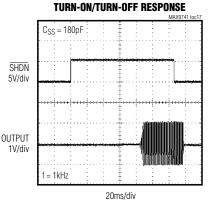

| Turn-On Time                             | tou             | $C_{SS} = 470 nF$                      |                            |      | 100  |      |       |

|                                          | ton             | $C_{SS} = 180 nF$                      |                            |      | 50   |      | ms    |

| Amplifier Output Resistance in Shutdown  |                 | SHDN = GND                             |                            | 150  | 320  |      | kΩ    |

|                                          |                 | $A_V = 13 dB$                          |                            | 35   | 53   | 80   |       |

| lane at lane a dama a                    | R <sub>IN</sub> | A <sub>V</sub> = 16dB                  |                            | 30   | 45   | 65   | kΩ    |

| Input Impedance                          |                 | A <sub>V</sub> = 19.1dB                |                            | 23   | 36   | 55   |       |

|                                          |                 | A <sub>V</sub> = 29.6dB                |                            | 10   | 14.3 | 22   |       |

|                                          |                 | G1 = L, G2 = L                         |                            | 29.4 | 29.6 | 29.8 |       |

| Voltago Coin                             |                 | G1 = L, G2 = H                         |                            | 18.9 | 19.1 | 19.3 | dB    |

| Voltage Gain                             | Av              | G1 = H, G2 = L                         |                            | 12.8 | 13   | 13.2 |       |

|                                          |                 | G1 = H, G2 = H                         |                            | 15.9 | 16   | 16.3 | 1     |

| Gain Matching                            |                 | Between channels                       |                            |      | 0.5  |      | %     |

| Output Offset Voltage                    | VOS             |                                        |                            |      | ±5   | ±30  | mV    |

| Common-Mode Rejection Ratio              | CMRR            | f <sub>IN</sub> = 1kHz, input referred |                            |      | 60   |      | dB    |

|                                          |                 | $V_{DD} = 10V$ to 25V                  |                            | 48   | 83   |      |       |

| Power-Supply Rejection Ratio<br>(Note 3) | PSRR            | 200mV <sub>P-P</sub> ripple            | f <sub>RIPPLE</sub> = 1kHz |      | 80   |      | dB    |

|                                          |                 | 2001114-5 ubbie                        | $f_{RIPPLE} = 20 kHz$      |      | 60   |      |       |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 18V, GND = PGND = 0V, \overline{SHDN} \ge V_{IH}, A_V = 16dB, C_{SS} = C_{IN} = 0.47\mu$ F,  $C_{REG} = 0.01\mu$ F, C1 = 100nF,  $C2 = 1\mu$ F, FS1 = FS2 = GND (f<sub>S</sub> = 670kHz), R<sub>L</sub> connected between OUTL+ and OUTL- and OUTR+ and OUTR-, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Notes 1, 2)

| PARAMETER                               | SYMBOL | CON                                                         | CONDITIONS                              |                 | MIN | ТҮР        | MAX | UNITS |

|-----------------------------------------|--------|-------------------------------------------------------------|-----------------------------------------|-----------------|-----|------------|-----|-------|

|                                         |        | $V_{DD} = 18V, THD+N =$                                     | $R_L = 8\Omega$                         |                 |     | 12         |     |       |

|                                         |        | 10%, f = 1kHz                                               | $R_L = 4\Omega$                         | $R_L = 4\Omega$ |     | 6.5        |     |       |

| Continuous Output Power                 |        | $V_{DD} = 24V, THD+N =$                                     | $R_L = 8\Omega$                         |                 |     | 11         |     |       |

| (Notes 4, 5)                            | PCONT  | 10%, f = 1kHz                                               | $R_L = 4\Omega$                         |                 |     | 5          |     | W     |

|                                         |        | $V_{DD} = 12V$ , THD+N =                                    | $R_L = 8\Omega$                         |                 |     | 8          |     |       |

|                                         |        | 10%, f = 1kHz                                               | $R_L = 4\Omega$                         |                 |     | 8.5        |     | 1     |

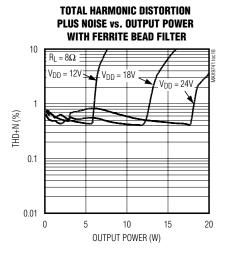

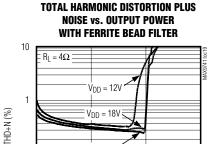

| Total Harmonic Distortion Plus<br>Noise | THD+N  | f <sub>IN</sub> = 1kHz, either FFM<br>P <sub>OUT</sub> = 4W | or SSM, $R_L = 8$                       | 3Ω,             |     | 0.1        |     | %     |

|                                         |        | $R_{L} = 8\Omega$ ,                                         | L la vaja la ta d                       | FFM             |     | 95.8       |     |       |

| Signal-to-Noise Ratio                   |        | $P_{OUT} = 4W,$<br>f = 1kHz<br>BW = 22Hz to 22kHz           | Unweighted                              | SSM             |     | 91.8       |     | dB    |

|                                         | SNR    |                                                             | A-weighted                              | FFM             |     | 99.1       |     |       |

|                                         |        |                                                             |                                         | SSM             |     | 95.7       |     |       |

| Crosstalk                               |        | Left to right, right to left                                | ft, 8 $\Omega$ load, f <sub>IN</sub> :  | = 10kHz         |     | 65         |     | dB    |

|                                         |        | FS1 = L, FS2 = L                                            |                                         |                 | 560 | 670        | 800 | kHz   |

|                                         |        | FS1 = L, FS2 = H                                            |                                         |                 |     | 930        |     |       |

| Oscillator Frequency                    | fosc   | FS1 = H, FS2 = L                                            |                                         |                 |     | 470        |     |       |

|                                         |        | FS1 = H, FS2 = H (spr                                       | FS1 = H, FS2 = H (spread-spectrum mode) |                 |     | 670<br>±7% |     |       |

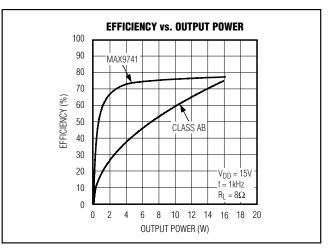

|                                         |        | $V_{DD}=12V,R_L=8\Omega,$                                   | Pout = 8W                               |                 |     | 78         |     |       |

| Efficiency (Note 4)                     | η      | $V_{DD} = 18V, R_L = 8\Omega, P_{OUT} = 10W$                |                                         |                 |     | 78         |     | %     |

| Regulator Output                        | VREG   |                                                             |                                         |                 |     | 6          |     | V     |

| DIGITAL INPUTS (SHDN, FS_,              | G_)    | ·                                                           |                                         |                 | •   |            |     |       |

| Input Throoboldo                        |        | VIH                                                         |                                         |                 | 2.5 |            |     | V     |

| Input Thresholds                        |        | V <sub>IL</sub>                                             |                                         |                 |     |            | 0.8 |       |

| Input Leakage Current                   |        |                                                             |                                         |                 |     |            | ±1  | μA    |

**Note 2:** All devices are 100% production tested at +25°C. All temperature limits are guaranteed by design.

Note 3: PSRR is specified with the amplifier inputs connected to GND through CIN.

Note 4: Testing performed with a resistive load in series with an inductor to simulate an actual speaker load. For  $R_L = 8\Omega$ ,  $L = 68\mu$ H. For  $R_L = 12\Omega$ ,  $L = 100\mu$ H. For  $R_L = 16\Omega$ ,  $L = 120\mu$ H.

**Note 5:** Output power measured at  $T_A = +25^{\circ}C$ , with a soak time of 15 minutes.

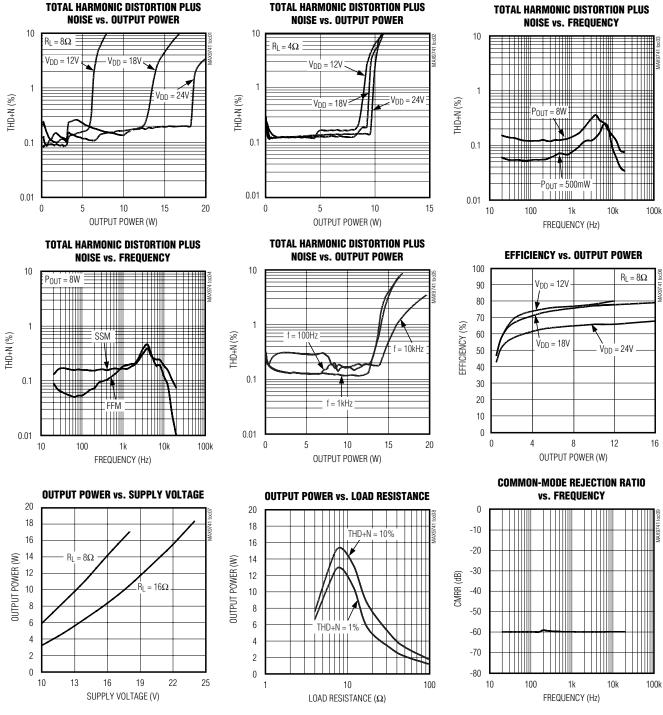

$(V_{DD} = 18V, R_{L} = 8\Omega, f_{IN} = 1 \text{ kHz}, 33 \mu\text{H}$  with  $4\Omega$ ,  $68 \mu\text{H}$  with  $8\Omega$ , part in SSM mode,  $136 \mu\text{H}$  with  $16\Omega$ , measurement BW = 22 \text{Hz} to

22kHz, unless otherwise noted.)

**Typical Operating Characteristics**

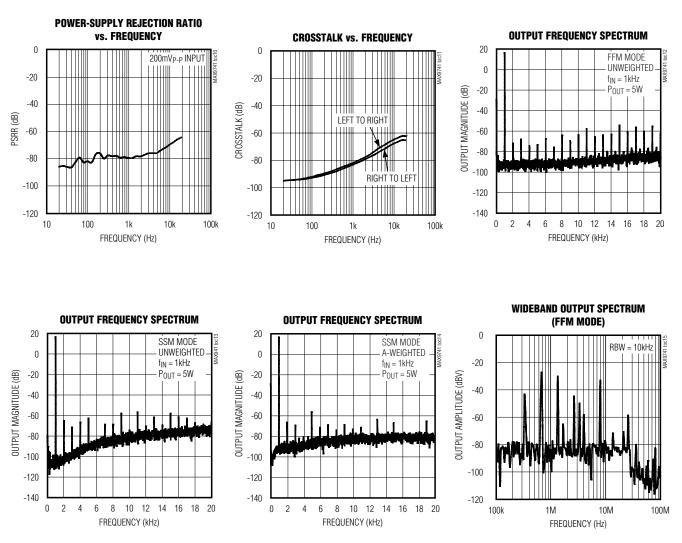

# **Typical Operating Characteristics (continued)**

$(V_{DD} = 18V, R_L = 8\Omega, f_{IN} = 1kHz, 33\mu H$  with  $4\Omega$ ,  $68\mu H$  with  $8\Omega$ , part in SSM mode,  $136\mu H$  with  $16\Omega$ , measurement BW = 22Hz to 22kHz, unless otherwise noted.)

# **Typical Operating Characteristics (continued)**

$(V_{DD} = 18V, R_L = 8\Omega, f_{IN} = 1kHz, 33\mu H with 4\Omega, 68\mu H with 8\Omega, part in SSM mode, 136\mu H with 16\Omega, measurement BW = 22Hz to 22kHz, unless otherwise noted.)$

$V_{DD} = 24V$

5

OUTPUT POWER (W)

10

15

0.1

0.01

0

14

SUPPLY VOLTAGE (V)

16

18

20

MAX974

M/IXI/M

# **Pin Description**

| PIN                                                                             | NAME            | FUNCTION                                                                                                                             |  |  |

|---------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 4, 7, 11–15, 19, 21,<br>23, 25, 28, 33–36, 39,<br>42, 43, 44, 49, 50, 55, 56 | N.C.            | No Connection. Not internally connected.                                                                                             |  |  |

| 2, 3, 40, 41                                                                    | PGND            | Power Ground                                                                                                                         |  |  |

| 5, 6, 37, 38                                                                    | V <sub>DD</sub> | Power-Supply Input                                                                                                                   |  |  |

| 8                                                                               | C1N             | Charge-Pump Flying Capacitor Negative Terminal                                                                                       |  |  |

| 9                                                                               | C1P             | Charge-Pump Flying Capacitor Positive Terminal                                                                                       |  |  |

| 10                                                                              | CHOLD           | Charge-Pump Hold Capacitor. Connect a $1\mu$ F capacitor from CHOLD to V <sub>DD</sub> .                                             |  |  |

| 16                                                                              | INL-            | Left-Channel Negative Input                                                                                                          |  |  |

| 17                                                                              | INL+            | Left-Channel Positive Input                                                                                                          |  |  |

| 18                                                                              | SHDN            | Active-Low Shutdown. Connect $\overline{\text{SHDN}}$ to GND to disable the device. Connect to $V_{\text{DD}}$ for normal operation. |  |  |

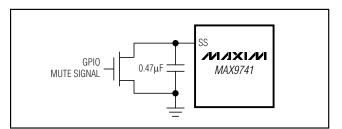

| 20                                                                              | SS              | Soft-Start. Connect a 0.47µF capacitor from SS to GND to enable soft-start feature.                                                  |  |  |

| 22                                                                              | AGND            | Analog Ground                                                                                                                        |  |  |

| 24                                                                              | REG             | Internal Regulator Output. Bypass with a 0.01µF capacitor to PGND.                                                                   |  |  |

| 26                                                                              | INR-            | Right-Channel Negative Input                                                                                                         |  |  |

| 27                                                                              | INR+            | Right-Channel Positive Input                                                                                                         |  |  |

| 29                                                                              | G1              | Gain-Select Input 1                                                                                                                  |  |  |

| 30                                                                              | G2              | Gain-Select Input 2                                                                                                                  |  |  |

| 31                                                                              | FS1             | Frequency-Select Input 1                                                                                                             |  |  |

| 32                                                                              | FS2             | Frequency-Select Input 2                                                                                                             |  |  |

| 45, 46                                                                          | OUTR-           | Right-Channel Negative Audio Output                                                                                                  |  |  |

| 47, 48                                                                          | OUTR+           | Right-Channel Positive Audio Output                                                                                                  |  |  |

| 51, 52                                                                          | OUTL-           | Left-Channel Negative Audio Output                                                                                                   |  |  |

| 53, 54                                                                          | OUTL+           | Left-Channel Positive Audio Output                                                                                                   |  |  |

| _                                                                               | EP              | Exposed Paddle. Connect to GND.                                                                                                      |  |  |

# **Detailed Description**

The MAX9741 low-EMI, Class D audio power amplifier features several improvements to switch-mode amplifier technology. This device offers Class AB performance with Class D efficiency, while occupying minimal board space. A unique modulation scheme and spread-spectrum switching mode create a compact, flexible, low-noise, efficient audio power amplifier. The differential input architecture reduces commonmode noise pickup, and can be used without inputcoupling capacitors. The device can also be configured as a single-ended input amplifier.

# **MAX9741**

# **Operating Modes**

# Fixed-Frequency Modulation (FFM) Mode

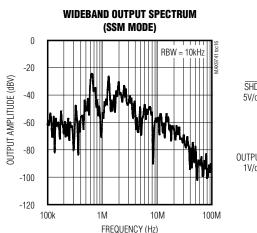

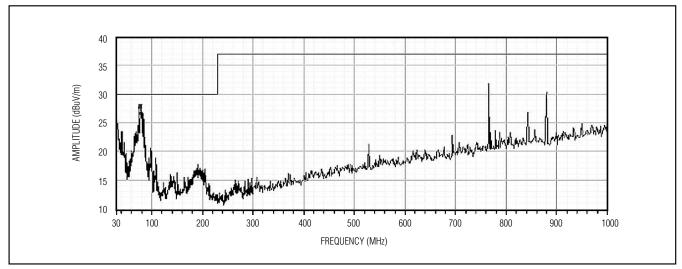

The MAX9741 features three FFM modes with different switching frequencies (Table 1). In FFM mode, the frequency spectrum of the Class D output consists of the fundamental switching frequency and its associated harmonics (see the Wideband Output Spectrum graph in the *Typical Operating Characteristics*). The MAX9741 allows the switching frequency to be changed by ±35%, should the frequency of one or more of the harmonics fall in a sensitive band. This can be done at any time and does not affect audio reproduction.

| FS1 | FS2 | SWITCHING MODE<br>(kHz) |

|-----|-----|-------------------------|

| L   | L   | 670                     |

| L   | Н   | 930                     |

| Н   | L   | 470                     |

| Н   | Н   | 670 ±7%                 |

# Table 1. Operating Modes

# Spread-Spectrum Modulation (SSM) Mode

A unique, proprietary spread-spectrum mode flattens the wideband spectral components, improving EMI emissions that may be radiated by the speaker and cables. This mode is enabled by setting FS1 = FS2 = H. In SSM mode, the switching frequency varies randomly by  $\pm$ 7% around the center frequency (670kHz). The modulation scheme remains the same, but the period of the triangle waveform changes from cycle to cycle. Instead of a large amount of spectral energy present at multiples of the switching frequency, the energy is now spread over a bandwidth that increases with frequency. Above a few megahertz, the wideband spectrum looks like white noise for EMI purposes.

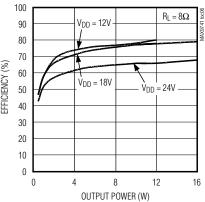

# Efficiency

Efficiency of a Class D amplifier is attributed to the region of operation of the output stage transistors. In a Class D amplifier, the output transistors act as current-steering switches and consume negligible additional power.

The theoretical best efficiency of a linear amplifier is 78%; however, that efficiency is only exhibited at peak output powers. Under normal operating levels (typical music reproduction levels), efficiency falls below 30%, whereas the MAX9741 still exhibits > 78% efficiency under the same conditions (Figure 1).

# Shutdown

A shutdown mode reduces power consumption and extends battery life. Driving SHDN low places the

device in low-power (0.2µA) shutdown mode. Connect SHDN to a logic-high for normal operation.

### **Click-and-Pop Suppression**

Comprehensive click-and-pop suppression eliminates audible transients on startup and shutdown. While in shutdown, the H-bridge is pulled to GND through  $320k\Omega$ . During startup, or power-up, the input amplifiers are muted and an internal loop sets the modulator bias voltages to the correct levels, preventing clicks and pops when the H-bridge is subsequently enabled. Following startup, a soft-start function gradually unmutes the input amplifiers. The value of the soft-start capacitor has an impact on the click/pop levels. For optimum performance, CSS should be 470nF with a voltage rating of at least 7V.

### **Mute Function**

The MAX9741 features a clickless/popless mute mode. When the device is muted, the outputs stop switching, muting the speaker. Mute only affects the output stage and does not shut down the device. To mute the MAX9741, drive SS to GND by using a MOSFET pulldown (Figure 2). Driving SS to GND during the powerup/down or shutdown/turn-on cycle optimizes click-and-pop suppression.

Figure 1. MAX9741 Efficiency vs. Class AB Efficiency

Figure 2. MAX9741 Mute Circuit

# **Internal Regulator**

The MAX9741 has an internal linear regulator, REG, used to power the internal analog circuitry. The voltage at REG is nominally 6V. Bypass REG to AGND with a 10nF capacitor, rated for at least 10V. REG is turned off in shutdown.

# **Applications Information**

# **Class D Amplifier Outputs**

Class D amplifiers differ from analog amplifiers such as Class AB in that their output waveform is composed of high-frequency pulses from ground to the supply rail. When viewed with an oscilloscope the audio signal will not be seen; instead, the high-frequency pulses dominate. To evaluate the output of a Class D amplifier requires taking the difference from the positive and negative outputs, then lowpass filtering the difference to recover the amplified audio signal.

# Ferrite Bead Output Filters

The MAX9741's low-EMI output switching method reduces the output filtering requirements when compared

to pure PWM Class D amplifiers. The outputs will contain both differential and common-mode noise at the switching frequency and its harmonics. In many applications, a simple ferrite bead filter (see the *Simplified Block Diagram*) will allow the amplifier to pass FCC EMI limits. Ferrite beads offer significant cost and size reductions when compared to conventional inductors. The ferrite bead type and capacitor value can be adjusted to tune the rejection to match the speaker cable length.

Actual EMI test results for the MAX9741 are shown in Figure 3. This shows the MAX9741, tested in a 10m anechoic EMC chamber. The MAX9741 test conditions were: SSM mode, 0.5m cables on each side, 16dB gain, 18V supply voltage, both channels playing pink noise at 4W per channel into  $8\Omega$  shielded speakers.

The graph of Figure 3 indicates peak readings. Actual quasi peak readings per EN55022B specification will be lower due to Maxim's proprietary SSM mode. Table 2 lists select values, indicating the peak reading, the quasi-peak reading, and the actual margin to EN55022B specification.

Figure 3. EMI Measurement of MAX9741 in 10m Anechoic Chamber

# Table 2. Peak and Quasi-Peak EMI Readings

| FREQUENCY<br>(MHz) | PRELIMINARY PEAK<br>READING (dBµV/m) | QUASI PEAK READING<br>(dBµV/m) | EN55022B LIMIT<br>(dBµV/m) | ACTUAL MARGIN<br>(dBµV/m) |

|--------------------|--------------------------------------|--------------------------------|----------------------------|---------------------------|

| 75.38              | 28.1                                 | 18.3                           | 30.0                       | 11.7                      |

| 78.57              | 28.0                                 | 21.9                           | 30.0                       | -8.1                      |

| 83.18              | 26.6                                 | 20.6                           | 30.0                       | -9.4                      |

Ferrite beads are available from many manufacturers. Table 3 lists some manufacturers who make ferrite beads and other products suitable for use with Class D amplifiers.

Although they offer a low cost and small size, ferrite bead filters slightly increase distortion and slightly reduce efficiency. If the audio performance of the ferrite bead filters does not meet the system requirements, then a full inductor/capacitor (LC) filter should be considered.

# Inductor/Capacitor Output Filters

Using a full inductor and capacitor (LC) output filter provides significant attenuation of the fundamental switching energy.

Select inductors rated for the expected RMS current load. For example, if using a Class D amplifier up to 10W into  $8\Omega$ , the inductor should be rated for 1.25A RMS or more. Furthermore, the inductor should maintain a constant inductance value across the expected current range. Inductors which change in value as a function of current will cause harmonic distortion.

The output capacitors can also affect audio performance. Ceramic capacitors are often selected for their size and cost advantage, but they cause distortion. If the application constraints dictate ceramic capacitors, selecting higher voltage rating and larger package size mitigates some of the shortcomings. Best performance is obtained with plastic film capacitors, but these are larger and more expensive.

# **Filterless Operation**

In some cases, a Class D amplifier can be used without an output filter. The intrinsic inductance of the loudspeaker stores energy from the high-speed PWM pulses,

Table 3. Filter Component Suppliers

|             | •                         |                                             |

|-------------|---------------------------|---------------------------------------------|

| SUPPLIER    | PRODUCT                   | WEBSITE                                     |

| Murata      | Ferrite beads, capacitors | www.murata.com                              |

| Taiyo Yuden | Ferrite beads, capacitors | www.t-yuden.com                             |

| TDK         | Ferrite beads, capacitors | www.tdk.co.jp/tetop01                       |

| Fairrite    | Ferrite beads             | www.fair-rite.com                           |

| Coilcraft   | Inductors                 | www.coilcraft.com                           |

| Sumida      | Inductors                 | www.sumida.com                              |

| Panasonic   | Inductors                 | www.panasonic.com/indu<br>strial/components |

converting these into power in the audible frequency range. Filterless operation requires the Class D amplifier to be very close to the speaker. Distances greater than a few centimeters must be evaluated for EMC compliance.

# **Gain Selection**

Table 4 shows the suggested gain settings to attain a maximum output power from a given peak input voltage and given load.

# **Output Offset**

Unlike a Class AB amplifier, the output offset voltage of Class D amplifiers does not noticeably increase quiescent current draw when a load is applied. This is due to the power conversion of the Class D amplifier. For example, an 8mVDC offset across an 8 $\Omega$  load results in 1mA extra current consumption in a Class AB device. In the Class D case, an 8mV offset into 8 $\Omega$  equates to an additional power drain of 8 $\mu$ W. Due to the high efficiency of the Class D amplifier, this represents an additional quiescent current draw of: 8 $\mu$ W / (V<sub>DD</sub> / 100 ×  $\eta$ ), which is in the order of a few microamps.

# **Input Amplifier**

# Differential Input

The MAX9741 features a differential input structure, making them compatible with many CODECs, and offering improved noise immunity over a single-ended input amplifier. In devices such as PCs, noisy digital signals can be picked up by the amplifier's input traces. The signals appear at the amplifiers' inputs as common-mode noise. A differential input amplifier amplifies the difference of the two inputs, any signal common to both inputs is canceled.

# **Table 4. Gain Settings**

| G1 | G2 | GAIN (dB) |

|----|----|-----------|

| 0  | 0  | 29.6      |

| 0  | 1  | 19.1      |

| 1  | 0  | 13        |

| 1  | 1  | 16        |

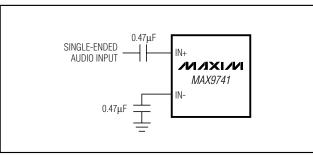

### Single-Ended Input

The MAX9741 can be configured as single-ended input amplifiers by capacitively coupling either input to GND and driving the other input (Figure 4).

# **Component Selection**

### Input Filter

An input capacitor,  $C_{IN}$ , in conjunction with the input impedance of the MAX9741, forms a highpass filter that removes the DC bias from an incoming signal. The AC-coupling capacitor allows the amplifier to bias the signal to an optimum DC level. Assuming zero-source impedance, the -3dB point of the highpass filter is given by:

$$f_{-3dB} = \frac{1}{2\pi R_{IN} C_{IN}}$$

Choose  $C_{IN}$  so  $f_{-3dB}$  is well below the lowest frequency of interest. Setting  $f_{-3dB}$  too high affects the low-frequency response of the amplifier. Use capacitors with dielectrics that have low-voltage coefficients, such as tantalum or aluminum electrolytic. Capacitors with highvoltage coefficients, such as ceramics, may result in increased distortion at low frequencies.

### **Charge-Pump Capacitor Selection**

Use capacitors with an ESR less than  $100m\Omega$  for optimum performance. Low-ESR ceramic capacitors minimize the output resistance of the charge pump. For best performance over the extended temperature range, select capacitors with an X7R dielectric.

### Flying Capacitor (C1)

The value of the flying capacitor (C1) affects the load regulation and output resistance of the charge pump. A C1 value that is too small degrades the device's ability to provide sufficient current drive. Increasing the value of C1 improves load regulation and reduces the charge-pump output resistance to an extent. Above 1 $\mu$ F, the on-resistance of the switches and the ESR of C1 and C2 dominate.

### Hold Capacitor (C2)

The output capacitor value and ESR directly affect the ripple at CHOLD. Increasing C2 reduces output ripple. Likewise, decreasing the ESR of C2 reduces both ripple and output resistance. Lower capacitance values can be used in systems with low maximum output power levels.

### **Sharing Input Sources**

In certain systems, a single audio source can be shared by multiple devices (speaker and headphone amplifiers).

Figure 4. Single-Ended Input

When sharing inputs, it is common to mute the unused device, rather than completely shutting it down, preventing the unused device inputs from distorting the input signal. Mute the MAX9741 by driving SS low through an open-drain output or MOSFET. Driving SS low turns off the Class D output stage, but does not affect the input bias levels of the MAX9741. Be aware that during normal operation, the voltage at SS can be up to 7V, depending on the MAX9741 supply.

### Supply Bypassing/Layout

**MAX9741**

Proper power-supply bypassing ensures low-distortion operation. For optimum performance, bypass V<sub>DD</sub> to PGND with a 0.1µF or greater capacitor as close to each V<sub>DD</sub> pin as possible. In some applications, a 0.1µF capacitor in parallel with a larger value, low-ESR ceramic or aluminum electrolytic capacitor provides good results. A low-impedance, high-current power-supply connection to V<sub>DD</sub> is assumed. Additional bulk capacitance should be added as required depending on the application and power-supply characteristics. AGND and PGND should be star connected to system ground. Refer to the MAX9741 Evaluation Kit for layout guidance.

# **Class D Amplifier Thermal Considerations**

Class D amplifiers provide much better efficiency and thermal performance than a comparable Class AB amplifier. However, the system's thermal performance must be considered with realistic expectations and consideration of many parameters. This application note examines Class D amplifiers using general examples to illustrate good design practices.

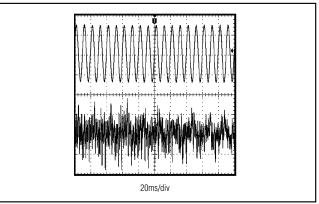

# Continuous Sine Wave vs. Music

When a Class D amplifier is evaluated in the lab, often a continuous sine wave is used as the signal source. While this is convenient for measurement purposes, it represents a worst-case scenario for thermal loading on the amplifier. It is not uncommon for a Class D amplifier to enter thermal shutdown if driven near maximum output power with a continuous sine wave.

**MAX9741**

Audio content, both music and voice, has a much lower RMS value relative to its peak output power. Figure 5 shows a sine wave and an audio signal in the time domain. Both are measured for RMS value by the oscilloscope. Although the audio signal has a slightly higher peak value than the sine wave, its RMS value is almost half that of the sine wave. Therefore, while an audio signal may reach similar peaks as a continuous sine wave, the actual thermal impact on the Class D amplifier is highly reduced. If the thermal performance of a system is being evaluated, it is important to use actual audio signals instead of sine waves for testing. If sine waves must be used, the thermal performance will be less than the system's actual capability.

# **PC Board Thermal Considerations**

The exposed pad is the primary route of heat away from the IC. With a bottom-side exposed pad, the PC board and its copper becomes the primary heatsink for the Class D amplifier. Solder the exposed pad to a large copper polygon. Add as much copper as possible from this polygon to any adjacent pin on the Class D amplifier as well as to any adjacent components, provided these connections are at the same potential. These copper paths must be as wide as possible. Each of these paths contributes to the overall thermal capabilities of the system.

The copper polygon to which the exposed pad is attached should have multiple vias to the opposite side of the PC board, where they connect to another copper polygon. Make this polygon as large as possible within the system's constraints for signal routing.

Additional improvements are possible if all the traces from the device are made as wide as possible. Although the IC pins are not the primary thermal path out of the package, they do provide a small amount. The total improvement would not exceed approximately 10%, but it could make the difference between acceptable performance and thermal problems.

With a bottomside exposed pad, the lowest resistance thermal path is on the bottom of the PC board. The topside of the IC is not a significant thermal path for the device.

# **Thermal Calculations**

The die temperature of a Class D amplifier can be estimated with some basic calculations. For example, the die temperature is calculated for the below conditions:

• T<sub>A</sub> = +40°C

- POUT = 10W (5W + 5W)

- Efficiency  $(\eta) = 78\%$

- $\theta_{JA} = 21^{\circ}C/W$

Figure 5. RMS Comparison of Sine Wave vs. Audio Signal

F

First, the Class D amplifier's power dissipation must be calculated.

$$P_{\text{DISS}} = \frac{P_{\text{OUT}}}{\eta} - P_{\text{OUT}} = \frac{10W}{78\%} - 10W = 2.82W$$

Then the power dissipation is used to calculate the die temperature,  $T_C$ , as follows:

$$T_{C} = T_{A} + P_{DISS} \times \theta_{JA} = 40^{\circ}C + 2.82W \times 21^{\circ}C/W = 99.2^{\circ}C$$

# Load Impedance

The on-resistance of the MOSFET output stage in Class D amplifiers affects both the efficiency and the peakcurrent capability. Reducing the peak current into the load reduces the I<sup>2</sup>R losses in the MOSFETs, increasing efficiency. To keep the peak currents lower, choose the highest impedance speaker which can still deliver the desired output power within the voltage swing limits of the Class D amplifier and its supply voltage.

# **Optimize MAX9741 Efficiency with Load Impedance and Supply Voltage**

To optimize efficiency, load the output stage with  $12\Omega$  to  $16\Omega$  speakers. The MAX9741 exhibits highest efficiency performance when driving higher load impedance (see the *Typical Operating Characteristics*). If a  $12\Omega$  to  $16\Omega$  load is not available, select a lower supply voltage when driving  $4\Omega$  to  $10\Omega$  loads.

For best performance, choose a speaker impedance to complement the required output power and the available supply voltage. For example, if operating from a 24V supply and a peak output of 10W per channel is desired, using 12 $\Omega$  speakers provides the best audio performance and power efficiency. The amplifier outputs are short-circuit protected at approximately 2A. Selecting a higher impedance driver helps prevent exceeding the current limit.

# **Application Circuit**

**MAX9741**

Pin Configuration TOP VIEW N.C. PgND PGND N.C. VDD N.C. N.C. N.C. N.C. N.C. SFS2 FS3 G2 G1 42 41 40 39 38 37 36 35 34 33 32 31 30 29 N.C. 28 N.C. 43 27 INR+ N.C. 44 26 INR-OUTR-45 OUTR-25 N.C. 46 24 REG OUTR+ 47 OUTR+ 48 23 N.C. 22 M NXI M AGND N.C. 49 MAX9741 21 N.C. 50 N.C. OUTL-20 SS 51 19 N.C. OUTL-52 OUTL+ 53 18 SHDN 17 INL+ OUTL+ 54 16 INL-55 N.C. 15 N.C. N.C. 56 1 2 3 4 5 6 7 8 9 10 11 12 13 14 CHOLD PGND N.C. VDD C1P N.C. PGND VDD N.C. C1N N.C. N.C. N.C. THIN QFN 8mm x 8mm

**Chip Information**

TRANSISTOR COUNT: 4630 PROCESS: BICMOS

**MAX9741**

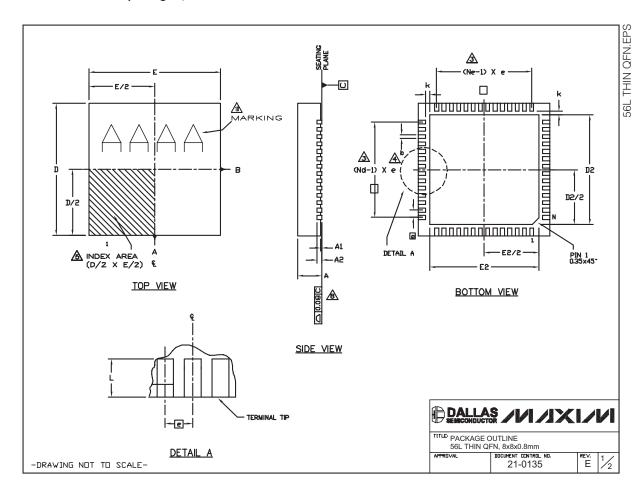

# Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

# **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

- 1. DIE THICKNESS ALLOWABLE IS 0.225mm MAXIMUM (0.009 INCHES MAXIMUM). 2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. - 1994.

- $\overline{3}$  n is the number of terminals.

- Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION & No IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

- 4. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

- ✓5. THE PIN #1 IDENTIFIER MUST BE LOCATED ON THE TOP SURFACE OF THE PACKAGE WITHIN HATCHED AREA AS SHOWN. EITHER AN INDENTATION MARK OR INK/LASER MARK IS ACCEPTABLE.

- 6. ALL DIMENSIONS ARE IN MILLIMETERS.

- 7. PACKAGE WARPAGE MAX 0.01mm

- APPLIES TO EXPOSED PAD AND TERMINALS. EXCLUDES INTERNAL DIMENSION OF EXPOSED PAD.

- 9. MEETS JEDEC MO220.

- 10 MARKING IS FOR PACKAG ORIENTATION REFERENCE ONLY

- 11. NUMBER OF LEADS ARE FOR REFERENCE ONLY

|         |      | EXF  | POSED I | PAD VA | RIATION | 1    |        |                |

|---------|------|------|---------|--------|---------|------|--------|----------------|

| PKG.    |      | D2   |         |        | E2      |      | JEDEC  | DEWN<br>Sciner |

| CODE    | MIN. | NOM. | MAX.    | MIN.   | NOM.    | MAX. | JEDEC  | ALLOVED        |

| T5688-2 | 6.50 | 6.65 | 6.70    | 6.50   | 6.65    | 6.70 | WLLD-5 | YES            |

| T5688-3 | 6,50 | 6.65 | 6.70    | 6.50   | 6.65    | 6.70 | WLLD-5 | NO             |

| -0 <sup>66,4</sup> <sup>69</sup> | 56L 8x8  |                |      |                 |  |  |  |

|----------------------------------|----------|----------------|------|-----------------|--|--|--|

| ٩ [                              | MIN.     | MIN. NOM. MAX. |      |                 |  |  |  |

| A                                | 0.70     | 0.75           | 0.80 | No <sub>7</sub> |  |  |  |

| b                                | 0.20     | 0.25           | 0.30 | 4               |  |  |  |

| D                                | 7.90     | 8.00           | 8.10 |                 |  |  |  |

| E                                | 7.90     | 8.00           | 8.10 |                 |  |  |  |

| e                                | 0.50 BSC |                |      |                 |  |  |  |

| N                                |          | 56             |      |                 |  |  |  |

| Nd                               |          | 14             |      | 3               |  |  |  |

| Ne                               |          | 14             |      | 3               |  |  |  |

| L                                | 0.30     | 0.40           | 0.50 |                 |  |  |  |

| A1                               | 0.00     | 0.02           | 0.05 |                 |  |  |  |

| A2                               | 0.20 REF |                |      |                 |  |  |  |

| k                                | 0.25     |                |      |                 |  |  |  |

DOCUMENT CONTROL NO

21-0135

E

TITLE PACKAGE OUTLINE 56L THIN QFN, 8x8x0.8mm

APPROVAL

| -DRAWING | ΝΠΤ | ΤП | SCALE- |  |

|----------|-----|----|--------|--|

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2006 Maxim Integrated Products Printed USA **MAXIM** is a registered trademark of Maxim Integrated Products, Inc.