Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

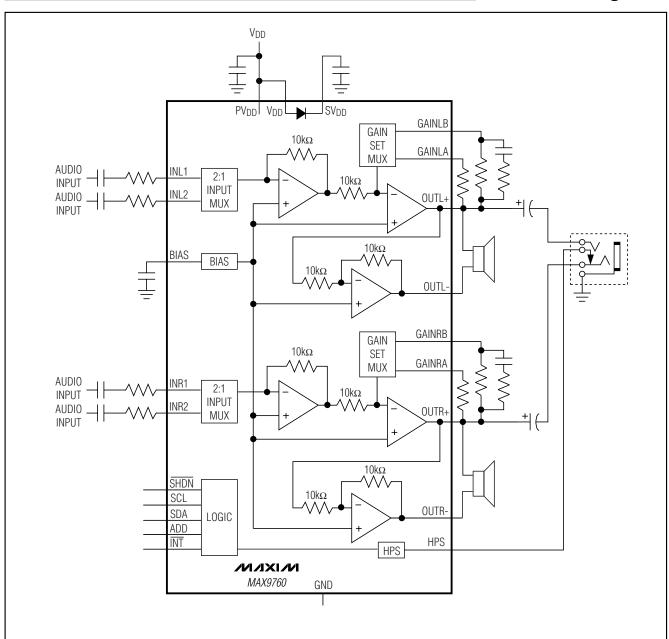

### **General Description**

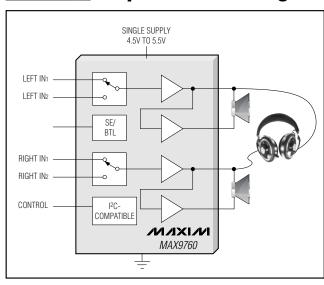

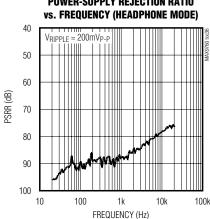

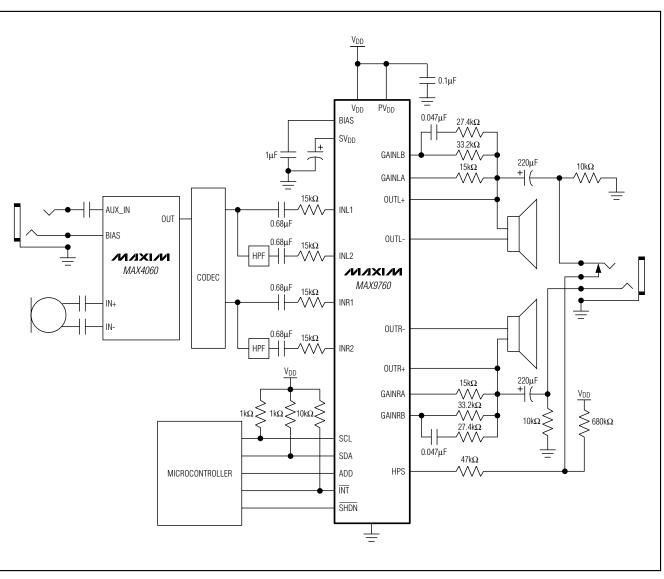

The MAX9760-MAX9763 family combines a stereo or mono 3W bridge-tied load (BTL) audio power amplifier, stereo single-ended headphone amplifier, headphone sensing, and a 2:1 input multiplexer all in a tiny 28-pin thin QFN package. These devices operate from a single 4.5V to 5.5V supply and feature an industry-leading 100dB PSRR, allowing these devices to operate from noisy supplies without the addition of a linear regulator. An ultra-low 0.002% THD+N ensures clean, low-distortion amplification of the audio signal. Click-and-pop suppression eliminates audible transients on power and shutdown cycles. Power-saving features include low 4mV Vos (minimizes DC current drain through the speakers), low 13mA supply current, and a 10µA shutdown mode. A MUTE function allows the outputs to be quickly enabled or disabled.

A headphone sense input detects the presence of a headphone jack and automatically configures the amplifiers for either speaker or headphone mode. In speaker mode, the amplifiers can deliver up to 3W of continuous average power into a  $3\Omega$  load. In headphone mode, the amplifier can deliver up to 200mW of continuous average power into a  $16\Omega$  load. The gain of the amplifiers is externally set, allowing maximum flexibility in optimizing output levels for a given load. The amplifiers also feature a 2:1 input multiplexer, allowing multiple audio sources to be selected. The multiplexer can also be used to compensate for limitations in the frequency response of the loud speakers by selecting an external equalizer network. The various functions are controlled by either an I<sup>2</sup>C-compatible or simple parallel control interface.

The MAX9760-MAX9763 are available in either a thermally efficient 28-pin thin QFN package (5mm × 5mm × 0.8mm) or a TSSOP-EP package. All devices have thermal overload protection (OVP) and are specified over the extended -40°C to +85°C temperature range.

#### **Applications**

Notebooks Portable DVD Players Tablet PCs PC Audio Peripherals Camcorders

Pin Configurations and Functional Diagrams appear at end of data sheet.

#### **Features**

- ♦ Industry-Leading, Ultra-High 100dB PSRR

- ♦ PC99/01 Compliant

- **♦ 3W BTL Stereo Speaker Amplifier**

- ♦ 200mW Stereo Headphone Amplifier

- ♦ Low 0.002% THD+N

- ♦ Click-and-Pop Suppression

- **♦ ESD-Protected Outputs**

- ♦ Low Quiescent Current: 13mA

- ♦ Low-Power Shutdown Mode: 10µA

- **♦ MUTE Function**

- ♦ Headphone Sense Input

- ♦ Stereo 2:1 Input Multiplexer

- ♦ Optional 2-Wire, I<sup>2</sup>C-Compatible or Parallel Interface

- ♦ Tiny 28-Pin Thin QFN (5mm  $\times$  5mm  $\times$  0.8mm) and **TSSOP-EP Packages**

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE     |

|------------|----------------|-----------------|

| MAX9760ETI | -40°C to +85°C | 28 Thin QFN-EP* |

| MAX9760EUI | -40°C to +85°C | 28 TSSOP-EP*    |

\*EP = Exposed paddle.

Ordering Information continued at end of data sheet.

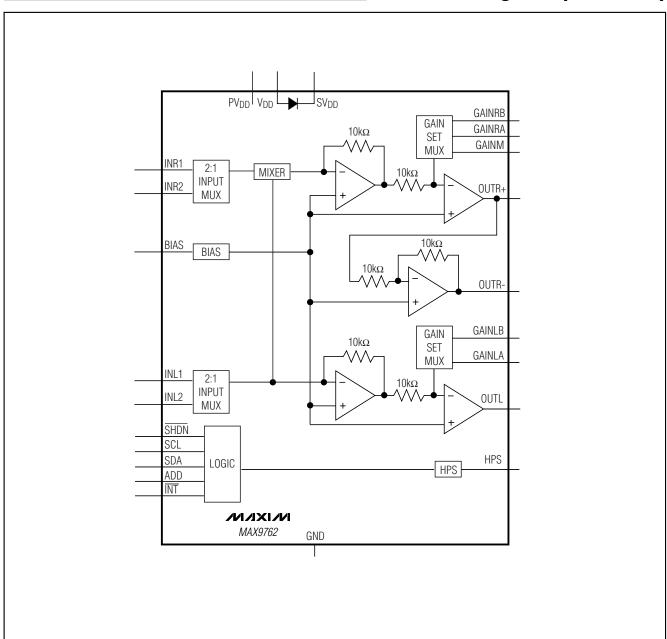

## Simplified Block Diagram

MIXIM

Maxim Integrated Products 1

## **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND                | +6V                       |

|---------------------------------------|---------------------------|

| SV <sub>DD</sub> to GND               |                           |

| SV <sub>DD</sub> to V <sub>DD</sub>   | 0.3V                      |

| PV <sub>DD</sub> to V <sub>DD</sub>   | ±0.3V                     |

| PGND to GND                           | ±0.3V                     |

| All Other Pins to GND                 | 0.3V to $(V_{DD} + 0.3V)$ |

| Continuous Input Current (into any pi | n except power-supply     |

| and output pins)                      | ±20mA                     |

Continuous Power Dissipation

28-Pin Thin QFN (derate 20.8mW/°C above +70°C) ....1667mW

28-Pin TSSOP-EP (derate 23.8mW/°C above +70°C) ...1905mW

Operating Temperature Range .....-40°C to +85°C

Storage Temperature Range ....-65°C to +150°C

Junction Temperature ....+150°C

Lead Temperature (soldering, 10s) ....+300°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = PV_{DD} = 5.0V, \ GND = PGND = 0V, \ \overline{SHDN} = 5V, \ C_{BIAS} = 1\mu F, \ R_{IN} = R_F = 15k\Omega, \ R_L = \infty. \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise noted. \ Typical values are at T_A = +25°C.) \ (Note 1)$

| PARAMETER                               | SYMBOL                            | CC                              | ONDITIONS                                             | MIN | TYP   | MAX | UNITS |  |

|-----------------------------------------|-----------------------------------|---------------------------------|-------------------------------------------------------|-----|-------|-----|-------|--|

| Supply Voltage Range                    | V <sub>DD</sub> /PV <sub>DD</sub> | Inferred from PSRI              | R test                                                | 4.5 |       | 5.5 | V     |  |

|                                         |                                   | BTL mode,                       | MAX9760/MAX9761                                       |     | 13    | 32  |       |  |

| Quiescent Supply Current (IVDD + IPVDD) | I <sub>DD</sub>                   | HPS = 0V                        | MAX9762/MAX9763                                       |     | 7     | 18  | mA    |  |

| (1400 + 15400)                          |                                   | Single-ended mod                | le, HPS = V <sub>DD</sub>                             |     | 7     | 18  |       |  |

| Shutdown Current                        | ISHDN                             | SHDN = GND                      |                                                       |     | 10    | 50  | μΑ    |  |

| Switching Time                          | tsw                               | Gain or input switch            | ching                                                 |     | 10    |     | μs    |  |

| Turn-On Time                            | 4                                 | C <sub>BIAS</sub> = 1µF         |                                                       |     | 300   |     |       |  |

| rum-On Time                             | ton                               | C <sub>BIAS</sub> = 0.1µF       |                                                       |     | 30    |     | ms    |  |

| Thermal Shutdown Threshold              |                                   |                                 |                                                       |     | 160   |     | °C    |  |

| Thermal Shutdown Hysteresis             |                                   |                                 |                                                       |     | 15    |     | °C    |  |

| OUTPUT AMPLIFIERS (SPEAKE               | R MODE, H                         | PS = GND)                       |                                                       |     |       |     |       |  |

| Output Offset Voltage                   | Vos                               | OUT_+ - OUT, A                  | v = 1V/V                                              |     | ±4    | ±32 | mV    |  |

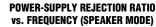

|                                         |                                   |                                 | $V_{DD} = 4.5V \text{ to } 5.5V$                      | 75  | 100   |     |       |  |

| Power-Supply Rejection Ratio            | PSRR                              | (Note 2)                        | f = 1kHz, V <sub>RIPPLE</sub> = 200mV <sub>P-P</sub>  |     | 82    |     | dB    |  |

|                                         |                                   |                                 | f = 20kHz, V <sub>RIPPLE</sub> = 200mV <sub>P-P</sub> |     | 70    |     |       |  |

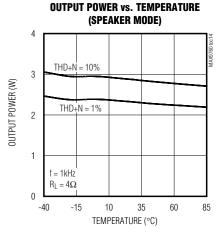

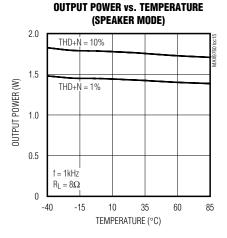

|                                         |                                   | fin = 1kHz,                     | $R_L = 8\Omega$                                       | 1   | 1.4   |     |       |  |

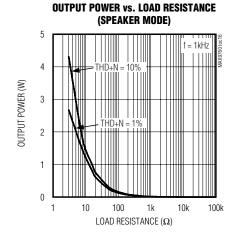

| Output Power                            | Pout                              | THD+N < 1%,                     | $R_L = 4\Omega$                                       |     | 2.6   |     | W     |  |

|                                         |                                   | $T_A = +25^{\circ}C$            | $R_L = 3\Omega$                                       |     | 3     |     | 1     |  |

| Total Harmonic Distortion Plus          | TUD N                             | f <sub>IN</sub> = 1kHz, BW =    | $P_{OUT} = 1W, R_L = 8\Omega$                         |     | 0.005 |     | 0/    |  |

| Noise                                   | THD+N                             | 22Hz to 22kHz                   | $P_{OUT} = 2W, R_L = 4\Omega$                         |     | 0.01  |     | %     |  |

| Signal-to-Noise Ratio                   | SNR                               | $R_L = 8\Omega$ , $P_{OUT} = 1$ | IW, BW = 22Hz to 22kHz                                |     | 95    |     | dB    |  |

| Slew Rate                               | SR                                |                                 |                                                       |     | 1.6   |     | V/µs  |  |

| Maximum Capacitive Load Drive           | CL                                | No sustained oscil              | lations                                               |     | 1     |     | nF    |  |

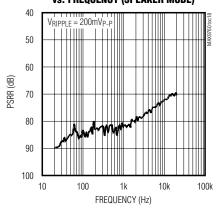

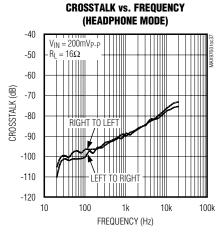

| Crosstalk                               |                                   | f <sub>IN</sub> = 10kHz         |                                                       |     | 73    |     | dB    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = PV_{DD} = 5.0V, GND = PGND = 0V, \overline{SHDN} = 5V, C_{BIAS} = 1\mu F, R_{IN} = R_F = 15k\Omega, R_L = \infty. T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                        | SYMBOL            | CONE                                                 | DITIONS                                               | MIN                      | TYP   | MAX                      | UNITS |  |  |

|----------------------------------|-------------------|------------------------------------------------------|-------------------------------------------------------|--------------------------|-------|--------------------------|-------|--|--|

| <b>OUTPUT AMPLIFIERS (HEADPH</b> | ONE MODE          | , HPS = V <sub>DD</sub> )                            |                                                       |                          |       |                          |       |  |  |

|                                  |                   |                                                      | $V_{DD} = 4.5V \text{ to } 5.5V$                      | 75                       | 106   |                          |       |  |  |

| Power-Supply Rejection Ratio     | PSRR              | (Note 2)                                             | f = 1kHz, V <sub>RIPPLE</sub> = 200mV <sub>P-P</sub>  |                          | 88    |                          | dB    |  |  |

|                                  |                   |                                                      | f = 20kHz, V <sub>RIPPLE</sub> = 200mV <sub>P-P</sub> |                          | 76    |                          |       |  |  |

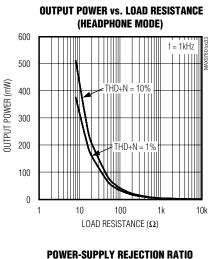

| Output Power                     | Dour              | f <sub>IN</sub> = 1kHz, THD+N <                      | $R_L = 32\Omega$                                      |                          | 88    |                          | m\\\  |  |  |

| Output Power                     | Pout              | 1%, T <sub>A</sub> = +25°C                           | $R_L = 16\Omega$                                      | 120                      | 200   |                          | mW    |  |  |

| Total Harmonic Distortion Plus   | TUD 11            | f <sub>IN</sub> = 1kHz, BW = 22Hz to 22kHz           | $P_{OUT} = 60$ mW, $R_L = 32\Omega$                   |                          | 0.002 |                          |       |  |  |

| Noise                            | THD+N             |                                                      | $P_{OUT} = 125$ mW,<br>$R_L = 16\Omega$               |                          | 0.002 |                          | %     |  |  |

| Signal-to-Noise Ratio            | SNR               | $R_L = 32\Omega$ , BW = 22Hz<br>$V_{OUT} = 1V_{RMS}$ |                                                       | 92                       |       | dB                       |       |  |  |

| Slew Rate                        | SR                |                                                      |                                                       |                          | 1.8   |                          | V/µs  |  |  |

| Maximum Capacitive Load Drive    | CL                | No sustained oscillation                             | ons                                                   |                          | 2     |                          | nF    |  |  |

| Crosstalk                        |                   | $f_{IN} = 10kHz$                                     |                                                       |                          | 78    |                          | dB    |  |  |

| STANDBY SUPPLY (SVDD) (Note      | 3)                |                                                      |                                                       |                          |       |                          |       |  |  |

| SV <sub>DD</sub> Current         | Isvdd             | $V_{BIAS} = 1.25V, V_{DD} =$                         |                                                       | 425                      | 750   |                          |       |  |  |

| 3VDD Garrent                     | ממאפי             | $V_{BIAS} = 2.5V, V_{DD} = 5$                        |                                                       |                          | 15    | μΑ                       |       |  |  |

| BIAS VOLTAGE (BIAS)              |                   |                                                      |                                                       |                          |       |                          |       |  |  |

| BIAS Voltage                     | V <sub>BIAS</sub> |                                                      |                                                       | 2.35                     | 2.5   | 2.65                     | V     |  |  |

| Output Resistance                | R <sub>BIAS</sub> |                                                      |                                                       |                          | 50    |                          | kΩ    |  |  |

| DIGITAL INPUTS (MUTE, SHDN,      | HPS_EN, G         | AINĀ/B, IN <del>1</del> /2)                          |                                                       |                          |       |                          |       |  |  |

| Input Voltage High               | $V_{IH}$          |                                                      |                                                       | 2                        |       |                          | V     |  |  |

| Input Voltage Low                | $V_{IL}$          |                                                      |                                                       |                          |       | 0.8                      | V     |  |  |

| Input Leakage Current            | I <sub>IN</sub>   |                                                      |                                                       |                          |       | ±1                       | μΑ    |  |  |

| HEADPHONE SENSE INPUT (HPS)      |                   |                                                      |                                                       |                          |       |                          |       |  |  |

| Input Voltage High               | VIH               |                                                      |                                                       | 0.9 x<br>V <sub>DD</sub> |       |                          | V     |  |  |

| Input Voltage Low                | VIL               |                                                      |                                                       |                          |       | 0.7 x<br>V <sub>DD</sub> | V     |  |  |

| Input Leakage Current            | I <sub>IN</sub>   |                                                      |                                                       |                          |       | ±1                       | μΑ    |  |  |

|                                  |                   | •                                                    |                                                       | •                        |       |                          | •     |  |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = PV_{DD} = 5.0V, GND = PGND = 0V, \overline{SHDN} = 5V, C_{BIAS} = 1\mu F, R_{IN} = R_F = 15k\Omega, R_L = \infty. T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                                      | SYMBOL          | CONDITIONS            | MIN                       | TYP | MAX | UNITS |  |  |  |

|----------------------------------------------------------------|-----------------|-----------------------|---------------------------|-----|-----|-------|--|--|--|

| 2-WIRE SERIAL INTERFACE (SCL, SDA, ADD, INT) (MAX9760/MAX9762) |                 |                       |                           |     |     |       |  |  |  |

| Input Voltage High                                             | VIH             |                       | 2.6                       |     |     | V     |  |  |  |

| Input Voltage Low                                              | VIL             |                       |                           |     | 0.8 | V     |  |  |  |

| Input Hysteresis                                               |                 |                       |                           | 0.2 |     | V     |  |  |  |

| Input High Leakage Current                                     | l <sub>IH</sub> | $V_{IN} = 5V$         |                           |     | ±1  | μΑ    |  |  |  |

| Input Low Leakage Current                                      | IIL             | $V_{IN} = 0V$         |                           |     | ±1  | μΑ    |  |  |  |

| Input Capacitance                                              | CIN             |                       |                           | 10  |     | рF    |  |  |  |

| Output Voltage Low                                             | V <sub>OL</sub> | I <sub>OL</sub> = 3mA |                           |     | 0.4 | V     |  |  |  |

| Output Current High                                            | Іон             | V <sub>OH</sub> = 5V  |                           |     | 1   | μΑ    |  |  |  |

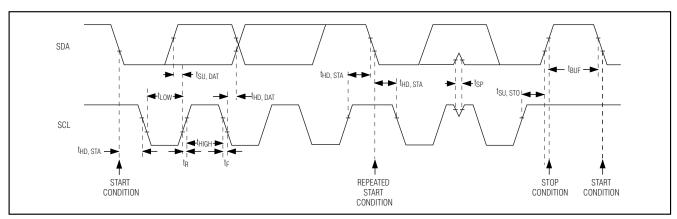

| TIMING CHARACTERISTICS (MAX9760/MAX9762)                       |                 |                       |                           |     |     |       |  |  |  |

| Serial Clock Frequency                                         | fscl            |                       |                           |     | 400 | kHz   |  |  |  |

| Bus Free Time Between STOP and START Conditions                | tBUF            |                       | 1.3                       |     |     | μs    |  |  |  |

| START Condition Hold Time                                      | thd:STA         |                       | 0.6                       |     |     | μs    |  |  |  |

| START Condition Setup Time                                     | tsu:sta         |                       | 0.6                       |     |     | μs    |  |  |  |

| Clock Period Low                                               | tLOW            |                       | 1.3                       |     |     | μs    |  |  |  |

| Clock Period High                                              | tHIGH           |                       | 0.6                       |     |     | μs    |  |  |  |

| Data Setup Time                                                | tsu:dat         |                       | 100                       |     |     | ns    |  |  |  |

| Data Hold Time                                                 | thd:dat         | (Note 4)              | 0                         |     | 0.9 | μs    |  |  |  |

| Receive SCL/SDA Rise Time                                      | t <sub>r</sub>  | (Note 5)              | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |  |  |  |

| Receive SCL/SDA Fall Time                                      | t <sub>f</sub>  | (Note 5)              | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |  |  |  |

| Transmit SDA Fall Time                                         | t <sub>f</sub>  | (Note 5)              | 20 +<br>0.1C <sub>B</sub> | _   | 250 | ns    |  |  |  |

| Pulse Width of Suppressed<br>Spike                             | tsp             | (Note 6)              |                           | 50  |     | ns    |  |  |  |

- Note 1: All devices are 100% production tested at +25°C. All temperature limits are guaranteed by design.

- Note 2: PSRR is specified with the amplifier inputs connected to GND through RIN and CIN.

- **Note 3:** Refer to the SV<sub>DD</sub> section.

- Note 4: A master device must provide a hold time of at least 300ns for the SDA signal to bridge the undefined region of SCL's falling edge.

- Note 5:  $C_B$  = total capacitance of one of the bus lines in picofarads. Device tested with  $C_B$  = 400pF. 1k $\Omega$  pullup resistors connected from SDA/SCL to VDD.

- Note 6: Input filters on SDA, SCL, and ADD suppress noise spikes of less than 50ns.

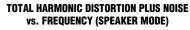

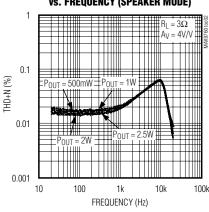

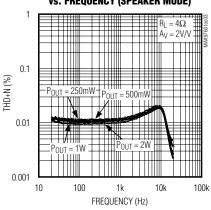

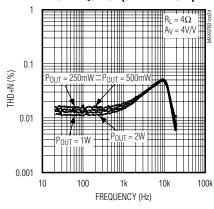

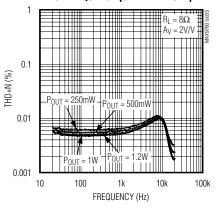

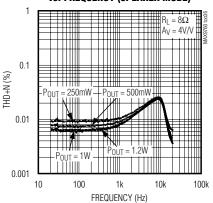

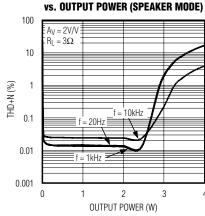

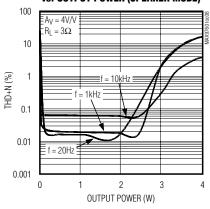

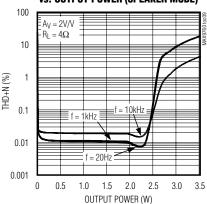

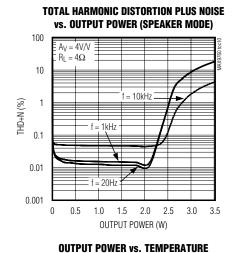

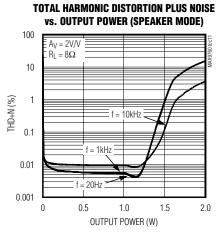

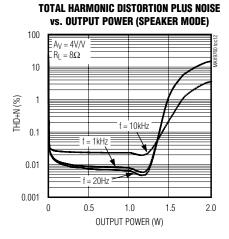

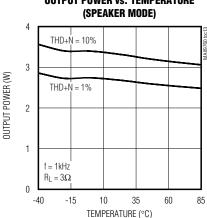

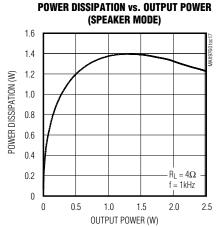

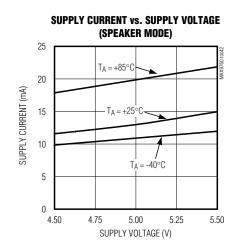

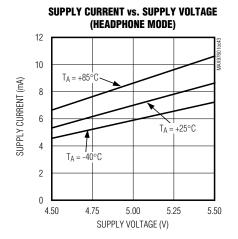

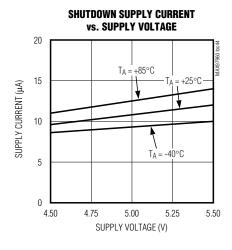

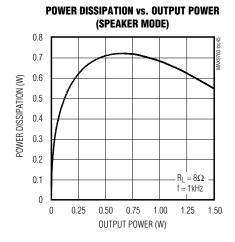

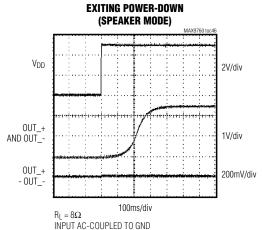

## **Typical Operating Characteristics**

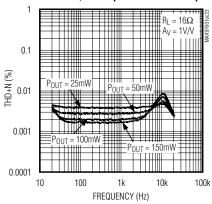

$(V_{DD} = PV_{DD} = 5V, T_A = +25^{\circ}C, unless otherwise noted.)$

TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency (Speaker Mode)

TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency (Speaker Mode)

TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency (Speaker Mode)

TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency (Speaker Mode)

TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency (Speaker Mode)

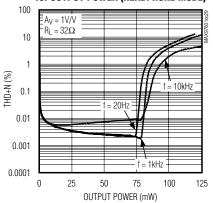

TOTAL HARMONIC DISTORTION PLUS NOISE

VS. OUTPUT POWER (SPEAKER MODE)

TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER (SPEAKER MODE)

TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER (SPEAKER MODE)

## \_Typical Operating Characteristics (continued)

$(V_{DD} = PV_{DD} = 5V, T_A = +25^{\circ}C, unless otherwise noted.)$

## **Typical Operating Characteristics (continued)**

$(V_{DD} = PV_{DD} = 5V, T_A = +25^{\circ}C, unless otherwise noted.)$

#### CROSSTALK vs. FREQUENCY (SPEAKER MODE)

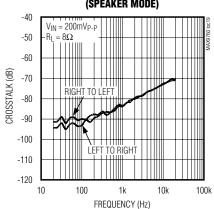

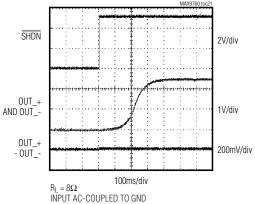

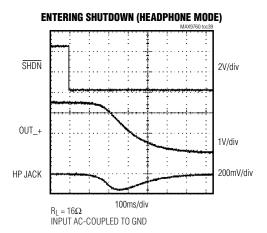

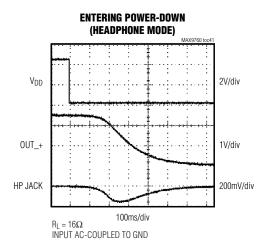

#### **ENTERING SHUTDOWN (SPEAKER MODE)**

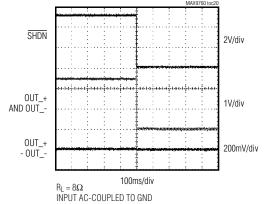

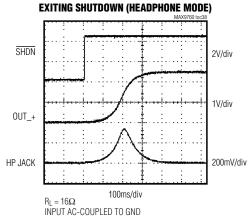

#### **EXITING SHUTDOWN (SPEAKER MODE)**

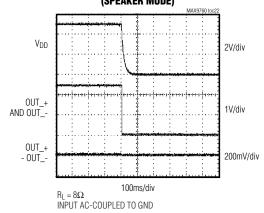

# ENTERING POWER-DOWN (SPEAKER MODE)

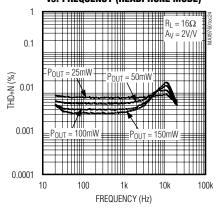

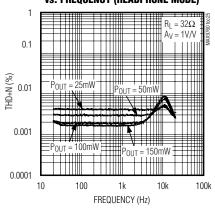

# TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency (Headphone Mode)

## Typical Operating Characteristics (continued)

$(V_{DD} = PV_{DD} = 5V, T_A = +25^{\circ}C, unless otherwise noted.)$

TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency (Headphone Mode)

TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency (Headphone Mode)

TOTAL HARMONIC DISTORTION PLUS NOISE vs. Frequency (Headphone Mode)

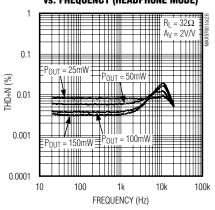

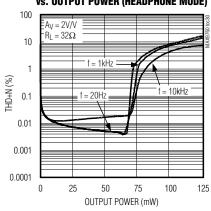

TOTAL HARMONIC DISTORTION PLUS NOISE vs. Output Power (Headphone Mode)

TOTAL HARMONIC DISTORTION PLUS NOISE vs. Output power (Headphone Mode)

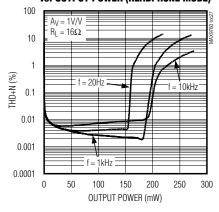

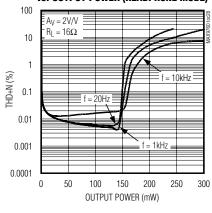

TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER (HEADPHONE MODE)

TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER (HEADPHONE MODE)

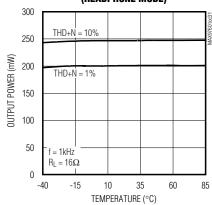

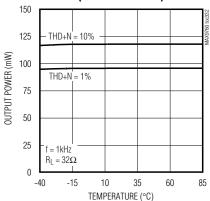

OUTPUT POWER vs. TEMPERATURE (HEADPHONE MODE)

OUTPUT POWER vs. TEMPERATURE (HEADPHONE MODE)

## **Typical Operating Characteristics (continued)**

$(V_{DD} = PV_{DD} = 5V, T_A = +25$ °C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

$(V_{DD} = PV_{DD} = 5V, T_A = +25$ °C, unless otherwise noted.)

## **Pin Description**

|                  |                  |                  | PI               | N            |           |                                                                                                                                                           |           |                                                                                                                                                                                                                                             |                                                                                                                                                    |

|------------------|------------------|------------------|------------------|--------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX              | 9760             | MAX              | (9761            | MA           | X9762     | MAX                                                                                                                                                       | 9763      | NAME                                                                                                                                                                                                                                        | FUNCTION                                                                                                                                           |

| QFN              | TSSOP            | QFN              | TSSOP            | QFN          | TSSOP     | QFN                                                                                                                                                       | TSSOP     |                                                                                                                                                                                                                                             |                                                                                                                                                    |

| 1                | 26               | _                | _                | 1            | 26        | _                                                                                                                                                         | _         | SDA                                                                                                                                                                                                                                         | Bidirectional Serial Data I/O                                                                                                                      |

| 2                | 27               | _                | _                | 2            | 27        | _                                                                                                                                                         | _         | ĪNT                                                                                                                                                                                                                                         | μC Interrupt Output                                                                                                                                |

| 3                | 28               | 3                | 28               | 3            | 28        | 3                                                                                                                                                         | 28        | $V_{DD}$                                                                                                                                                                                                                                    | Power Supply                                                                                                                                       |

| 4                | 1                | 4                | 1                | 4            | 1         | Standby Power Supply. Of to a standby power supply always on, or connect to through a Schottky dioded by pass with 220 µF capa GND. Short to VDD if clice |           | Standby Power Supply. Connect to a standby power supply that is always on, or connect to V <sub>DD</sub> through a Schottky diode and bypass with 220µF capacitor to GND. Short to V <sub>DD</sub> if clickless operation is not essential. |                                                                                                                                                    |

| 5                | 2                | 5                | 2                | 5            | 2         | 5                                                                                                                                                         | 2         | INL1                                                                                                                                                                                                                                        | Left-Channel Input 1                                                                                                                               |

| 6                | 3                | 6                | 3                | 6            | 3         | 6                                                                                                                                                         | 3         | INL2                                                                                                                                                                                                                                        | Left-Channel Input 2                                                                                                                               |

| 7                | 4                | 7                | 4                | 7            | 4         | 7                                                                                                                                                         | 4         | GAINLA                                                                                                                                                                                                                                      | Left-Channel Gain Set A                                                                                                                            |

| 8                | 5                | 8                | 5                | 8            | 5         | 8                                                                                                                                                         | 5         | GAINLB                                                                                                                                                                                                                                      | Left-Channel Gain Set B                                                                                                                            |

| 9, 13,<br>23, 27 | 6, 10,<br>20, 24 | 9, 13,<br>23, 27 | 6, 10, 20,<br>24 | 9, 23,<br>27 | 6, 20, 24 | 9, 23, 27                                                                                                                                                 | 6, 20, 24 | PGND                                                                                                                                                                                                                                        | Power Ground                                                                                                                                       |

| 10               | 7                | 10               | 7                | 10           | 7         | 10                                                                                                                                                        | 7         | OUTL+                                                                                                                                                                                                                                       | Left-Channel Bridged Amplifier Positive Output. OUTL+ also serves as the left-channel headphone amplifier output.                                  |

| 11, 25           | 8, 22            | 11, 25           | 8, 22            | 11, 25       | 8, 22     | 11, 25                                                                                                                                                    | 8, 22     | PV <sub>DD</sub>                                                                                                                                                                                                                            | Output Amplifier Power Supply                                                                                                                      |

| 12               | 9                | 12               | 9                |              | _         |                                                                                                                                                           |           | OUTL-                                                                                                                                                                                                                                       | Left-Channel Bridged Amplifier<br>Negative Output                                                                                                  |

| 14               | 11               | 14               | 11               | 14           | 11        | 14                                                                                                                                                        | 11        | SHDN                                                                                                                                                                                                                                        | Active-Low Shutdown. Connect SHDN to V <sub>DD</sub> for normal operation.                                                                         |

| 15               | 12               | _                |                  | 15           | 12        | _                                                                                                                                                         |           | ADD                                                                                                                                                                                                                                         | Address Select. A logic high sets the address LSB to 1, a logic low sets the address LSB to zero.                                                  |

| 16               | 13               | 16               | 13               | 16           | 13        | 16                                                                                                                                                        | 13        | HPS                                                                                                                                                                                                                                         | Headphone Sense Input. A logic high configures the device as a single-ended headphone amp. A logic low configures the device as a BTL speaker amp. |

| 17               | 14               | 17               | 14               | 17           | 14        | 17                                                                                                                                                        | 14        | BIAS                                                                                                                                                                                                                                        | DC Bias Bypass. See BIAS Capacitor Selection section for capacitor selection. Connect CBIAS from BIAS to GND.                                      |

| 18               | 15               | 18               | 15               | 13           | 10        | 13                                                                                                                                                        | 10        | GND                                                                                                                                                                                                                                         | Ground                                                                                                                                             |

## Pin Description (continued)

|     |       |     | PI    | N   |       |     |       |         |                                                                                                                                         |  |

|-----|-------|-----|-------|-----|-------|-----|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX | (9760 | MAX | K9761 | MA  | X9762 | MAX | (9763 | NAME    | FUNCTION                                                                                                                                |  |

| QFN | TSSOP | QFN | TSSOP | QFN | TSSOP | QFN | TSSOP |         |                                                                                                                                         |  |

| 19  | 16    | 19  | 16    | 19  | 16    | 19  | 16    | INR1    | Right-Channel Input 1                                                                                                                   |  |

| 20  | 17    | 20  | 17    | 20  | 17    | 20  | 17    | INR2    | Right-Channel Input 2                                                                                                                   |  |

| 21  | 18    | 21  | 18    | 21  | 18    | 21  | 18    | GAINRA  | Right-Channel Gain Set A                                                                                                                |  |

| 22  | 19    | 22  | 19    | 22  | 19    | 22  | 19    | GAINRB  | Right-Channel Gain Set B                                                                                                                |  |

| 24  | 21    | 24  | 21    | 24  | 21    | 24  | 21    | OUTR+   | Right-Channel Bridged Amplifier<br>Positive Output. OUTR+ also<br>serves as the right-channel<br>headphone amplifier output.            |  |

| 26  | 23    | 26  | 23    | 26  | 23    | 26  | 23    | OUTR-   | Right-Channel Bridged Amplifier<br>Negative Output                                                                                      |  |

| 28  | 25    | _   | _     | 28  | 25    | _   | _     | SCL     | Serial Clock Line                                                                                                                       |  |

| _   |       | _   | _     | 12  | 9     | 12  | 9     | N.C.    | No Connection. Not internally connected.                                                                                                |  |

| _   | _     | _   | _     | 18  | 15    | 18  | 15    | GAINM   | Mono Gain Set                                                                                                                           |  |

| _   | _     | 1   | 26    | _   | _     | 1   | 26    | MUTE    | Active-High Mute Input                                                                                                                  |  |

| _   | _     | 2   | 27    | _   | _     | 2   | 27    | HPS_EN  | Headphone Enable. A logic high<br>enables HPS. A logic low disables<br>HPS and the device is always<br>configured as a BTL speaker amp. |  |

| _   | _     | 15  | 12    | _   | _     | 15  | 12    | GAINĀ/B | Gain Select. A logic low selects the gain set by GAIN_A. A logic high selects the gain set by GAIN_B.                                   |  |

| _   | _     | 28  | 25    | _   | _     | 28  | 25    | IN1/2   | Input Select. A logic low selects amplifier input 1. A logic high selects amplifier input 2.                                            |  |

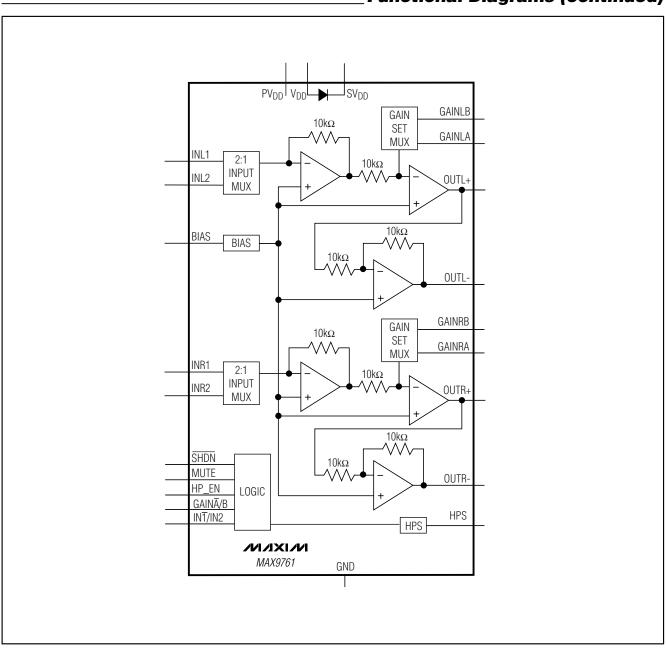

### **Detailed Description**

The MAX9760-MAX9763 feature 3W BTL speaker amplifiers, 200mW headphone amplifiers, input multiplexers, headphone sensing, and comprehensive clickand-pop suppression. The MAX9760/ MAX9761 are stereo BTL/headphone amplifiers. The MAX9762/MAX9763 are mono BTL/stereo headphone amplifiers. The MAX9760/MAX9762 are controlled through an I<sup>2</sup>C-compatible, 2-wire serial interface. The MAX9761/MAX9763 are controlled through five logic inputs: MUTE, SHDN, HPS\_EN, GAINA/B, and IN1/2 (see Selector Guide). The MAX9760-MAX9763 feature exceptional PSRR (100dB at 1kHz), allowing these

devices to operate from noisy digital supplies without the need for a linear regulator.

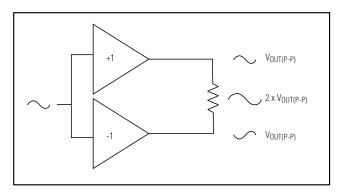

The speaker amplifiers use a BTL configuration. The signal path is composed of an input amplifier and an output amplifier. Resistor  $R_{\text{IN}}$  sets the input amplifier's gain, and resistor  $R_{\text{F}}$  sets the output amplifier's gain. The output of these two amplifiers serves as the input to a slave amplifier configured as an inverting unity-gain follower. This results in two outputs, identical in magnitude, but  $180^\circ$  out of phase. The overall gain of the speaker amplifiers is twice the product of the two amplifier gains (see Gain-Setting Resistor section). A feature of this architecture is that there is no phase inversion from input to output.

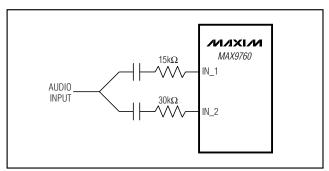

Figure 1. Using the Input Multiplexer for Gain Setting

When configured as a headphone (single-ended) amplifier, the slave amplifier is disabled, muting the speaker and the main amplifier drives the headphone. The MAX9760–MAX9763 can deliver 3W of continuous average power into a 3 $\Omega$  load with less than 1% THD+N in speaker mode, and 200mW of continuous average power into a 16 $\Omega$  load with less than 1% THD+N in headphone mode. These devices also feature thermal overload protection.

#### **Mono Mode**

The MAX9762/MAX9763 are 3W mono speaker amplifiers, 200mW stereo headphone amplifiers, and a mixer/attenuator (see the MAX9762/MAX9763 Functional Diagram). In speaker (mono) mode, the mixer/attenuator combines the two stereo inputs (INL\_ and INR\_) and attenuates the resultant signal by a factor of 2. This allows for full reproduction of a stereo signal through a single speaker, while maintaining optimum headroom. The resistor connected between GAINM and OUTR+, sets the gain of the devices in speaker mode (see the MAX9762 Functional Diagram). This allows the speaker amplifier to have a different gain and feedback network from the headphone amplifier.

#### BIAS

These devices operate from a single 5V supply, and feature an internally generated, power-supply independent, common-mode bias voltage of 2.5V referenced to GND. BIAS provides both click-and-pop suppression and sets the DC bias level for the audio outputs. BIAS is internally connected to the noninverting input of each speaker amplifier (see *Typical Application Circuit/Functional Diagram*). Choose the value of the bypass capacitor as described in the *BIAS Capacitor* section. No external load should be applied to BIAS. Any load lowers the BIAS voltage, affecting the overall performance of the device.

#### **Input Multiplexer**

Each amplifier features a 2:1 input multiplexer, allowing input selection between two stereo sources. Both multiplexers are controlled by bit 1 in the control register (MAX9760/MAX9762) or by the IN1/2 pin (MAX9761/MAX9763). A logic low selects input IN\_1 and a logic high selects input IN\_2.

The input multiplexer can also be used to further expand the number of gain options available from the MAX9760–MAX9763 family. Connecting the audio source to the device through two different input resistors (Figure 1) increases the number of gain options from two to four (MAX9760/MAX9761) and from three to six (MAX9762/MAX9763). Additionally, the input multiplexer allows a speaker equalization network to be switched into the speaker signal path. This is typically useful in optimizing acoustic response from speakers with small physical dimensions.

#### Headphone Sense Enable

The HPS pin is enabled by HPS\_EN (MAX9762/MAX9763) or the HPSD bit (MAX9760/MAX9761). HPSD or HPS\_EN determines whether the device is in automatic detection mode or fixed mode operation (see Tables 1a and 1b).

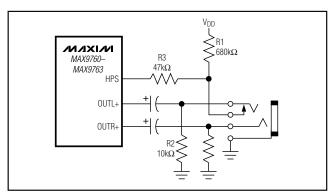

#### **Headphone Sense Input (HPS)**

A voltage on HPS less than  $0.7 \times V_{DD}$  sets the device to speaker mode. A voltage greater than  $0.9 \times V_{DD}$  disables the inverting bridge amplifier (OUT\_-), which mutes the speaker amplifier and sets the device into headphone mode.

For automatic headphone detection, connect HPS to the control pin of a 3-wire headphone jack as shown in Figure 2. With no headphone present, the resistive voltage-divider created by R1 and R2 sets the voltage on HPS to be less than  $0.7 \times V_{DD}$ , setting the device to speaker mode and the gain setting defaults to GAINA (MAX9760/MAX9762). When a headphone plug is inserted into the jack, the control pin is disconnected from the tip contact, and HPS is pulled to  $V_{DD}$  through R1, setting the device into headphone mode and the gain-setting defaults to GAINB (MAX9760/MAX9762) (see *Gain Select* section). Place a resistor in series with the control pin and HPS (R3) to prevent any audio signal from coupling into HPS when the device is in speaker mode.

#### Shutdown

The MAX9760-MAX9763 feature a 10µA, low-power shutdown mode that reduces quiescent current consumption and extends battery life. The drive amplifiers and bias circuitry are disabled, the amplifier outputs (OUT\_) go high impedance, and BIAS is driven to

GND. Driving SHDN low places the devices into shutdown mode, disables the interface, and resets the I<sup>2</sup>C registers to a default state. A logic high on SHDN enables the devices.

#### MAX9760/MAX9762 Software Shutdown

A logic high on bit 0 of the SHDN register places the MAX9760/MAX9762 in shutdown mode. A logic low enables the device. The digital section of the MAX9760/MAX9762 remains active when the device is shut down through the interface. All devices feature a logic low on the SHDN input.

#### MUTE

All devices feature a mute mode. When the device is muted, the input is disconnected from the amplifiers. MUTE does not shut down the device.

#### MAX9760/MAX9762 MUTE

The MAX9760/MAX9762 MUTE mode is selected by writing to the MUTE register (see the *Command Byte Definitions* section). The left and right channels can be independently muted.

#### **MAX9761/MAX9763 MUTE**

The MAX9761/MAX9763 feature an active-high MUTE input that mutes both channels.

#### **Click-and-Pop Suppression**

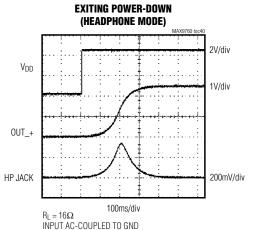

The MAX9760–MAX9763 feature Maxim's comprehensive click-and-pop suppression. During startup and shutdown, the common-mode bias voltage of the amplifiers is slowly ramped to and from the DC bias point using an S-shaped waveform. In headphone mode, this waveform shapes the frequency spectrum, minimizing the amount of audible components present at the headphone. In speaker mode, the BTL amplifiers start up in the same fashion as in headphone mode. When entering shutdown, both amplifier outputs ramp to GND quickly and simultaneously. The MAX9760–MAX9763 can also be connected to a standby power source that ensures that the device undergoes its full shutdown cycle even after power has been removed.

#### Standby Power Supply (SVDD)

The MAX9760–MAX9763 feature a system that provides clickless power-down when power is inadvertently removed from the device. SVDD is an **optional** secondary supply that powers the device through its shutdown cycle when VDD is removed. During this cycle, the amplifier output DC level slowly ramps to GND, ensuring clickless power-down. If clickless power-down is required, connect SVDD to either a secondary power supply that is always on, or connect a reservoir capacitor from SVDD to GND. SVDD does not need to be con-

Figure 2. HPS Configuration Circuit

## Table 1a. HPS Setting (MAX9760/MAX9761)

|      | INPU | гѕ      |      |                          |                          |  |

|------|------|---------|------|--------------------------|--------------------------|--|

| HPSD | HPS  | SPKR/HP | MODE | MAX9760<br>GAIN<br>PATH* | MAX9762<br>GAIN<br>PATH* |  |

| 0    | 0    | Χ       | BTL  | А                        | М                        |  |

| 0    | 1    | Χ       | SE   | В                        | В                        |  |

| 1    | X    | 0       | BTL  | A or B                   | M                        |  |

| 1    | X    | 1       | SE   | A or B                   | A or B                   |  |

#### \*Note:

A - GAINA path selected

B - GAINB path selected

M - GAINM path selected

A or B – Gain path selected by GAINAB control bit in register 02h

## Table 1b. HPS Setting (MAX9762/MAX9763)

| INPL  | JTS | MODE | MAX9761<br>GAIN PATH* | MAX9763<br>GAIN PATH* |  |

|-------|-----|------|-----------------------|-----------------------|--|

| HPSEN | HPS |      | GAIIT ATT             | GAINT ATT             |  |

| 0     | Χ   | BTL  | A or B                | М                     |  |

| 1     | 0   | BTL  | A or B                | М                     |  |

| 1     | 1   | SE   | A or B                | A or B                |  |

#### \*Note:

A or B – Gain path selected by external GAINAB M – GAINM path selected

nected to either a secondary power supply or reservoir capacitor for normal device operation. If click-and-pop suppression during power-down is not required, connect SV<sub>DD</sub> to V<sub>DD</sub> directly.

Figure 3. 2-Wire Serial Interface Timing Diagram

The clickless power-down cycle only occurs when the device is in headphone mode. The speaker mode is inherently clickless, the differential architecture cancels the DC shift across the speaker. The MAX9760–MAX9763 BTL outputs are pulled to GND quickly and simultaneously, resulting in no audible components. If the MAX9760–MAX9763 are only used as speaker amplifiers, then reservoir capacitors or secondary supplies are not necessary.

When using a reservoir capacitor, a 220µF capacitor provides optimum charge storage for the shutdown cycle for all conditions. If a smaller reservoir capacitor is desired, decrease the size of CBIAS. A smaller CBIAS causes the output DC level to decay at a faster rate, increasing the audible content at the speaker, but reducing the duration of the shutdown cycle.

#### **Digital Interface**

The MAX9760/MAX9762 feature an I<sup>2</sup>C/SMBus-compatible 2-wire serial interface consisting of a serial data line (SDA) and a serial clock line (SCL). SDA and SCL facilitate bidirectional communication between the MAX9760/MAX9762 and the master at clock rates up to 400kHz. Figure 3 shows the 2-wire interface timing diagram. The MAX9760/MAX9762 are transmit/receive slave-only devices, relying upon a master to generate a clock signal. The master (typically a microcontroller) initiates data transfer on the bus and generates SCL to permit that transfer.

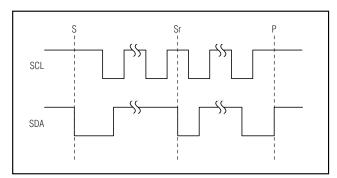

A master device communicates to the MAX9760/MAX9762 by transmitting the proper address followed by a command and/or data words. Each transmit sequence is framed by a START (S) or REPEATED START (S<sub>r</sub>) condition and a STOP (P) condition. Each word transmitted over the bus is 8 bits long and is always followed by an acknowledge clock pulse.

Figure 4. START/STOP Conditions

The MAX9760/MAX9762 SDA and SCL amplifiers are open-drain outputs requiring a pullup resistor (500 $\Omega$  or greater) to generate a logic high voltage. Series resistors in line with SDA and SCL are optional. These series resistors protect the input stages of the devices from high-voltage spikes on the bus lines, and minimize crosstalk and undershoot of the bus signals.

#### Bit Transfer

One data bit is transferred during each SCL clock cycle. The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high are control signals (see *START and STOP Conditions* section). SDA and SCL idle high when the I<sup>2</sup>C bus is not busy.

#### START and STOP Conditions

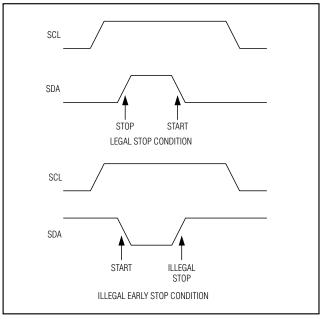

When the serial interface is inactive, SDA and SCL idle high. A master device initiates communication by issuing a START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA while SCL is high (Figure 4). A START condition from the master signals the beginning of a transmission to the MAX9760/

Figure 5. Early STOP Condition

Figure 6. Slave Address Byte Definition

MAX9762. The master terminates transmission by issuing the STOP condition, this frees the bus. If a REPEAT-ED START condition is generated instead of a STOP condition, the bus remains active.

#### Early STOP Conditions

The MAX9760/MAX9762 recognize a STOP condition at any point during the transmission except if a STOP condition occurs in the same high pulse as a START condition (Figure 5). This condition is not a legal I<sup>2</sup>C format, at least one clock pulse must separate any START and STOP conditions.

#### **REPEATED START Conditions**

A REPEATED START ( $S_r$ ) condition may indicate a change of data direction on the bus. Such a change occurs when a command word is required to initiate a read operation.  $S_r$  may also be used when the bus master is writing to several I<sup>2</sup>C devices and does not want to relinquish control of the bus. The MAX9760/MAX9762 serial interface supports continuous write operations with or without an  $S_r$  condition separating them. Continuous read operations require  $S_r$  conditions because of the change in direction of data flow.

#### Acknowledge Bit (ACK)

The acknowledge bit (ACK) is the ninth bit attached to any 8-bit data word. The receiving device always generates ACK. The MAX9760/MAX9762 generate an ACK when receiving an address or data by pulling SDA low during the night clock period. When transmitting data, the MAX9760/MAX9762 wait for the receiving device to generate an ACK. Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master should reattempt communication at a later time.

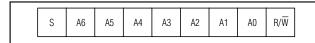

#### Slave Address

The bus master initiates communication with a slave device by issuing a START condition followed by a 7-bit slave address (Figure 6). When idle, the MAX9760/MAX9762 wait for a START condition followed by its slave address. The LSB of the address word is the Read/Write (R/W) bit. R/W indicates whether the master is writing to or reading from the MAX9760/MAX9762 (R/W = 0 selects the write condition, R/W = 1 selects the read condition). After receiving the proper address, the MAX9760/MAX9762 issue an ACK by pulling SDA low for one clock cycle.

The MAX9760/MAX9762 have a factory-/user-programmed address. Address bits A6–A2 are preset, while A0 and A1 is set by ADD. Connect ADD to either  $V_{DD}$ , GND, SCL, or SDA to change the last 2 bits of the slave address (Table 2).

#### Write Data Format

There are three registers that configure the MAX9760/MAX9762: the MUTE register, SHDN register, and control register. In write data mode ( $R/\overline{W}=0$ ), the register address and data byte follow the device address (Figure 7).

#### **MUTE Register**

The MUTE register (01hex) is a read/write register that sets the MUTE status of the device. Bit 3 (MUTEL) of the MUTE register controls the left channel, bit 4 (MUTER) controls the right channel. A logic high mutes the respective channel, a logic low brings the channel out of mute.

#### SHDN Register

The SHDN register (02hex) is a read/write register that controls the power-up state of the device. A logic high in bit 0 of the SHDN register shuts down the device; a logic low turns on the device. A logic high is required in bits 2 to 7 to reset all registers to their default settings.

| S      | ADDRESS                                   | WR     | ACK    | COMMAND                                           | ACK   | DATA   | ACK     | Р |

|--------|-------------------------------------------|--------|--------|---------------------------------------------------|-------|--------|---------|---|

| 7 BITS |                                           | 8 BITS | 8 BITS |                                                   |       | 1      |         |   |

|        | I <sup>2</sup> C SLAVE ADD<br>SELECTS DEV |        |        | REGISTER ADDRI<br>SELECTS REGISTER<br>WRITTEN TO. | TO BE | REGIST | ER DATA |   |

| S | ADDRESS                                   | WR | ACK | COMMAND                                        | ACK | S | ADDRESS                                    | WR | ACK | DATA                        | Р |

|---|-------------------------------------------|----|-----|------------------------------------------------|-----|---|--------------------------------------------|----|-----|-----------------------------|---|

|   | 7 BITS                                    |    |     | 8 BITS                                         |     |   | 7 BITS                                     |    |     | 8 BITS                      | 1 |

|   | I <sup>2</sup> C SLAVE ADD<br>SELECTS DEV |    |     | REGISTER ADDRI<br>SELECTS REGIS<br>TO BE READ. | TER |   | I <sup>2</sup> C SLAVE ADDI<br>SELECTS DEV |    |     | DATA FROM<br>SELECTED REGIS |   |

Figure 7. Write/Read Data Format Example

### Table 2. I<sup>2</sup>C Slave Addresses

| ADD CONNECTION | I <sup>2</sup> C ADDRESS |

|----------------|--------------------------|

| GND            | 100 1000                 |

| $V_{DD}$       | 100 1001                 |

| SDA            | 100 1010                 |

| SCL            | 100 1011                 |

**Table 3. MUTE Register Format**

| REGISTER<br>ADDRESS |       | 0000 0001              |                      |  |  |

|---------------------|-------|------------------------|----------------------|--|--|

| BIT                 | NAME  | VALUE                  | DESCRIPTION          |  |  |

| 7                   | Х     | Don't Care             | _                    |  |  |

| 6                   | Х     | Don't Care             | _                    |  |  |

| 5                   | Х     | Don't Care             | _                    |  |  |

| 4                   | MUTER | 0*                     | Unmute right channel |  |  |

|                     |       | 1                      | Mute right channel   |  |  |

| 3                   | MUTEL | 0* Unmute left channel |                      |  |  |

|                     |       | 1                      | Mute left channel    |  |  |

| 2                   | Х     | Don't Care             | _                    |  |  |

| 1                   | Х     | Don't Care             | _                    |  |  |

| 0                   | Х     | Don't Care             | _                    |  |  |

<sup>\*</sup>Default state.

#### **Control Register**

The control register (03hex) is a read/write register that determines the device configuration. Bit 1 (IN1/IN2) controls the input multiplexer, a logic high selects input 1, a logic low selects input 2. Bit 2 (HPS\_D) controls the headphone sensing. A logic low configures the device

**Table 4. SHDN Register Format**

| REGISTER<br>ADDRESS |       | 0000 0010  |                  |

|---------------------|-------|------------|------------------|

| BIT                 | NAME  | VALUE      | DESCRIPTION      |

| 7                   | RESET | 0*         | _                |

| /                   |       | 1          | Reset device     |

| 6                   | RESET | 0*         | _                |

|                     | NESET | 1          | Reset device     |

| 5                   | RESET | 0*         | _                |

| 5                   |       | 1          | Reset device     |

| 4                   | RESET | 0*         | _                |

| 4                   |       | 1          | Reset device     |

| 3                   | RESET | 0*         | _                |

| 3                   |       | 1          | Reset device     |

| 2                   | RESET | 0*         | _                |

|                     |       | 1          | Reset device     |

| 1                   | Χ     | Don't Care | _                |

| 0                   | SHDN  | 0*         | Normal operation |

| U                   | SHDIN | 1          | Shutdown         |

<sup>\*</sup>Default state.

in automatic headphone detection mode. A logic high disables the HPS input. Bit 3 (GAINA/B) controls the gain-select multiplexer. A logic low selects GAINA. A logic high selects GAINB. GAINA/B is ignored when HPS\_D = 0. Bit 4 (SPKR/HP) selects the amplifier operating mode when HPS\_D = 1. A logic high selects speaker mode and a logic low selects headphone mode.

### **Table 5. Control Register Format**

| REGISTER<br>ADDRESS |           | 0000 0011  |                                                       |

|---------------------|-----------|------------|-------------------------------------------------------|

| BIT                 | NAME      | VALUE      | DESCRIPTION                                           |

| 7                   | X         | Don't Care | _                                                     |

| 6                   | X         | Don't Care | _                                                     |

| 5                   | X         | Don't Care | _                                                     |

| 4                   | SPKR/HP   | 0*         | Speaker mode selected                                 |

|                     |           | 1          | Headphone mode selected                               |

| 3                   | GAINA/B   | 0*         | Gain-setting A selected                               |

|                     |           | 1          | Gain-setting B selected                               |

| 2                   |           | 0*         | Automatic headphone detection enabled                 |

|                     | HPS_D     | 1          | Automatic headphone detection disabled (HPS ignored). |

| 1                   | 1014/1010 | 0*         | Input 1 selected                                      |

|                     | IN1/IN2   | 1          | Input 2 selected                                      |

| 0                   | Х         | Don't Care | _                                                     |

#### Read Data Format

In read mode (R/ $\overline{W}=1$ ), the MAX9760/MAX9762 write the contents of the selected register to the bus. The direction of the data flow reverses following the address acknowledge by the MAX9760/MAX9761. The master device reads the contents of all registers, including the read-only status register. Table 6 shows the status register format.

#### Interrupt Output (INT)

The MAX9760/MAX9762 include an interrupt output (INT) that can indicate to a master device that an event has occurred. INT is triggered when the state of HPS changes. During normal operation, INT idles high. If a headphone is inserted/removed from the jack and that action is detected by HPS, INT pulls the line low. INT remains low until a read data operation is executed.

#### I<sup>2</sup>C Compatibility

The MAX9760/MAX9762 are compatible with existing I<sup>2</sup>C systems. SCL and SDA are high-impedance inputs; SDA has an open drain that pulls the data line low during the ninth clock pulse. The communication protocol supports the standard I<sup>2</sup>C 8-bit communications. The general call address is ignored. The MAX9760/MAX9762 addresses are compatible with the 7-bit I<sup>2</sup>C addressing protocol only. No 10-bit formats are supported.

Figure 8. Bridge-Tied Load Configuration

## Applications Information

#### **BTL Speaker Amplifiers**

The MAX9760–MAX9763 feature speaker amplifiers designed to drive a load differentially, a configuration referred to as bridge-tied load (BTL). The BTL configuration (Figure 8) offers advantages over the single-ended configuration, where one side of the load is connected to ground. Driving the load differentially doubles the output voltage compared to a single-ended amplifier under similar conditions. Thus, the devices' differential gain is twice the closed-loop gain of the input amplifier. The effective gain is given by:

$$A_{VD} = 2 \times \frac{R_F}{R_{IN}}$$

Substituting 2 x V<sub>OUT(P-P)</sub> for V<sub>OUT(P-P)</sub> into the following equations yields four times the output power due to doubling of the output voltage:

$$V_{RMS} = \frac{V_{OUT(P-P)}}{2\sqrt{2}}$$

$$P_{OUT} = \frac{V_{RMS}^{2}}{R_{L}}$$

Since the differential outputs are biased at midsupply, there is no net DC voltage across the load. This eliminates the need for DC-blocking capacitors required for single-ended amplifiers. These capacitors can be large, expensive, consume board space, and degrade low-frequency performance.

**Table 6. Status Register Format**

| REGISTER ADDRESS |       | 0000 0000  |                                            |

|------------------|-------|------------|--------------------------------------------|

| BIT              | NAME  | VALUE      | DESCRIPTION                                |

| 7                | THRM  | 0          | Device temperature below thermal limit     |

| /                |       | 1          | Device temperature exceeding thermal limit |

| 6                | AMPR- | 0          | OUTR- current below current limit          |

| 0                |       | 1          | OUTR- current exceeding current limit      |

| 5                | AMPR+ | 0          | OUTR+ current below current limit          |

| 5                |       | 1          | OUTR+ current exceeding current limit      |

| 4                | AMPL- | 0          | OUTL- current below current limit          |

| 4                |       | 1          | OUTL- current exceeding current limit      |

| 3                | AMPL+ | 0          | OUTL+ current below current limit          |

| 3                |       | 1          | OUTL+ current exceeding current limit      |

| 2                | HPSTS | 0          | Device in speaker mode                     |

| 2                |       | 1          | Device in headphone mode                   |

| 1                | Х     | Don't Care | -                                          |

| 0                | Х     | Don't Care | _                                          |

When the MAX9760/MAX9762 are configured to automatically detect the presence of a headphone jack, the device defaults to gain setting A when the device is in speaker mode. When the MAX9762/MAX9763 are configured as speaker amplifiers, the gain setting defaults to the mono setting (GAINM).

#### Single-Ended Headphone Amplifier

The MAX9760–MAX9763 can be configured as single-ended headphone amplifiers through software or by sensing the presence of a headphone plug (HPS). In headphone mode, the inverting output of the BTL amplifier is disabled, muting the speaker. The gain is 1/2 that of the device in speaker mode, and the output power is reduced by a factor of 4.

In headphone mode, the load must be capacitively coupled to the device, blocking the DC bias voltage from the load (see *Typical Application Circuit*).

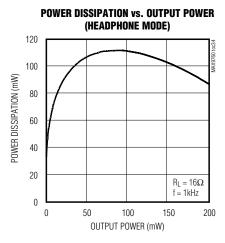

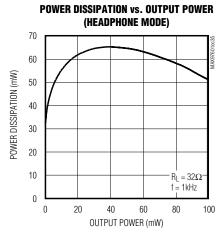

#### **Power Dissipation and Heat Sinking**

Under normal operating conditions, the MAX9760–MAX9763 can dissipate a significant amount of power. The maximum power dissipation for each package is given in the *Absolute Maximum Ratings* section under Continuous Power Dissipation or can be calculated by the following equation:

$$P_{\text{DISSPKG}(MAX)} = \frac{T_{\text{J}(MAX)} - T_{\text{A}}}{\theta_{\text{JA}}}$$

where  $T_{J(MAX)}$  is +150°C,  $T_{A}$  is the ambient temperature, and  $\theta_{JA}$  is the reciprocal of the derating factor in °C/W as specified in the *Absolute Maximum Ratings* section. For example,  $\theta_{JA}$  of the QFN package is +42°C/W.

The increase in power delivered by the BTL configuration directly results in an increase in internal power dissipation over the single-ended configuration. The maximum power dissipation for a given VDD and load is given by the following equation:

$$P_{\text{DISS(MAX)}} = \frac{2V_{\text{DD}}^2}{\pi^2 R_{\text{L}}}$$

If the power dissipation for a given application exceeds the maximum allowed for a given package, either reduce  $V_{DD}$ , increase load impedance, decrease the ambient temperature, or add heat sinking to the device. Large output, supply, and ground PC board traces improve the maximum power dissipation in the package.

Thermal overload protection limits total power dissipation in these devices. When the junction temperature exceeds +160°C, the thermal protection circuitry disables the amplifier output stage. The amplifiers are enabled once the junction temperature cools by 15°C. This results in a pulsing output under continuous thermal-overload conditions as the device heats and cools.

#### **Component Selection**

#### Gain-Setting Resistors

External feedback components set the gain of the MAX9760–MAX9763. Resistor  $R_{\text{IN}}$  sets the gain of the input amplifier (AVIN) and resistor  $R_{\text{F}}$  sets the gain of the second stage amplifier (AVOUT):

$$A_{VIN} = -\left(\frac{10k\Omega}{R_{IN}}\right), A_{VOUT} = -\left(\frac{R_F}{10k\Omega}\right)$$

Combining AVIN and AVOUT, RIN and RF set the single-ended gain of the device as follows:

$$A_{V} = A_{VIN} \times A_{VOUT} = -\left(\frac{10k\Omega}{R_{IN}}\right) \times -\left(\frac{R_{F}}{10k\Omega}\right) = +\left(\frac{R_{F}}{R_{IN}}\right)$$

As shown, the two-stage amplifier architecture results in a noninverting gain configuration, preserving absolute phase through the MAX9760–MAX9763. The gain of the device in BTL mode is twice that of the single-ended mode. Choose  $R_{IN}$  between  $10k\Omega$  and  $15k\Omega$  and  $R_F$  between  $15k\Omega$  and  $100k\Omega$ .

#### Input Filter

The input capacitor ( $C_{IN}$ ), in conjunction with  $R_{IN}$ , forms a highpass filter that removes the DC bias from an incoming signal. The AC-coupling capacitor allows the amplifier to bias the signal to an optimum DC level. Assuming zero-source impedance, the -3dB point of the highpass filter is given by:

$$f_{-3dB} = \frac{1}{2\pi R_{IN} C_{IN}}$$

Choose  $R_{IN}$  according to the *Gain-Setting Resistors* section. Choose the  $C_{IN}$  such that  $f_{-3dB}$  is well below the lowest frequency of interest. Setting  $f_{-3dB}$  too high affects the amplifier's low-frequency response. Use capacitors whose dielectrics have low-voltage coefficients, such as tantalum or aluminum electrolytic. Capacitors with high-voltage coefficients, such as ceramics, may result in an increased distortion at low frequencies.

Other considerations when designing the input filter include the constraints of the overall system, the actual frequency band of interest, and click-and-pop suppression.

#### **Output-Coupling Capacitor**

The MAX9760/MAX9763 require output-coupling capacitors to operate in single-ended (headphone) mode. The output-coupling capacitor blocks the DC component of the amplifier output, preventing DC current from flowing to the load. The output capacitor and the load impedance form a highpass filter with a -3dB point determined by:

$$f_{-3dB} = \frac{1}{2\pi R_L C_{OUT}}$$

As with the input capacitor, choose  $C_{OUT}$  such that  $f_{-3dB}$  is well below the lowest frequency of interest. Setting  $f_{-3dB}$  too high affects the amplifier's low-frequency response.

Load impedance is a concern when choosing Cout. Load impedance can vary, changing the -3dB point of the output filter. A lower impedance increases the corner frequency, degrading low-frequency response. Select Cout such that the worst-case load/Cout combination yields an adequate response. Select capacitors with low ESR to minimize resistive losses and optimize power transfer to the load.

#### **BIAS Capacitor**

BIAS is the output of the internally generated 2.5VDC bias voltage. The BIAS bypass capacitor, C<sub>BIAS</sub>, improves PSRR and THD+N by reducing power supply and other noise sources at the common-mode bias node, and also generates the clickless/popless, start-up/shutdown DC bias waveforms for the speaker amplifiers. Bypass BIAS with a 1µF capacitor to GND.

#### Supply Bypassing

Proper power-supply bypassing ensures low-noise, low-distortion performance. Place a 0.1µF ceramic capacitor from VDD to GND. Add additional bulk capacitance as required by the application, typically 100µF. Bypass PVDD with a 100µF capacitor to GND. Locate bypass capacitors as close to the device as possible.

#### **Gain Select**

The MAX9760–MAX9763 feature multiple gain settings on each channel, making available different gain and feedback configurations. The gain-setting resistor (R<sub>F</sub>) is connected between the amplifier output (OUT\_+) and the gain setpoint (GAIN\_). An internal multiplexer switches between the different feedback resistors

Figure 9. Bass Boost Circuit

depending on the status of the gain control input. The stereo MAX9760/MAX9761 feature two gain options per channel. The mono MAX9762/MAX9763 feature two gain options per single-ended channel, and a single gain option for the mono speaker amplifier (see Tables 1a and 1b for the gain-setting options).

The MAX9762 defaults to GAINM in speaker mode and can switch between GAINA and GAINB in headphone mode.

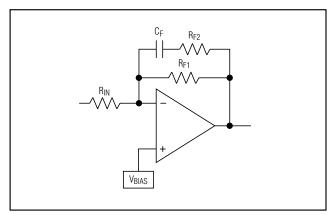

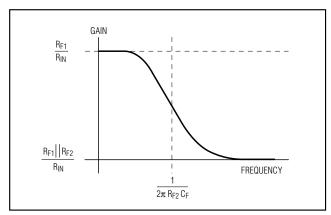

#### Bass Boost Circuit

Headphones typically have a poor low-frequency response due to speaker and enclosure size limitations. A bass boost circuit compensates the poor low-frequency response (Figure 9). At low frequencies, the capacitor CF is an open circuit, and the effective impedance in the feedback loop (RF(EFF)) is RF(EFF) = RF1.

At the frequency:

$$\frac{1}{2\pi R_{E2}C_{E}}$$

where the impedance,  $C_{\text{F}}$ , begins to decrease, and at high frequencies, the  $C_{\text{F}}$  is a short circuit. Here the impedance of the feedback loop is:

$$R_{F(EFF)} = \frac{R_{F1} \times R_{F2}}{R_{F1} + R_{F2}}$$

Figure 10. Bass Boost Response

Assuming  $R_{F1} = R_{F2}$ , then  $R_{F(EFF)}$  at low frequencies is twice that of  $R_{F(EFF)}$  at high frequencies (Figure 10). Thus, the amplifier has more gain at lower frequencies, boosting the system's bass response. Set the gain roll-off frequency based upon the response of the speaker and enclosure.

#### **Layout and Grounding**