Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **General Description**

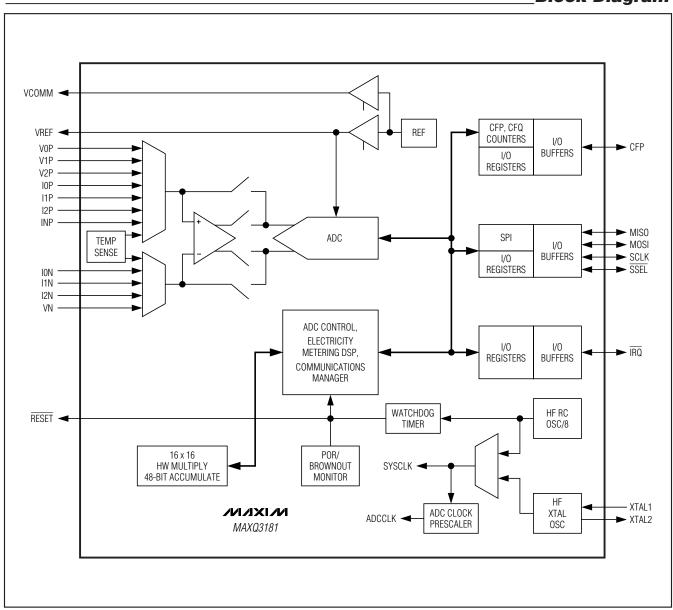

The MAXQ3181 is a dedicated electricity measurement front-end that collects and calculates polyphase voltage, current, active power and energy, and many other metering parameters of a polyphase load. The computed results can be retrieved by an external master through the on-chip serial peripheral interface (SPI™) bus. This bus is also used by the external master to configure the operation of the MAXQ3181 and monitor the status of operations.

The MAXQ3181 performs voltage and current measurements using an integrated ADC that can measure up to seven external differential signal pairs. An eighth differential signal pair is used to measure the die temperature. An internal amplifier automatically adjusts the current channel gain to compensate for low-current channel-signal levels.

### **Applications**

3-Phase Active Energy Electricity Meters

### **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAXQ3181-RAN+ | -40°C to +85°C | 28 TSSOP    |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Pin Configuration and Typical Application Circuit appear at end of data sheet.

### **Features**

- ♦ Compatible with 3-Phase/3-Wire, 3-Phase/4-Wire, and Other 3-Phase Services

- ♦ 0.1% Active Power and Energy Linearity Error

- ♦ 0.5% Apparent Power and Energy Linearity Error

- ♦ 0.5% Linearity Errors for RMS Voltage and RMS Current

- Neutral Line Current Measurement

- **♦** Line Frequency (Hz)

- **♦ Power Factors**

- ♦ Phase Sequence Indication

- ♦ Phase Voltage Absence Detection

- ♦ Programmable Pulse Width

- **♦ Programmable No-Load Current Threshold**

- **♦ Programmable Meter Constant**

- **♦** Programmable Thresholds for Undervoltage and Overvoltage Detection

- ♦ Programmable Threshold for Overcurrent Detection

- ♦ Amp-Hours in Absence of Voltage Signals

- ♦ On-Chip Digital Temperature Sensor

- ♦ Precision Internal Voltage Reference 2.048V (30ppm/°C typical), Also Supports An External **Voltage Reference**

- **♦** Active Power and Energy of Each Phase and Combined 3-Phase (kWh), Positive and Negative

- ♦ Apparent Power and Energy of Each Phase and **Combined 3-Phase**

- **♦** Supports Software Meter Calibration

- ♦ Up to 3-Point Multipoint Calibration to **Compensate for Transducer Nonlinearity**

- **♦** Power-Fail Detection

- ♦ Bidirectional Reset Input/Output

- ♦ SPI-Compatible Serial Interface with Interrupt Request (IRQ) Output

- ♦ Single 3.3V Supply, Low Power (35mW typical)

MAXQ is a registered trademark of Maxim Integrated Products, Inc. SPI is a trademark of Motorola. Inc.

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: www.maxim-ic.com/errata.

| TABLE OF CONTENTS                           |   |

|---------------------------------------------|---|

| sbsolute Maximum Ratings                    | 8 |

| Netering Specifications                     | 8 |

| lectrical Characteristics                   | 8 |

| SPI Slave Mode Timing                       |   |

| Block Diagram                               |   |

| in Description                              |   |

| Detailed Description                        |   |

| Analog Front-End                            |   |

| Digital Signal Processor                    |   |

| Precision Pulse Generators                  |   |

| SPI Peripheral                              |   |

| Operating Modes                             |   |

| Run Mode                                    |   |

| Stop Mode                                   |   |

| Reset Sources                               |   |

| External Reset                              |   |

| Power-On Reset                              |   |

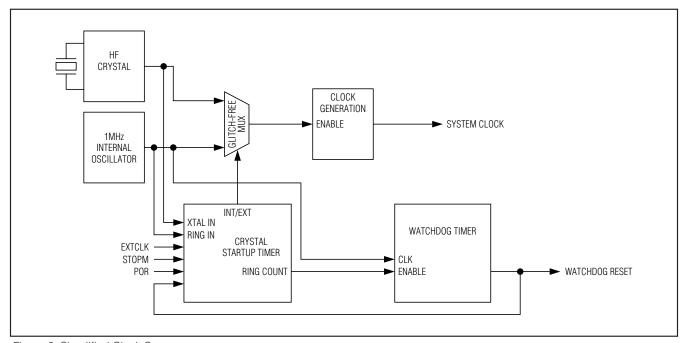

| Watchdog Reset                              |   |

| Software Reset                              |   |

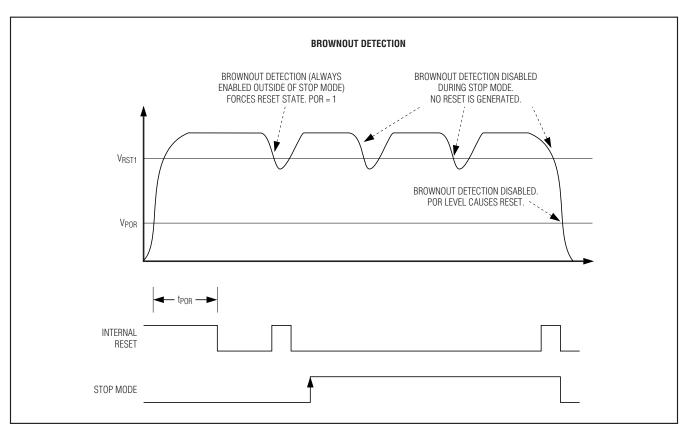

| Power-Supply Monitoring                     |   |

| Clock Sources                               |   |

| External High-Frequency Crystal             |   |

| External High-Frequency Clock               |   |

| Internal RC Oscillator                      |   |

| Master Communications                       |   |

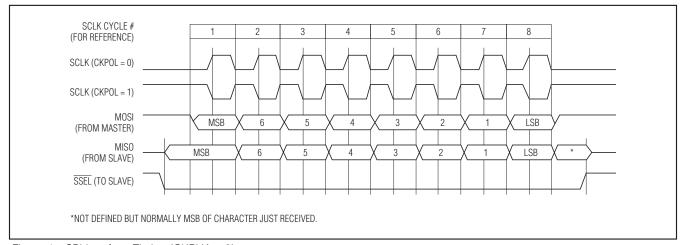

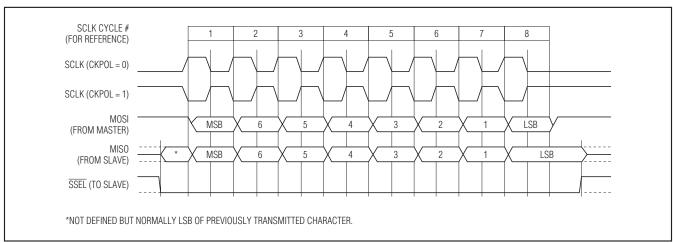

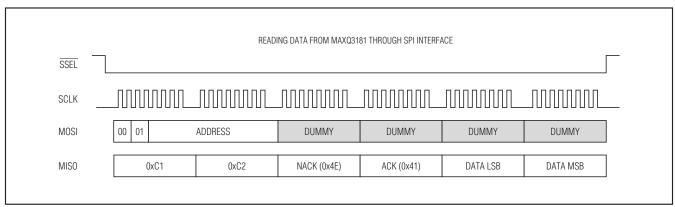

| SPI Communications Rate and Format          |   |

| SPI Communications Protocol                 |   |

| Host Software Design                        |   |

| Register Set                                |   |

| AAM-Based Registers                         |   |

| General Operating Registers                 |   |

| Global Status Register (STATUS) (0x000)     |   |

| Operating Mode Register 0 (OPMODE0) (0x001) |   |

| Operating Mode Register 1 (OPMODE1) (0x002) |   |

| Operating Mode Register 2 (OPMODE2) (0x003) |   |

| TABLE OF CONTENTS (continued)                                                                  |    |

|------------------------------------------------------------------------------------------------|----|

| Global Interrupt Registers                                                                     | 31 |

| Interrupt Request Flag Register (IRQ_FLAG) (0x004)                                             | 31 |

| Interrupt Mask Register (IRQ_MASK) (0x006)                                                     | 32 |

| Meter Pulse Configuration                                                                      | 33 |

| Pulse Configuration—CFP Output (PLSCFG1) (0x01E)                                               | 33 |

| CFP Pulse Width (PLS1_WD) (0x020)                                                              | 33 |

| CFP Pulse Threshold (THR1) (0x022)                                                             | 34 |

| Calibration Registers                                                                          | 34 |

| Current Gain, Phase X = A/B/C/N (X.I_GAIN) (A: 0x130, B: 0x21C, C: 0x308, N: 0x12E)            | 34 |

| Voltage Gain, Phase X = A/B/C (X.V_GAIN) (A: 0x132, B: 0x21E, C: 0x30A)                        | 35 |

| Energy Gain, Phase X = A/B/C (X.E_GAIN) (A: 0x134, B: 0x220, C: 0x30C)                         | 35 |

| Phase-Angle Compensation, High Range, Phase X = A/B/C (X.PA0) (A: 0x13E, B: 0x22A, C: 0x316)   | 35 |

| Phase-Angle Compensation, Medium Range, Phase X = A/B/C (X.PA1) (A: 0x140, B: 0x22C, C: 0x318) | 36 |

| Phase-Angle Compensation, Low Range, Phase X = A/B/C (X.PA2) (A: 0x142, B: 0x22E, C: 0x31A)    | 36 |

| Limit Registers                                                                                | 36 |

| Overcurrent Level (OCLVL) (0x044)                                                              | 36 |

| Overvoltage Level (OVLVL) (0x046)                                                              | 37 |

| Undervoltage Level (UVLVL) (0x048)                                                             | 37 |

| No-Load Level (NOLOAD) (0x04A)                                                                 | 37 |

| Phase Status Registers                                                                         | 38 |

| Interrupt Flags, Phase X = A/B/C (X.FLAGS) (A: 0x144, B: 0x230, C: 0x31C)                      | 38 |

| Interrupt Mask, Phase X = A/B/C (X.MASK) (A: 0x145, B: 0x231, C: 0x31D)                        | 39 |

| Energy Overflow Flags, Phase X = A/B/C (X.EOVER) (A: 0x146, B: 0x232, C: 0x31E)                | 39 |

| Measurements                                                                                   | 40 |

| Line Frequency (LINEFR) (0x062)                                                                | 40 |

| Power Factor, Phase X = A/B/C (X.PF) (A: 0x1C6, B: 0x2B2, C: 0x39E)                            | 40 |

| RMS Voltage, Phase X = A/B/C (X.VRMS) (A: 0x1C8, B: 0x2B4, C: 0x3A0)                           | 40 |

| RMS Current, Phase X = A/B/C (X.IRMS) (A: 0x1CC, B: 0x2B8, C: 0x3A4)                           | 41 |

| Energy, Real Positive, Phase X = A/B/C (X.EAPOS) (A: 0x1E8, B: 0x2D4, C: 0x3C0)                | 41 |

| Energy, Real Negative, Phase X = A/B/C (X.EANEG) (A: 0x1EC, B: 0x2D8, C: 0x3C4)                | 42 |

| Energy, Apparent, Phase X = A/B/C (X.ES) (A: 0x1F8, B: 0x2E4, C: 0x3D0)                        | 42 |

| Virtual Register Conversion Coefficients                                                       | 43 |

| Voltage Units Conversion Coefficient (VOLT_CC) (0x014)                                         | 43 |

| Current Units Conversion Coefficient (AMP_CC) (0x016)                                          | 43 |

| Power Units Conversion Coefficient (PWR_CC) (0x018)                                            | 44 |

| Energy Units Conversion Coefficient (ENR_CC) (0x01A)                                           | 45 |

| TABLE OF CONTENTS (continued)                                                       |  |

|-------------------------------------------------------------------------------------|--|

| Virtual Registers                                                                   |  |

| Power                                                                               |  |

| Real Power, Phase X = A/B/C/T (PWRP.X) (A: 0x801, B: 0x802, C: 0x804, T: 0x807)     |  |

| Apparent Power, Phase X = A/B/C/T (PWRS.X) (A: 0x821, B: 0x822, C: 0x824, T: 0x827) |  |

| Voltage and Current                                                                 |  |

| RMS Volts, Phase X = A/B/C (V.X) (A: 0x831, B: 0x832, C: 0x834)                     |  |

| RMS Amps, Phase X = A/B/C/N (I.X) (A: 0x841, B: 0x842, C: 0x844, N: 0x840)          |  |

| Power Factor                                                                        |  |

| Power Factor (PF.T) (0x867)                                                         |  |

| Energy                                                                              |  |

| Real Energy, Phase A/B/C/T (ENRP.X) (A: 0x8C1, B: 0x8C2, C: 0x8C4, T: 0x8C7)        |  |

| Apparent Energy, Phase A/B/C/T (ENRS.X) (A: 0x871, B: 0x872, C: 0x874, T: 0x877)    |  |

| Theory of Operation                                                                 |  |

| Analog Front-End Operation                                                          |  |

| Digital Signal Processing (DSP) Terminology                                         |  |

| Digital Processing                                                                  |  |

| Per Sample Operations                                                               |  |

| Per DSP Cycle Operations                                                            |  |

| Energy Accumulation                                                                 |  |

| No-Zero-Crossing Detection                                                          |  |

| Phase Sequence Status                                                               |  |

| Power Calculation (Active and Apparent)                                             |  |

| Energy Accumulation Start Delay                                                     |  |

| No-Load Feature                                                                     |  |

| On Demand Calculations                                                              |  |

| RMS Volts, RMS Amps                                                                 |  |

| Power                                                                               |  |

| Power Factor                                                                        |  |

| Line Frequency                                                                      |  |

| Energy                                                                              |  |

| Meter Pulse                                                                         |  |

| Generating Pulses                                                                   |  |

| Meter Constant                                                                      |  |

| Interrupts                                                                          |  |

| Overvoltage and Overcurrent Detection                                               |  |

| Meter Units to Real Units Conversion                                                |  |

| Units Conversion Examples                                                           |  |

| TABLE OF CONTENTS (continued)                                                             |    |

|-------------------------------------------------------------------------------------------|----|

| Calibration Procedure                                                                     | 58 |

| Calibration Overview                                                                      | 58 |

| Calibrating Voltage                                                                       | 59 |

| Calibrating Current                                                                       | 59 |

| Calibrating Phase Offset                                                                  | 60 |

| Interfacing the MAXQ3181 to External Hardware                                             | 60 |

| Connections to the Power Source                                                           | 61 |

| Sensor Selection                                                                          | 61 |

| Voltage Sensors                                                                           | 61 |

| Voltage-Divider                                                                           | 61 |

| Voltage Transformer                                                                       | 61 |

| Current Sensors                                                                           | 62 |

| Current Shunt                                                                             | 62 |

| Current Transformer                                                                       | 62 |

| Advanced Operation                                                                        |    |

| Modifying the ADC Operation                                                               |    |

| Fine-Tuning the DSP Controls                                                              |    |

| Fine-Tuning the Line Frequency Measurement                                                |    |

| Low-Power Measurement Mode (LOWPM)                                                        |    |

| Temperature                                                                               |    |

| Advanced Calibrations                                                                     |    |

| Calibrating Current Offset                                                                |    |

| Calibrating Linearity                                                                     |    |

| Calibrating Power/Energy Gain                                                             |    |

| Multipoint Phase Offset Calibration                                                       |    |

| Advanced Register Configurations                                                          |    |

| Analog Scan Configuration Registers                                                       |    |

| Time Slot Assignment—Current Channel X = A/B/C (SCAN_IX) (A: 0x008, B: 0x00C, C: 0x00A)   |    |

| Time Slot Assignment—Voltage Channel $X = A/B/C$ (SCAN_VX) (A: 0x009, B: 0x00D, C: 0x00B) |    |

| Time Slot Assignment—Neutral Current Channel (SCAN_IN) (0x00E)                            |    |

| Time Slot Assignment—Temperature Channel (SCAN_TE) (0x00F)                                |    |

| Neutral Current                                                                           |    |

| Auxiliary Channel Configuration (AUX_CFG) (0x010)                                         |    |

| DSP System Configuration                                                                  |    |

| System Clock Frequency (SYS_KHZ) (0x012)                                                  |    |

| Cycle Count (CYCNT) (0x01C)                                                               |    |

| Number of Scan Frames per DSP Cycle (NS) (0x040)                                          |    |

| TABLE OF CONTENTS (continued)                                                                       |    |

|-----------------------------------------------------------------------------------------------------|----|

| Filter Coefficients                                                                                 |    |

| Line Cycle Noise Rejection Filter (REJ_NS) (0x02C)                                                  | 71 |

| Line Cycle Averaging Filter (AVG_NS) (0x02E)                                                        | 71 |

| Meter Measurement Averaging Filter (AVG_C) (0x030)                                                  | 72 |

| Meter Measurement Highpass Filter (HPF_C) (0x032)                                                   | 72 |

| Zero-Cross Lowpass Filter (ZC_LPF) (0x05A)                                                          | 72 |

| Hardware Mirror Registers                                                                           | 73 |

| ADC Configuration (R_ACFG) (0x04C)                                                                  | 73 |

| ADC Conversion Rate (R_ADCRATE) (0x04E)                                                             | 73 |

| ADC Settling Time (R_ADCACQ) (0x050)                                                                | 74 |

| SPI Configuration (R_SPICF) (0x052)                                                                 | 74 |

| Timeouts                                                                                            | 75 |

| Zero-Crossing Timeout (NZX_TIMO) (0x054)                                                            | 75 |

| Communications Timeout (COM_TIMO) (0x056)                                                           | 75 |

| Energy Accumulation Timeout (ACC_TIMO) (0x058)                                                      | 75 |

| Phase-Angle Compensation                                                                            | 76 |

| Phase Offset Current Threshold 1 (I1THR) (0x05C)                                                    | 76 |

| Phase Offset Current Threshold 2 (I2THR) (0x05E)                                                    | 76 |

| Miscellaneous Gain                                                                                  | 76 |

| Neutral Current Gain (N.I_GAIN) (0x12E)                                                             | 76 |

| Linearity Compensation                                                                              | 77 |

| Linearity Offset, High Range, Phase X = A/B/C (X.OFFS_HI) (A: 0x138, B: 0x224, C: 0x310)            | 77 |

| Linearity Gain Coefficient, Low Range, Phase X = A/B/C (X.GAIN_LO) (A: 0x13A, B: 0x226, C: 0x312) . | 77 |

| Linearity Offset, Low Range, Phase X = A/B/C (X.OFFS_LO) (A: 0x13C, B: 0x228, C: 0x314)             | 78 |

| Measurements—RAM Registers                                                                          | 78 |

| On-Demand RMS Result (N.IRMS) (0x11C)                                                               | 78 |

| Energy Accumulated in the Last DSP Cycle                                                            | 79 |

| Real Energy, Phase X = A/B/C (X.ACT) (A: 0x1D0, B: 0x2BC, C: 0x3A8)                                 | 79 |

| Apparent Energy, Phase X = A/B/C (X.APP) (A: 0x1D8, B: 0x2C4, C: 0x3B0)                             | 79 |

| Checksum (CHKSUM) (0x060)                                                                           | 80 |

| Neutral Current                                                                                     | 81 |

| RMS Current, Neutral (I.N) (0x840)                                                                  | 81 |

| Special Commands                                                                                    | 81 |

| Applications Information                                                                            | 81 |

| Grounds and Bypassing                                                                               | 81 |

| Specific Design Considerations for MAXQ3181-Based Systems                                           | 81 |

| Additional Documentation                                                                            | 82 |

| TABLE OF CONTENTS (continued)                             |    |

|-----------------------------------------------------------|----|

| Technical Support                                         |    |

| Package Information                                       |    |

| Pin Configuration                                         |    |

| Typical Application Circuit                               |    |

| Revision History                                          |    |

| LIST OF FIGURES                                           |    |

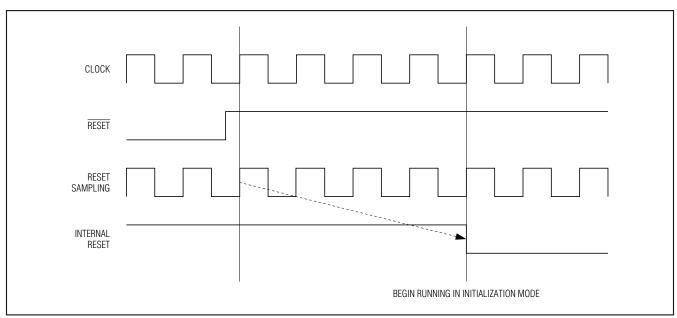

| Figure 1. External Reset                                  |    |

| Figure 2. Brownout Reset                                  |    |

| Figure 3. Simplified Clock Sources                        |    |

| Figure 4a. SPI Interface Timing (CKPHA = 0)               |    |

| Figure 4b. SPI Interface Timing (CKPHA = 1)               |    |

| Figure 5. Read SPI Transfer                               |    |

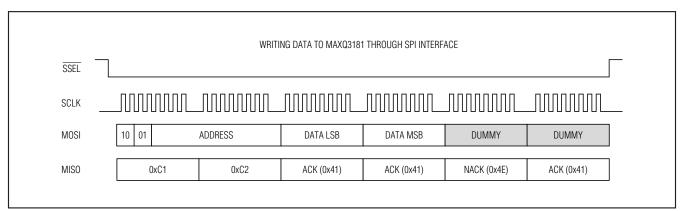

| Figure 6. Write SPI Transfer                              |    |

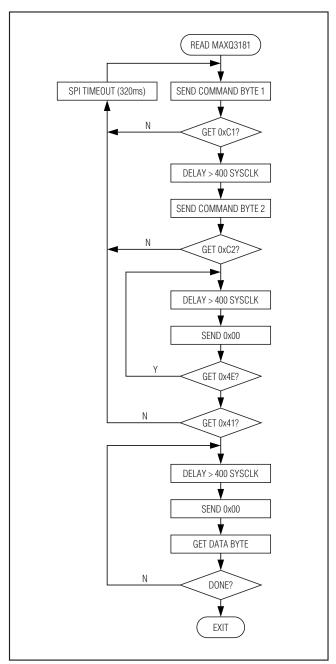

| Figure 7. Flowchart for Reading from MAXQ3181             |    |

| Figure 8. Flowchart for Writing to MAXQ3181               |    |

| Figure 9. Per Sample Operations                           |    |

| Figure 10. Computation of RMS Values                      |    |

| Figure 11. Phase Compensation for Energy Calculations     |    |

| Figure 12. Apparent Energy Calculations                   |    |

| Figure 13. Sample Voltage Input Circuit                   |    |

| Figure 14. Sample Current Input Circuit                   |    |

| Figure 15. Offset Testing Setup                           |    |

| Figure 16. Phase Offset vs. Input Current Calibration     | 64 |

| LIST OF TABLES                                            |    |

| Table 1. Command Format for SPI Register Read             |    |

| Table 2. Command Format for SPI Register Write            |    |

| Table 3. RAM Register Map                                 |    |

| Table 4. Virtual Register Map                             |    |

| Table 5. Meter Unit Definitions                           |    |

| Table 6. Virtual Register Coefficients                    |    |

| Table 7. Virtual Registers That Activate Special Commands |    |

|                                                           |    |

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on DVDD Relative to DGND0.3V to +4.0V | Voltage Range on VxP, IxN Relative to AGND0.3V to +4.0V |

|-----------------------------------------------------|---------------------------------------------------------|

| Voltage Range on AVDD Relative to AGND0.3V to +4.0V | Operating Temperature Range40°C to +85°C                |

| Voltage Range on AGND Relative to DGND0.3V to +0.3V | Junction Temperature+150°C                              |

| Voltage Range on AVDD Relative to DVDD0.3V to +0.3V | Storage Temperature Range65°C to +150°C                 |

| Voltage Range on Any Pin Relative to                | Lead Soldering TemperatureRefer to the IPC/             |

| DGND except VxP, IxN Pins0.3V to +4.0V              | JEDEC J-STD-020 Specification.                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **METERING SPECIFICATIONS**

(VAVDD = VDVDD = VRST to 3.6V, Current Channel Dynamic Range 1000:1 at TA = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                       | CONDITIONS | MIN | TYP | MAX | UNITS |

|---------------------------------|------------|-----|-----|-----|-------|

| Active Energy Linearity Error   | DR 1000:1  |     | 0.1 |     | %     |

| Apparent Energy Linearity Error | DR 1000:1  |     | 0.5 |     | %     |

| RMS Voltage Linearity Error     | DR 20:1    |     | 0.5 |     | %     |

| RMS Current Linearity Error     | DR 500:1   |     | 1.0 |     | %     |

|                                 | DR 20:1    |     | 0.5 |     | /°    |

| Line Frequency Error            |            |     | 0.5 |     | %     |

| Power Factor Error              |            |     | 1.0 |     | %     |

### **ELECTRICAL CHARACTERISTICS**

(VAVDD = VDVDD = VRST to 3.6V, TA = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                             | SYMBOL            | CONDITIONS                                               | MIN                        | TYP   | MAX                        | UNITS |

|---------------------------------------|-------------------|----------------------------------------------------------|----------------------------|-------|----------------------------|-------|

| POWER-SUPPLY SPECIFICATION            | ONS               |                                                          |                            |       |                            |       |

| Digital Supply Voltage                | V <sub>DVDD</sub> |                                                          | V <sub>RST</sub>           |       | 3.6                        | V     |

| Power-Fail Interrupt Trip Point       | VPFW              | Active mode, EPWRF = 1                                   | 2.84                       |       | 3.13                       | V     |

| Power-Fail Reset Trip Point           | V <sub>RST</sub>  | Active mode                                              | 2.70                       |       | 2.99                       | V     |

| Analog Supply Voltage                 | Vavdd             |                                                          | VRST                       |       | 3.6                        | V     |

| Analog Supply Current                 | lavdd             | f <sub>CLK</sub> = 8MHz                                  |                            | 0.9   | 1.8                        | mA    |

| Digital Supply Current                | IDVDD             | f <sub>CLK</sub> = 8MHz                                  |                            | 8.5   | 13                         | mA    |

| Low-Power Measurement Mode<br>Current | ILOWPM            | LOWPM = 1 (Note 1)                                       |                            | 4.2   |                            | mA    |

| Stop-Mode Current                     |                   |                                                          |                            | 0.2   | 12                         | μΑ    |

| DIGITAL I/O SPECIFICATIONS            |                   |                                                          |                            |       | ,                          |       |

| Input High Voltage                    | VIH               |                                                          | 0.7 x<br>V <sub>DVDD</sub> |       |                            | V     |

| Input Low Voltage                     | VIL               |                                                          |                            |       | 0.3 x<br>V <sub>DVDD</sub> | V     |

| Input Hysteresis                      | VIHYS             | $V_{DVDD} = 3.3V$                                        |                            | 500   |                            | mV    |

| Input Leakage                         | ΙL                | V <sub>IN</sub> = DGND or V <sub>DVDD</sub> , pullup off |                            | ±0.01 | ±1                         | μΑ    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = V_{RST}$  to 3.6V,  $T_A = -40$ °C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                               | SYMBOL          | CONDITIONS                             | MIN                                   | TYP   | MAX              | UNITS  |

|-----------------------------------------|-----------------|----------------------------------------|---------------------------------------|-------|------------------|--------|

| Input Low Current                       | lıL             | V <sub>IN</sub> = 0.4V, weak pullup on | -50                                   |       |                  | μΑ     |

| RESET Pullup Resistance                 | RRESET          |                                        | 50                                    | 150   | 200              | kΩ     |

| Output High Voltage (Except             | Vон             | I <sub>OH</sub> = -4mA                 | V <sub>DVDD</sub><br>- 0.4            |       |                  | V      |

| RESET)                                  | VOH             | I <sub>OH</sub> = -6mA                 | V <sub>D</sub> V <sub>D</sub> D - 0.5 |       |                  | Ů      |

| Output Low Voltage                      | V <sub>OL</sub> | I <sub>OL</sub> = 4mA                  |                                       |       | 0.4              | V      |

| Output Low Voltage                      | VOL             | I <sub>OL</sub> = 6mA                  |                                       |       | 0.5              | V      |

| SYSTEM CLOCK SOURCES                    |                 |                                        |                                       |       |                  |        |

| External Clock Input Frequency          |                 |                                        | 0                                     |       | 8.12             | MHz    |

| External Clock Input Duty Cycle         |                 |                                        | 45                                    |       | 55               | %      |

| External HF Crystal Frequency           |                 | Fundamental mode                       |                                       |       | 8.12             | MHz    |

| XTAL1, XTAL2 Internal Load Capacitance  |                 |                                        |                                       | 16    |                  | pF     |

| Internal RC Oscillator Frequency        |                 |                                        | 7.4                                   | 7.6   | 8.6              | MHz    |

| Internal RC Oscillator Accuracy         |                 |                                        |                                       | ±2    |                  | %      |

| Internal RC Oscillator Current          |                 |                                        |                                       | 50    | 120              | μΑ     |

| Internal RC Oscillator Startup<br>Delay |                 | (Note 1)                               |                                       | 0.45  |                  | μs     |

| ANALOG-TO-DIGITAL CONVERTE              | R               |                                        | '                                     |       |                  | l      |

| Input Voltage Range                     |                 |                                        | 0                                     |       | V <sub>REF</sub> | V      |

| Common-Mode Bias                        | VCOMM           |                                        |                                       | 1.14  |                  | V      |

| Offset Error                            |                 |                                        |                                       | ±2    |                  | mV     |

| Offset Error Drift                      |                 |                                        |                                       | ±8    |                  | μV/°C  |

| Gain Error (G = 1)                      |                 |                                        |                                       | 0.05  |                  | %      |

| Spurious-Free Dynamic Range             | SFDR            |                                        |                                       | 90    |                  | dB     |

| Total Harmonic Distortion               | THD             |                                        |                                       | 90    |                  | dB     |

| Input Bandwidth (-3dB)                  |                 | (Note 1)                               |                                       | 7     |                  | kHz    |

| INTERNAL VOLTAGE REFERENCE              | CE              |                                        | •                                     |       |                  |        |

| Temperature Coefficient                 |                 | (Note 1)                               |                                       | 30    |                  | ppm/°C |

| Output Voltage                          | VREF            |                                        |                                       | 2.048 |                  | V      |

| INTERNAL TEMPERATURE SEN                |                 |                                        | •                                     |       |                  |        |

| Temperature Error                       |                 | (Note 1)                               | -4                                    |       | +4               | °C     |

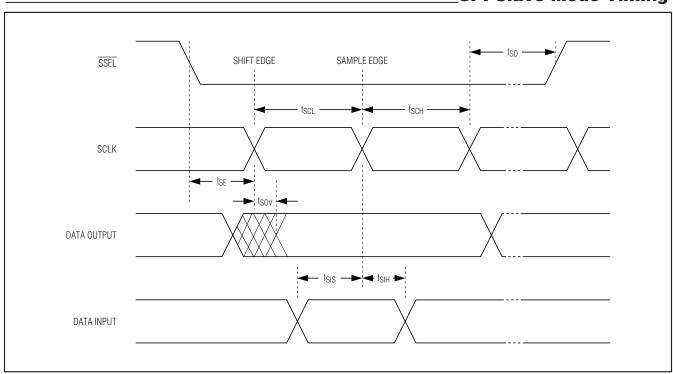

| SPI SLAVE-MODE INTERFACE T              | IMING           |                                        | •                                     |       |                  |        |

| Maximum SPI Clock Rate                  |                 | (Note 3)                               |                                       |       | fsys/4           | MHz    |

| SCLK Input Pulse-Width High             | tsch            | (Note 3)                               | 4 x<br>tsys                           |       |                  | ns     |

| SCLK Input Pulse-Width Low              | tscl            | (Note 3)                               | 4 x<br>tsys                           |       |                  | ns     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = V_{RST}$  to 3.6V,  $T_A = -40$ °C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                      | SYMBOL          | CONDITIONS | MIN                | TYP | MAX     | UNITS |

|------------------------------------------------|-----------------|------------|--------------------|-----|---------|-------|

| SSEL Low to First SCLK Edge (Slave Enable)     | tsE             | (Note 3)   | 4/t <sub>SYS</sub> |     |         | ns    |

| Last SCLK Edge to SSEL High (Slave Disable)    | t <sub>SD</sub> |            | tsys + 5           |     |         | ns    |

| MOSI Valid to SCLK Sample<br>Edge (MOSI Setup) | tsis            |            | 5                  |     |         | ns    |

| SCLK Sample Edge to MOSI<br>Change (MOSI Hold) | tsıH            |            | tsys + 5           |     |         | ns    |

| SCLK Shift Edge to MISO Valid (MISO Hold)      | tsov            |            |                    | 3t; | sys + 5 | ns    |

**Note 1:** Specifications guaranteed by design but not production tested.

**Note 2:** Specifications to -40°C are guaranteed by design and are not production tested.

**Note 3:**  $t_{SYS} = 1/f_{SYS}$ , where  $f_{SYS}$  is the system clock frequency, external or internal.

### **SPI Slave Mode Timing**

### **Block Diagram**

### **Pin Description**

| PIN   NAME   POWER PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | T     |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 17, 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PIN      | NAME  |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 25 AVDD Analog Supply Voltage  18 DGND Digital Ground  9 AGND Analog Ground  19 AGND Analog Ground  20 VOOMM Voltage Bias. This pin can be used to create an input common-mode DC offset for ADC channel conversions.  24 VREF Voltage Reference. Reference voltage for the ADC. An external reference voltage can be connected to this pin when extremely high accuracy is required.  26. 3, 4 VOP, IOP, ION, ION, ION, ION, ION, ION, ION, ION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | T     |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 18 DGND Digital Ground  9 AGND Analog Ground  19 VCOMM Voltage Bias. This pin can be used to create an input common-mode DC offset for ADC channel conversions.  24 VREF Voltage Reference. Reference voltage for the ADC. An external reference voltage can be connected to this pin when extremely high accuracy is required.  26, 3, 4 VOP, IOP, ION Place AN OUTAGE AND CURRENT PINS  27, 5, 6 V1P, ITP, INP Phase A Voltage and Current Analog Inputs  28, 7, 8 V2P, I2P, I2N Phase C Voltage and Current Analog Inputs  1 VN Analog Input for Common Voltage  2 INP Analog Input for Neutral Current  10 XTAL2 High-Frequency Crystal Input/Output. When using an external high-frequency crystal, the crystal oscillator circuit should be connected between XTAL1 and XTAL2. When using an externally driven clock (EXTCLK = 1), the clock should be input at XTAL1, with XTAL2 left unconnected.  11 Interrupt Request Output. This line is driven low by the device to indicate to the master that an unmasked interrupt has occurred.  13 SSEC Slave Select Input. This line is the active-low slave select input for the SPI interface.  14 SCLK Slave Clock Input. This line is used by the master to transmit data to the slave (the MAXQ3181) over the SPI interface.  16 MISO Master In-Slave Out Output. This line is used by the MAXQ3181 (the slave) to transmit data back to the master over the SPI interface.  17 RESET RESET RESET of in its released.  18 NO CONNECTION PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | l        |       |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 9 AGND Analog Ground  VCOMM Voltage Reference, Reference voltage for the ADC. An external reference voltage can be connected to this pin when extremely high accuracy is required.  VOLTAGE AND CURRENT PINS  26, 3, 4 VOP, IOP, ION, ION IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -        | 1     |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| VCOMM Voltage Bias. This pin can be used to create an input common-mode DC offset for ADC channel conversions.  VREF Voltage Reference. Reference voltage for the ADC. An external reference voltage can be connected to this pin when extremely high accuracy is required.  VOLTAGE AND CURRENT PINS  26, 3, 4 VOP, IOP, ION PloN IN Phase A Voltage and Current Analog Inputs  27, 5, 6 VIP, IIP, INP Phase B Voltage and Current Analog Inputs  28, 7, 8 VZP, IZP, IZN Phase C Voltage and Current Analog Inputs  1 VA Analog Input for Common Voltage 2 INP Analog Input for Neutral Current  CLOCK PINS  10 XTAL2 High-Frequency Crystal Input/Output. When using an external high-frequency crystal, the crystal oscillator circuit should be connected between XTAL1 and XTAL2. When using an externally driven clock (EXTCLK = 1), the clock should be input at XTAL1, with XTAL2 left unconnected.  11 IRQ Interrupt Request Output. This line is driven low by the device to indicate to the master that an unmasked interrupt has occurred.  13 SSEL Slave Select Input. This line is the active-low slave select input for the SPI interface.  14 SCLK Slave Clock Input. This line is the active-low slave select input for the SPI interface.  15 MOSI Master Out-Slave In Input. This line is used by the master to transmit data to the slave (the MAXQ3181) over the SPI interface.  16 MISO Master In-Slave Out Output. This line is used by the MAXQ3181 (the slave) to transmit data back to the master over the SPI interface.  18 CFP Pulse Output. Configurable to represent energy or RMS voltage or current.  Active-Low Reset Input/Output. An external master can reset the MAXQ3181 by driving this pin low. This pin includes a weak pullup resistor to allow for a combination of wired-OR external reset esteet, etc.). In this case, the RESET pin is held low by the device until it exits the reset state, then the RESET pin is released. |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| VREF Voltage Reference. Reference voltage for the ADC. An external reference voltage can be connected to this pin when extremely high accuracy is required.  VOLTAGE AND CURRENT PINS  26, 3, 4 VOP, IOP, ION ION IN Phase A Voltage and Current Analog Inputs  27, 5, 6 VIP, IIP, IIN IN IN Phase B Voltage and Current Analog Inputs  Phase C Voltage and Current Analog Inputs  Phase C Voltage and Current Analog Inputs  1 VN Analog Input for Common Voltage 2 INP Analog Input for Neutral Current  CLOCK PINS  10 XTAL2 High-Frequency Crystal Input/Output. When using an external high-frequency crystal, the crystal oscillator circuit should be connected between XTAL1 and XTAL2. When using an externally driven clock (EXTCLK = 1), the clock should be input at XTAL1, with XTAL2 left unconnected.  11 INFO INFO INFO INFO INFO INFO INFO INFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9        | AGND  |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| this pin when extremely high accuracy is required.  VOLTAGE AND CURRENT PINS  26, 3, 4 VOP, IOP, ION ION ION Phase A Voltage and Current Analog Inputs  27, 5, 6 V1P, I1P, I1N Phase B Voltage and Current Analog Inputs  28, 7, 8 V2P, I2P, I2P, I2N Phase C Voltage and Current Analog Inputs  1 VN Analog Input for Common Voltage 2 INP Analog Input for Neutral Current  CLOCK PINS  10 XTAL2 High-Frequency Crystal Input/Output. When using an external high-frequency crystal, the crystal oscillator circuit should be connected between XTAL1 and XTAL2. When using an externally driven clock (EXTCLK = 1), the clock should be input at XTAL1, with XTAL2 left unconnected.  11 IRQ Interrupt Request Output. This line is driven low by the device to indicate to the master that an unmasked interrupt has occurred.  13 SSEL Slave Select Input. This line is the clock input for the SPI interface.  14 SCLK Slave Clock Input. This line is used by the master to transmit data to the slave (the MAXQ3181) over the SPI interface.  15 MOSI Master Out-Slave In Input. This line is used by the MAXQ3181 (the slave) to transmit data back to the master over the SPI interface.  16 MISO Master In-Slave Out Output. This line is used by the MAXQ3181 (the slave) to transmit data back to the master over the SPI interface.  17 RESET RESET Pin in includes a weak pullup resistor to allow for a combination of wired-OR external reset sources. An RC circuit is not required for power-up, as this function is provided internally. This pin also acts as a reset output when the source of the reset is internal to the device (power-fail, watchdog reset, etc.). In this case, the RESET pin is held low by the device until it exits the reset state, then the RESET pin is released.                                                                                                                                                           | 23       | VCOMM |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 26, 3, 4 VOP, IOP, ION Phase A Voltage and Current Analog Inputs  27, 5, 6 V1P, I1P, I1N Phase B Voltage and Current Analog Inputs  28, 7, 8 V2P, I2P, I2P, I2P, I2P, I2P Phase C Voltage and Current Analog Inputs  1 VN Analog Input for Common Voltage 2 INP Analog Input for Neutral Current  CLOCK PINS  10 XTAL2 High-Frequency Crystal Input/Output. When using an external high-frequency crystal, the crystal oscillator circuit should be connected between XTAL1 and XTAL2. When using an externally driven clock (EXTCLK = 1), the clock should be input at XTAL1, with XTAL2 left unconnected.  11 IRO Interrupt Request Output. This line is driven low by the device to indicate to the master that an unmasked interrupt has occurred.  13 SSEL Slave Select Input. This line is the active-low slave select input for the SPI interface.  14 SCLK Slave Clock Input. This line is used by the master to transmit data to the slave (the MAXQ3181) over the SPI interface.  15 MOSI Master Out-Slave In Input. This line is used by the MAXQ3181 (the slave) to transmit data back to the master over the SPI interface.  16 MISO Master In-Slave Out Output. This line is used by the MAXQ3181 (the slave) to transmit data back to the master over the SPI interface.  21 Active-Low Reset Input/Output. An external master can reset the MAXQ3181 by driving this pin low. This pin includes a weak pullup resistor to allow for a combination of wired-OR external reset sources. An RC circuit is not required for power-up, as this function is provided internally. This pin also acts as a reset output when the source of the reset is internal to the device (power-fail, watchdog reset, etc.). In this case, the RESET pin is held low by the device until it exits the reset state, then the RESET pin is released.                                                                                                                             | 24       | VREF  | Voltage Reference. Reference voltage for the ADC. An external reference voltage can be connected to this pin when extremely high accuracy is required.                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 27, 5, 6 V1P, I1P, I1N Phase B Voltage and Current Analog Inputs  28, 7, 8 V2P, I2P, I2P, I2P, I2P Phase C Voltage and Current Analog Inputs  1 VN Analog Input for Common Voltage  2 INP Analog Input for Neutral Current  CLOCK PINS  10 XTAL2 High-Frequency Crystal Input/Output. When using an external high-frequency crystal, the crystal oscillator circuit should be connected between XTAL1 and XTAL2. When using an externally driven clock (EXTCLK = 1), the clock should be input at XTAL1, with XTAL2 left unconnected.  11 IRQ Interrupt Request Output. This line is driven low by the device to indicate to the master that an unmasked interrupt has occurred.  13 SSEL Slave Select Input. This line is the active-low slave select input for the SPI interface.  14 SCLK Slave Clock Input. This line is used by the master to transmit data to the slave (the MAXQ3181) over the SPI interface.  15 MOSI Master Out-Slave In Input. This line is used by the MAXQ3181 (the slave) to transmit data back to the master over the SPI interface.  16 MISO Master In-Slave Out Output. This line is used by the MAXQ3181 (the slave) to transmit data back to the master over the SPI interface.  21 Active-Low Reset Input/Output. An external master can reset the MAXQ3181 by driving this pin low. This pin includes a weak pullup resistor to allow for a combination of wired-OR external reset sources. An RC circuit is not required for power-up, as this function is provided internally. This pin also acts as a reset output when the source of the reset is internal to the device (power-fail, watchdog reset, etc.). In this case, the RESET pin is held low by the device until it exits the reset state, then the RESET pin is released.                                                                                                                                                                                                   |          | •     | VOLTAGE AND CURRENT PINS                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 28, 7, 8 V2P, I2P, I2N Phase C Voltage and Current Analog Inputs  1 VN Analog Input for Common Voltage  2 INP Analog Input for Neutral Current  CLOCK PINS  10 XTAL2 High-Frequency Crystal Input/Output. When using an external high-frequency crystal, the crystal oscillator circuit should be connected between XTAL 1 and XTAL 2. When using an externally driven clock (EXTCLK = 1), the clock should be input at XTAL 1, with XTAL 2 left unconnected.  11 Interrupt Request Output. This line is driven low by the device to indicate to the master that an unmasked interrupt has occurred.  13 SSEL Slave Select Input. This line is the active-low slave select input for the SPI interface.  14 SCLK Slave Clock Input. This line is the clock input for the SPI interface.  15 MOSI Master Out-Stave In Input. This line is used by the master to transmit data to the slave (the MAXQ3181) over the SPI interface.  16 MISO Master In-Slave Out Output. This line is used by the MAXQ3181 (the slave) to transmit data back to the master over the SPI interface.  17 Pulse Output. Configurable to represent energy or RMS voltage or current.  28 Active-Low Reset Input/Output. An external master can reset the MAXQ3181 by driving this pin low. This pin includes a weak pullup resistor to allow for a combination of wired-OR external reset sources. An RC circuit is not required for power-up, as this function is provided internally. This pin also acts as a reset output when the source of the reset is internal to the device (power-fail, watchdog reset, etc.). In this case, the RESET pin is held low by the device until it exits the reset state, then the RESET pin is released.                                                                                                                                                                                                                                                       | 26, 3, 4 | I .   | Phase A Voltage and Current Analog Inputs                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 1 VN Analog Input for Common Voltage 2 INP Analog Input for Neutral Current  CLOCK PINS  10 XTAL2 High-Frequency Crystal Input/Output. When using an external high-frequency crystal, the crystal oscillator circuit should be connected between XTAL1 and XTAL2. When using an externally driven clock (EXTCLK = 1), the clock should be input at XTAL1, with XTAL2 left unconnected.  12 IRQ Interrupt Request Output. This line is driven low by the device to indicate to the master that an unmasked interrupt has occurred.  13 SSEL Slave Select Input. This line is the active-low slave select input for the SPI interface.  14 SCLK Slave Clock Input. This line is the clock input for the SPI interface.  15 MOSI Master Out-Slave In Input. This line is used by the master to transmit data to the slave (the MAXQ3181) over the SPI interface.  16 MISO Master In-Slave Out Output. This line is used by the MAXQ3181 (the slave) to transmit data back to the master over the SPI interface.  17 Pulse Output. Configurable to represent energy or RMS voltage or current.  18 Active-Low Reset Input/Output. An external master can reset the MAXQ3181 by driving this pin low. This pin includes a weak pullup resistor to allow for a combination of wired-OR external reset sources. An RC circuit is not required for power-up, as this function is provided internally. This pin also acts as a reset output when the source of the reset is internal to the device (power-fail, watchdog reset, etc.). In this case, the RESET pin is held low by the device until it exits the reset state, then the RESET pin is released.                                                                                                                                                                                                                                                                                                                          | 27, 5, 6 |       | Phase B Voltage and Current Analog Inputs                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| CLOCK PINS    10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28, 7, 8 |       | Phase C Voltage and Current Analog Inputs                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| CLOCK PINS    10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1        | VN    | Analog Input for Common Voltage                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| High-Frequency Crystal Input/Output. When using an external high-frequency crystal, the crystal oscillator circuit should be connected between XTAL1 and XTAL2. When using an externally driven clock (EXTCLK = 1), the clock should be input at XTAL1, with XTAL2 left unconnected.  IRQ Interrupt Request Output. This line is driven low by the device to indicate to the master that an unmasked interrupt has occurred.  SSEL Slave Select Input. This line is the active-low slave select input for the SPI interface.  SCLK Slave Clock Input. This line is the clock input for the SPI interface.  MOSI Master Out-Slave In Input. This line is used by the master to transmit data to the slave (the MAXQ3181) over the SPI interface.  MISO Master In-Slave Out Output. This line is used by the MAXQ3181 (the slave) to transmit data back to the master over the SPI interface.  Pulse Output. Configurable to represent energy or RMS voltage or current.  Active-Low Reset Input/Output. An external master can reset the MAXQ3181 by driving this pin low. This pin includes a weak pullup resistor to allow for a combination of wired-OR external reset sources. An RC circuit is not required for power-up, as this function is provided internally. This pin also acts as a reset output when the source of the reset is internal to the device (power-fail, watchdog reset, etc.). In this case, the RESET pin is held low by the device until it exits the reset state, then the RESET pin is released.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2        | INP   | Analog Input for Neutral Current                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| oscillator circuit should be connected between XTAL1 and XTAL2. When using an externally driven clock (EXTCLK = 1), the clock should be input at XTAL1, with XTAL2 left unconnected.  ITRQ Interrupt Request Output. This line is driven low by the device to indicate to the master that an unmasked interrupt has occurred.  SSEL Slave Select Input. This line is the active-low slave select input for the SPI interface.  SCLK Slave Clock Input. This line is the clock input for the SPI interface.  MOSI Master Out-Slave In Input. This line is used by the master to transmit data to the slave (the MAXQ3181) over the SPI interface.  MISO Master In-Slave Out Output. This line is used by the MAXQ3181 (the slave) to transmit data back to the master over the SPI interface.  Pulse Output. Configurable to represent energy or RMS voltage or current.  Active-Low Reset Input/Output. An external master can reset the MAXQ3181 by driving this pin low. This pin includes a weak pullup resistor to allow for a combination of wired-OR external reset sources. An RC circuit is not required for power-up, as this function is provided internally. This pin also acts as a reset output when the source of the reset is internal to the device (power-fail, watchdog reset, etc.). In this case, the RESET pin is held low by the device until it exits the reset state, then the RESET pin is released.  NO CONNECTION PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |       | CLOCK PINS                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |