# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

The following document contains information on Cypress products. Although the document is marked with the name "Spansion" and "Fujitsu", the company that originally developed the specification, Cypress will continue to offer these products to new and existing customers.

### **Continuity of Specifications**

There is no change to this document as a result of offering the device as a Cypress product. Any changes that have been made are the result of normal document improvements and are noted in the document history page, where supported. Future revisions will occur when appropriate, and changes will be noted in a document history page.

### **Continuity of Ordering Part Numbers**

Cypress continues to support existing part numbers. To order these products, please use only the Ordering Part Numbers listed in this document.

### For More Information

Please contact your local sales office for additional information about Cypress products and solutions.

### **About Cypress**

Cypress (NASDAQ: CY) delivers high-performance, high-quality solutions at the heart of today's most advanced embedded systems, from automotive, industrial and networking platforms to highly interactive consumer and mobile devices. With a broad, differentiated product portfolio that includes NOR flash memories, F-RAM<sup>™</sup> and SRAM, Traveo<sup>™</sup> microcontrollers, the industry's only PSoC<sup>®</sup> programmable system-on-chip solutions, analog and PMIC Power Management ICs, CapSense<sup>®</sup> capacitive touch-sensing controllers, and Wireless BLE Bluetooth<sup>®</sup> Low-Energy and USB connectivity solutions, Cypress is committed to providing its customers worldwide with consistent innovation, best-in-class support and exceptional system value.

# ASSP for Power Management Applications of Ultra Mobile PC 6ch DC/DC Converter IC for LPIA Platform VR

# MB39C308

# DESCRIPTION

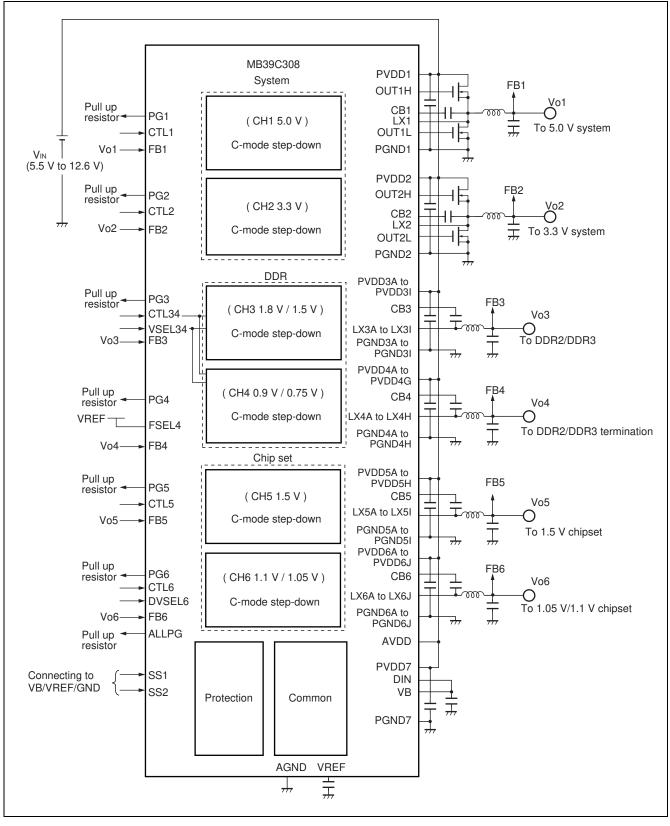

The MB39C308 is a 6ch DC/DC buck converter LSI, which integrates all of necessary power supplies for Ultra-Mobile PC powered by 2-cell Li-ion battery. And the MB39C308 uses current mode topology with N-channel synchronous rectification to realize high conversion efficiency.

The MB39C308 is the Power Management IC supporting the LPIA(Low Power Intel Architecture) which Intel Corporation proposes as the low power consumption platform for UMPC.

The CH1 and CH2 are flexible to adopt the output current capability by selection of external FETs and easy to optimize efficiency. The CH3, CH4, CH5 and CH6 integrate the switching FETs capable of high current for down-sizing the power supply solution.

The MB39C308 uses Fujitsu's LDMOS process technology and supplies all power without dispersing power from a lithium-ion battery.

: 5.5 V to 12.6 V

## ■ FEATURES

- Input voltage range

- Topology

- : Current Mode

- Integrated FET Driver for external MOSFETs : CH1, CH2

- Integrated Switching MOSFETs : CH3, CH4, CH5, CH6

- Fixed Preset Output Voltage

- : CH1, CH2, CH5 : CH3, CH4, CH6

- Selectable Preset Output Voltage : CH3

| Channel | Output<br>voltage | Output<br>current | Remarks                    |

|---------|-------------------|-------------------|----------------------------|

| CH1     | 5 V               | 2 A*              | _                          |

| CH2     | 3.3 V             | 4.5 A*            | —                          |

| CH3     | 1.8 V/1.5 V       | Max : 2.7 A       | DDR2/DDR3 are selectable.  |

| CH4     | 0.9 V/0.75 V      | Max : 1.5 A       |                            |

| CH5     | 1.5 V             | Max : 2.5 A       | —                          |

| CH6     | 1.1 V/1.05 V      | Max : 3.5 A       | Two values are selectable. |

\* : It is the reference value at the typical EVB.

(Continued)

• PWM switching frequency

: 0.7 MHz (CH4 : 0.7 MHz/0.35 MHz)

- Various protection

- Over current protection (OCP) Input over voltage protection (IVP)

- Output short circuit protection (SCP) Under voltage lock out protection (UVLO)

- Output over voltage protection (OVP) Over temperature protection (OTP)

- POWERGOOD function

- Soft start function independent from output loads.

- Soft stop function independent from output loads.

- High conversion efficiency in wide range of load current.

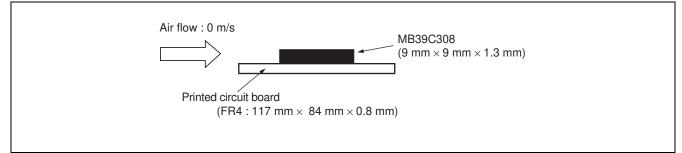

- Packaged in a compact package : PFBGA-208 (9.00 mm × 9.00 mm × 1.30 mm)

## ■ APPLICATIONS

- UMPC (Ultra Mobile PC)

- MID (Mobile Internet Device)

- Mobile equipment etc.

# MB39C308

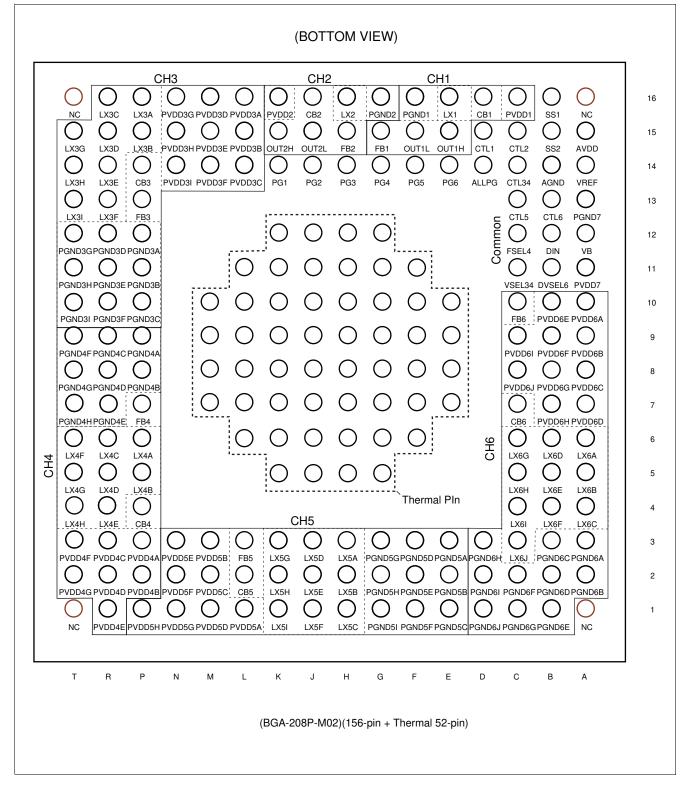

### ■ PIN ASSIGNMENT

# ■ PIN DESCRIPTIONS

| Block | Pin Name               | I/O | Description                                                      |

|-------|------------------------|-----|------------------------------------------------------------------|

|       | FB1                    | Ι   | CH1 Error amplifier input pin, being connected to output of CH1. |

|       | PVDD1                  | _   | Power supply pin of the CH1 output block.                        |

|       | CB1                    | 0   | Internal power supply pin of the CH1 gate driver block.          |

| CH1   | LX1                    | _   | CH1 inductor connection pin.                                     |

|       | OUT1H                  | 0   | CH1 High-side N-ch FET drive output pin.                         |

|       | OUT1L                  | 0   | CH1 Low-side N-ch FET drive output pin.                          |

|       | PGND1                  |     | Ground pin of the CH1 output block.                              |

|       | FB2                    | Ι   | CH2 Error amplifier input pin, being connected to output of CH2. |

|       | PVDD2                  | _   | Power supply pin of the CH2 output block.                        |

|       | CB2                    | 0   | Internal power supply pin of the CH2 gate driver block.          |

| CH2   | LX2                    | _   | CH2 inductor connection pin.                                     |

|       | OUT2H                  | 0   | CH2 High-side N-ch FET drive output pin.                         |

|       | OUT2L                  | 0   | CH2 Low-side N-ch FET drive output pin.                          |

|       | PGND2                  |     | Ground pin of the CH2 output block.                              |

|       | FB3                    | Ι   | CH3 Error amplifier input pin, being connected to output of CH3. |

|       | PVDD3A<br>to<br>PVDD3I |     | Power supply pins of the CH3 output block.                       |

|       | CB3                    | 0   | Internal power supply pin of the CH3 gate driver block.          |

| CH3   | LX3A<br>to<br>LX3I     |     | CH3 inductor connection pins.                                    |

|       | PGND3A<br>to<br>PGND3I |     | Ground pins of the CH3 output block.                             |

|       | FB4                    | Ι   | CH4 Error amplifier input pin, being connected to output of CH4. |

|       | PVDD4A<br>to<br>PVDD4G |     | Power supply pins of the CH4 output block.                       |

|       | CB4                    | 0   | Internal power supply pin of the CH4 gate driver block.          |

| CH4   | LX4A<br>to<br>LX4H     |     | CH4 inductor connection pins.                                    |

|       | PGND4A<br>to<br>PGND4H |     | Ground pins of the CH4 output block.                             |

# MB39C308

| Block  | Pin Name               | I/O | Description                                                                                                                           |

|--------|------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------|

|        | FB5                    | Ι   | CH5 Error amplifier input pin, being connected to output of CH5.                                                                      |

|        | PVDD5A<br>to<br>PVDD5H |     | Power supply pins of the CH5 output block.                                                                                            |

|        | CB5                    | 0   | Internal power supply pin of the CH5 gate driver block.                                                                               |

| CH5    | LX5A<br>to<br>LX5I     |     | CH5 inductor connection pins.                                                                                                         |

|        | PGND5A<br>to<br>PGND5I |     | Ground pins of the CH5 output block.                                                                                                  |

|        | FB6                    | Ι   | CH6 Error amplifier input pin, being connected to output of CH6.                                                                      |

|        | PVDD6A<br>to<br>PVDD6J |     | Power supply pins of the CH6 output block.                                                                                            |

|        | CB6                    | 0   | Internal power supply pin of the CH6 gate driver block.                                                                               |

| CH6    | LX6A<br>to<br>LX6J     |     | CH6 inductor connection pins.                                                                                                         |

|        | PGND6A<br>to<br>PGND6J |     | Ground pins of the CH6 output block.                                                                                                  |

|        | CTL1                   | Ι   | CH1 Control input pin. (L : Standby / H : Normal operation)                                                                           |

|        | CTL2                   | Ι   | CH2 Control input pin. (L : Standby / H : Normal operation)                                                                           |

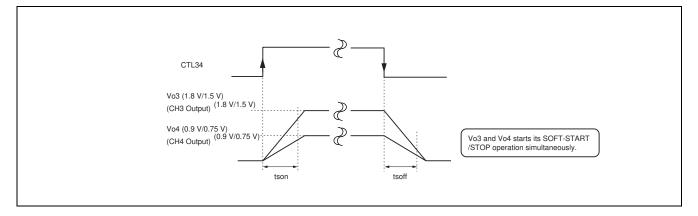

|        | CTL34                  | Ι   | CH3 and CH4 control input pin. (L: Standby / H: Normal operation)                                                                     |

|        | CTL5                   | Ι   | CH5 Control input pin. (L : Standby / H : Normal operation)                                                                           |

|        | CTL6                   | Ι   | CH6 Control input pin. (L : Standby / H : Normal operation)                                                                           |

|        | PG1                    | 0   | CH1 POWERGOOD output pin. (N-ch MOS open drain output)                                                                                |

|        | PG2                    | 0   | CH2 POWERGOOD output pin. (N-ch MOS open drain output)                                                                                |

| Common | PG3                    | 0   | CH3 POWERGOOD output pin. (N-ch MOS open drain output)                                                                                |

|        | PG4                    | 0   | CH4 POWERGOOD output pin. (N-ch MOS open drain output)                                                                                |

|        | PG5                    | 0   | CH5 POWERGOOD output pin. (N-ch MOS open drain output)                                                                                |

|        | PG6                    | 0   | CH6 POWERGOOD output pin. (N-ch MOS open drain output)                                                                                |

|        | ALLPG                  | 0   | POWERGOOD output pin (The ALLPG pin outputs "H", When channels CH3, CH4, CH5 and CH6 are the power good).                             |

|        | FSEL4                  | Ι   | CH4 switching frequency setting pin.<br>FSEL4 = "H" : 700 kHz<br>FSEL4 = "L" : 0.35 MHz (Shown in the "■ ELECTRICAL CHARACTERISTICS") |

# MB39C308

| Block  | Pin Name | I/O | Description                                                                                                                                             |

|--------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | VSEL34   | I   | Preset output voltage setting pin for CH3/CH4.<br>VSEL34 = "H" : Vout_CH3 =1.8 V, Vout_CH4 = 0.9 V<br>VSEL34 = "L" : Vout_CH3 =1.5 V, Vout_CH4 = 0.75 V |

|        | DVSEL6   | I   | Preset output voltage setting pin for CH6 dynamically.<br>DVSEL6 = "H" : Vout_CH6 = 1.1 V<br>DVSEL6 = "L" : Vout_CH6 = 1.05 V                           |

|        | SS1      |     | Soft-Start and Soft-Stop time setting pin (Shown in the "■ DESCRIPTION OF                                                                               |

| SS2    | SS2      | Ι   | SOFT-START AND SOFT-STOP OPERATION • Soft-Start/Soft-Stop time (tson/tsoff) Setting Conditions").                                                       |

| Common | VB       | 0   | Bias voltage output pin for bootstrap and low-side N-ch gate driver of all channels.                                                                    |

|        | DIN      | Ι   | Bias voltage input pin for bootstrap.<br>DIN pin should be connected with VB pin.<br>(Shown in the "■ BLOCK DIAGRAM")                                   |

|        | PVDD7    |     | Power supply pin of VB block.                                                                                                                           |

|        | PGND7    |     | Ground pin of VB block.                                                                                                                                 |

|        | AVDD     |     | Power supply pin for common block.                                                                                                                      |

|        | VREF     | 0   | Reference voltage output pin.                                                                                                                           |

|        | AGND     |     | Ground pin of common block.                                                                                                                             |

### BLOCK DIAGRAM

### Used in 2-cell Li-lon power system

### **CURRENT MODE TOPOLOGY**

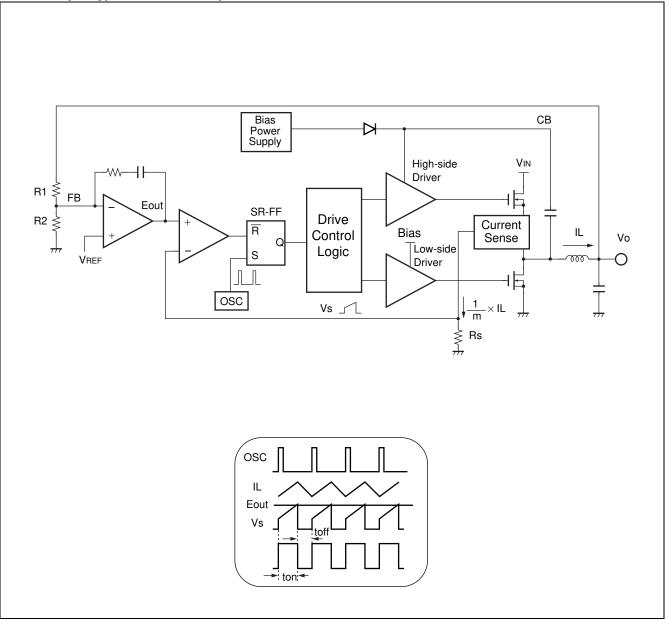

A DC/DC regulation block of Current-mode (C-mode) is illustrated in the "• DC/DC topology, Current mode operation".

In this C-mode, the High-side FET is turned ON while the SR-FF is set at every clock cycle generated by on chip oscillator. During ON period (ton), the current is supplied by  $V_{IN}$ , then Inductor current(IL) is increased. Besides a current (IL/m), which senses the inductor current(IL), flows across a resistor (Rs) then the resister voltage (Vs) is increased. When the Vs reaches Eout , which is an output of the Error amp, the SR-FF is reset and the High-side FET is turned OFF (toff) until the next rising clock comes.

The voltage regulation is done by controlling a peak current of the inductor current (IL).

#### • DC/DC topology, Current mode operation

### ABSOLUTE MAXIMUM RATINGS

| Parameter                     | Symbol | Condition                | Rat                   | ing    | Unit |

|-------------------------------|--------|--------------------------|-----------------------|--------|------|

| Parameter                     | Symbol | Condition                | Min                   | Max    | Unit |

| Power supply voltage          | Vdd    | AVDD, PVDD1 to PVDD7 pin | -0.3                  | + 13.5 | V    |

| CB voltage                    | Vсв    | CB1 to CB6 pin           | -0.3                  | + 18.5 | V    |

| LX voltage                    | VLX    | LX1 to LX6 pin           | -0.3                  | Vdd    | V    |

| CB to LX voltage              | VCBLX  | CB pin to LX pin         | -0.3                  | + 7    | V    |

| OUTH voltage                  | Vouth  | OUT1H, OUT2H pin         | $V_{\text{LX}} - 0.3$ | Vсв    | V    |

| OUTL voltage                  | Voutl  | OUT1L, OUT2L pin         | -0.3                  | + 7    | V    |

| DIN voltage                   | VDIN   | DIN pin                  | -0.3                  | + 7    | V    |

| VB voltage                    | Vvв    | VB pin                   | -0.3                  | + 7    | V    |

| VREF voltage                  | VVREF  | VREF pin                 | -0.3                  | + 7    | V    |

| CTL voltage                   | VCTL   | CTL1 to CTL6 pin         | -0.3                  | + 13.5 | V    |

| VSEL voltage                  | VSEL   | VSEL34, DVSEL6 pin       | -0.3                  | + 7    | V    |

| FSEL voltage                  | VFSEL  | FSEL4 pin                | -0.3                  | + 7    | V    |

| FB voltage                    | VFB    | FB1 to FB6 pin           | -0.3                  | + 7    | V    |

| PG voltage                    | Vpg    | PG1 to PG6, ALLPG pin    | -0.3                  | + 7    | V    |

| SS voltage                    | Vss    |                          | -0.3                  | + 7    | V    |

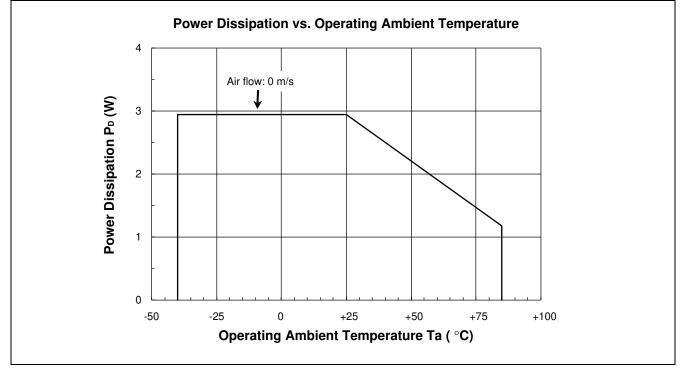

| Deckage newer discinction     | D-     | Ta ≤ + 25 °C             |                       | 2940*  | mW   |

| Package power dissipation     | Po     | Ta = + 85 °C             | —                     | 1180*  | mW   |

| Operating ambient temperature | Та     | _                        | -40                   | + 85   | °C   |

| Storage temperature           | Тѕтс   | —                        | -55                   | + 125  | °C   |

\* : See the diagram of "■ TYPICAL CHARACTERISTICS • Maximum Power Dissipation vs. Operating Ambient Temperature", for the package power dissipation of Ta from + 25 °C to + 85 °C.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

WARNING: The use of negative voltage below –0.3 Volts on the GND pins (AGND, PGND1 to PGND7) may activate parasitic transistors on the silicon, which can introduce abnormal operation. Connecting the LX pin to either VDD pins (AVDD, PVDD1 to PVDD7) or GND pins (AGND, PGND1 to PGND7) directly may cause permanently damage to the device.

# ■ RECOMMENDED OPERATING CONDITIONS

| <b>_</b>             |        | <b>a</b>                                                                                    |     | Value                                               |      |      |

|----------------------|--------|---------------------------------------------------------------------------------------------|-----|-----------------------------------------------------|------|------|

| Parameter            | Symbol | Condition                                                                                   | Min | Тур                                                 | Max  | Unit |

| Power supply voltage | Vdd    | AVDD = PVDD1 to PVDD7 pin                                                                   | 5.5 |                                                     | 12.6 | V    |

| Input capacitor      | CIN    | VDD to GND pin                                                                              |     | 4.7                                                 | —    | μF   |

| CB to LX capacitor   | Ссв    | CB to LX pin                                                                                | _   | 0.1                                                 |      | μF   |

|                      | L1     | LX1 pin                                                                                     | _   | 3.3                                                 |      | μH   |

|                      | L2     | LX2 pin                                                                                     |     | 3.3                                                 |      | μH   |

|                      | L3     | LX3 pin                                                                                     |     | 1.5                                                 |      | μH   |

| LX inductor          | L4     | LX4 pin, FSEL4 pin = H<br>fosc = 0.7 MHz                                                    |     | 1.5                                                 |      |      |

|                      | L4     | LX4 pin, FSEL4 pin = L<br>fosc = 0.35 MHz                                                   |     | 1.5                                                 |      | μH   |

|                      | L5     | LX5 pin                                                                                     |     | 1.5                                                 |      | μH   |

|                      | L6     | LX6 pin                                                                                     |     | 1.5                                                 | —    | μH   |

|                      | lo1    | Vo1 (5 V), DC, when $Ron_{H1} = 32 m\Omega$                                                 |     | 1                                                   | 2*   | Α    |

|                      | lo2    | Vo2 (3.3 V), DC, when $Ron_{H2} = 16 m\Omega$                                               | _   | 2.25                                                | 4.5* | Α    |

| Output current       | lo3    | Vo3 (1.8 V/1.5 V), DC                                                                       |     | 1.35                                                | 2.7* | A    |

|                      | lo4    | Vo4 (0.9 V/0.75 V), DC                                                                      |     | 1                                                   | 1.5* | Α    |

|                      | lo5    | Vo5 (1.5 V), DC                                                                             |     | 1.25                                                | 2.5* | Α    |

|                      | lo6    | Vo6 (1.1 V/1.05 V), DC                                                                      |     | 1.75                                                | 3.5* | A    |

|                      | Co1    | Vo1 (5 V), when Ron <sub>H1</sub> = 32 m $\Omega$ ,<br>L = 3.3 $\mu$ H, SS1,SS2 pin = GND   |     | 1.25     2.5*       1.75     3.5*       100     300 | μF   |      |

|                      | Co2    | Vo2 (3.3 V), when Ron <sub>H1</sub> = 16 m $\Omega$ ,<br>L = 3.3 $\mu$ H, SS1,SS2 pin = GND |     | 100                                                 | 700  | μF   |

|                      | Co3    | Vo3 (1.8 V), when L = 1.5 $\mu$ H, SS1, SS2 pin = GND                                       |     | 100                                                 | 300  | μF   |

|                      | Co4    | Vo4 (0.9 V), when L = 1.5 $\mu$ H, SS1, SS2 pin = GND                                       |     | 100                                                 | 500  | μF   |

|                      | Co5    | Vo5 (1.5 V), when L = 1.5 μH,<br>SS1, SS2 pin = GND                                         |     | 100                                                 | 300  | μF   |

|                      | Co6    | Vo6 (1.05 V), when L = 1.5 μH,<br>SS1, SS2 pin = GND                                        |     | 200                                                 | 500  | μF   |

|                      | RonH1  | CH1 High-side FET connected to<br>OUT1H pin                                                 |     | 32                                                  |      | mΩ   |

| External FET         | RonL1  | CH1 Low-side FET connected to<br>OUT1L pin                                                  |     | 32                                                  |      | mΩ   |

| On-resistance        | RonH2  | CH2 High-side FET connected to<br>OUT2H pin                                                 | 12  | 16                                                  | 20   | mΩ   |

|                      | RonL2  | CH2 Low-side FET connected to<br>OUT2L pin                                                  |     | 16                                                  |      | mΩ   |

| Parameter             | Symbol | Condition             |     | Value |      | Unit |

|-----------------------|--------|-----------------------|-----|-------|------|------|

| Farameter             | Symbol | Condition             | Min | Тур   | Max  | Unit |

| VB output capacitor   | Сув    | VB pin                | —   | 1     | —    | μF   |

| VREF output capacitor | CVREF  | VREF pin              |     | 4.7   |      | μF   |

| VREF output current   | IVREF  | VREF pin              | - 1 |       | 0    | mA   |

| PG input voltage      | Vpg    | PG1 to PG6, ALLPG pin | —   | _     | 6    | V    |

| PG sink current       | IPG    | PG1 to PG6, ALLPG pin | —   |       | 2    | mA   |

| CTL input voltage     | Vctl   | CTL1 to CTL6 pin      |     |       | AVDD | V    |

| VSEL input voltage    | VSEL   | VSEL34, DVSEL6 pin    | —   | _     | 6    | V    |

| FSEL input voltage    | VFSEL  | FSEL4 pin             |     |       | 6    | V    |

| SS input voltage      | Vss    | SS1, SS2 pin          |     |       | Vв   | V    |

(Continued)

\* : The MB39C308 is designed with assumed operating conditions, which is 60% of the maximum output current on the each channel and being operated with recommended input voltage range.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

# ■ ELECTRICAL CHARACTERISTICS

(Ta =  $+25 \circ$ C, AVDD = PVDD1 to PVDD7 = 7.2 V)

| Dever                                | -                       | Cumhal       | Condition                                           |      | Value   |      | Unit |

|--------------------------------------|-------------------------|--------------|-----------------------------------------------------|------|---------|------|------|

| Param                                | leter                   | Symbol       | Condition                                           | Min  | Тур     | Max  | Unit |

|                                      | Reference<br>voltage    | VREF         | VREF pin = 0 mA                                     | 2.45 | 2.5     | 2.55 | V    |

| Reference voltage<br>block<br>[VREF] | Line regulation         | VREF<br>Line | AVDD pin = 5.5 V to 12.6 V                          | -10  | _       | + 10 | mV   |

| [****                                | Load regulation         | VREF<br>Load | VREF pin = 0 mA to $-1$ mA                          | -15  | _       | + 15 | mV   |

| Bias voltage block                   | Bias voltage            | Vvв          | $5.5 V \le AVDD \le 12.6 V$<br>VB pin = 0 mA        | 4.8  | 5       | 5.2  | V    |

| [VB]                                 | Load regulation         | VB<br>Load   | VB pin = 0 mA to $-1$ mA                            | -15  | _       | + 15 | mV   |

| Under-voltage lockout protection     | Threshold voltage       | VTLH         | AVDD pin                                            | 4.5  | 5.0     | 5.2  | V    |

| circuit block<br>[ UVLO ]            | Hysteresis<br>width     | Vнu          | AVDD pin                                            | 0.05 | 0.1     | 0.4  | V    |

| Over-temperature protection circuit  | Shutdown<br>temperature | Тотрн        |                                                     | _    | + 150*1 |      | °C   |

| block<br>[OTP]                       | Hysteresis<br>width     | Тн           |                                                     | _    | + 25*1  |      | °C   |

| Input over voltage                   | Threshold voltage       | VIVPH        | AVDD pin                                            | 12.6 | 13.0    | 13.4 | V    |

| protection circuit<br>block          | Release<br>voltage      | VIVPL        | AVDD pin                                            | 12.5 | 12.85   | 13.3 | V    |

| [IVP]                                | Hysteresis<br>width     | Vні          | AVDD pin                                            | _    | 0.15    |      | V    |

| Oscillator block                     | Oscillation             | fosc         | CH1 to CH3, CH5, CH6<br>CH4 : FSEL4 pin = "H" Level | 0.56 | 0.7     | 0.84 | MHz  |

| [OSC]                                | frequency*2             |              | CH4 : FSEL4 pin = "L" Level                         | 0.28 | 0.35    | 0.42 | MHz  |

|                                      | Output on level         | VIH          | CTL1 to CTL6 pin                                    | 2    |         |      | V    |

| Control block                        | Output off level        | VIL          | CTL1 to CTL6 pin                                    |      |         | 0.8  | V    |

| [CTL1 to CTL6]                       |                         | Істін        | CTL1 to CTL6 pin = 3 V                              | 23   | 30      | 43   | μA   |

|                                      | Input current           | ICTLL        | CTL1 to CTL6 pin = 0 V                              | —    |         | 1    | μA   |

| De                                                                                                                                          |                              | Cumhal                      | Condition                                                                                                                                                  |                                       | Value        |              | ,<br>11 |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------|--------------|---------|

| Pa                                                                                                                                          | rameter                      | Symbol                      | Condition                                                                                                                                                  | Min                                   | Тур          | Max          | Unit    |

|                                                                                                                                             | VSEL34, "H" level            | Vlgh                        | VSEL34, DVSEL6 pin                                                                                                                                         | 2                                     |              |              | V       |

| Output voltage                                                                                                                              | VSEL34, "L" level            | Vlgl                        | VSEL34, DVSEL6 pin                                                                                                                                         |                                       |              | 0.8          | V       |

| select block<br>[VSEL34,                                                                                                                    |                              | ISELH                       | VSEL34, DVSEL6<br>pin = 3 V                                                                                                                                | 23                                    | 30           | 43           | μA      |

| Output voltage<br>select block<br>[VSEL34,<br>DVSEL6]<br>Power good<br>detection<br>circuit block<br>[PG1 to PG6,<br>ALLPG]<br>Common block | Input current                | ISELL                       | VSEL34, DVSEL6<br>pin = 0 V                                                                                                                                |                                       | _            | 1            | μA      |

|                                                                                                                                             | Low side threshold voltage   | Vpgl                        | FB1 to FB6 pin _⊼<br>PG1 to PG6 pin                                                                                                                        | Vo ×<br>0.85                          | Vo ×<br>0.9  | Vo ×<br>0.95 | V       |

| Power good                                                                                                                                  | High side threshold voltage  | Vpgh                        | FB1 to FB6 pin 구<br>PG1 to PG6 pin                                                                                                                         | Vo ×<br>1.05                          | Vo ×<br>1.1  | Vo ×<br>1.15 | V       |

| circuit block                                                                                                                               | Hysteresis width             | Vн                          | _                                                                                                                                                          |                                       | Vo ×<br>0.03 |              | V       |

| ALLPG]                                                                                                                                      | PG output low voltage        | Vol                         | PG1 to PG6, ALLPG pin = 1 mA                                                                                                                               | -     0.1     0.3       -     -     1 | V            |              |         |

|                                                                                                                                             |                              | PG1 to PG6, ALLPG pin = 6 V |                                                                                                                                                            | _                                     | 1            | μA           |         |

| Common block                                                                                                                                | AVDD standby<br>current      | lavdds                      | CTL1 to CTL6 pin = 0 V,<br>AVDD pin = $12.6$ V                                                                                                             |                                       | _            | 1            | μA      |

|                                                                                                                                             | AVDD power supply<br>current | lavdd                       | CTL1 to CTL6 pin = 3 V                                                                                                                                     |                                       | 0.25         |              | mA      |

|                                                                                                                                             | CH1 output voltage           | Vo1                         | FB1 pin                                                                                                                                                    | 4.75                                  | 5            | 5.25         | V       |

|                                                                                                                                             | PVDD1 standby<br>current     | PVDD1S                      | CTL1 pin = 0 V,<br>PVDD1 pin = 12.6 V                                                                                                                      |                                       | _            | 15           | μA      |

|                                                                                                                                             |                              | ηL1                         | 0.05 × lo (Max) < lo <<br>0.3 × lo (Max)                                                                                                                   | 87* <sup>3</sup>                      | _            |              | %       |

|                                                                                                                                             | CH1 efficiency               | ηT1                         | 0.3 × lo (Max) < lo <<br>0.6 × lo (Max)                                                                                                                    | 92* <sup>3</sup>                      | _            | _            | %       |

| CH1 block                                                                                                                                   |                              | ηF1                         | $0.6 \times lo (Max) < lo < lo (Max)$                                                                                                                      | 92* <sup>3</sup>                      |              |              | %       |

| [CH1]                                                                                                                                       | OUT1H source<br>current      | IsourceH1                   | $\begin{array}{l} \text{Duty} \leq 5\%, \ \text{CB1 pin} = 5 \ \text{V}, \\ \text{LX1 pin} = 0 \ \text{V}, \\ \text{OUT1H pin} = 0 \ \text{V} \end{array}$ | _                                     | -400*1       |              | mA      |

|                                                                                                                                             | OUT1H sink current           | lsinkH1                     | $\begin{array}{l} \text{Duty} \leq 5\%,  \text{CB1 pin} = 5  \text{V}, \\ \text{LX1 pin} = 0  \text{V}, \\ \text{OUT1H pin} = 5  \text{V} \end{array}$     |                                       | 400*1        |              | mA      |

|                                                                                                                                             | OUT1L source<br>current      | IsourceN1                   | Duty $\leq$ 5%, VB pin = 5 V,<br>LX1 pin = 0 V,<br>OUT1L pin = 0 V                                                                                         |                                       | -400*1       |              | mA      |

(Ta =  $+25 \circ$ C, AVDD = PVDD1 to PVDD7 = 7.2 V)

$(Ta = +25 \circ C, AVDD = PVDD1 \text{ to } PVDD7 = 7.2 \text{ V})$

|                    | Deverater                         | Cumbel           | Condition                                                           |                  | Value                                                  |                   | Linit |

|--------------------|-----------------------------------|------------------|---------------------------------------------------------------------|------------------|--------------------------------------------------------|-------------------|-------|

|                    | Parameter                         | Symbol           | Condition                                                           | Min              | Тур                                                    | Max               | Unit  |

|                    | OUT1L sink current                | lsinkN1          | Duty $\leq$ 5%, VB pin = 5 V,<br>LX1 pin = 0 V,<br>OUT1L pin = 5 V  | _                | 400*1                                                  |                   | mA    |

|                    | OUT1H on resistance               | Roн1             | OUT1H pin = -15 mA                                                  | _                | 12                                                     | 18                | Ω     |

|                    | OUT IN ON resistance              | Rol1             | OUT1H pin = 15 mA                                                   | —                | 12                                                     | 18                | Ω     |

|                    | OUT1L on resistance               | Roн1             | OUT1L pin = -15 mA                                                  |                  | 12                                                     | 18                | Ω     |

| CH1 block          |                                   | Rol1             | OUT1L pin = 15 mA                                                   | —                | 12                                                     | 18                | Ω     |

| [CH1]              | Vo1 output over voltage threshold | Vo1              | FB1 pin                                                             | 5.9*1            | 6* <sup>1</sup>                                        | 6.1* <sup>1</sup> | V     |

|                    | Vo1 over current limit            | IOCP1            | lo1<br>Ronн1 = 32 mΩ, L = 3.3 μH                                    | 3.4*1            | 4.0 <sup>*1</sup>                                      | 4.6*1             | А     |

|                    | FB1 input resistance              | R <sub>FB1</sub> | FB1 pin                                                             | —                | 340                                                    |                   | kΩ    |

|                    | Soft Start time                   | SS1              | FB1 pin<br>SS1 = SS2 = AGND pin                                     | 1.19             | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | ms                |       |

|                    | CH2 output voltage                | Vo2              | FB2 pin                                                             | 3.135            | 3.3                                                    | 3.465             | V     |

|                    | PVDD2 standby current             | PVDD2S           | CTL2 pin = 0 V,<br>PVDD2 pin = 12.6 V                               | _                |                                                        | 15                | μA    |

|                    |                                   | ηL2              | 0.05 × lo (Max) < lo <<br>0.3 × lo (Max)                            | 87* <sup>3</sup> |                                                        |                   | %     |

|                    | CH2 efficiency                    | ηT2              | 0.3 × lo (Max) < lo <<br>0.6 × lo (Max)                             | 92* <sup>3</sup> |                                                        | _                 | %     |

|                    |                                   | ηF2              | $0.6 \times lo (Max) < lo < lo (Max)$                               | 92* <sup>3</sup> |                                                        |                   | %     |

|                    | OUT2H source current              | IsourceH2        | Duty $\leq$ 5%, CB2 pin = 5 V,<br>LX2 pin = 0 V,<br>OUT2H pin = 0 V | _                | - 400                                                  |                   | mA    |

| CH2 block<br>[CH2] | OUT2H sink current                | lsinkH2          | Duty $\leq$ 5%, CB2 pin = 5 V,<br>LX2 pin = 0 V,<br>OUT2H pin = 5 V | _                | 400                                                    |                   | mA    |

|                    | OUT2L source current              | IsourceN2        | Duty $\leq$ 5%, VB pin = 5 V,<br>LX2 pin = 0 V,<br>OUT2L pin = 0 V  | _                | - 400                                                  |                   | mA    |

|                    | OUT2L sink current                | lsinkN2          | Duty $\leq$ 5%, VB pin = 5 V,<br>LX2 pin = 0 V,<br>OUT2L pin = 5 V  |                  | 400                                                    |                   | mA    |

|                    | OUT2H on resistance               | <b>R</b> он2     | OUT2H pin = -15 mA                                                  |                  | 12                                                     | 18                | Ω     |

|                    |                                   | Rol2             | OUT2H pin = 15 mA                                                   |                  | 12                                                     | 18                | Ω     |

|                    | OUT2L on resistance               | Roн2             | OUT2L pin = -15 mA                                                  |                  | 12                                                     | 18                | Ω     |

|                    |                                   | Rol2             | OUT2L pin = 15 mA                                                   | —                | 12                                                     | 18                | Ω     |

|                    | _                                 |         | (1a - + 25 0, A                                                                                                                                                                                  |                  | Value            |         | ,    |

|--------------------|-----------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|---------|------|

|                    | Parameter                         | Symbol  | Condition                                                                                                                                                                                        | Min              | Тур              | Max     | Unit |

|                    | Vo2 output over voltage threshold | Vo2     | FB2 pin                                                                                                                                                                                          | 3.894*1          | 3.96*1           | 4.026*1 | V    |

| CH2 block          | Vo2 over current limit            | Іоср2   | $  lo2 \\ Ron_{H1} = 16 \ m\Omega, \ L = 3.3 \ \mu H $                                                                                                                                           | 6.7*1            | 7.9*1            | 9.0*1   | А    |

| [CH2]              | FB2 input resistance              | Rfb2    | FB2 pin                                                                                                                                                                                          |                  | 220              |         | kΩ   |

|                    | Soft start time                   | SS2     | FB2 pin<br>SS1 = SS2 = AGND pin                                                                                                                                                                  | 1.19             | 1.4              | 1.61    | ms   |

|                    | CH3 output voltage                | Vo3     | VSEL34 = "H" Level,<br>FB3 pin                                                                                                                                                                   | 1.71             | 1.8              | 1.89    | V    |

|                    | Chi Soliput Voltage               | V03     | VSEL34 = "L" Level,<br>FB3 pin                                                                                                                                                                   | 1.425            | 1.5              | 1.575   | V    |

|                    | High-side FET<br>on-resistance    | Ronhз   | LX3 pin = $-100$ mA,<br>V <sub>GS</sub> = 5 V                                                                                                                                                    |                  | 65* <sup>1</sup> |         | mΩ   |

|                    | Low-side FET<br>on-resistance     | Ronl3   | LX3 pin = 100 mA,<br>$V_{GS} = 5 V$                                                                                                                                                              |                  | 40*1             | _       | mΩ   |

|                    | PVDD3 standby current             | Ipvdd3s | CTL34 pin = 0 V,<br>PVDD3 pin = 12.6 V                                                                                                                                                           |                  | _                | 15      | μA   |

|                    |                                   | ηL31    | VSEL34 pin = "H" Level,<br>Vo3 = 1.8 V<br>0.05 × lo (Max) < lo <<br>0.3 × lo (Max)                                                                                                               | 85* <sup>3</sup> |                  |         | %    |

| CH3 block<br>[CH3] |                                   | ηL32    | VSEL34 pin = "L" Level,<br>Vo3 = 1.5 V<br>0.05 × lo (Max) < lo <<br>0.3 × lo (Max)                                                                                                               | 82* <sup>3</sup> |                  |         | %    |

|                    |                                   | ηT31    | VSEL34 pin = "H" Level,<br>Vo3 = 1.8 V<br>0.3 × lo (Max) < lo <<br>0.6 × lo (Max)                                                                                                                | 87* <sup>3</sup> |                  |         | %    |

|                    | CH3 efficiency                    | ηT32    | $\begin{array}{l} \text{VSEL34 pin} = \text{``L'' Level,} \\ \text{Vo3} = 1.5 \text{ V} \\ 0.3 \times \text{lo} \ (\text{Max}) < \text{lo} < \\ 0.6 \times \text{lo} \ (\text{Max}) \end{array}$ | 85* <sup>3</sup> |                  |         | %    |

|                    |                                   | ηF31    | VSEL34 pin = "H" Level,<br>Vo3 = 1.8 V<br>0.6 × lo (Max) < lo < lo<br>(Max)                                                                                                                      | 87* <sup>3</sup> |                  |         | %    |

|                    |                                   | ηF32    | $\begin{array}{l} \text{VSEL34 pin} = \text{``L'' Level}, \\ \text{Vo3} = 1.5 \text{ V} \\ 0.6 \times \text{ lo (Max)} < \text{ lo < lo} \\ (\text{Max}) \end{array}$                            | 85* <sup>3</sup> |                  |         | %    |

$(Ta = +25 \circ C, AVDD = PVDD1 \text{ to } PVDD7 = 7.2 \text{ V})$

(Ta =  $+25 \circ$ C, AVDD = PVDD1 to PVDD7 = 7.2 V)

|                    | <b>_</b>                       |              |                                                                                                                                                                                                                       |                  | Value             |         |      |

|--------------------|--------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|---------|------|

|                    | Parameter                      | Symbol       | Condition                                                                                                                                                                                                             | Min              | Тур               | Max     | Unit |

|                    | Vo3 output over                | Vovp3        | VSEL34 pin = "H" Level,<br>Vo3 = 1.8 V, FB3 pin                                                                                                                                                                       | 2.124*1          | 2.16*1            | 2.196*1 | V    |

|                    | voltage threshold              | V OVP3       | VSEL34 pin = "L" Level,<br>Vo3 = 1.5 V, FB3 pin                                                                                                                                                                       | <b>1</b> .77*1   | 1.8* <sup>1</sup> | 1.83*1  | V    |

| CH3 block<br>[CH3] | Vo3 over current limit         | ЮСРЗ         | lo3,<br>L = 1.5 μH                                                                                                                                                                                                    | 3.0*1            | 3.75*1            | 4.5*1   | А    |

|                    | FB3 input resistance           | <b>R</b> FB3 | FB3 pin                                                                                                                                                                                                               |                  | 250               |         | kΩ   |

|                    | Soft start time                | SS3          | FB3 pin<br>SS1 = SS2 = AGND pin                                                                                                                                                                                       | 1.19             | 1.4               | 1.61    | ms   |

|                    | CH4 output voltage             | Vo4          | VSEL34 pin = "H" Level,<br>FB4 pin                                                                                                                                                                                    | 0.855            | 0.9               | 0.945   | V    |

|                    | On the output voltage          | V04          | VSEL34 pin = "L" Level,<br>FB4 pin                                                                                                                                                                                    | 0.7125           | 0.75              | 0.7875  | V    |

|                    | High-side FET<br>on-resistance | Ronh4        | $\begin{array}{l} LX4 \ pin = -100 \ mA, \\ V_{GS} = 5 \ V \end{array}$                                                                                                                                               | _                | 130*1             |         | mΩ   |

|                    | Low-side FET<br>on-resistance  | Ronl4        | $\begin{array}{l} LX4 \mbox{ pin} = 100 \mbox{ mA}, \\ V_{GS} = 5 \mbox{ V} \end{array}$                                                                                                                              | _                | 55*1              |         | mΩ   |

|                    | PVDD4 standby<br>current       | PVDD4S       | CTL34 pin = 0 V,<br>PVDD4 pin = 12.6 V                                                                                                                                                                                | _                | _                 | 15      | μA   |

|                    |                                | ηT41         | VSEL34 pin = "H" Level,<br>FSEL4 pin = "H" Level,<br>Vo4 = 0.9 V<br>$0.3 \times lo (Max) < lo <$<br>$0.6 \times lo (Max)$                                                                                             | 80* <sup>3</sup> |                   |         | %    |

| CH4 block<br>[CH4] | CH4 efficiency                 | ηT42         | VSEL34 pin = "L" Level,<br>FSEL4 pin = "H" Level,<br>Vo4 = $0.75$ V<br>$0.3 \times lo$ (Max) < $lo <$<br>$0.6 \times lo$ (Max)                                                                                        | 80* <sup>3</sup> |                   |         | %    |

|                    |                                | ηF41         | $\label{eq:VSEL34} \begin{array}{l} \mbox{pin} = \mbox{``H" Level}, \\ \mbox{FSEL4 pin} = \mbox{``H" Level}, \\ \mbox{Vo4} = 0.9 \ \mbox{V} \\ \mbox{0.6} \times \mbox{ lo (Max)} < \mbox{lo < lo (Max)} \end{array}$ | 83* <sup>3</sup> | _                 |         | %    |

|                    |                                | ηF42         | $\begin{array}{l} \text{VSEL34 pin} = \text{``L'' Level,} \\ \text{FSEL4 pin} = \text{``H'' Level,} \\ \text{Vo4} = 0.75 \text{ V} \\ 0.6 \times \text{ lo (Max)} < \text{ lo < lo (Max)} \end{array}$                | 83* <sup>3</sup> |                   |         | %    |

|                    | Vo4 output over                | Vovp4        | VSEL34 pin = "H" Level,<br>Vo4 = 0.9 V, FB4 pin                                                                                                                                                                       | 1.035*1          | 1.08*1            | 1.125*1 | V    |

|                    | voltage threshold              | ¥ UVP4       | VSEL34 pin = "L" Level,<br>Vo4 = 0.75 V, FB4 pin                                                                                                                                                                      | 0.862*1          | 0.90*1            | 0.938*1 | V    |

|                    |                                   |             | (1a = +25  C, 7                                                                          |                  | Í                 |        |      |

|--------------------|-----------------------------------|-------------|------------------------------------------------------------------------------------------|------------------|-------------------|--------|------|

| Parameter          |                                   | Symbol      | Condition                                                                                | Min              | Тур               | Max    | Unit |

|                    | Vo4 over current limit            | OCP4        | lo4,<br>L = 1.5 μH,fosc = 700 kHz                                                        | 1.92*1           | 2.4*1             | 2.88*1 | А    |

|                    | FB4 input resistance              | Rfb4        | FB4 pin                                                                                  |                  | 750               |        | kΩ   |

| CH4 block          | Soft start time                   | SS4         | FB4 pin,<br>SS1 = SS2 = AGND pin                                                         | 1.19             | 1.4               | 1.61   | ms   |

| [CH4]              | FSEL4, "H" level                  | $V_{FLGH4}$ | FSEL4 pin                                                                                | 2                |                   |        | V    |

|                    | FSEL4, "L" level                  | VFLGL4      | FSEL4 pin                                                                                |                  |                   | 0.8    | V    |

|                    | FSEL4 input current               | FSELH4      | FSEL4 pin = 3 V                                                                          | 23               | 30                | 43     | μA   |

|                    |                                   | FSELL4      | FSEL4 pin = 0 V                                                                          |                  |                   | 1      | μA   |

|                    | CH5 output voltage                | Vo5         | FB5 pin                                                                                  | 1.425            | 1.5               | 1.575  | V    |

|                    | High-side FET<br>on-resistance    | Ronh5       | LX5 pin = $-100 \text{ mA}$ ,<br>V <sub>GS</sub> = 5 V                                   |                  | 65* <sup>1</sup>  |        | mΩ   |

|                    | Low-side FET<br>on-resistance     | Ronl5       | $\begin{array}{l} LX5 \mbox{ pin} = 100 \mbox{ mA}, \\ V_{GS} = 5 \mbox{ V} \end{array}$ |                  | 40*1              |        | mΩ   |

|                    | PVDD5 standby<br>current          | PVDD5S      | CTL5 pin = 0 V,<br>PVDD5 pin = 12.6 V                                                    |                  | _                 | 15     | μA   |

|                    | CH5 efficiency                    | ηL5         | 0.05 × lo (Max) < lo <<br>0.3 × lo (Max)                                                 | 82* <sup>3</sup> | _                 |        | %    |

| CH5 block<br>[CH5] |                                   | ηT5         | 0.3 × lo (Max) < lo <<br>0.6 × lo (Max)                                                  | 85* <sup>3</sup> |                   |        | %    |

|                    |                                   | ηF5         | $0.6 \times lo (Max) < lo < lo (Max)$                                                    | 85* <sup>3</sup> |                   |        | %    |

|                    | Vo5 output over voltage threshold | Vovp5       | FB5 pin                                                                                  | 1.77*1           | 1.8* <sup>1</sup> | 1.83*1 | V    |

|                    | Vo5 over current limit            | IOCP5       | lo5,<br>L = 1.5 μH                                                                       | 2.8*1            | 3.5* <sup>1</sup> | 4.2*1  | А    |

|                    | FB5 input resistance RFE          |             | FB5 pin                                                                                  |                  | 250               |        | kΩ   |

|                    | Soft start time                   | SS5         | FB5 pin,<br>SS1 = SS2 = AGND pin                                                         | 1.19             | 1.4               | 1.61   | ms   |

| CH6 block<br>[CH6] |                                   | Vo6         | DVSEL6 = "H" Level,<br>FB6 pin                                                           | 1.045            | 1.1               | 1.155  | V    |

|                    | CH6 output voltage                |             | DVSEL6 = "L" Level,<br>FB6 pin                                                           | 0.9975           | 1.05              | 1.1025 | V    |

|                    | High-side FET<br>on-resistance    | Ronh6       | LX6 pin = $-100$ mA,<br>V <sub>GS</sub> = 5 V                                            | _                | 61*1              |        | mΩ   |

|                    | Low-side FET<br>on-resistance     | Ronle       | LX6 pin = 100 mA, $V_{GS} = 5 V$                                                         | _                | 35*1              | _      | mΩ   |

|                    | PVDD6 standby<br>current          | PVDD6S      | CTL6 pin = 0 V,<br>PVDD6 pin = 12.6 V                                                    | _                |                   | 15     | μA   |

(Ta =  $+25 \circ$ C, AVDD = PVDD1 to PVDD7 = 7.2 V)

# MB39C308

(Continued)

$(Ta = +25 \circ C, AVDD = PVDD1 \text{ to } PVDD7 = 7.2 \text{ V})$

| Parameter |                                   | Symbol           | Condition                                                                                                                       |                  | Unit              |                   |      |

|-----------|-----------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-------------------|------|

|           |                                   | Symbol           | Condition                                                                                                                       | Min              | Тур               | Max               | Unit |

| CH6 block | CH6 efficiency                    | ηL61             | DVSEL6 pin = "H" Level,<br>Vo6 = 1.1 V<br>0.05 × lo (Max) < lo <<br>0.3 × lo (Max)                                              | 80* <sup>3</sup> |                   |                   | %    |

|           |                                   | ηL62             | DVSEL6 pin = "L" Level,<br>Vo6 = 1.05 V<br>0.05 × lo (Max) < lo <<br>0.3 × lo (Max)                                             | 80* <sup>3</sup> | _                 |                   | %    |

|           |                                   | ηT61             | $\begin{array}{l} DVSEL6\ pin = ``H" \ Level,\\ Vo6 = 1.1 \ V\\ 0.3 \times lo\ (Max) < lo <\\ 0.6 \times lo\ (Max) \end{array}$ | 82* <sup>3</sup> | _                 |                   | %    |

|           |                                   | ηT62             | DVSEL6 pin = "L" Level,<br>Vo6 = 1.05 V<br>0.3 × lo (Max) < lo <<br>0.6 × lo (Max)                                              | 82* <sup>3</sup> |                   |                   | %    |

| [CH6]     |                                   | ηF61             | $\begin{array}{l} DVSEL6\ pin = ``H"\ Level,\\ Vo6 = 1.1\ V\\ 0.6 \times Io\ (Max) < Io < Io\ (Max) \end{array}$                | 81* <sup>3</sup> |                   |                   | %    |

|           |                                   | ηF62             | $\begin{array}{l} DVSEL6\ pin = ``L"\ Level,\\ Vo6 = 1.05\ V\\ 0.6 \times Io\ (Max) < Io < Io\ (Max) \end{array}$               | 81* <sup>3</sup> | _                 | _                 | %    |

|           | Vo6 output over voltage threshold | Vovp6            | DVSEL6 pin = "H" Level,<br>Vo6 = 1.1 V, FB6 pin                                                                                 | 1.298*1          | 1.32*1            | 1.342*1           | V    |

|           |                                   |                  | DVSEL6 pin = "L" Level,<br>Vo6 = 1.05 V, FB6 pin                                                                                | 1.239*1          | 1.26*1            | 1.281*1           | V    |

|           | Vo6 over<br>current limit         | ЮСРб             | lo6,<br>L = 1.5 μH                                                                                                              | 4.0*1            | 5.0* <sup>1</sup> | 6.0* <sup>1</sup> | А    |

|           | FB6 input resistance              | R <sub>FB6</sub> | FB6 pin                                                                                                                         | —                | 350               |                   | kΩ   |

|           | Soft start time                   | SS6              | FB6 pin,<br>SS1 = SS2 = AGND pin                                                                                                | 1.19             | 1.4               | 1.61              | ms   |

\*1 : This parameter isn't be specified. This should be used as a reference to support designing the circuits.

- \*2 : FSEL4 pin is typically recommended to set to "H" level for fosc = 700 kHz setting. When Vo4 is preset to 0.75 V, the ON duty becomes so small at high input voltage. Then, there is a case CH4 output regulation becomes worse at light load condition. In that case, please set FSEL4 pin to "L" level for fosc = 350 kHz setting.

- \*3 : This is a reference value, which is evaluated by the recommended EVB circuit. This should be used as a reference to support designing the circuits.

### CHANNEL CONTROL FUNCTION

The each channel is turned on and off depending on the voltage levels at the CTL1 pin, CTL2 pin, CTL34 pin, CTL5 pin and CTL6 pin.

| CTL1 | CTL2 | CTL34 | CTL5 | CTL6 | CH1 | CH2 | CH3 | CH4 | CH5 | CH6 |

|------|------|-------|------|------|-----|-----|-----|-----|-----|-----|

| L    | L    | L     | L    | L    | OFF | OFF | OFF | OFF | OFF | OFF |

| Н    | L    | L     | L    | L    | ON  | OFF | OFF | OFF | OFF | OFF |

| L    | Н    | L     | L    | L    | OFF | ON  | OFF | OFF | OFF | OFF |

| L    | L    | Н     | L    | L    | OFF | OFF | ON  | ON  | OFF | OFF |

| L    | L    | L     | Н    | L    | OFF | OFF | OFF | OFF | ON  | OFF |

| L    | L    | L     | L    | Н    | OFF | OFF | OFF | OFF | OFF | ON  |

| Н    | Н    | Н     | Н    | Н    | ON  | ON  | ON  | ON  | ON  | ON  |

### Channel On/Off Setting Conditions

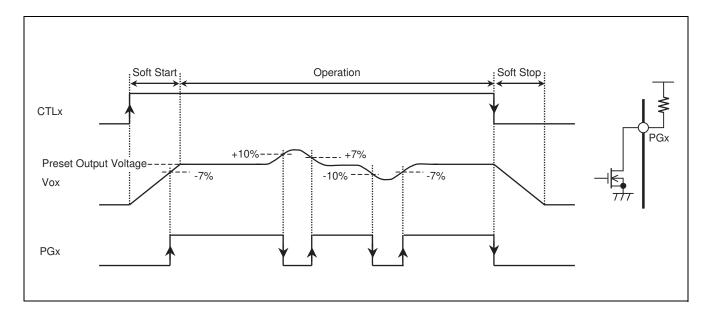

### POWER GOOD FUNCTION

The Power Good function is shown in the following figure. The ALLPG pin and the PGx pins are connected to the open drain of the NMOS, and are used by connecting the resistor. When the CTLx pin is turned on, and the output voltage becomes within 7% of the preset voltage, the PGx pin is changed from "L" to "H". PGx = "H" means the status of Power Good. When the change of the output voltage exceeds 10% of the preset voltage, the PGx pin becomes "L". And when the output voltage becomes within 7% of the preset voltage becomes within 7% of the preset voltage, the PGx pin becomes "H". Moreover, when all of the channels from CH3 to CH6 are the Power Good, the ALLPG pin becomes "H".

### ■ PROTECTION

### <1> Under Voltage Lock Out Protection (UVLO)

The UVLO prevents IC malfunctions or system damage and the degradation caused by the excessive voltage or instantaneous voltage drop of the power supply voltage (AVDD), bias voltage (VB), internal reference voltage (VREF).

The UVLO turns off all the high- and low-side FETs of CH1 to CH6 when the AVDD pin drops below 5.0 V(Typ). The UVLO is released when the AVDD pin is above 5.1 V (Typ). This is the non-latch type protection.

### <2> Input Over Voltage Protection (IVP)

The circuit prevents IC malfunctions or system damage and the degradation caused by the excessive voltage or instantaneous voltage drop of the power supply voltage (AVDD).

The IVP turns off all the high- and low-side FETs of CH1 to CH6 when the AVDD pin exceeds 13.0 V(Typ). The IVP is released when the AVDD pin drops below 12.85 V (Typ). This is the non-latch type protection.

### <3> Over Temperature Protection (OTP)

The OTP prevents thermal damages on ICs. The IVP function turns off all the high- and low-side FETs of CH1 to CH6 when the junction temperature exceeds +150 °C (Typ). The OPT is released when the temperature drops below +125 °C (Typ). This is the non-latch type protection.

### <4> Output Short Circuit Protection (SCP)

The SCP function stops outputting data when the output voltage falls and protects the devices connected to outputs.

The SCP timer will start to count when either of output voltages CH1 to CH6 falls due to the output short-circuit to GND or excessive currents. The SCP function starts to operate the latch protection and turns off all the high-and low-side FETs when the output voltage continues to fall to 1.4 ms (Typ).

Follow either of the steps to release the latch of output short circuit protection.

- After all of CTL signals from CH1 to CH6 are set to "L" level, turn on the each CTL signal again.

- When the voltage of the AVDD pin is below the threshold voltage of the UVLO, and then the voltage of the AVDD pin becomes higher than the threshold voltage of UVLO again, the each output will start up.

#### <5> Output Over Voltage Protection (OVP)

The OVP protects the devices which are connected to outputs when the output voltage rises. When either output voltage of the CH1 to CH6 is higher than 120% of each channel's preset voltage (Typ), the OVP turns off all the high- and low-side FETs of the channels (However, the only CH4 is turned off the high-side FET and turned on the low-side FET. The CH4 logic is different from other channels as it is controlled with PWM). The OVP is released when the output voltage is below 103% of the preset voltage (Typ). This is the non-latch type protection.

#### <6> Over Current Protection (OCP)

The OCP function controls the output current. When drain-to-source current excessively increases, the OCP controls the output current to the preset value for each channel. Then, because of the OCP functions, the output voltage usually drops. As a result, the SCP stop the all outputs with the latch setting.

The OCP functions only for the corresponding channels only, however, the SCP stops all of the channels in the end.

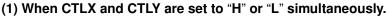

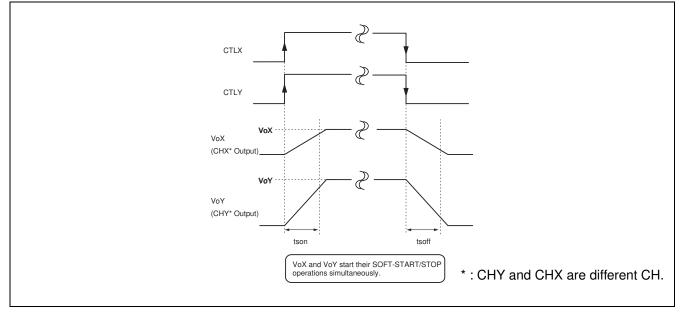

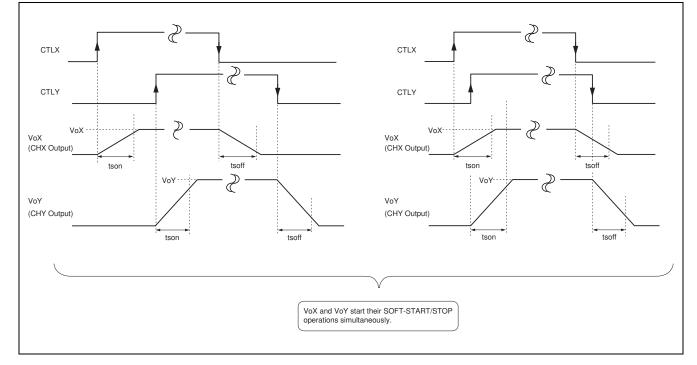

### DESCRIPTION OF SOFT-START AND SOFT-STOP OPERATION

Soft-start function is featured to avoid inrush current when each channels is turned-on. When the CTL1, CTL2, CTL34, CTL5 and CTL6 are set to "H" level, ramped-up voltage is fed on an inverting input of an error amplifier of a channel. Start-time of the soft-start can be predefined and the start time is kept constant independent from a load of the output of the channels. When the CTL1, CTL2, CTL34, CTL5 and CTL6 are set to "L" level, ramped-down voltage is fed on an inverting input of an error amplifier of a channel the output voltage goes low. Stop-time of the Soft-stop can be predefined and the stop-time is kept constant independent from a load of the output of the channel.

The time of both soft-start and soft-stop can be predefined with combination of the level on the SS1 and the SS2 pins as shown in the "• Soft-Start/Soft-Stop time (tson/tsoff) Setting Conditions", and external capacitors and resistors aren't required

| SS1 pin                | SS2 pin                | Soft-Start time<br>(tson) (Typ) * | Soft-Stop time<br>(tsoff) (Typ) * | Unit |

|------------------------|------------------------|-----------------------------------|-----------------------------------|------|

| Connecting to AGND pin | Connecting to AGND pin | 1.4                               | 1.4                               | ms   |

| Connecting to AGND pin | Connecting to VREF pin | 2.2                               | 2.2                               | ms   |

| Connecting to AGND pin | Connecting to VB pin   | 2.9                               | 2.9                               | ms   |

| Connecting to VREF pin | Connecting to AGND pin | 3.5                               | 3.5                               | ms   |

| Connecting to VREF pin | Connecting to VREF pin | 4.1                               | 4.1                               | ms   |

| Connecting to VREF pin | Connecting to VB pin   | 5.1                               | 5.1                               | ms   |

| Connecting to VB pin   | Connecting to AGND pin | 5.9                               | 5.9                               | ms   |

| Connecting to VB pin   | Connecting to VREF pin | 7.3                               | 7.3                               | ms   |

| Connecting to VB pin   | Connecting to VB pin   | 8.2                               | 8.2                               | ms   |

#### • Soft-Start/Soft-Stop time (tson/tsoff) Setting Conditions

\* : Accuracy : Typ  $\pm 15\%$

### << Trace of the Output voltage on each channel, during Soft-Start/Soft-Stop operations>>

The sequence of turning on/off different output channels is defined by the CTL1, CTL2, CTL34, CTL5 and CTL6 pins.

# (2) When CTLY is set to "H" or "L" after completion of SOFT-START or -STOP on VoX .

(3) When CTLY is set to "H" or "L" after VoX has started its SOFT-START or -STOP operation.

#### (4) When CTL34 is set to "H" or "L".

### ■ PRESET FUNCTION OF CH3/CH4/CH6 OUTPUT VOLTAGE

The preset output voltage of CH3 and CH4 are selected by VSEL34 pin condition. Please refer the following table. The preset output voltage of CH6 is selected by DVSEL6 pin condition. Please refer the following table.

| CH3/CH4/CH6 Preset Output Voltage Conditions |  |

|----------------------------------------------|--|

|                                              |  |

| CONNECTION | VREF                                       | GND                                         |