# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

The following document contains information on Cypress products. Although the document is marked with the name "Spansion" and "Fujitsu", the company that originally developed the specification, Cypress will continue to offer these products to new and existing customers.

#### **Continuity of Specifications**

There is no change to this document as a result of offering the device as a Cypress product. Any changes that have been made are the result of normal document improvements and are noted in the document history page, where supported. Future revisions will occur when appropriate, and changes will be noted in a document history page.

#### **Continuity of Ordering Part Numbers**

Cypress continues to support existing part numbers. To order these products, please use only the Ordering Part Numbers listed in this document.

#### For More Information

Please contact your local sales office for additional information about Cypress products and solutions.

#### **About Cypress**

Cypress (NASDAQ: CY) delivers high-performance, high-quality solutions at the heart of today's most advanced embedded systems, from automotive, industrial and networking platforms to highly interactive consumer and mobile devices. With a broad, differentiated product portfolio that includes NOR flash memories, F-RAM<sup>™</sup> and SRAM, Traveo<sup>™</sup> microcontrollers, the industry's only PSoC<sup>®</sup> programmable system-on-chip solutions, analog and PMIC Power Management ICs, CapSense<sup>®</sup> capacitive touch-sensing controllers, and Wireless BLE Bluetooth<sup>®</sup> Low-Energy and USB connectivity solutions, Cypress is committed to providing its customers worldwide with consistent innovation, best-in-class support and exceptional system value.

# ASSP (for Mobile Terminals)

# Power Management IC for Mobile Terminals 3ch DC/DC Converter + 4ch LDO

# MB39C316

# DESCRIPTION

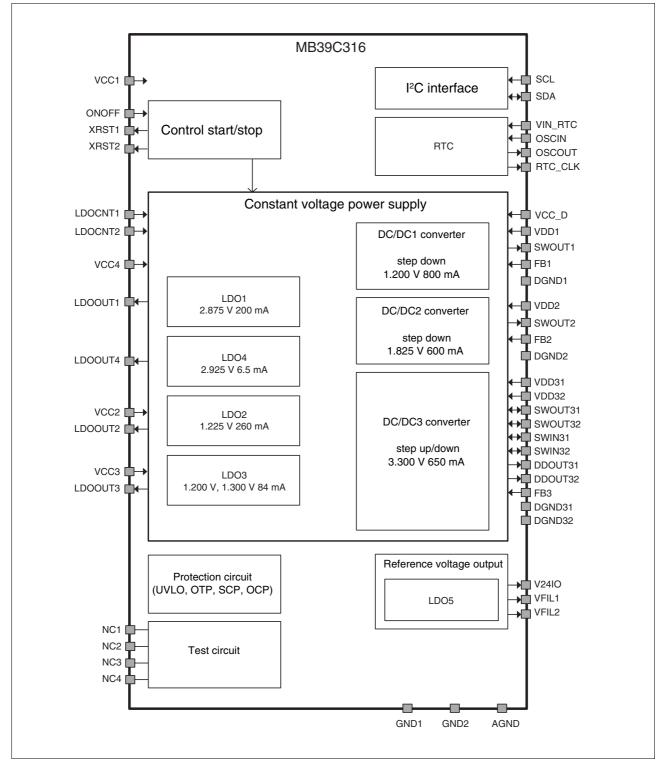

The MB39C316 is equipped with the 3 ch DC/DC converter and the 4 ch linear regulator (LDO), and is the power supply LSI for mobile terminals which operate in the range of power supply voltage with 1-cell Li-ion power by 1ch high efficiency voltage step-up/down DC/DC.

The MB39C316 contains the 2ch synchronous rectification DC/DC converter with current mode system and the 1ch voltage step-up/down DC/DC converter. Detecting load current by each DC/DC converter alternates the Normal mode (PWM) with the ECO mode (PFM) automatically.

MB39C316 has the built-in 4ch LDO which is suitable to supply voltage to the system block and the built-in 1ch LDO which generates stable internal reference voltage.

It is possible to control a notice of internal condition, the power supply and reset in order to support the communication interface which is compliant with the I<sup>2</sup>C bus standard.

# ■ FEATURES

- Input voltage range : 2.7 V to 5.5 V

- Step-down regulators : 2 channels

- Step-up/down regulator : 1 channel

- Linear regulator (LDO) : 4 channels

- Possible to select output voltage : LDO3 1.2 V/1.3 V (register setting)

- On/Off control of LDO and DC/DC converter by external signals and register settings

- Compliant with I<sup>2</sup>C bus standard (Max 400 kbps)

- · Possible to output the 32.768 kHz clock by connecting crystal oscillator

- Protection function: Over current protection (OCP), Output short circuit protection (SCP),

- Under voltage lock out protection (UVLO), Over temperature protection (OTP)

- Package : 49 pin, WL-CSP (3.14 mm × 3.11 mm × 0.8 mm)

# ■ APPLICATIONS

- Mobile WiMAX terminals

- Other mobile terminals etc.

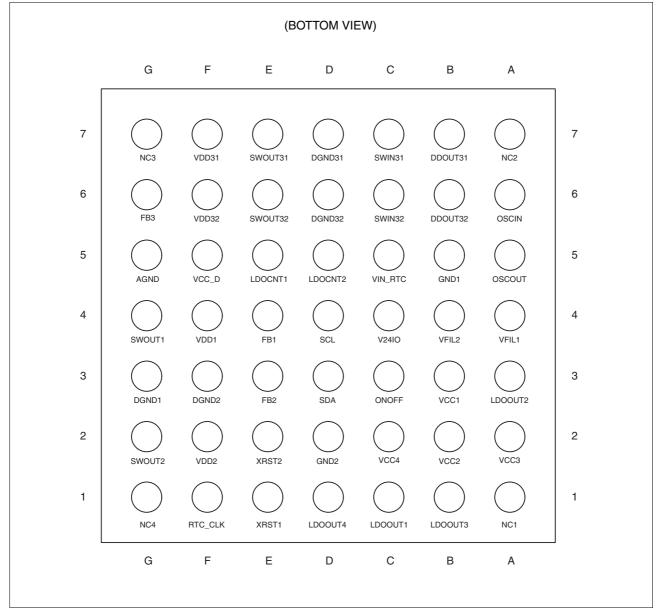

# ■ PIN ASSIGNMENT

# ■ PIN DISCRIPTIONS

| Block            | Pin No. | Pin name | I/O | Descriptions                                                      |

|------------------|---------|----------|-----|-------------------------------------------------------------------|

|                  | B3      | VCC1     | I   | Power supply input, Power supply input pin for LDO2, LDO3 control |

|                  | B2      | VCC2     | Ι   | Power supply input pin for LDO2 power                             |

|                  | A2      | VCC3     | Ι   | Power supply input pin for LDO3 power                             |

| External         | C2      | VCC4     | I   | Power supply input pin for LDO1, LDO4 control/power               |

| power            | F5      | VCC_D    | I   | Power supply input pin for DC/DC converter control                |

| supply           | F4      | VDD1     | I   | Power supply input pin for DC/DC1 converter power                 |

|                  | F2      | VDD2     | I   | Power supply input pin for DC/DC2 converter power                 |

|                  | F7      | VDD31    | I   | Power supply input pin 1 for DC/DC3 converter power               |

|                  | F6      | VDD32    | I   | Power supply input pin 2 for DC/DC3 converter power               |

|                  | C5      | VIN_RTC  | I   | Power supply input pin for RTC                                    |

|                  | E5      | LDOCNT1  | I   | LDO output control input pin 1                                    |

|                  | D5      | LDOCNT2  | I   | LDO output control input pin 2                                    |

|                  | D1      | LDOOUT4  | 0   | LDO4 output pin ( + 2.9 V)                                        |

|                  | B1      | LDOOUT3  | 0   | LDO3 output pin ( + 1.2 V/1.3 V)                                  |

|                  | C1      | LDOOUT1  | 0   | LDO1 output pin ( + 2.9 V)                                        |

|                  | A3      | LDOOUT2  | 0   | LDO2 output pin ( + 1.2 V)                                        |

|                  | G4      | SWOUT1   | 0   | DC/DC1 converter inductance connection output pin                 |

| Constant         | E4      | FB1      | I   | DC/DC1 converter output voltage feedback input pin (1.2 V)        |

| voltage          | G2      | SWOUT2   | 0   | DC/DC2 converter inductance connection output pin                 |

| power<br>supply  | E3      | FB2      | I   | DC/DC2 converter output voltage feedback input pin (1.8 V)        |

|                  | E7      | SWOUT31  |     | DC/DC3 converter inductance connection pin 1                      |

|                  | E6      | SWOUT32  |     | DC/DC3 converter inductance connection pin 2                      |

|                  | C7      | SWIN31   |     | DC/DC3 converter inductance connection pin 1                      |

|                  | C6      | SWIN32   |     | DC/DC3 converter inductance connection pin 2                      |

|                  | B7      | DDOUT31  | 0   | DC/DC3 converter output pin 1                                     |

|                  | B6      | DDOUT32  | 0   | DC/DC3 converter output pin 2                                     |

|                  | G6      | FB3      | I   | DC/DC3 converter output voltage feedback input pin (3.3 V)        |

| I <sup>2</sup> C | D4      | SCL      | I   | I <sup>2</sup> C interface clock input pin                        |

| interface        | D3      | SDA      | I/O | I <sup>2</sup> C interface data I/O pin                           |

|                  | A6      | OSCIN    | I   | Input pin for crystal oscillator connection                       |

| RTC              | A5      | OSCOUT   | 0   | Output pin for crystal oscillator connection                      |

|                  | F1      | RTC_CLK  | 0   | 32.768 kHz Clock output pin                                       |

|                  | C3      | ONOFF    | I   | Enable pin for the MB39C316                                       |

| Start/Stop       | E1      | XRST1    | 0   | Reset output pin 1                                                |

|                  | E2      | XRST2    | 0   | Reset output pin 2                                                |

|                  | C4      | V24IO    | 0   | Power supply output pin for internal 2.4 V I/O                    |

| Reference        | A4      | VFIL1    | 0   | Reference voltage output pin 1 (0.47 µF connected )               |

| voltage          | B4      | VFIL2    | 0   | Reference voltage output pin 2 (0.47 µF connected )               |

| Block | Pin No. | Pin name | I/O | Descriptions                                                        |

|-------|---------|----------|-----|---------------------------------------------------------------------|

|       | A1      | NC1      |     | Pin for TEST (Set to Non Connect. Prohibited to connect to others.) |

| TEST  | A7      | NC2      |     | Pin for TEST (Set to Non Connect. Prohibited to connect to others.) |

| 1231  | G7      | NC3      |     | Pin for TEST (Set to Non Connect. Prohibited to connect to others.) |

|       | G1      | NC4      |     | Pin for TEST (Set to Non Connect. Prohibited to connect to others.) |

|       | B5      | GND1     |     | Ground pin (COMMON, RTC)                                            |

|       | D2      | GND2     |     | Ground pin (LDO, INPUT_IF, OUTPUT_IF)                               |

|       | G5      | AGND     |     | Ground pin (DC/DC converter control block)                          |

| GND   | G3      | DGND1    |     | DC/DC1 converter ground pin                                         |

|       | F3      | DGND2    |     | DC/DC2 converter ground pin                                         |

|       | D7      | DGND31   |     | DC/DC3 converter ground pin 1                                       |

|       | D6      | DGND32   |     | DC/DC3 converter ground pin 2                                       |

### ■ BLOCK DIAGRAM

# ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                     | Symbol   | Condition                                | Rat    | ing         | Unit |

|-------------------------------|----------|------------------------------------------|--------|-------------|------|

| Parameter                     | Symbol   | Condition                                | Min    | Max         | Onit |

|                               | Vmax1    | VCC1, VCC_D, VDD1,<br>VDD2, VDD31, VDD32 | - 0.3  | + 6.0       | V    |

| Power supply voltage          | Vmax2    | VCC2, VCC3                               | - 0.3  | + 6.0       | V    |

|                               | Vmax3    | VCC4                                     | - 0.3  | + 6.0       | V    |

|                               | Vmax4    | VIN_RTC                                  | - 0.3  | + 3.6       | V    |

|                               | Vinmax1  | LDOCNT1, LDOCNT2, SCL,<br>SDA            | - 0.3  | Vvcc3 + 0.3 | V    |

| Input voltage                 | Vinmax2  | ONOFF, FB1, FB2, FB3                     | - 0.3  | Vvcc1 + 0.3 | V    |

|                               | Vinmax3  | OSCIN                                    | - 0.3  | Vrtc        | V    |

| Storage temperature range     | Tstg     |                                          | - 55   | + 125       | °C   |

| ESD                           | Vesdh    | Human Body Model<br>(100 pF, 1.5 kΩ)     | - 1000 | + 1000      | V    |

| withstand voltage             | Vesdm    | Machine Model (200 pF, 0 $\Omega$ )      | - 100  | + 100       | V    |

| latch-up<br>withstand voltage | Vlatchup | EIA/JEDEC Standard                       | – 150  | + 150       | mA   |

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

# RECOMMENDED OPERATION CONDITIONS

their representatives beforehand.

| Parameter                      | Symbol | Condition                                |       | Value |         | Unit |

|--------------------------------|--------|------------------------------------------|-------|-------|---------|------|

| Farameter                      | Symbol | Condition                                | Min   | Тур   | Max     | Unit |

|                                | Vvcc1  | VCC1, VCC_D, VDD1,<br>VDD2, VDD31, VDD32 | 2.7   | 3.3   | 5.5     | V    |

| Power supply voltage           | Vvcc2  | VCC2, VCC3                               | 1.75  | _     | 1.90    | V    |

|                                | Vvcc3  | VCC4                                     | 3.2   | _     | 5.5     | V    |

|                                | Vrtc   | VIN_RTC                                  | 2.325 |       | 2.475   | V    |

|                                | VIvcc1 | ONOFF                                    | 0.0   | _     | Vvcc1   | V    |

|                                | VIvcc3 | LDOCNT1, LDOCNT2, SCL,<br>SDA            | 0.0   |       | Vvcc3   | V    |

| Input voltage                  | VIdd1  | FB1                                      | 0.0   |       | Voutdd1 | V    |

|                                | VIdd2  | FB2                                      | 0.0   |       | Voutdd2 | V    |

|                                | VIdd3  | FB3                                      | 0.0   | _     | Voutdd3 | V    |

|                                | VIrtc  | OSCIN                                    | 0.0   |       | Vrtc    | V    |

| Operating<br>temperature range | Та     |                                          | - 30  |       | + 85    | °C   |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact

# ■ ELECTRICAL CHARACTERISTICS

# 1. DC characteristics

|      | Devenueter              | Quanta d  |                                                | $cc2 = 1.75 \text{ V}^{-1}$                    |       | Value |       | Unit  |

|------|-------------------------|-----------|------------------------------------------------|------------------------------------------------|-------|-------|-------|-------|

|      | Parameter               | Symbol    | Symbol Condition                               |                                                | Min   | Тур   | Max   | Unit  |

|      | Output voltage          | Voutld1   | lout = 0 to lomax                              |                                                | 2.800 | 2.875 | 3.000 | V     |

|      | Maximum output current  | loutId1   | _                                              |                                                | 200   |       |       | mA    |

|      | Input stability         | Vlineld1  | lout = $-10 \text{ mA}$                        |                                                |       | 5     |       | mV    |

|      | Load stability          | Vloadld1  | lout = 0 to lomax                              |                                                | _     | 20    |       | mV    |

|      | Ripple removal          | RR1kld1   | Vinput = 0.2 Vpp,                              | f = 1 kHz                                      | _     | 60    |       | dB    |

|      | ratio                   |           | Vvcc1 = 3.3 V,<br>lout = lomax/2               | f = 10 kHz                                     | _     | 40    | _     | dB    |

|      | Output noise<br>voltage | Vnoiseld1 | f = 10 Hz to 100 kHz,<br>lout = 10 mA to lomax |                                                |       | 30    | 45    | μVrms |

|      | Rise time               | Trld1     | Vvcc1 = 3.3 V, lout = 0 mA,<br>Vout = 90%      |                                                |       | 200   |       | μs    |

|      | Fall time               | Tfld1     | Vvcc1 = 3.3 V, lout = 0 mA,<br>Vout = 10%      |                                                |       | 70    | _     | μs    |

|      | Output voltage          | Voutld2   | lout = 0 to lomax                              |                                                | 1.150 | 1.225 | 1.300 | V     |

|      | Maximum output current  | loutld2   | _                                              | —                                              |       | _     | _     | mA    |

|      | Input stability         | Vlineld2  | lout = - 10mA                                  |                                                |       | 5     |       | mV    |

|      | Load stability          | Vloadld2  | lout = 0 to lomax                              |                                                |       | 25    |       | mV    |

|      | Ripple removal          | RR1kld2   | Vinput = 0.2 Vpp,                              | f = 1 kHz                                      |       | 60    |       | dB    |

| LDO2 | ratio                   | RR10kld2  | Vvcc1, lout = 1 mA<br>to lomax                 | f = 10 kHz                                     |       | 40    | _     | dB    |

|      | Output noise<br>voltage | Vnoiseld2 |                                                | f = 10 Hz to 100 kHz,<br>lout = 10 mA to lomax |       | 30    | 45    | μVrms |

|      | Rise time               | Trld2     | Vvcc1, lout = 0 mA,<br>Vout = 90%              |                                                |       | 70    |       | μs    |

|      | Fall time               | Tfld2     | Vvcc1, lout = 0 mA,<br>Vout = 10%              |                                                |       | 150   |       | μs    |

$(Ta = -30 \ ^{\circ}C \ to + 85 \ ^{\circ}C, \ Vvcc1 = 2.7 \ V \ to 5.5 \ V, \ Vvcc3 = 3.2 \ V \ to 5.5 \ V, \ Vvcc2 = 1.75 \ V \ to 1.90 \ V, \ Vrcc = 2.325 \ V \ to 2.475 \ V)$

|      | Deveryorker             | Ormahal   | 0 an diti an                                      |                                                                      |       | Value |       | 11    |

|------|-------------------------|-----------|---------------------------------------------------|----------------------------------------------------------------------|-------|-------|-------|-------|

|      | Parameter               | Symbol    | Condition                                         |                                                                      | Min   | Тур   | Max   | Unit  |

|      | Output voltage          | Voutld3   | lout = 0 to lomax, VSE<br>"0" ( register 02⊦[0])  | L_SYN =                                                              | 1.100 | 1.200 | 1.300 | V     |

|      | Output voltage          | Voulids   | lout = 0 to lomax, VSEI<br>"1" ( register 02⊦[0]) | lout = 0 to lomax, VSEL_SYN =<br>"1" ( register 02 <sub>H</sub> [0]) |       | 1.300 | 1.400 | V     |

|      | Maximum output current  | loutld3   |                                                   | _                                                                    |       | _     | _     | mA    |

|      | Input stability         | Vlineld3  | lout = -10 mA                                     |                                                                      | _     | 5     | _     | mV    |

|      | Load stability          | Vloadld3  | lout = 0 to lomax                                 |                                                                      |       | 20    |       | mV    |

| LDO3 | Ripple removal          | RR1kld3   | Vinput = 0.2 Vpp,                                 | f = 1 kHz                                                            |       | 60    |       | dB    |

|      | ratio                   | RR10kld3  | Vvcc1,<br>lout = 1mA to lomax                     | f = 10 kHz                                                           |       | 40    |       | dB    |

|      | Output noise voltage    | Vnoiseld3 | f = 10 Hz to 100 kHz,<br>lout = 10 mA to lomax    |                                                                      | 30    | 40    | μVrms |       |

|      | Rise time               | Trld3     | Vvcc1, lout = 0 mA,<br>Vout = 90%                 |                                                                      |       | 60    | _     | μs    |

|      | Fall time               | Tfld3     | Vvcc1, lout = 0 mA,<br>Vout = 10%                 |                                                                      |       | 150   |       | μs    |

|      | Output voltage          | Voutld4   | lout = 0 to lomax                                 |                                                                      | 2.850 | 2.925 | 3.000 | V     |

|      | Maximum output current  | loutld4   | _                                                 |                                                                      | 6.5   |       |       | mA    |

|      | Input stability         | Vlineld4  | lout = -6.5 mA                                    |                                                                      | _     | 5     | _     | mV    |

|      | Load stability          | Vloadld4  | lout = 0 to lomax                                 |                                                                      |       | 5     |       | mV    |

|      | Ripple removal          | RR1kld4   | Vinput = 0.2 Vpp,                                 | f = 1 kHz                                                            |       | 60    |       | dB    |

| LDO4 | ratio                   | RR10kld4  | Vvcc1 = Vvcc3 = 3.3 V,<br>lout = 1 mA to lomax    | f = 10 kHz                                                           |       | 40    |       | dB    |

|      | Output noise<br>voltage | Vnoiseld4 | f = 10 Hz to 100 kHz,<br>lout = 1 mA to lomax     |                                                                      |       | 30    | 40    | μVrms |

|      | Rise time               | Trld4     |                                                   | Vvcc1 = Vvcc3 = 3.3 V,<br>lout = 0 mA, Vout = 90%                    |       | 130   |       | μs    |

|      | Fall time               | Tfld4     | Vvcc1 = Vvcc3 = 3.3 V,<br>lout = 0 mA, Vout = 10% |                                                                      |       | 70    |       | μs    |

| Parameter |                           | Ourse had | O a u diti a u                 |       | Value |       | Unit |

|-----------|---------------------------|-----------|--------------------------------|-------|-------|-------|------|

| Pa        | irameter                  | Symbol    | Condition                      | Min   | Тур   | Max   | Unit |

|           | Output voltage            | Voutdd1   | lout = 0 to lomax              | 1.100 | 1.200 | 1.300 | V    |

|           | Maximum<br>output current | loutdd1   |                                | 800   |       | _     | mA   |

|           | Output ripple<br>voltage  | Vrpldd11  | lout = 0 to Iomax              |       | 15    | _     | mV   |

| DC/DC1    | Input stability           | Vlinedd1  | Vvcc1 = 2.7 V to 5.5 V         |       | 10    |       | mV   |

| converter | Load stability            | Vloaddd1  | lout = $-1$ mA to lomax        |       |       | 20    | mV   |

|           | Oscillation<br>frequency  | Fdd1      | PWM mode                       |       | 1.7   | _     | MHz  |

|           | Efficiency                | ηdd1      | Vvcc1 = 3.3 V, lout = - 200 mA | 75    | 85    | _     | %    |

|           | Rise time                 | Trdd1     | Vvcc1 = 3.3 V, lout = 0 mA     |       | 50    | _     | μs   |

|           | Fall time                 | Tfdd1     | Vvcc1 = 3.3 V, lout = 0 mA     |       | 200   | _     | μs   |

|           | Output voltage            | Voutdd2   | lout = 0 to lomax              | 1.750 | 1.825 | 1.900 | V    |

|           | Maximum<br>output current | loutdd2   |                                | 600   |       | _     | mA   |

|           | Output ripple<br>voltage  | Vrpldd21  | lout = 0 to lomax              |       | 15    | _     | mV   |

| DC/DC2    | Input stability           | Vlinedd2  | Vvcc1 = 2.7 V to 5.5 V         |       | 10    |       | mV   |

| converter | Load stability            | Vloaddd2  | lout = $-1$ mA to lomax        |       |       | 20    | mV   |

|           | Oscillation<br>frequency  | Fdd2      | PWM mode                       |       | 1.7   | _     | MHz  |

|           | efficiency                | ηdd2      | Vvcc1 = 3.3 V, lout = - 200 mA | 80    | 90    |       | %    |

|           | Rise time                 | Trdd2     | Vvcc1 = 3.3 V, lout = 0 mA     |       | 50    | _     | μs   |

|           | Fall time                 | Tfdd2     | Vvcc1 = 3.3 V, lout = 0 mA     |       | 200   | _     | μs   |

|           | Output voltage            | Voutdd3   | lout = 0 to lomax              | 3.200 | 3.300 | 3.400 | V    |

|           | Maximum<br>output current | loutdd3   |                                | 650   |       | _     | mA   |

|           | Output ripple voltage     | Vrpldd31  | lout = 0 to lomax              |       | 60    | _     | mV   |

| DC/DC3    | Input stability           | Vlinedd3  | Vvcc1 = 2.7 V to 5.5 V         |       | 10    |       | mV   |

| converter | Load stability            | Vloaddd3  | lout = -1 mA to lomax          |       |       | 30    | mV   |

|           | Oscillation<br>frequency  | Fdd3      | PWM mode                       | _     | 1.7   |       | MHz  |

|           | efficiency                | ηdd3      | Vvcc1 = 3.3 V, lout = - 200 mA | 80    | 90    |       | %    |

|           | Rise time                 | Trdd3     | Vvcc1 = 3.3 V, lout = 0 mA     |       | 100   |       | μs   |

|           | Fall time                 | Tfdd3     | Vvcc1 = 3.3 V, lout = 0 mA     |       | 120   |       | μs   |

| Pai                                            | rameter                                                  | Symbol   | Condition                          |                     | Value |                 | Unit |

|------------------------------------------------|----------------------------------------------------------|----------|------------------------------------|---------------------|-------|-----------------|------|

| I di                                           |                                                          | Symbol   | Condition                          | Min                 | Тур   | Max             | Onit |

|                                                |                                                          | Vil1     | ONOFF                              | 0.0                 | —     | 0.3 	imes Vvcc1 | V    |

|                                                | land the set                                             | Vih1     | UNOFF                              | 0.7 ×<br>Vvcc1      |       | Vvcc1           | V    |

|                                                | Input voltage                                            | Vil2     |                                    | 0.0                 |       | 0.3 ×<br>Vvcc3  | V    |

|                                                |                                                          | Vih2     | LDOCNT1, LDOCNT2                   | 0.7 ×<br>Vvcc3      |       | Vvcc3           | V    |

| Start/stop control block                       | Output                                                   | Vol1     | XRST1, XRST2, lout = 1 mA          | 0.0                 |       | 0.15 ×<br>Vvcc3 | V    |

|                                                | voltage                                                  | Voh1     | XRST1, XRST2, lout = -1 mA         | $0.85 \times Vvcc3$ |       | Vvcc3           | V    |

|                                                | VCC1<br>power supply<br>detection voltage                | Vdetvon  | VCC1 rise = 0.1 V/10 μs            | 2.55                | 2.6   | 2.65            | V    |

|                                                | VCC1<br>Voltage for<br>power supply<br>cut-off detection | Vdetvoff | VCC1 fall = 0.3 V/10 μs            | 2.3                 | 2.4   | 2.5             | V    |

|                                                |                                                          | Vol32k   | RTC_CLK, lout = 0.5 mA             | 0.0                 |       | 0.15 ×<br>Vrtc  | V    |

|                                                | Output voltage                                           | Voh32k   | RTC_CLK, lout = - 0.5 mA           | 0.85 ×<br>Vrtc      |       | Vrtc            | V    |

| RTC block                                      | Internal<br>oscillation<br>capacitance 1                 | Cg       | OSCIN                              |                     | 10    |                 | pF   |

|                                                | Internal<br>oscillation<br>capacitance 2                 | Cd       | OSCOUT                             |                     | 10    |                 | pF   |

|                                                | Input voltage                                            | Vil14    | SCL, SDA (for input)               | 0.0                 |       | 0.3 ×<br>Vvcc3  | V    |

| I <sup>2</sup> C interface                     | input voltage                                            | Vih14    |                                    | 0.7 ×<br>Vvcc3      |       | Vvcc3           | V    |

|                                                | Output voltage                                           | Vol18    | SDA (for output)<br>lout = 3 mA    | 0.0                 |       | 0.4             | V    |

| VFIL1,                                         | Output voltage                                           | Vovfil1  | VFIL1                              | 1.175               | 1.225 | 1.275           | V    |

| VFIL2                                          |                                                          | Vovfil2  | VFIL2                              | 0.575               | 0.60  | 0.625           | V    |

| LDO5                                           | Output voltage                                           | Voutld5  | lout = 0 to lomax                  | 2.325               | 2.40  | 2.475           | V    |

| UVLO                                           | UVLO release<br>voltage                                  | Vuvlod   |                                    | 2.1                 | 2.2   | 2.3             | V    |

| •                                              | UVLO detection voltage                                   | Vuvlor   | _                                  | 2.0                 | 2.1   | 2.2             | V    |

| Over tem-<br>perature                          | Detection<br>temperature                                 | Totpd    |                                    | + 135               | + 150 | + 165           | °C   |

| protection<br>(OTP)                            | Release<br>temperature                                   | Totpr    | _                                  | + 105               | + 120 | + 135           | °C   |

| Output short<br>circuit<br>protection<br>(SCP) | Detection<br>protection time                             | Tshort   | Output = 0.6 V $\pm$ 0.2 V or less | 75                  | 100   | 125             | ms   |

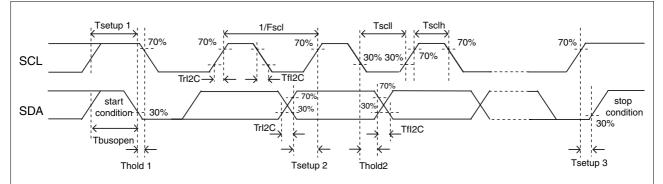

### 2. AC characteristics

|           | Parameter                                                  | Symbol   | Condition                                                                                                        |              | Value  |     | Unit |

|-----------|------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------|--------------|--------|-----|------|

|           | Farameter                                                  | Symbol   | Condition                                                                                                        | Min          | Тур    | Max | Unit |

| RTC block | Clock frequency                                            | Fck      | When using RTC_CLK,<br>and FC_12M (manufac-<br>tured by Epson Toyo-<br>com Corporation) for<br>external crystal. |              | 32.768 |     | kHz  |

|           | Clock duty                                                 | Rck      | When using RTC_CLK,<br>and FC_12M (manufac-<br>tured by Epson Toyo-<br>com Corporation) for<br>external crystal. | 25           | 50     | 75  | %    |

|           | Margin for oscillation                                     | Rfm      | Rmax = 90 k $\Omega$                                                                                             | 10 ×<br>Rmax |        |     | kΩ   |

|           | Clock frequency                                            | Fscl     | SCL                                                                                                              | _            |        | 400 | kHz  |

|           | Start condition hold time                                  | Thold1   | SCL, SDA                                                                                                         | 0.6          | —      |     | μs   |

|           | SCL clock L cycle                                          | Tscll    | SCL                                                                                                              | 1.3          |        |     | μs   |

|           | SCL clock H cycle                                          | Tsclh    | SCL                                                                                                              | 0.6          |        |     | μs   |

|           | Start condition set up time                                | Tsetup1  | SCL, SDA                                                                                                         | 0.6          |        |     | μs   |

| I²C       | Data hold time                                             | Thold2   | SCL, SDA                                                                                                         | 0            | —      | 0.9 | μs   |

| interface | Data set up time                                           | Tsetup2  | SCL, SDA                                                                                                         | 0.1          |        |     | μs   |

|           | Stop condition set up time                                 | Tsetup3  | SCL, SDA                                                                                                         | 0.6          |        |     | μs   |

|           | Bus open time between<br>stop condition-start<br>condition | Tbusopen | SDA                                                                                                              | 1.3          | _      |     | μs   |

|           | Rise time                                                  | Trl2C    | SCL, SDA                                                                                                         |              |        | 300 | ns   |

|           | Fall time                                                  | Tfl2C    | SCL, SDA                                                                                                         |              |        | 300 | ns   |

• I<sup>2</sup>C interface

### 3. Current dissipation

| Parameter       | Condition                                                                                  | Va  | Unit |      |

|-----------------|--------------------------------------------------------------------------------------------|-----|------|------|

|                 | Condition                                                                                  | Тур | Мах  | Onit |

| Standby current | ONOFF : L                                                                                  | 150 | 250  | μA   |

| ON current      | DC/DC1 converter, DC/DC2 converter : ON (no load)<br>LDO1, LDO2, LDO3, LDO4 : ON (no load) | 650 | 850  | μA   |

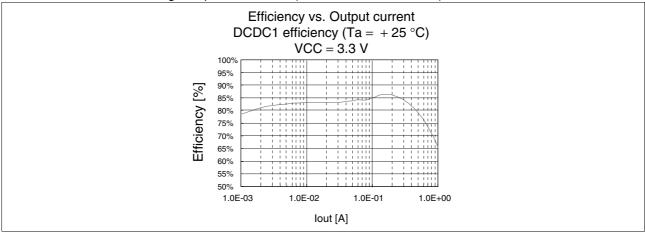

# ■ TYPICAL CHARACTERISTICS

For the reference of design, typical characteristics are shown below.

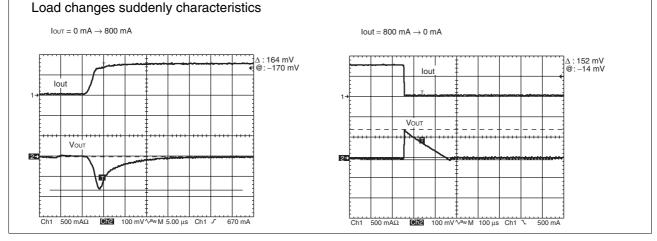

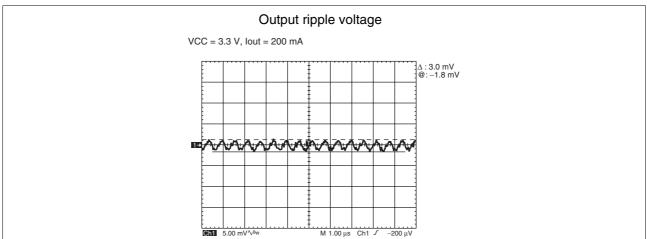

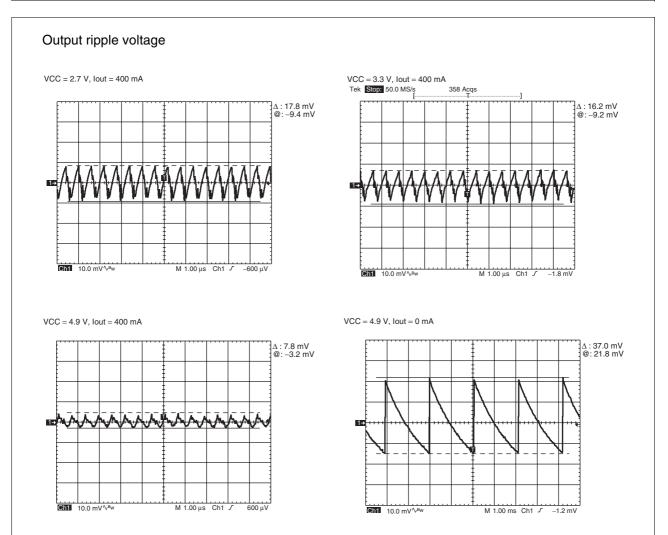

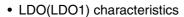

Characteristics of Voltage step-down DCDC (DCDC1, Vout = 1.200 V)

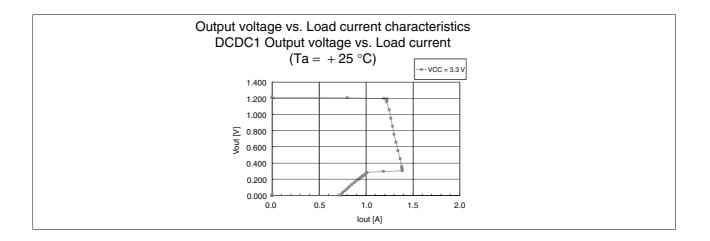

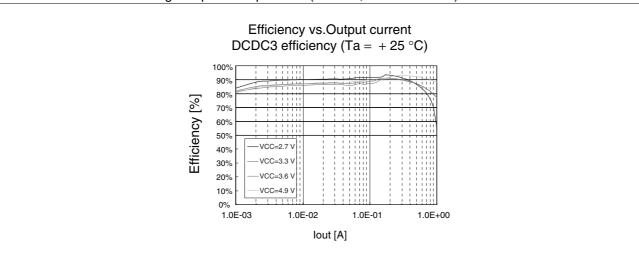

#### • Characteristics of Voltage step-down/up DCDC (DCDC3, Vout = 3.300 V)

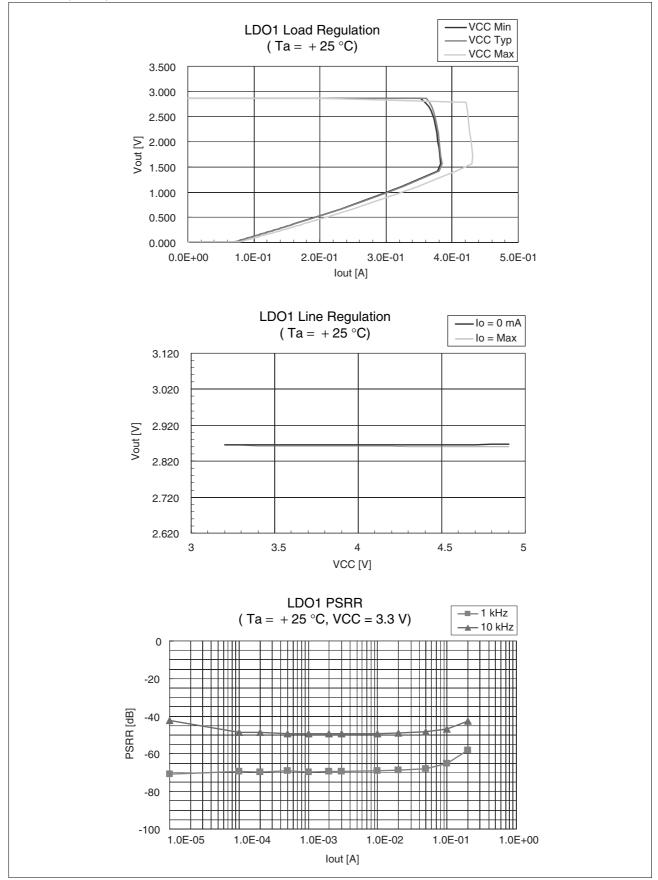

# ■ START/STOP CONTROL FUNCTION

Conditions of the VCC1 power supply pin and ONOFF, LDOCNT1 and LDOCNT2 pins and the setting of the REON register control the output of the LDO, the DC/DC converter and reset signals (XRST1 and XRST2). Also, the setting of the HRST register controls the output of the reset signal.

#### 1. Conditions for start and stop

#### • Conditions for start

When all conditions mentioned below are completed, the LDO and the DC/DC converter will start.

- VCC1 pin input voltage 2.6 V or more

- ONOFF pin input "H"

#### • Conditions for stop

When one of conditions mentioned below occurs, the LDO and the DC/DC converter will stop.

- VCC1 pin input voltage 2.4 V or less

- ONOFF pin input "L"

- When the REON bit in the REON register changes "0" to "1"

- OTP (Over temperature protection) detection

The start and stop status in the constant voltage power supply block by the VCC1 pin input voltage and the ONOFF pin input is reflected to the VCONT bit (address 05<sub>H</sub> [0]) in the STATE register.

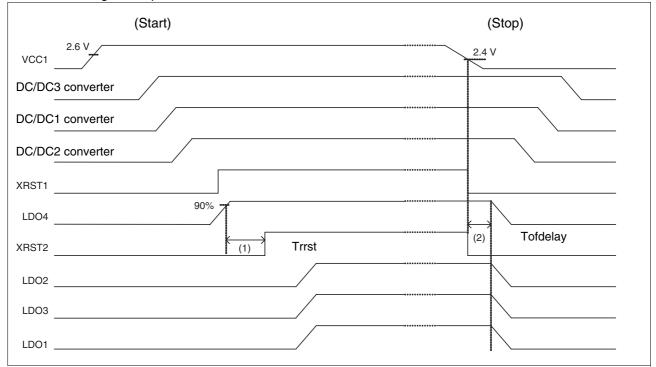

### 2. Start/stop sequence by VCC1 power supply pin and ONOFF pin

• When using VCC1 pin

When using ONOFF pin

| (Start)          | (Stop)       |

|------------------|--------------|

| ONOFF            |              |

| DC/DC3 converter |              |

| DC/DC1 converter |              |

| DC/DC2 converter |              |

| XRST1            |              |

| LDO24            |              |

| XRST2 Trrst      | (2) Tofdelay |

| LD02             |              |

| LDO3             |              |

| LD01             |              |

| Parameter | Symbol   |     |     | Unit |      |

|-----------|----------|-----|-----|------|------|

|           | Symbol   | Min | Тур | Max  | Unit |

| (1)       | Trrst    | 4   | 5   | 6    | ms   |

| (2)       | Tofdelay | 150 | 200 | 250  | μs   |

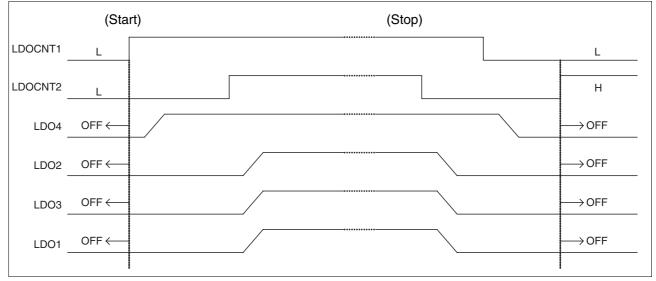

### 3. Start/stop by LDOCNT1 and LDOCNT2 pins (intermittent control)

When the XRST1 and the XRST2 pins are in "H", the LDO starts and stops depending on the conditions of the LDOCNT1 and the LDOCNT2 pins.

| Input co | Input condition |      | LDO2 | LDO3 | LDO4 |  |

|----------|-----------------|------|------|------|------|--|

| LDOCNT1  | LDOCNT2         | LDO1 | LDOZ | LDO3 | LDO4 |  |

| Н        | Н               | ON   | ON   | ON   | ON   |  |

| Н        | L               | OFF  | OFF  | OFF  | ON   |  |

| L        | L               | OFF  | OFF  | OFF  | OFF  |  |

| L        | Н               | OFF  | OFF  | OFF  | OFF  |  |

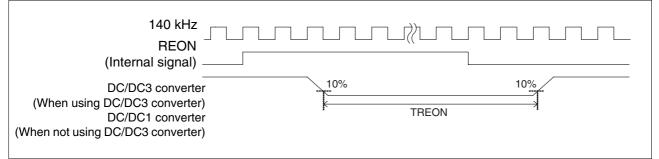

# 4. Start/stop by REON register (Restart power supply)

When "1" is written to the REON bit in the REON register (address  $04_{H}$  [0]), the power supply stops following the sequence and starts again after a fixed period has passed.

The STOPTIMEB bit (address  $04_{H}$  [5:4]) can set the time between the stop of the power supply and the restart of the power supply (calculated by the 140 kHz internal clock). The REON bit is automatically cleared after the time set by the STOPTIMEB bit has passed.

| Parameter | STOPTIMEB bit [1:0] |      |      | Unit |      |

|-----------|---------------------|------|------|------|------|

|           |                     | Min  | Тур  | Max  | Unit |

|           | 00в                 | 0.8  | 1.0  | 1.2  | ms   |

| TREON     | 01в                 | 3.4  | 4.0  | 5.2  | ms   |

| TREON     | 10в                 | 6.8  | 8.0  | 9.8  | ms   |

|           | 11в                 | 13.6 | 16.0 | 19.0 | ms   |

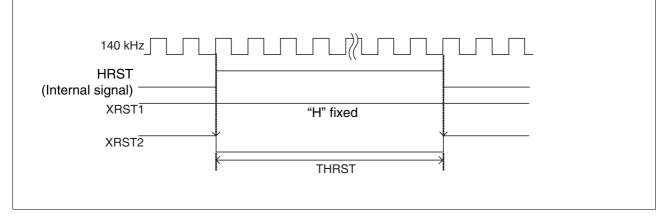

#### 5. Reset control by HRST register

When "1" is written to the HRST bit in the HRST register (address  $03_{H}$  [0]), the output of XRST2 remains at "L" level for a fixed period.

The STOPTIMEA bit (address  $03_{H}$  [5:4]) can set the time for remaining on XRST2 = "L". The HRST bit is automatically cleared after the time set by the STOPTIMEA bit has passed.

| Parameter | STOPTIMEA bit |      | Unit |      |      |

|-----------|---------------|------|------|------|------|

|           | [1:0]         | Min  | Тур  | Max  | Omit |

|           | 00в           | 0.8  | 1.0  | 1.2  | ms   |

| THRST     | 01в           | 3.4  | 4.0  | 5.2  | ms   |

|           | 10в           | 6.8  | 8.0  | 9.8  | ms   |

|           | 11в           | 13.6 | 16.0 | 19.0 | ms   |

# ■ 32.768 kHz OUTPUT (CMOS output)

If the crystal oscillator is connected to the OSCIN and the OSCOUT pins, the 32.768 kHz clock can be output from the RTC\_CLK pin.

### ■ I<sup>2</sup>C INTERFACE

This is the interface which is compliant with the I<sup>2</sup>C bus standard. The internal register data are read and write to the internal register data via two bidirectional bus lines which are the serial data line (SDA) and the serial clock line (SCL).

The MB39C316 has the following features.

- This LSI is set as slave, so the LSI cannot be set to master.

- The slave address is "2AH".

- Supports high speed mode (Max 400 kbps)

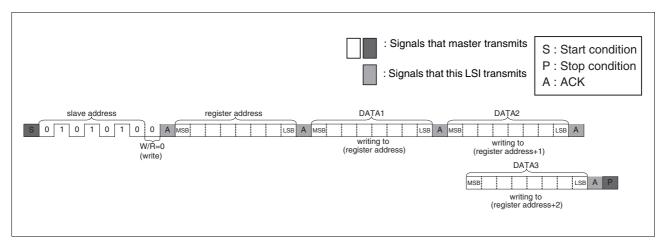

#### 1. Writing flow

- (1) Detect start condition

- (2) Receive slave address ("2AH") and W/R bit ("0")

- (3) Transmit ACK

- (4) Receive register address

- (5) Transmit ACK

- (6) Receive write data

- (7) Transmit ACK

- (8) Increase the register address and then go back to (6), when a stop condition is not detected.\*

- (9) Communication stops after detecting a stop condition.

- \* : Increment stops at address FF<sub>H</sub> and keeps at FF<sub>H</sub>. The flow does not go back to 00<sub>H</sub>.

Notes : • If the register address which does not exist or the bit which are not assigned is specified, ACK will be returned, but data will not be written.

• If writing is set to the Read Only address, ACK will not be returned, but data will not be written.

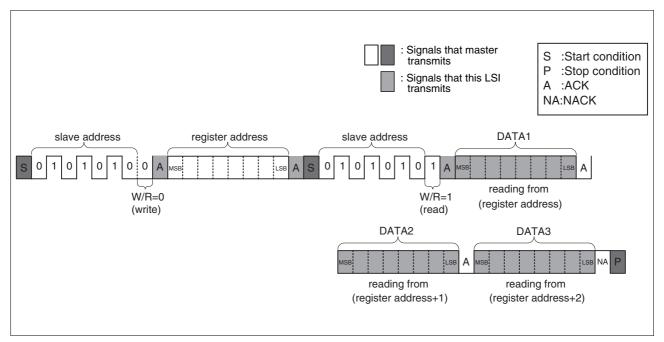

#### 2. Reading flow

- (1) Detect start condition

- (2) Receive slave address (" $2A_H$ ") and W/R bit ("0")

- (3) Transmit ACK

- (4) Receive register address

- (5) Transmit ACK

- (6) Detect start condition

- (7) Receive slave address ("2AH") and W/R bit ("1")

- (8) Transmit ACK

- (9) Transmission of read data

- (10) Increase the register address and then go back to (9).\* If [1] ACK is received. Release the bus if [2] NACK is received.

- (11) Communication stops after detecting a stop condition.

- $^{*}$  : Increment stops at address FFH and keeps FFH. Increment does not go back to 00H.

Note : If the register address which does not exist and the bit which does not execute the bit assign are specified, read data becomes "0".

# REGISTERS

### 1. Address allocation

| Ad-<br>dress | Turne                                  | Register name                                       | W/R |          |          |                | Register       | Contents |          |          |          | Default   |

|--------------|----------------------------------------|-----------------------------------------------------|-----|----------|----------|----------------|----------------|----------|----------|----------|----------|-----------|

| (hex)        | Туре                                   | (function)                                          | W/n | D7       | D6       | D5             | D4             | D3       | D2       | D1       | D0       | value     |

| 00           | Reset                                  | SRST<br>(Soft reset control)                        | *   | RSTDET   | —        | —              | —              | —        | —        | —        | SRST     | 0000 0000 |

| 01           | Version                                | VERSION<br>(Information about<br>versions)          | R   | _        | _        |                | _              | VER3     | VER2     | VER1     | VER0     | 0000 0011 |

| 02           | Constant<br>voltage<br>power<br>supply | VSEL_SYN<br>(LDO<br>voltage setting)                | WR  | _        | _        | _              | _              | _        | _        | _        | VSEL_SYN | 0000 0000 |

| 03           | Reset                                  | HRST<br>(Hard reset control)                        | WR  | HRDET    | _        | STOPTI<br>MEA1 | STOPTI<br>MEA0 | _        | —        | —        | HRST     | 0000 0000 |

| 04           | Power<br>supply<br>control             | REON<br>(Control of<br>re-starting power<br>supply) | WR  | REDET    | _        | STOPTI<br>MEB1 | STOPTI<br>MEB0 | _        | _        | _        | REON     | 0000 0000 |

| 05           | Notice of state                        | STATE<br>(Notice of state)                          | R   | —        | _        | _              | _              | CUR_lim  | OTP      | RTC_OSC  | VCONT    | 0000 0000 |

| 06           | General                                | GP<br>(General-purpose<br>register)                 | WR  | GP7      | GP6      | GP5            | GP4            | GP3      | GP2      | GP1      | GP0      | 0000 0000 |

| 07-7F        |                                        | —                                                   |     |          |          | _              |                | _        |          |          |          | _         |

| 80-8B        | TEST                                   | reserved<br>(reserved bytes)                        | _   | reserved | reserved | reserved       | reserved       | reserved | reserved | reserved | reserved | _         |

| 8C           | —                                      |                                                     | _   | _        | _        | _              | —              | _        | _        | —        | —        | _         |

$^{\ast}$  : 00\_H [D0] is Write only, [D7] is Write/Read.

- Although data which "\_" is shown is accessible to read and write, writing is invalid and reading data becomes "0".

- All registers are initialized to the default value by power-on reset.

- Executing the soft reset control initializes all Write registers to the default value. There is a possibility that written data during execution of the soft reset control is not reflected correctly.

'SU

Note : Address  $80_{\text{H}}$  to  $8B_{\text{H}}$  is mapped on the registers for this LSI test. It is prohibited to write to  $80_{\text{H}}$  to  $8B_{\text{H}}$  when using this LSI.

### 2. Functional description

• Soft reset control (Address 00H)

|          | D7     | D6 | D5 | D4 | D3 | D2 | D1 | D0   |

|----------|--------|----|----|----|----|----|----|------|

| At Write | RSTDET | —  | —  | —  |    | —  | —  | SRST |

| At Read  | RSTDET | 0  | 0  | 0  | 0  | 0  | 0  | 0    |

| Default  | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0    |

#### bit [7] RSTDET : Register reset history bit

| RSTDET | Operation                                                           |

|--------|---------------------------------------------------------------------|

| 0      | No execution of soft reset control (Read)/RSTDET clear bits (Write) |

| 1      | Execution of register reset by soft reset control (Read)            |

This bit saves the execution history of the reset operation by the soft reset control. If the reset operation by the soft reset control is executed, this bit is set to "1".

When clearing this bit, write "00H" to this register.

Writing RSTDET = "1" is ignored.

#### bit [0] SRST : Register reset bit

| SRST | Operation                                                         |

|------|-------------------------------------------------------------------|

| 0    | Normal operation                                                  |

| 1    | Reset the Write register for other than address 00 <sub>H</sub> . |

If writing "1" to this bit, all Write registers are reset, and the read value for address  $00_{\text{H}}$  is " $80_{\text{H}}$ ". The reset state will be remained for about 15 µs after writing SRST = "1". This bit is for the write only and the read value is always "0".

- Notes : If RSTDET = "0" and SRST = "1" are written simultaneously, RSTDET = "0" is ignored. The reset operation by SRST = "1" is executed and the RSTDET bit is set to "1".

- There is a possibility that written data during the soft reset control execution is not written correctly.

#### • Information about versions (Address 01H)

|          | D7 | D6 | D5 | D4 | D3                           | D2   | D1   | D0   |  |

|----------|----|----|----|----|------------------------------|------|------|------|--|

| At Write | _  | _  |    | _  | _                            | _    |      | —    |  |

| At Read  | 0  | 0  | 0  | 0  | VER3                         | VER2 | VER1 | VER0 |  |

| Default  | 0  | 0  | 0  | 0  | Fixed value for each version |      |      |      |  |

#### bit [3:0] VER : Version display bit

| VER  | Operation |

|------|-----------|

| 0000 | —         |

| 0001 | 1         |

| 0010 | 2         |

| 0011 | 3         |

| :    | :         |

This register reads information about device's versions.

• LDO voltage setting (Address 02<sub>H</sub>)

|          | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0       |

|----------|----|----|----|----|----|----|----|----------|

| At Write | _  | —  | —  | _  | —  | _  | —  | VSEL_SYN |

| At Read  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | VSEL_SYN |

| Default  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0        |

bit [0] VSEL\_SYN : Selection bit of LDO3 voltage

| VSEL_SYN | Operation   |  |  |  |  |

|----------|-------------|--|--|--|--|

| 0        | 1.2 V (Typ) |  |  |  |  |

| 1        | 1.3 V (Typ) |  |  |  |  |

This bit switches output voltage of LDO3.

• Hard reset control (Address 03H)

|          | D7    | D6 | D5         | D4         | D3 | D2 | D1 | D0   |

|----------|-------|----|------------|------------|----|----|----|------|

| At Write | HRDET | —  | STOPTIMEA1 | STOPTIMEA0 |    |    |    | HRST |

| At Read  | HRDET | 0  | STOPTIMEA1 | STOPTIMEA0 | 0  | 0  | 0  | HRST |

| Default  | 0     | 0  | 0          | 0          | 0  | 0  | 0  | 0    |

#### bit [7] HRDET : HRST history bit

| HRDET | Operation                                                          |  |

|-------|--------------------------------------------------------------------|--|

| 0     | No execution of hard reset control (Read)/HRDET clear bits (Write) |  |

| 1     | Execution of XRST2 reset by hard reset control (Read)              |  |

This bit saves the execution history of the reset operation by the hard reset control. The reset operation by the hard reset control sets this bit to "1" (same time as re-writing of the HRST bit). Write " $00_{\text{H}}$ " to this register when clearing this bit. Writing HRDET = "1" is ignored.

#### bit [5:4] STOPTIMEA : XRST2 = "L" time setting bit

| STOPTIMEA | Operation   |

|-----------|-------------|

| 00        | 1 ms (Typ)  |

| 01        | 4 ms (Typ)  |

| 10        | 8 ms (Typ)  |

| 11        | 16 ms (Typ) |

This bit selects the time of XRST2 = "L" by the hard reset control.

#### bit [0] HRST : HRST Control bit

| HRST | Operation                                        |

|------|--------------------------------------------------|

| 0    | Normal operation (Read)                          |

| 1    | Instructions of hard reset control start (Write) |

When writing "1" to this bit, the output of the XRST2 pin will remain in "L" for the time set by the STOPTIMEA bit.

This bit is automatically cleared after the time set has passed.

Note : If HRDET = "0" and HRST = "1" are written at the same time, HRDET = "0" is ignored. The reset operation is executed by HRST = "1" and the HRDET bit is set to "1".