# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 16-bit Proprietary Microcontroller

CMOS

# F<sup>2</sup>MC-16F MB90220 Series

# MB90223/224/P224A/W224A MB90P224B/W224B/V220

### ■ OUTLINE

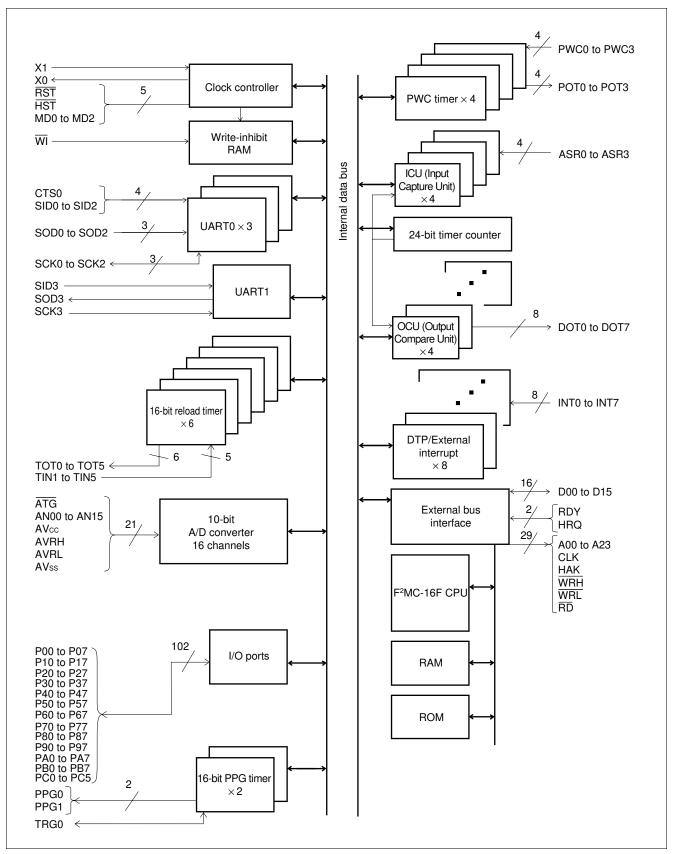

The MB90220 series of general-purpose high-performance 16-bit microcontrollers has been developed primarily for applications that demand high-speed real-time processing and is suited for industrial applications, office automation equipment, process control, and other applications. The F<sup>2</sup>MC-16F CPU is based on the F<sup>2</sup>MC\*-16 Family with improved high-level language support functions and task switching functions, as well as additional addressing modes.

On-chip peripheral resources include a 4-channel PWC timer, a 4-channel ICU (Input Capture Unit), a 1-channel 24-bit timer counter, an 8-channel OCU (Output Compare Unit), a 6-channel 16-bit reload timer, a 2-channel 16-bit PPG timer, a 10-bit A/D converter with 16 inputs, and a 4-channel serial port with a UART function (one channel includes the CTS function).

The MB90P224B, MB90W224B, MB90224 is under development.

\*: F<sup>2</sup>MC stands for FUJITSU Flexible Microcontroller.

### ■ FEATURES

#### F<sup>2</sup>MC-16F CPU

- Minimum execution time: 62.5 ns/16 MHz oscillation (using a duty control system)

- Instruction sets optimized for controllers

Upward object-compatible with the F<sup>2</sup>MC-16(H)

Various data types (bit, byte, word, and long-word)

Instruction cycle improved to speed up operation

Extended addressing modes: 25 types

High coding efficiency

Access method (bank access with linear pointer)

Enhanced multiplication and division instructions (with signed instructions added)

Higher-precision operation using a 32-bit accumulator

- Extended intelligent I/O service (automatic transfer function independent of instructions) Access area expanded to 64 Kbytes

- Enhanced instruction set applicable to high-level language (C) and multitasking System stack pointer

Enhanced pointer-indirect instructions

Barrel shift instruction

Stack check function

- · Increased execution speed: 8-byte instruction queue

- · Powerful interrupt functions: 8 levels and 28 sources

#### **Peripheral resources**

EPROM

- Mask ROM : 64 Kbytes (MB90223)

- 96 Kbytes (MB90224)

- : 96 Kbytes (MB90W224A/W224B)

- One-time PROM : 96 Kbytes (MB90P224A/P224B)

- RAM: 3 Kbytes (MB90223)

- 4.5 Kbytes (MB90224/MB90W224A/P224A/W224B/P224B) 5 Kbytes (MB90V220)

- General-purpose ports: max. 102 channels

- ICU (Input Capture Unit): 4 channels

- 24-bit timer counter: 1 channel

- OCU (Output Compare Unit): 8 channels

- · PWC timer with time measurement function: 4 channels

- 10-bit A/D converter: 16 channels

- UART: 4 channels (one channel includes CTS function)

- 16-bit reload timer

- Toggled output, external clock, and gate functions: 6 channels

- 16-bit PPG timer: 2 channels

- DTP/External-interrupt inputs: 8 channels (of which five have edge detection function only)

- Write-inhibit RAM: 0.5 Kbytes (1 Kbyte for MB90V220)

- Timebase counter: 18 bits

- Clock gear function

- Low-power consumption mode

Sleep mode

- Stop mode

- Hardware standby mode

#### **Product description**

- MB90223/224 are mask ROM product.

- MB90P224A/P224B are one-time PROM products.

- MB90W224A/W224B are EPROM products. ES only.

- Operating temperature of MB90P224A/W224A is -40°C to +85°C. (However, the AC characteristics is assured in -40°C to +70°C)

- Operation clock cycle of MB90223 is 10 MHz to 12 MHz.

- MB90V220 is a evaluation device for the program development. ES only.

### PRODUCT LINEUP

| Part number<br>Item          | MB90223                                                                                                                                                                                                                                                                                                              | MB90224                                                                                                                       | MB90P224A<br>MB90P224B                     | MB90W224A<br>MB90W224B | MB90V220          |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------|-------------------|--|--|--|

| Classification               | Mask ROM<br>product                                                                                                                                                                                                                                                                                                  | Mask ROM<br>product                                                                                                           | One-time<br>PROM product                   | EPROM<br>product       | Evaluation device |  |  |  |

| ROM size                     | 64 Kbytes                                                                                                                                                                                                                                                                                                            | 96 Kbytes                                                                                                                     | 96 Kbytes                                  | 96 Kbytes              | None              |  |  |  |

| RAM size                     | 3 Kbytes                                                                                                                                                                                                                                                                                                             | 4.5 Kbytes                                                                                                                    | 4.5 Kbytes                                 | 4.5 Kbytes             | 5 Kbytes          |  |  |  |

| CPU functions                | lns<br>Ins<br>Da<br>Mi                                                                                                                                                                                                                                                                                               | e number of instru<br>struction bit length:<br>struction length:<br>ta bit length:<br>nimum execution ti<br>errupt processing | 8 or 16<br>1 to 7<br>1, 4, 8<br>me: 62.5 n |                        |                   |  |  |  |

| Ports                        | I/C                                                                                                                                                                                                                                                                                                                  | ) ports (N-ch open-<br>) ports (CMOS):<br>tal:                                                                                | -drain): 16<br>86<br>102                   |                        |                   |  |  |  |

| ICU<br>(Input Capture Unit)  | Number of channels: 4<br>Rising edge/falling edge/both edges selectable                                                                                                                                                                                                                                              |                                                                                                                               |                                            |                        |                   |  |  |  |

| 24-bit timer counter         | Number of channels: 1<br>Overflow interrupt, intermediate bit interrupt                                                                                                                                                                                                                                              |                                                                                                                               |                                            |                        |                   |  |  |  |

| OCU<br>(Output Compare Unit) | Number of channels: 8<br>Pin change source (match signal causes register value transfer/general-purpose port)                                                                                                                                                                                                        |                                                                                                                               |                                            |                        |                   |  |  |  |

| PWC timer                    | Number of channels: 4<br>16-bit reload timer operation (operation clock cycle: 0.25 μs to 1.31 ms)<br>16-bit pulse-width count operation (Allowing continuous/one-shot measurement, H/L width<br>measurement, inter-edge measurement, and divided-frequency measurement)                                             |                                                                                                                               |                                            |                        |                   |  |  |  |

| 10-bit<br>A/D converter      | Resolution: 10 bits<br>Number of inputs: 16<br>Single conversion mode (conversion of each channel)<br>Scan conversion mode (continuous conversion for up to 16 consecutive channels)<br>Continuous conversion mode (repeated conversion of specified channel)<br>Stop conversion mode (conversion every fixed cycle) |                                                                                                                               |                                            |                        |                   |  |  |  |

| UART                         | Number of channels: 4 (1 channel with CTS function)<br>Clock-synchronous transfer mode<br>(full-duplex double buffering, 7 to 9-bit data length, 2400 to 62500 bps)<br>Asynchronous transfer mode<br>(full-duplex double buffering, 7 to 9-bit data length, 2400 to 62500 bps)                                       |                                                                                                                               |                                            |                        |                   |  |  |  |

| 16-bit reload<br>timer       | 16-bit i                                                                                                                                                                                                                                                                                                             |                                                                                                                               | umber of channels:<br>ion (operation cloc  |                        | 1.05 s)           |  |  |  |

(Continued)

| Part number<br>Item        | MB90223                                                                                                                                                                                                                                                                           | MB90224      | MB90P224A<br>MB90P224B | MB90W224A<br>MB90W224B | MB90V220     |  |  |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------|------------------------|--------------|--|--|--|

| 16-bit PPG timer           | Number of channels: 2<br>16-bit PPG operation (operation clock cycle: 0.25 μs to 6 s)                                                                                                                                                                                             |              |                        |                        |              |  |  |  |

| DTP/External<br>interrupts | Number of inputs: 8 (of which five have edge detection function only)<br>External interrupt mode (allowing interrupts to activate at four different request levels)<br>Simple DMA transfer mode (allowing extended I <sup>2</sup> OS to activate at two different request levels) |              |                        |                        |              |  |  |  |

| Write-inhibited<br>RAM     | RAM size: 512 bytes (1 Kbyte for MB90V220)<br>RAM write-protectable with WI pin                                                                                                                                                                                                   |              |                        |                        |              |  |  |  |

| Standby mode               | stop mode (activated by software or hardware) and sleep mode                                                                                                                                                                                                                      |              |                        |                        |              |  |  |  |

| Gear function              | Machine clock operation frequency switching: 16 MHz, 8 MHz, 4 MHz, 1 MHz (at 16-MHz oscillation)                                                                                                                                                                                  |              |                        |                        |              |  |  |  |

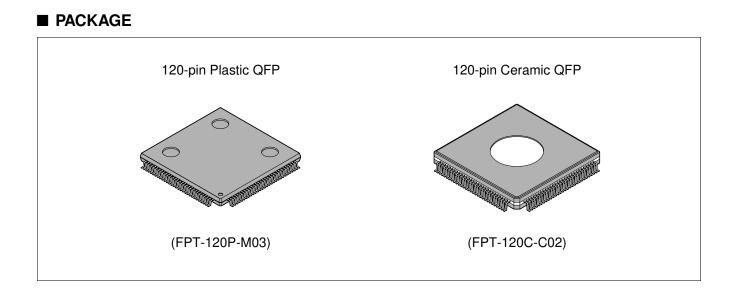

| Package                    |                                                                                                                                                                                                                                                                                   | FPT-120P-M03 |                        | FPT-120C-C02           | PGA-256C-A02 |  |  |  |

Note: MB90V220 is a evaluation device, therefore, the electrical characteristics are not assured.

### ■ DIFFERENCES BETWEEN MB90223/224 (MASK ROM PRODUCT) AND MB90P224A/ W224A/P224B/W224B

| Part number<br>Item   | MB90223               | MB90224               | MB90P224A<br>MB90P224B | MB90W224A<br>MB90W224B |

|-----------------------|-----------------------|-----------------------|------------------------|------------------------|

| ROM                   | Mask ROM<br>64 Kbytes | Mask ROM<br>96 Kbytes | OTPROM<br>96 Kbytes    | EPROM<br>96 Kbytes     |

| Pin functions: pin 87 | MD2 pin               |                       | MD2/                   | <b>/</b> ₽₽ pin        |

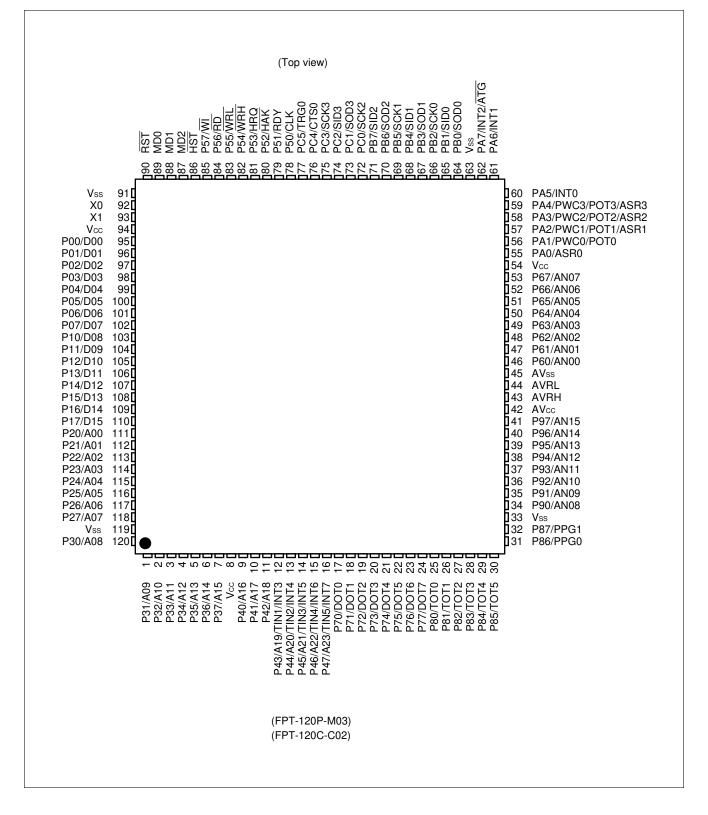

#### PIN ASSIGNMENT

### ■ PIN DESCRIPTION

| Pin no.        | Din nomo           | Circuit | Function                                                                                                                                                                                                          |

|----------------|--------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*           | Pin name           | type    | Function                                                                                                                                                                                                          |

| 92,<br>93      | X0,<br>X1          | A       | Crystal oscillation pins (16 MHz)                                                                                                                                                                                 |

| 89 to 87       | MD0 to MD2         | D       | Operation mode specification input pins<br>Connect directly to Vcc or Vss.                                                                                                                                        |

| 90             | RST                | G       | External reset request input                                                                                                                                                                                      |

| 86             | HST                | E       | Hardware standby input pin                                                                                                                                                                                        |

| 95 to 102      | P00 to P07         | С       | General-purpose I/O ports<br>This function is valid only in single-chip mode.                                                                                                                                     |

|                | D00 to D07         |         | Output pins for low-order 8 bits of the external address bus.<br>This function is valid only in modes where the external bus is<br>enabled.                                                                       |

| 103 to 110     | P10 to P17         | С       | General-purpose I/O ports<br>This function is valid only in single-chip mode or when the external bus<br>is enabled and the 8-bit data bus specification has been made.                                           |

|                | D08 to D15         |         | I/O pins for higher-order 8 bits of the external data bus<br>This function is valid only when the external bus is enabled and the<br>16-bit bus specification has been made.                                      |

| 111 to 118     | P20 to P27         | С       | General-purpose I/O ports<br>This function is valid only in single-chip mode.                                                                                                                                     |

|                | A00 to A07         |         | Output pins for lower-order 8 bits of the external address bus<br>This function is valid only in modes where the external bus is<br>enabled.                                                                      |

| 120,<br>1 to 7 | P30,<br>P31 to P37 | С       | General-purpose I/O ports<br>This function is valid either in single-chip mode or when the address<br>mid-order control register specification is "port".                                                         |

|                | A08,<br>A09 to A15 |         | Output pins for mid-order 8 bits of the external address bus<br>This function is valid in modes where the external bus is enabled and<br>the address mid-order control register specification is "address".       |

| 9 to 11        | P40 to P42         | С       | General-purpose I/O ports<br>This function is valid either in single-chip mode or when the address<br>high-order control register specification is "port".                                                        |

|                | A16 to A18         |         | Output pins for higher-order 8 bits of the external address bus<br>This function is valid in modes where the external bus is enabled and<br>the address high-order control register specification is "address".   |

| 12 to 16       | P43 to P47         | С       | General-purpose I/O ports<br>This function is valid when either single-chip mode is enabled or the<br>address higher-order control register specification is "port".                                              |

|                | A19 to A23         |         | Output pins for higher-order 8 bits of the external address bus<br>This function is valid in modes where the external bus is enabled and<br>the address higher-order control register specification is "address". |

|                | TIN1 to TIN5       |         | 16-bit reload timer input pins<br>This function is valid when the timer input specification is "enabled".<br>The data on the pins is read as timer input (TIN1 to TIN5).                                          |

\* : FPT-120P-M03, FPT-120C-C02

-

| Pin no.  | – Pin name   | Circuit | Function                                                                                                                                                                                                                                                                                                                            |

|----------|--------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*     |              | type    |                                                                                                                                                                                                                                                                                                                                     |

| 12 to 16 | INT3 to INT7 | С       | External interrupt request input pins<br>When external interrupts are enabled, these inputs may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on these pins, except when using them for output<br>deliberately.                                                                  |

| 78       | P50          | С       | General-purpose I/O port<br>This function is valid in single-chip mode and when the CLK output<br>specification is disabled.                                                                                                                                                                                                        |

|          | CLK          |         | CLK output pin<br>This function is valid in modes where the external bus is enabled and<br>the CLK output specification is enabled.                                                                                                                                                                                                 |

| 79       | P51          | С       | General-purpose I/O port<br>This function is valid in single-chip mode or when the ready function<br>is disabled.                                                                                                                                                                                                                   |

|          | RDY          |         | Ready input pin<br>This function is valid in modes where the external bus is enabled and<br>the ready function is enabled.                                                                                                                                                                                                          |

| 80       | P52          | С       | General-purpose I/O port<br>This function is valid in single-chip mode or when the hold function is<br>disabled.                                                                                                                                                                                                                    |

|          | HAK          |         | Hold acknowledge output pin<br>This function is valid in modes where the external bus is enabled and<br>the hold function is enabled.                                                                                                                                                                                               |

| 81       | P53          | С       | General-purpose I/O port<br>This function is valid in single-chip mode or external bus mode and<br>when the hold function is disabled.                                                                                                                                                                                              |

|          | HRQ          | -       | Hold request input pin<br>This function is valid in modes where the external bus is enabled and<br>the hold function is enabled.<br>During this operation, the input may be used suddenly at any time;<br>therefore, it is necessary to stop output by other fuctions on this pin,<br>except when using it for output deliberately. |

| 82       | P54          | С       | General-purpose I/O port<br>This function is valid in single-chip mode, when the external bus is in<br>8-bit mode, or when WRH pin output is disabled.                                                                                                                                                                              |

|          | WRH          |         | Write strobe output pin for the high-order 8 bits of the data bus<br>This function is valid in modes where the external bus is enabled, the<br>external bus is in 16-bit mode, and WRH pin output is enabled.                                                                                                                       |

| 83       | P55          | С       | General-purpose I/O port This function is valid in single-chip mode or when $\overline{\text{WRL}}$ pin output is disabled.                                                                                                                                                                                                         |

|          | WRL          |         | Write strobe output pin for the low-order 8 bits of the data bus<br>This function is valid in modes where the external bus is enabled and<br>WRL pin output is enabled.                                                                                                                                                             |

\* : FPT-120P-M03, FPT-120C-C02

| Pin no.   | – Pin name    | Circuit | Function                                                                                                                                                                                                                                  |

|-----------|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*      |               | type    |                                                                                                                                                                                                                                           |

| 84        | P56           | С       | General-purpose I/O port<br>This function is valid in single-chip mode. This function is valid in<br>modes where the external bus is valid.                                                                                               |

|           | RD            |         | Read strobe output pin for the data bus<br>This function is valid in modes where the external bus is enabled.                                                                                                                             |

| 85        | P57           | В       | General-purpose I/O port<br>This function is always valid.<br>When these pins are open in input mode, through current may leak in<br>stop mode/reset mode, be sure to fix these pins to Vcc/Vss level to<br>use these pins in input mode. |

|           | WI            |         | RAM write disable request input<br>During this operation, the input may be used suddenly at any time;<br>therefore, it is necessary to stop output by other fuctions on this pin,<br>except when using it for output deliberately.        |

| 46 to 53  | P60 to P67    | F       | Open-drain I/O ports<br>This function is valid when the analog input enable register<br>specification is "port".                                                                                                                          |

|           | AN00 to AN07  |         | 10-bit A/D converter analog input pins<br>This function is valid when the analog input enable register<br>specification is "analog input".                                                                                                |

| 17 to 24  | P70 to P77    | С       | General-purpose I/O ports<br>This function is valid when the output specification for DOT0 to DOT7<br>is "disabled".                                                                                                                      |

|           | DOT0 to DOT7  |         | This function is valid when OCU (output compare unit) output is enabled.                                                                                                                                                                  |

| 25 to 30  | P80 to P85    | С       | General-purpose I/O ports<br>This function is valid when the output specification for TOT0 to TOT5<br>is "disabled".                                                                                                                      |

|           | TOT0 to TOT5  |         | 16-bit reload timer output pins (TOT0 to TOT5)                                                                                                                                                                                            |

| 31,<br>32 | P86,<br>P87   | С       | General-purpose I/O ports<br>This function is valid when the PPG0, and PPG1 output specification<br>is "disabled".                                                                                                                        |

|           | PPG0,<br>PPG1 |         | 16-bit PPG timer output pins<br>This function is valid when the PPG control/status register<br>specification is "PPG output pins".                                                                                                        |

| 34 to 41  | P90 to P97    | F       | Open-drain I/O ports<br>This function is valid when the analog input enable register<br>specification is "port".                                                                                                                          |

|           | AN08 to AN15  |         | 10-bit A/D converter analog input pins<br>This function is valid when the analog input enable register<br>specification is "analog input".                                                                                                |

\* : FPT-120P-M03, FPT-120C-C02

| <b>QFP</b> *<br>55 | PA0           | type<br>C |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55                 |               | С         |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                    | 1000          |           | General-purpose I/O port<br>This function is always valid.                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | ASR0          |           | ICU (input capture unit) input pin<br>This function is valid during ICU (input capture unit) input operations.                                                                                                                                                                                                                                                                                                                                            |

| 56                 | PA1           | С         | General-purpose I/O port<br>This function is always valid.                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | PWC0          |           | PWC input pin<br>During PWC0 input operations, this input may be used suddenly at<br>any time; therefore, it is necessary to stop output by other functions<br>on this pin, except when using it for output deliberately.                                                                                                                                                                                                                                 |

|                    | POT0          |           | PWC output pin<br>This function is valid during PWC output operations.                                                                                                                                                                                                                                                                                                                                                                                    |

| 57 to 59           | PA2 to PA4    | С         | General-purpose I/O ports<br>This function is always valid.                                                                                                                                                                                                                                                                                                                                                                                               |

|                    | PWC1 to PWC3  |           | PWC input pins<br>This function is valid during PWC input operations.<br>During PWC1 to PWC3 input operations, this input may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on this pin, except when using it for output deliberately.                                                                                                                                                                 |

|                    | POT1 to POT3  |           | PWC output pins<br>This function is valid during PWC output operations.                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | ASR1 to ASR3  |           | ICU (input capture unit) input pins<br>This function is valid during ICU (input capture unit) input operations.                                                                                                                                                                                                                                                                                                                                           |

| 60,<br>61          | PA5,<br>PA6   | В         | General-purpose I/O ports<br>This function is always valid.<br>When these pins are open in input mode, through current may leak in<br>stop mode/reset mode, be sure to fix these pins to Vcc/Vss level to<br>use these pins in input mode.                                                                                                                                                                                                                |

|                    | INTO,<br>INT1 |           | DTP/External interrupt request input pins<br>When DTP/external interrupts are enabled, these inputs may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on these pins, except when using them for output<br>deliberately.<br>When these pins are open in input mode, through current may leak in<br>stop mode/reset mode, be sure to fix these pins to Vcc/Vss level to<br>use these pins in input mode. |

| 62                 | PA7           | В         | General-purpose I/O port<br>This function is always valid.<br>When these pins are open in input mode, through current may leak in<br>stop mode/reset mode, be sure to fix these pins to Vcc/Vss level to<br>use these pins in input mode.                                                                                                                                                                                                                 |

\* : FPT-120P-M03, FPT-120C-C02

| Pin no. | Pin name | Circuit | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*    |          | type    |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 62      | INT2     | В       | DTP/External interrupt request input pin<br>When DTP/external interrupts are enabled, these inputs may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on these pins, except when using them for output<br>deliberately.<br>When these pins are open in input mode, through current may leak in<br>stop mode/reset mode, be sure to fix these pins to Vcc/Vss level to<br>use these pins in input mode. |

|         | ATG      |         | 10-bit A/D converter external trigger input pin When these pins are open in input mode, through current may leak in stop mode/reset mode, be sure to fix these pins to $V_{\rm CC}/V_{\rm SS}$ level to use these pins in input mode.                                                                                                                                                                                                                    |

| 64      | PB0      | С       | General-purpose I/O port<br>This function is valid when the UART0 (ch.0) serial data output<br>specification is "disabled".                                                                                                                                                                                                                                                                                                                              |

|         | SOD0     | _       | UART0 (ch.0) serial data output<br>This function is valid when the UART0 (ch.0) serial data output<br>specification is "enabled".                                                                                                                                                                                                                                                                                                                        |

| 65      | PB1      | С       | General-purpose I/O port<br>This function is always valid.                                                                                                                                                                                                                                                                                                                                                                                               |

|         | SID0     |         | UART0 (ch.0) serial data input pin<br>During UART0 (ch.0) input operations, this input may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on this pin, except when using it for output deliberately.                                                                                                                                                                                                   |

| 66      | PB2      | С       | General-purpose output port<br>This function is valid when the UART0 (ch.0) clock output<br>specification is "disabled".                                                                                                                                                                                                                                                                                                                                 |

|         | SCK0     |         | UART0 (ch.0) clock output pin<br>The clock output function is valid when the UART0 (ch.0) clock output<br>specification is "enabled".<br>UART0 (ch.0) external clock input pin. This function is valid when the<br>port is in input mode and the UART0 (ch.0) specification is external<br>clock mode.                                                                                                                                                   |

| 67      | PB3      | С       | General-purpose I/O port<br>This function is valid when the UART0 (ch.1) serial data output<br>specification is "disabled".                                                                                                                                                                                                                                                                                                                              |

|         | SOD1     |         | UART0 (ch.1) serial data output pin<br>This function is valid when the UART0 (ch.1) serial data output<br>specification is "enabled".                                                                                                                                                                                                                                                                                                                    |

| 68      | PB4      | С       | General-purpose I/O port<br>This function is always valid.                                                                                                                                                                                                                                                                                                                                                                                               |

|         | SID1     |         | UART0 (ch.1) serial data input pin<br>During UART0 (ch.1) input operations, this input may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on this pin, except when using it for output deliberately.                                                                                                                                                                                                   |

\* : FPT-120P-M03, FPT-120C-C02

| Pin no. Pin name |          | Circuit | Function                                                                                                                                                                                                                                                                                              |

|------------------|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*             | Pin name | type    | Function                                                                                                                                                                                                                                                                                              |

| 69               | PB5      | С       | General-purpose I/O port<br>This function is valid when the UART0 (ch.1) clock output specification<br>is "disabled".                                                                                                                                                                                 |

|                  | SCK1     |         | UART0 (ch.1) clock output pin<br>The clock output function is valid when the UART0 (ch.1) clock output<br>specification is "enabled".<br>UART0 (ch.1) external clock input pin<br>This function is valid when the port is in input mode and the UART0<br>(ch.1) specification is external clock mode. |

| 70               | PB6      | С       | General-purpose I/O port<br>This function is valid when the UART0 (ch.2) serial data output<br>specification is "disabled".                                                                                                                                                                           |

|                  | SOD2     | _       | UART0 (ch.2) serial data output pin<br>This function is valid when the UART0 (ch.2) serial data output<br>specification is "enabled".                                                                                                                                                                 |

| 71               | PB7      | С       | General-purpose I/O port<br>This function is always valid.                                                                                                                                                                                                                                            |

|                  | SID2     | _       | UART0 (ch.2) serial data input pin<br>During UART0 (ch.2) input operations, this input may be used<br>suddenly at any time; therefore, it is necessary to stop output by other<br>functions on this pin, except when using it for output deliberately.                                                |

| 72               | PC0      | С       | General-purpose I/O port<br>This function is valid when the UART0 (ch.2) clock output<br>specification is "disabled".                                                                                                                                                                                 |

|                  | SCK2     | _       | UART0 (ch.2) clock output pin<br>The clock output function is valid when the UART0 (ch.2) clock output<br>specification is "enabled".<br>UART0 (ch.2) external clock input pin<br>This function is valid when the port is in input mode and the UART0<br>(ch.2) specification is external clock mode. |

| 73               | PC1      | С       | General-purpose I/O port<br>This function is valid when the UART1 serial data output specification<br>is "disabled".                                                                                                                                                                                  |

|                  | SOD3     |         | UART1 serial data output pin<br>This function is valid when the UART1 serial data output specification<br>is "enabled".                                                                                                                                                                               |

| 74               | PC2      | С       | General-purpose I/O port<br>This function is always valid.                                                                                                                                                                                                                                            |

|                  | SID3     |         | UART1 serial data input pin<br>During UART1 input operations, this input may be used suddenly at<br>any time; therefore, it is necessary to stop output by other functions<br>on this pin, except when using it for output deliberately.                                                              |

\* : FPT-120P-M03, FPT-120C-C02

(Continued)

| Pin no.                  | Pin name  | Circuit         | Function                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|--------------------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| QFP*                     | i in name | type            | i diodon                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 75                       | PC3       | С               | General-purpose I/O port<br>This function is valid when the UART1 clock output specification is<br>"disabled".                                                                                                                                                                                                                                                                                                |  |

|                          | SCK3      |                 | UART1 clock output pin<br>The clock output function is valid when the UART1 clock output<br>specification is "enabled".<br>UART1 external clock input pin<br>This function is valid when the port is in input mode and the UART1<br>specification is external clock mode.                                                                                                                                     |  |

| 76                       | PC4       | С               | General-purpose I/O port<br>This function is always valid.                                                                                                                                                                                                                                                                                                                                                    |  |

|                          | CTS0      |                 | UART0 (ch.0) Clear To Send input pin<br>When the UART0 (ch.0) CTS function is enabled, this input may be<br>used suddenly at any time; therefore, it is necessary to stop output by<br>other functions on this pin, except when using it for output<br>deliberately.                                                                                                                                          |  |

| 77                       | PC5       | С               | General-purpose I/O port<br>This function is always valid.                                                                                                                                                                                                                                                                                                                                                    |  |

|                          | TRG0      |                 | 16-bit PPG timer trigger input pin<br>This function is valid when the 16-bit PPG timer trigger input<br>specification is enabled.<br>The data on this pin is read as 16-bit PPG timer trigger input (TRG0)<br>During this operation, the input may be used suddenly at any time;<br>therefore, it is necessary to stop output by other functions on this pin<br>except when using it for output deliberately. |  |

| 8,<br>54,<br>94          | Vcc       | Power<br>supply | Power supply for digital circuitry                                                                                                                                                                                                                                                                                                                                                                            |  |

| 33,<br>63,<br>91,<br>119 | Vss       | Power<br>supply | Ground level for digital circuitry                                                                                                                                                                                                                                                                                                                                                                            |  |

| 42                       | AVcc      | Power<br>supply |                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 43                       | AVRH      | Power<br>supply | Reference voltage input for analog circuitry                                                                                                                                                                                                                                                                                                                                                                  |  |

| 44                       | AVRL      | Power supply    | Reference voltage input for analog circuitry                                                                                                                                                                                                                                                                                                                                                                  |  |

| 45                       | AVss      | Power supply    | Ground level for analog circuitry                                                                                                                                                                                                                                                                                                                                                                             |  |

\* : FPT-120P-M03, FPT-120C-C02

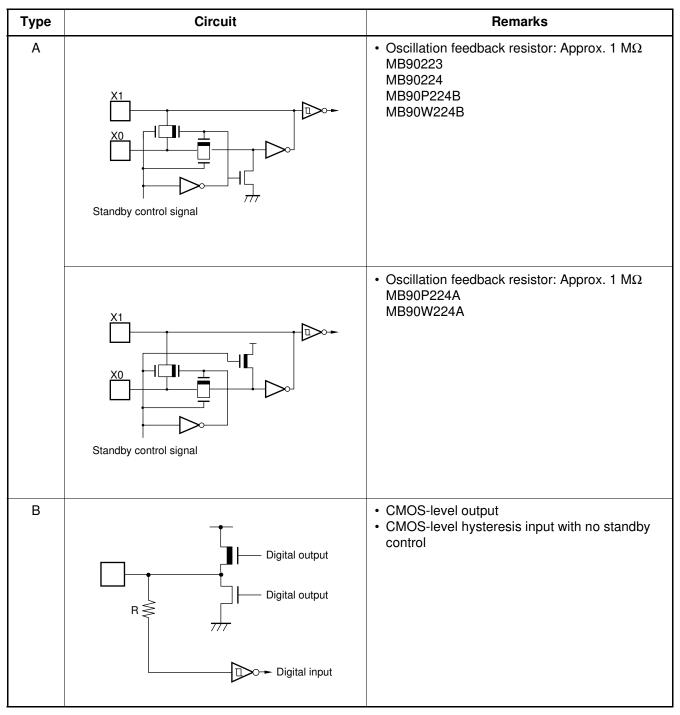

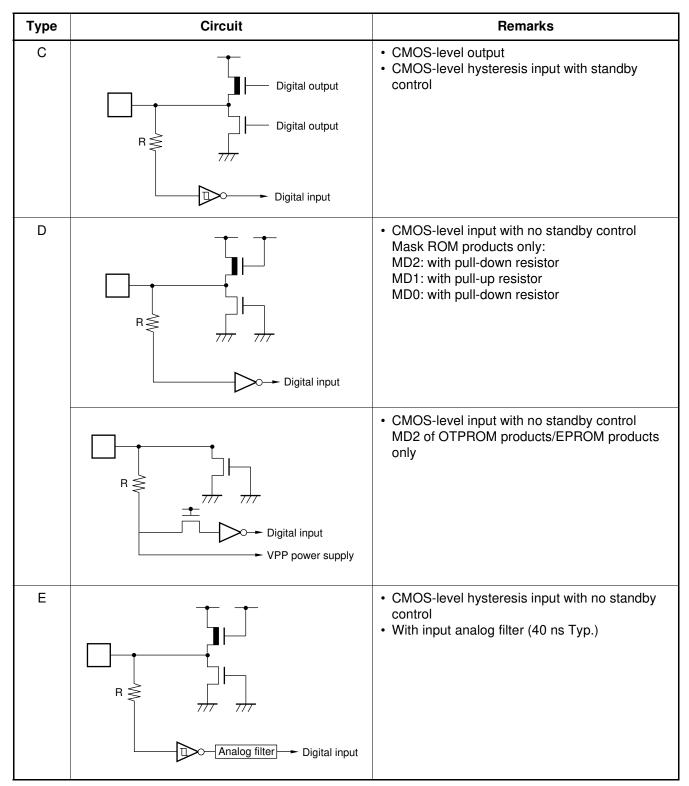

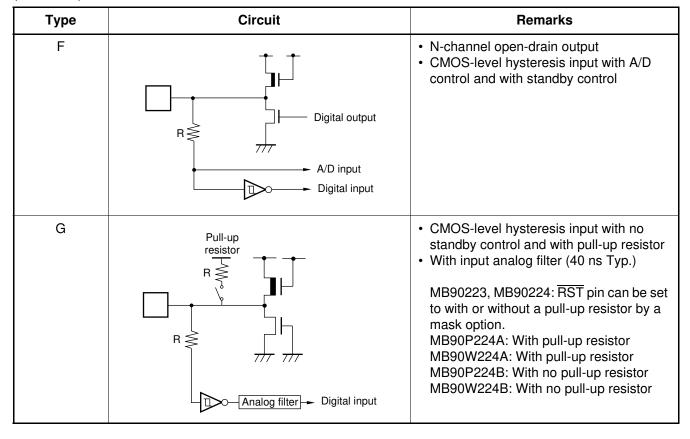

### ■ I/O CIRCUIT TYPE

Note: The pull-up and pull-down resistors are always connected, regardless of the state.

Note: The pull-up and pull-down resistors are always connected, regardless of the state.

| 10    | tinued)  |

|-------|----------|

| 1000  | iiniieai |

| 10011 | unaca,   |

□ - P-type transistor

] - : N-type transistor

Note: The pull-up and pull-down resistors are always connected, regardless of the state.

### ■ HANDLING DEVICES

#### 1. Preventing Latchup

CMOS ICs may cause latchup when a voltage higher than  $V_{CC}$  or lower than  $V_{SS}$  is applied to input or output pins other than medium-and high-voltage pins, or when a voltage exceeding the rating is applied between  $V_{CC}$  and  $V_{SS}$ .

If latch-up occurs, the power supply current increases rapidly, sometimes resulting in thermal breakdown of the device. Use meticulous care not to let any voltage exceed the maximum rating.

Also, take care to prevent the analog power supply (AV<sub>CC</sub> and AVRH) and analog input from exceeding the digital power supply (V<sub>CC</sub>) when the analog system power supply is turned on and off.

#### 2. Treatment of Unused Input Pins

Leaving unused input pins open could cause malfunctions. They should be connected to a pull-up or pull-down resistor.

#### 3. Treatment of Pins when A/D is not Used

Connect to be AVcc = AVRH = Vcc and AVss = AVRL = Vss even if the A/D converter is not in use.

#### 4. Precautions when Using an External Input

To reset the internal circuit properly by the "L" level input to the  $\overline{RST}$  pin, the "L" level input to the  $\overline{RST}$  pin must be maintained for at least five machine cycles. Pay attention to it if the chip uses external clock input.

#### 5. Vcc and Vss Pins

Apply equal potential to the Vcc and Vss pins.

#### 6. Supply Voltage Variation

The operation assurance range for the V<sub>cc</sub> supply voltage is as given in the ratings. However, sudden changes in the supply voltage can cause misoperation, even if the voltage remains within the rated range. Therefore, it is important to supply a stable voltage to the IC. The recommended power supply control guidelines are that the commercial frequency (50 to 60 Hz) ripple variation (P-P value) on V<sub>cc</sub> should be less than 10% of the standard V<sub>cc</sub> value and that the transient rate of change during sudden changes, such as during power supply switching, should be less than 0.1 V/ms.

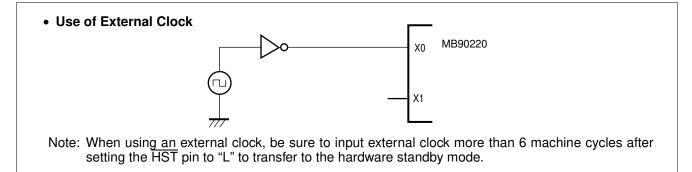

#### 7. Notes on Using an External Clock

When using an external clock, drive the X0 pin as illustrated below. When an external clock is used, oscillation stabilization time is required even for power-on reset and wake-up from stop mode.

#### 8. Power-on Sequence for A/D Converter Power Supplies and Analog Inputs

Be sure to turn on the digital power supply (Vcc) before applying voltage to the A/D converter power supplies (AVcc, AVRH, and AVRL) and analog inputs (AN00 to AN15).

When turning power supplies off, turn off the A/D converter power supplies (AVcc, AVRH, and AVRL) and analog inputs (AN00 to AN15) first, then the digital power supply (Vcc).

When turning AVRH on or off, be careful not to let it exceed AVcc.

### ■ PROGRAMMING FOR MB90P224A/P224B/W224A/W224B

In EPROM mode, the MB90P224A/P224B/W224A/W224B functions equivalent to the MBM27C1000. This allows the EPROM to be programmed with a general-purpose EPROM programmer by using the dedicated socket adapter (do not use the electronic signature mode).

#### 1. Program Mode

When shipped from Fujitsu, and after each erasure, all bits (96 K  $\times$  8 bits) in the MB90P224A/P224B/W224A/W224B are in the "1" state. Data is written to the ROM by selectively programming "0's" into the desired bit locations. Bits cannot be set to "1" electrically.

#### 2. Programming Procedure

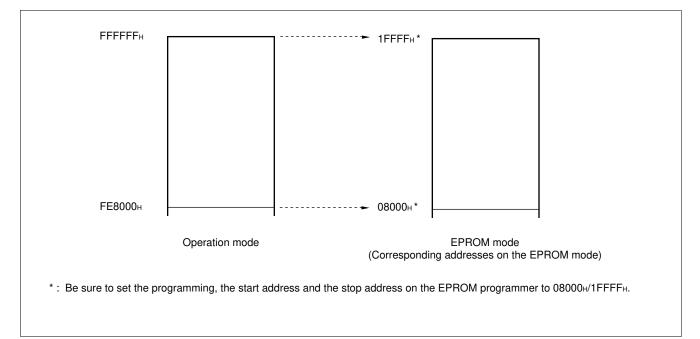

- (1) Set the EPROM programmer to MBM27C1000.

- (2) Load program data into the EPROM programmer at 08000H to 1FFFFH.

Note that ROM addresses FE8000<sub>H</sub> to FFFFF<sub>H</sub> in the operation mode in the MB90P224A/P224B/W224A/ W224B series assign to 08000<sub>H</sub> to 1FFFF<sub>H</sub> in the EPROM mode (on the EPROM programmer).

- (3) Mount the MB90P224A/P224B/W224A/W224B on the adapter socket, then fit the adapter socket onto the EPROM programmer. When mounting the device and the adapter socket, pay attention to their mounting orientations.

- (4) Start programming the program data to the device.

- (5) If programming has not successfully resulted, connect a capacitor of approx. 0.1 μF between V<sub>CC</sub> and GND, between V<sub>PP</sub> and GND.

- Note: The mask ROM products (MB90223, MB90224) does not support EPROM mode. Data cannot, therefore, be read by the EPROM programmer.

#### 3. EPROM Programmer Socket Adapter and Recommended Programmer Manufacturer

| Part No.                                                               |                 |                                                    | MB90P224B          |

|------------------------------------------------------------------------|-----------------|----------------------------------------------------|--------------------|

| Package                                                                |                 |                                                    | QFP-120            |

| Compatible sock<br>Sun Hayato Co.,                                     | -               |                                                    | ROM-120QF-32DP-16F |

| Recommended<br>programmer<br>manufacturer<br>and<br>programmer<br>name | Advantest corp. | R4945A<br>(main unit)<br>+<br>R49451A<br>(adapter) | Recommended        |

Inquiry: Sun Hayato Co., Ltd.: TEL: (81)-3-3986-0403 FAX: (81)-3-5396-9106 Advantest Corp.: TEL: Except JAPAN (81)-3-3930-4111

#### 4. Erase Procedure

Data written in the MB90W224A/W224B is erased (from "0" to "1") by exposing the chip to ultraviolet rays with a wavelength of 2,537 Å through the translucent cover.

Recommended irradiation dosage for exposure is 10 Wsec/cm<sup>2</sup>. This amount is reached in 15 to 20 minutes with a commercial ultraviolet lamp positioned 2 to 3 cm above the package (when the package surface illuminance is 1200  $\mu$ W/cm<sup>2</sup>).

If the ultraviolet lamp has a filter, remove the filter before exposure. Attaching a mirrored plate to the lamp increases the illuminance by a factor of 1.4 to 1.8, thus shortening the required erasure time. If the translucent part of the package is stained with oil or adhesive, transmission of ultraviolet rays is degraded, resulting in a longer erasure time. In that case, clean the translucent part using alcohol (or other solvent not affecting the package).

The above recommended dosage is a value which takes the guard band into consideration and is a multiple of the time in which all bits can be evaluated to have been erased. Observe the recommended dosage for erasure; the purpose of the guard band is to ensure erasure in all temperature and supply voltage ranges. In addition, check the life span of the lamp and control the illuminance appropriately.

Data in the MB90W224A/W224B is erased by exposure to light with a wavelength of 4,000 Å or less.

Data in the device is also erased even by exposure to fluorescent lamp light or sunlight although the exposure results in a much lower erasure rate than exposure to 2,537 Å ultraviolet rays. Note that exposure to such lights for an extended period will therefore affect system reliability. If the chip is used where it is exposed to any light with a wavelength of 4,000 Å or less, cover the translucent part, for example, with a protective seal to prevent the chip from being exposed to the light.

Exposure to light with a wavelength of 4,000 to 5,000 Å or more will not erase data in the device. If the light applied to the chip has a very high illuminance, however, the device may cause malfunction in the circuit for reasons of general semiconductor characteristics. Although the circuit will recover normal operation when exposure is stopped, the device requires proper countermeasures for use in a place exposed continuously to such light even though the wavelength is 4,000 Å or more.

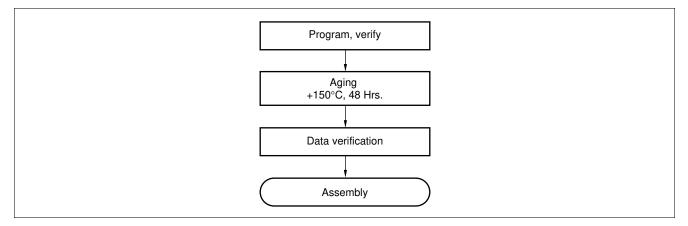

#### 5. Recommended Screening Conditions

High temperature aging is recommended as the pre-assembly screening procedure.

#### 6. Programming Yeild

MB90P224A/P224B cannot be write-tested for all bits due to their nature. Therefore the write yield cannot always be guaranteed to be 100%.

#### 7. Pin Assignments in EPROM Mode

#### (1) Pins Compatible with MBM27C1000

| MBM27C1000 |          | MB90P224A/P224B/<br>MB90W224A/W224B |           | MBM2    | 27C1000  | MB90P224A/P224B/<br>MB90W224A/W224B |          |

|------------|----------|-------------------------------------|-----------|---------|----------|-------------------------------------|----------|

| Pin no.    | Pin name | Pin no.                             | Pin name  | Pin no. | Pin name | Pin no.                             | Pin name |

| 1          | Vpp      | 87                                  | MD2 (VPP) | 32      | Vcc      | 8, 54, 94                           | Vcc      |

| 2          | OE       | 83                                  | P55       | 31      | PGM      | 84                                  | P56      |

| 3          | A15      | 7                                   | P37       | 30      | N.C.     |                                     | _        |

| 4          | A12      | 4                                   | P34       | 29      | A14      | 6                                   | P36      |

| 5          | A07      | 118                                 | P27       | 28      | A13      | 5                                   | P35      |

| 6          | A06      | 117                                 | P26       | 27      | A08      | 120                                 | P30      |

| 7          | A05      | 116                                 | P25       | 26      | A09      | 1                                   | P31      |

| 8          | A04      | 115                                 | P24       | 25      | A11      | 3                                   | P33      |

| 9          | A03      | 114                                 | P23       | 24      | A16      | 9                                   | P40      |

| 10         | A02      | 113                                 | P22       | 23      | A10      | 2                                   | P32      |

| 11         | A01      | 112                                 | P21       | 22      | CE       | 82                                  | P54      |

| 12         | A00      | 111                                 | P20       | 21      | D07      | 102                                 | P07      |

| 13         | D00      | 95                                  | P00       | 20      | D06      | 101                                 | P06      |

| 14         | D01      | 96                                  | P01       | 19      | D05      | 100                                 | P05      |

| 15         | D02      | 97                                  | P02       | 18      | D04      | 99                                  | P04      |

| 16         | GND      | 33, 63, 91,119                      | Vss       | 17      | D03      | 98                                  | P03      |

| Туре         | Pin no.                                       | Pin name                                             |

|--------------|-----------------------------------------------|------------------------------------------------------|

| Power supply | 89<br>88<br>86<br>8, 54, 94                   | MD0<br>MD1<br>HST<br>Vcc                             |

| GND          | 33, 63, 91, 119<br>44<br>45<br>80<br>81<br>90 | V <sub>SS</sub><br>AVRL<br>AVss<br>P52<br>P53<br>RST |

#### (2) Power Supply and GND Connection Pins

#### (3) Pins other than MBM27C1000-compatible Pins

| Pin no.                                                                                                                                                            | Pin name                                                                                                                                                                                    | Treatment                                                 |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

| 92                                                                                                                                                                 | X0                                                                                                                                                                                          | Pull up with 4.7 K $\Omega$ resistor                      |  |  |  |

| 93                                                                                                                                                                 | X1                                                                                                                                                                                          | OPEN                                                      |  |  |  |

| 109<br>110<br>10 to 16<br>42<br>43<br>46<br>47<br>48 to 53<br>17 to 24<br>25 to 32<br>34 to 41<br>55 to 61<br>63 to 70<br>71 to 76<br>78<br>79<br>85<br>103 to 108 | P16<br>P17<br>P41 to P47<br>AVcc<br>AVRH<br>P60<br>P61<br>P62 to P67<br>P70 to P77<br>P80 to P82<br>P90 to P97<br>PA0 to P47<br>PB0 to P87<br>PC0 to PC5<br>P50<br>P51<br>P57<br>P10 to P15 | Connect pull-up resistor of about 1 $M\Omega$ to each pin |  |  |  |

■ BLOCK DIAGRAM

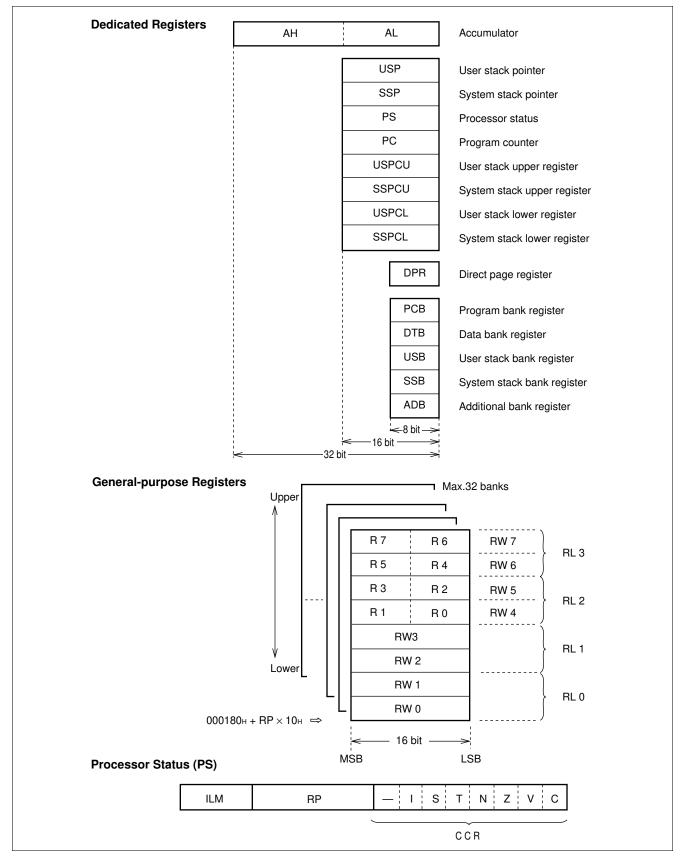

#### PROGRAMMING MODEL

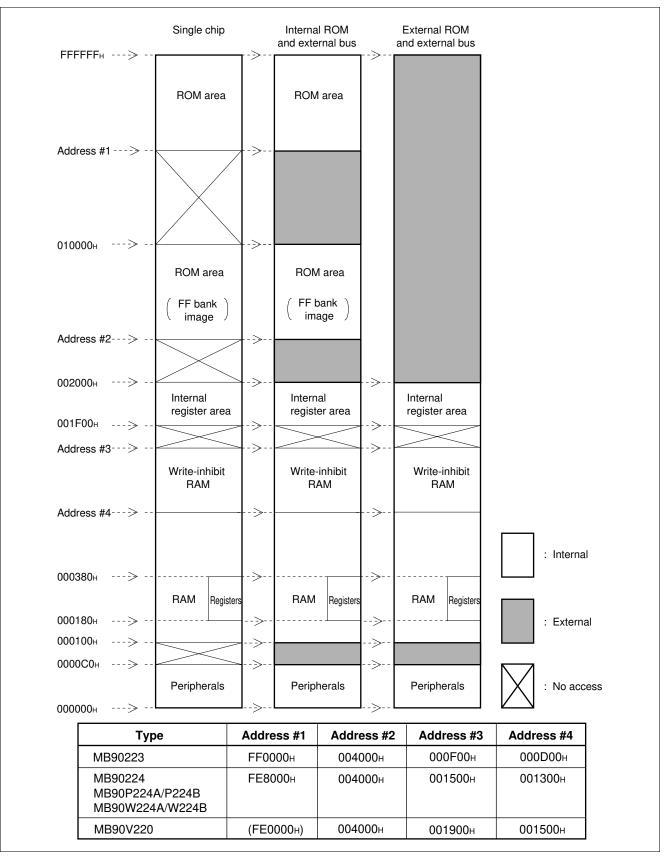

#### ■ MEMORY MAP

### ■ I/O MAP

| Address               | Register                                         | Register name   | Access | Resouce<br>name | Initial value |  |  |

|-----------------------|--------------------------------------------------|-----------------|--------|-----------------|---------------|--|--|

| 000000H*3             | Port 0 data register                             | PDR0            | R/W    | Port 0          | XXXXXXXX      |  |  |

| 000001н <sup>*3</sup> | Port 1 data register                             | PDR1            | R/W    | Port 1          | XXXXXXXX      |  |  |

| 000002H*3             | Port 2 data register                             | PDR2            | R/W    | Port 2          | XXXXXXXX      |  |  |

| 000003н <sup>*3</sup> | Port 3 data register                             | PDR3            | R/W    | Port 3          | XXXXXXXX      |  |  |

| 000004н <sup>*3</sup> | Port 4 data register                             | PDR4            | R/W    | Port 4          | XXXXXXXX      |  |  |

| 000005н <sup>*3</sup> | Port 5 data register                             | PDR5            | R/W    | Port 5          | XXXXXXXX      |  |  |

| 00006н                | Port 6 data register                             | PDR6            | R/W    | Port 6          | 11111111      |  |  |

| 00007н                | Port 7 data register                             | PDR7            | R      | Port 7          | XXXXXXXX      |  |  |

| 00008н                | Port 8 data register                             | PDR8            | R/W    | Port 8          | XXXXXXXX      |  |  |

| 00009н                | Port 9 data register                             | PDR9            | R/W    | Port 9          | 11111111      |  |  |

| 00000Ан               | Port A data register                             | PDRA            | R/W    | Port A          | XXXXXXXX      |  |  |

| 00000Вн               | Port B data register                             | PDRB            | R/W    | Port B          | XXXXXXXX      |  |  |

| 00000Сн               | Port C data register                             | PDRC            | R/W    | Port C          | XXXXXX        |  |  |

| 00000Dн<br>to 0Fн     | (Reserved area)*1                                |                 |        |                 |               |  |  |

| 000010H*3             | Port 0 data direction register                   | DDR0            | R/W    | Port 0          | 00000000      |  |  |

| 000011н <sup>*3</sup> | Port 1 data direction register                   | DDR1            | R/W    | Port 1          | 00000000      |  |  |

| 000012H*3             | Port 2 data direction register                   | DDR2            | R/W    | Port 2          | 00000000      |  |  |

| 000013н <sup>*3</sup> | Port 3 data direction register                   | DDR3            | R/W    | Port 3          | 00000000      |  |  |

| 000014H <sup>*3</sup> | Port 4 data direction register                   | DDR4            | R/W    | Port 4          | 00000000      |  |  |

| 000015н <sup>*3</sup> | Port 5 data direction register                   | DDR5            | R/W    | Port 5          | 00000000      |  |  |

| 000016н               | Port 6 analog input enable register              | ADER0           | R/W    | Port 6          | 11111111      |  |  |

| 000017н               | Port 7 data direction register                   | DDR7            | R/W    | Port 7          | 11111111      |  |  |

| 000018H               | Port 8 data direction register                   | DDR8            | R/W    | Port 8          | 00000000      |  |  |

| 000019н               | Port 9 analog input enable register              | ADER1           | R/W    | Port 9          | 11111111      |  |  |

| 00001Aн               | Port A data direction register                   | DDRA            | R/W    | Port A          | 00000000      |  |  |

| 00001Bн               | Port B data direction register                   | DDRB            | R/W    | Port B          | 00000000      |  |  |

| 00001CH               | Port C data direction register                   | DDRC            | R/W    | Port C          | 000000        |  |  |

| 00001Dн<br>to 1Fн     | (Reserved area) <sup>*1</sup>                    |                 |        |                 |               |  |  |

| 000020н               | Mode control register 0                          | UMC0            | R/W    |                 | 00000100      |  |  |

| 000021н               | Status register 0                                | USR0            | R/W    | UART 0 (ch.0)   | 00010000      |  |  |

| 000022н               | Input data register 0<br>/output data register 0 | UIDR0<br>/UODR0 | R/W    |                 | xxxxxxx       |  |  |