Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# F<sup>2</sup>MC-16LX16-bit Microcontrollers

The MB90350E series, loaded 1 channel FULL-CAN\* interface and Flash ROM, is general-purpose Cypress 16-bit microcontroller designing for automotive and industrial applications. Its main feature is the on-board CAN interface, which conforms to CAN standard Version2.0 Part A and Part B, while supporting a very flexible message buffer scheme and so offering more functions than a normal full CAN approach.

The power supply (3 V) is supplied to the MCU core from an internal regulator circuit. This creates a major advantage in terms of EMI and power consumption.

The PLL clock multiplication circuit provides an internal 42 ns instruction execution time from an external 4 MHz clock. Also, the clock supervisor function can monitor main clock and sub clock independently.

As the peripheral resources, the unit features a 4-channel Output Compare Unit, 6-channel Input Capture Unit, 2 separate 16-bit free-run timers, 2-channel LIN-UART and 15-channel 8/10-bit A/D converter built-in.

: Controller Area Network (CAN) - License of Robert Bosch GmbH

### **Features**

### Clock

- Built-in PLL clock frequency multiplication circuit

- Selection of machine clocks (PLL clocks) is allowed among frequency division by two on oscillation clock, and multiplication of 1 to 6 times of oscillation clock (for 4 MHz oscillation clock, 4 MHz to 24 MHz).

- Operation by sub clock (up to 50 kHz: 100 kHz oscillation clock divided by two) is allowed (devices without S-suffix only).

- Minimum execution time of instruction: 42 ns (when operating with 4-MHz oscillation clock, and 6-time multiplied PLL clock).

- Built-in clock modulation circuit

### 16 Mbytes CPU memory space

24-bit internal addressing

### Instruction system best suited to controller

- Wide choice of data types (bit, byte, word, and long word)

- Wide choice of addressing modes (23 types)

- Enhanced multiply-divide instructions with sign and RETI instructions

# Clock supervisor (MB90x356x and MB90x357x only)

Main clock or sub clock is monitored independently.

# Enhanced high-precision computing with 32-bit accumulator

# Instruction system compatible with high-level language (C language) and multitask

- Employing system stack pointer

- Enhanced various pointer indirect instructions

- Barrel shift instructions

### Increased processing speed

4-byte instruction queue

## **Powerful interrupt function**

- Powerful 8-level, 34-condition interrupt feature

- Up to 8 channels external interrupts are supported.

# Automatic data transfer function independent of CPU

- Extended intelligent I/O service function (EI<sup>2</sup>OS): up to 16 channels

- DMA: up to 16 channels

### Low power consumption (standby) mode

- Sleep mode (a mode that stops CPU operating clock)

- Main timer mode (a timebase timer mode switched from the main clock mode)

- PLL timer mode (a timebase timer mode switched from the PLL clock mode)

- Watch mode (a mode that operates sub clock and watch timer only)

- Stop mode (a mode that stops oscillation clock and sub clock)

- CPU intermittent operation mode

### **Process**

CMOS technology

### I/O port

■ General-purpose input/output port (CMOS output)

49 ports (devices without S-suffix : devices that correspond to sub clock)

51 ports (devices with S-suffix : devices that do not correspond to sub clock)

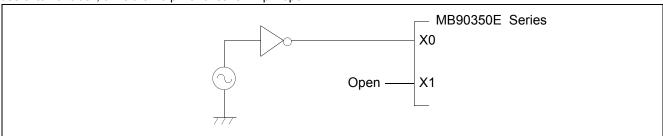

### Sub clock pin (X0A, X1A)

- Yes (using the external oscillation) : devices without S-suffix

- No (using the sub clock mode at internal CR oscillation) : devices with S-suffix

### Timer

■ Timebase timer, watch timer, watchdog timer: 1 channel

Cypress Semiconductor Corporation Document Number: 002-04493 Rev. \*A

198 Champion Court

San Jose, CA 95134-1709

408-943-2600

Revised April 7, 2016

- 8/16-bit PPG timer: 8-bit ∞ 10 channels or 16-bit × 6 channels

- 16-bit reload timer : 2 channels (only Evaluation products has 4 channels)

- 16- bit input/output timer

- 16-bit free-run timer : 2 channels (FRT0 : ICU0/1, FRT1 : ICU4/5/6/7, OCU4/5/6/7)

- 16- bit input capture: (ICU): 6 channels - 16-bit output compare: (OCU): 4 channels

### FULL-CAN interface: 1 channel

- Compliant with CAN standard Version2.0 Part A and Part B

- 16 message buffers are built-in

- CAN wake-up function

### LIN-UART: 2 channels

- Equipped with full-duplex double buffer

- Clock-asynchronous or clock-synchronous serial transmission is available.

### I<sup>2</sup>C interface: 1 channel

Up to 400 kbps transfer rate

# DTP/External interrupt: 8 channels, CAN wakeup: 1 channel

Module for activation of extended intelligent I/O service (El<sup>2</sup>OS), DMA, and generation of external interrupt by external input.

### Delay interrupt generator module

Generates interrupt request for task switching.

### 8/10-bit A/D converter: 15 channels

- Resolution is selectable between 8-bit and 10-bit.

- Activation by external trigger input is allowed.

- Conversion time : 3 µs (at 24 MHz machine clock, including sampling time)

# Address matching detection (Program patch) function

■ Address matching detection for 6 address pointers.

### Capable of changing input voltage level for port

- Automotive/CMOS-Schmitt (initial level is Automotive in single chip mode)

- TTL level (corresponds to external bus pins only, initial level of these pins is TTL in external bus mode)

# Low voltage/CPU operation detection reset (devices with T-suffix)

- $\blacksquare$  Detects low voltage (4.0 V  $\pm$  0.3 V) and resets automatically

- Resets automatically when program is runaway and counter is not cleared within interval time (approx. 262 ms : external 4 MHz)

# Dual operation Flash memory (only devices 128 Kbytes Flash memory)

■ Erase/write and read can be executed in the different bank (Upper Bank/Lower Bank) at the same time.

### Supported $T_{\Delta} = + 125^{\circ}C$

The maximum operating frequency is 24 MHz\*: (at  $T_A = +125$ °C).

### Flash security function

■ Protects the content of Flash memory (MB90F352x, MB90F357x only)

### **External bus interface**

- 4 Mbytes external memory space MB90F351E(S), MB90F351TE(S), MB90F352E(S), MB90F352TE(S): External bus Interface can not be used in internal vector mode. It can be used only in external vector mode.

- \*: If used exceeding  $T_A = +105$  °C, be sure to contact Cypress for reliability limitations.

# MB90350E Series

### Contents

| Product Lineup1 (Without Clock supervisor fund         | tion) 4 |

|--------------------------------------------------------|---------|

| <b>Product Lineup 2 (With Clock supervisor functio</b> | n)7     |

| Packages and Product Correspondence                    | 12      |

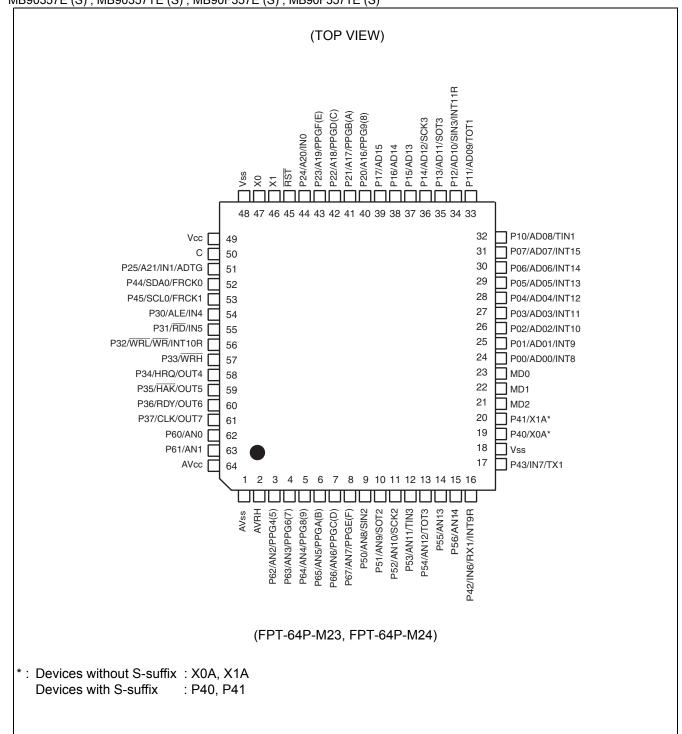

| Pin Assignments                                        | 13      |

| Pin Description                                        | 14      |

| I/O Circuit Type                                       |         |

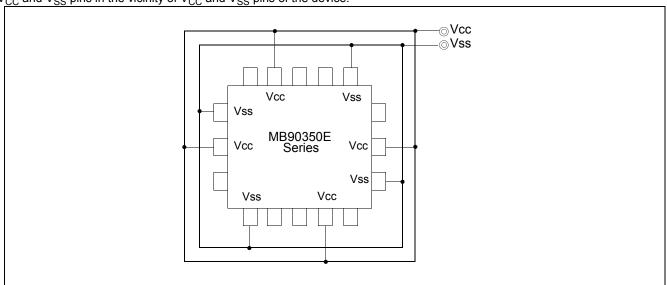

| Handling Devices                                       | 22      |

| Block Diagrams                                         | 27      |

| Memory Map                                             | 33      |

| I/O Map                                                | 34      |

| CAN Controllers                                        | 42      |

| Interrupt Factors, Interrupt Vectors, Interrupt        |         |

| Control Register                                       | 50      |

| Electrical Characteristics                             | 51      |

| Absolute Maximum Ratings                               | 51      |

| Recommended Operating Conditions                       | 53      |

| DC Characteristics                                     | 54      |

| AC Characteristics                                     | 59      |

| Clock Timing                                           | 59      |

| Reset Standby Input                        | 62 |

|--------------------------------------------|----|

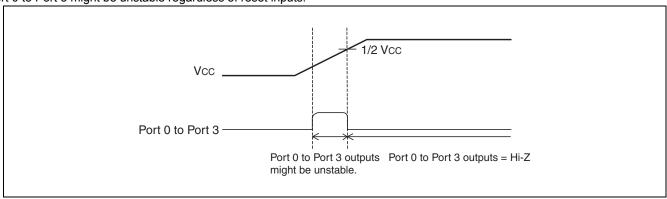

| Power On Reset                             | 63 |

| Clock Output Timing                        | 63 |

| Bus Timing (Read)                          |    |

| Bus Timing (Write)                         | 66 |

| Ready Input Timing                         | 67 |

| Hold Timing                                | 68 |

| LIN-UART2/3                                | 69 |

| Trigger Input Timing                       | 73 |

| Timer Related Resource Input Timing        | 74 |

| Timer Related Resource Output Timing       | 74 |

| I2C Timing                                 | 75 |

| A/D Converter                              | 76 |

| Definition of A/D Converter Terms          | 80 |

| Flash Memory Program/Erase Characteristics | 82 |

| Ordering Information                       | 83 |

| Package Dimensions                         | 85 |

| Major Changes                              | 87 |

|                                            |    |

# 1. Product Lineup1 (Without Clock supervisor function)

■ Flash memory products

| Part Number                                  | MP00E254E                                                                                                                                                                                                                                                                                                                          | MD00E2E4TE                                                                                                                              | MB00E251E6                            | MD00E2E4TEC                |  |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------|--|--|--|--|

|                                              | MB90F351E<br>MB90F352E                                                                                                                                                                                                                                                                                                             | MB90F351TE<br>MB90F352TE                                                                                                                | MB90F351ES<br>MB90F352ES              | MB90F351TES<br>MB90F352TES |  |  |  |  |

| Parameter                                    |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                         |                                       |                            |  |  |  |  |

| Туре                                         |                                                                                                                                                                                                                                                                                                                                    | Flash memo                                                                                                                              | ory products                          |                            |  |  |  |  |

| CPU                                          |                                                                                                                                                                                                                                                                                                                                    | F <sup>2</sup> MC-16LX CPU                                                                                                              |                                       |                            |  |  |  |  |

| System clock                                 | •                                                                                                                                                                                                                                                                                                                                  | cuit ( $\times$ 1, $\times$ 2, $\times$ 3, $\times$ 4, $\times$ 6, 1/2 ion time : 42 ns (oscillation of                                 | • •                                   |                            |  |  |  |  |

| ROM                                          |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                         | 1TE(S)<br>and read can be operated at | the same time) :           |  |  |  |  |

| RAM                                          |                                                                                                                                                                                                                                                                                                                                    | 4 Kb                                                                                                                                    | oytes                                 |                            |  |  |  |  |

| Emulator-specific power supply*              |                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                       | _                                     |                            |  |  |  |  |

| Sub clock pin<br>(X0A, X1A)<br>(Max 100 kHz) | Ye                                                                                                                                                                                                                                                                                                                                 | es                                                                                                                                      | N                                     | 0                          |  |  |  |  |

| Clock supervisor                             |                                                                                                                                                                                                                                                                                                                                    | N                                                                                                                                       | lo                                    |                            |  |  |  |  |

| Low voltage/CPU operation detection reset    | No                                                                                                                                                                                                                                                                                                                                 | Yes                                                                                                                                     | No                                    | Yes                        |  |  |  |  |

| Operating voltage                            |                                                                                                                                                                                                                                                                                                                                    | perating (not using A/D conv<br>converter/Flash programmi<br>ernal bus                                                                  |                                       |                            |  |  |  |  |

| Operating temperature                        |                                                                                                                                                                                                                                                                                                                                    | –40°C to                                                                                                                                | ) +125°C                              |                            |  |  |  |  |

| Package                                      |                                                                                                                                                                                                                                                                                                                                    | LQF                                                                                                                                     | P-64                                  |                            |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                    | 2 cha                                                                                                                                   | nnels                                 |                            |  |  |  |  |

| LIN-UART                                     | Wide range of baud rate settings using a dedicated baud rate generator (reload timer) Special synchronous options for adapting to different synchronous serial protocols LIN functionality working either as master or slave LIN device                                                                                            |                                                                                                                                         |                                       |                            |  |  |  |  |

| I <sup>2</sup> C (400 kbps)                  |                                                                                                                                                                                                                                                                                                                                    | 1 cha                                                                                                                                   | annel                                 |                            |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                    | 15 cha                                                                                                                                  | annels                                |                            |  |  |  |  |

| A/D converter                                | 10-bit or 8-bit resolution Conversion time : Min 3 μs includes sample time (per one channel)                                                                                                                                                                                                                                       |                                                                                                                                         |                                       |                            |  |  |  |  |

| 16-bit reload timer<br>(2 channels)          | Operation clock frequency:<br>Supports External Event Co                                                                                                                                                                                                                                                                           |                                                                                                                                         | ys = Machine clock frequenc           | y)                         |  |  |  |  |

|                                              | Free-run Timer 1 (clock inp                                                                                                                                                                                                                                                                                                        | Free-run Timer 0 (clock input FRCK0) corresponds to ICU0/1. Free-run Timer 1 (clock input FRCK1) corresponds to ICU4/5/6/7, OCU4/5/6/7. |                                       |                            |  |  |  |  |

| 16-bit Free-run timer<br>(2 channels)        | Signals an interrupt when overflowing. Supports Timer Clear when it matches Output Compare (ch.0, ch.4). Operation clock frequency: fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> , fsys/2 <sup>5</sup> , fsys/2 <sup>6</sup> , fsys/2 <sup>7</sup> (fsys = Machine clock frequency) |                                                                                                                                         |                                       |                            |  |  |  |  |

| 4.C. hit autout                              |                                                                                                                                                                                                                                                                                                                                    | 4 cha                                                                                                                                   | nnels                                 |                            |  |  |  |  |

| 16-bit output compare                        | Signals an interrupt when 1                                                                                                                                                                                                                                                                                                        | 6-bit free-run Timer matches                                                                                                            | s with output compare registe         | ers.                       |  |  |  |  |

| Part Number Parameter                                                                                                                                                                                                                                    | MB90F351E<br>MB90F352E                                                                                                                                                                                                                                                                                                                                                                                                              | MB90F351TE<br>MB90F352TE                                                                                                                                                                                                                                                                                                                                                                                                      | MB90F351ES<br>MB90F352ES         | MB90F351TES<br>MB90F352TES |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------|--|--|--|--|

| 16-bit Input capture                                                                                                                                                                                                                                     | 6 channels  Retains 16-bit free-run timer value by (rising edge, falling edge or rising & falling edge), signals an interrupt.                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |                            |  |  |  |  |

| 8/16-bit<br>programmable pulse gen-<br>erator                                                                                                                                                                                                            | 6 channels (16-bit)/10 char<br>8-bit reload counters × 12<br>8-bit reload registers for L p<br>8-bit reload registers for H<br>Supports 8-bit and 16-bit of<br>A pair of 8-bit reload counte<br>8-bit prescaler + 8-bit reload                                                                                                                                                                                                      | S channels (16-bit)/10 channels (8-bit)  B-bit reload counters × 12  B-bit reload registers for L pulse width × 12  B-bit reload registers for H pulse width×12  Supports 8-bit and 16-bit operation modes.  A pair of 8-bit reload counters can be configured as one 16-bit reload counter or as  B-bit prescaler + 8-bit reload counter.  Operation clock frequency: fsys, fsys/2¹, fsys/2³, fsys/2⁴ or 128 μs@fosc = 4 MHz |                                  |                            |  |  |  |  |

|                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 cha<br>ard Version2.0 Part A and Pa                                                                                                                                                                                                                                                                                                                                                                                         | annel                            |                            |  |  |  |  |

| Automatic transmission responding to Remote Frame 16 prioritized message buffers for data and ID Supports multiple messages. Flexible configuration of acceptance filtering: Full bit compare/Full bit mask/Two partial bit masks Supports up to 1 Mbps. |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |                            |  |  |  |  |

|                                                                                                                                                                                                                                                          | 8 channels                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |                            |  |  |  |  |

| External interrupt                                                                                                                                                                                                                                       | Can be used rising edge, fa extended intelligent I/O ser                                                                                                                                                                                                                                                                                                                                                                            | alling edge, starting up by "H<br>vices (El <sup>2</sup> OS) and DMA.                                                                                                                                                                                                                                                                                                                                                         | "/"L" level input, external inte | errupt,                    |  |  |  |  |

| D/A converter                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                |                            |  |  |  |  |

| I/O ports                                                                                                                                                                                                                                                | Virtually all external pins can be used as general purpose I/O port. All push-pull outputs Bit-wise settable as input/output or peripheral signal Settable as CMOS schmitt trigger/ automotive inputs TTL input level settable for external bus (only for external bus pin)                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |                            |  |  |  |  |

| Flash memory                                                                                                                                                                                                                                             | Supports automatic programming, Embedded Algorithm Write/Erase/Erase-Suspend/Resume commands A flag indicating completion of the algorithm Number of erase cycles: 10000 times Data retention time: 20 years Boot block configuration Erase can be performed on each block. Block protection with external programming voltage Flash Security Feature for protecting the content of the Flash (MB90F352E(S) and MB90F352TE(S) only) |                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |                            |  |  |  |  |

| Corresponding evaluation name                                                                                                                                                                                                                            | MB90V3                                                                                                                                                                                                                                                                                                                                                                                                                              | 40E-102                                                                                                                                                                                                                                                                                                                                                                                                                       | MB90V3                           | 40E-101                    |  |  |  |  |

<sup>\*:</sup> It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to the Emulator hardware manual about details.

■ MASK ROM products/Evaluation products

| Part Number Parameter                        | MB90351E<br>MB90352E                                                                                                                                                                                                                                                                                        | MB90351TE<br>MB90352TE                                                                                                                                                                                                                                                                                                              | MB90351ES<br>MB90352ES                        | MB90351TES<br>MB90352TES                             | MB90V340E-1<br>01 | MB90V340E-1 |  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------|-------------------|-------------|--|

| Туре                                         |                                                                                                                                                                                                                                                                                                             | MASK RO                                                                                                                                                                                                                                                                                                                             | M products                                    |                                                      | Evaluation        | n products  |  |

| CPU                                          |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                     | F <sup>2</sup> MC-1                           | 6LX CPU                                              | •                 |             |  |

| System clock                                 | ·                                                                                                                                                                                                                                                                                                           | •                                                                                                                                                                                                                                                                                                                                   | 2, ×3, ×4, ×6, 1/2 v<br>42 ns (oscillation of | when PLL stops)<br>clock 4 MHz, PLL ×                | 6)                |             |  |

| ROM                                          | ,                                                                                                                                                                                                                                                                                                           | B90351E(S), MB90<br>B90352E(S), MB90                                                                                                                                                                                                                                                                                                | ` '                                           |                                                      | Exte              | ernal       |  |

| RAM                                          |                                                                                                                                                                                                                                                                                                             | 4 Kt                                                                                                                                                                                                                                                                                                                                | oytes                                         |                                                      | 30 K              | bytes       |  |

| Emulator-specific power supply*              |                                                                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                   | _                                             |                                                      | Y                 | es          |  |

| Sub clock pin<br>(X0A, X1A)<br>(Max 100 kHz) | Ye                                                                                                                                                                                                                                                                                                          | es                                                                                                                                                                                                                                                                                                                                  | N                                             | lo                                                   | No                | Yes         |  |

| Clock supervisor                             |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                     | N                                             | lo                                                   | •                 | 1           |  |

| Low voltage/CPU operation detection reset    | No                                                                                                                                                                                                                                                                                                          | Yes                                                                                                                                                                                                                                                                                                                                 | No                                            | Yes                                                  | N                 | lo          |  |

| Operating<br>voltage range                   | 4.0 V to 5.5 V : at                                                                                                                                                                                                                                                                                         | 3.5 V to 5.5 V : at normal operating (not using A/D converter) 4.0 V to 5.5 V : at using A/D converter 4.5 V to 5.5 V : at using external bus                                                                                                                                                                                       |                                               |                                                      |                   | - 10%       |  |

| Operating temperature range                  |                                                                                                                                                                                                                                                                                                             | −40°C to                                                                                                                                                                                                                                                                                                                            | ) +125°C                                      |                                                      | _                 |             |  |

| Package                                      |                                                                                                                                                                                                                                                                                                             | LQF                                                                                                                                                                                                                                                                                                                                 | P-64                                          |                                                      | PGA-299           |             |  |

|                                              |                                                                                                                                                                                                                                                                                                             | 2 cha                                                                                                                                                                                                                                                                                                                               | innels                                        |                                                      | 5 cha             | nnels       |  |

| LIN-UART                                     | Special synchrono                                                                                                                                                                                                                                                                                           | ous options for ada                                                                                                                                                                                                                                                                                                                 |                                               | d rate generator (re<br>nchronous serial p<br>device |                   |             |  |

| I <sup>2</sup> C (400 kbps)                  |                                                                                                                                                                                                                                                                                                             | 1 cha                                                                                                                                                                                                                                                                                                                               | annel                                         |                                                      | 2 cha             | nnels       |  |

|                                              |                                                                                                                                                                                                                                                                                                             | 15 ch                                                                                                                                                                                                                                                                                                                               | annels                                        |                                                      | 24 ch             | annels      |  |

| A/D converter                                |                                                                                                                                                                                                                                                                                                             | 10-bit or 8-bit resolution Conversion time : Min 3 μs includes sample time (per one channel)                                                                                                                                                                                                                                        |                                               |                                                      |                   |             |  |

|                                              |                                                                                                                                                                                                                                                                                                             | 2 cha                                                                                                                                                                                                                                                                                                                               | innels                                        |                                                      | 4 cha             | nnels       |  |

| 16-bit reload timer                          | Operation clock frequency: fsys/2 <sup>1</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>5</sup> (fsys = Machine clock frequency) Supports External Event Count function.                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                     |                                               |                                                      |                   |             |  |

| 16-bit free-run timer<br>(2 channels)        | Free-run Timer 0 (clock input FRCK0) corresponds to ICU0/1.  Free-run Timer 1 (clock input FRCK1) corresponds to ICU4/5/6/7, OCU4/5/6/7.  Free-run Timer 1 (clock input FRCK1) corresponds to ICU4/5/6/7.  Free-run Timer 0 corresponds to ICU OCU4/1/2/3.  Free-run Timer 1 corresponds to ICU OCU4/5/6/7. |                                                                                                                                                                                                                                                                                                                                     |                                               |                                                      |                   |             |  |

|                                              | Supports Timer Ci<br>Operation clock from                                                                                                                                                                                                                                                                   | Signals an interrupt when overflowing. Supports Timer Clear when it matches Output Compare (ch.0, ch.4).  Operation clock frequency: fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> , fsys/2 <sup>5</sup> , fsys/2 <sup>6</sup> , fsys/2 <sup>7</sup> (fsys = Machine clock frequency) |                                               |                                                      |                   |             |  |

| Part Number<br>Parameter                      | MB90351E<br>MB90352E                                                                                                                                                                                                                                                                                                                                                                         | MB90351TE<br>MB90352TE | MB90351ES<br>MB90352ES | MB90351TES<br>MB90352TES | MB90V340E-1<br>01    | MB90V340E-1<br>02 |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|--------------------------|----------------------|-------------------|

|                                               |                                                                                                                                                                                                                                                                                                                                                                                              | 4 cha                  | ınnels                 |                          | 8 channels           |                   |

| 16-bit output compare                         |                                                                                                                                                                                                                                                                                                                                                                                              |                        | run Timer matches      |                          | egisters.            |                   |

| 40 hit is not a set of                        |                                                                                                                                                                                                                                                                                                                                                                                              | 6 cha                  | innels                 |                          | 8 cha                | annels            |

| 16-bit input capture                          | Retains 16-bit free                                                                                                                                                                                                                                                                                                                                                                          | e-run timer value by   | / (rising edge, fallin | ig edge, or the both     | n edges), signals ar | n interrupt.      |

| 8/16-bit<br>programmable pulse gen-<br>erator | 8 channels 6 channels (16-bit)/10 channels (8-bit) 8-bit reload counters × 12 8-bit reload registers for L pulse width×12 8-bit reload registers for H pulse width×12 8-bit reload registers                                                             |                        |                        |                          |                      |                   |

| erator                                        | Supports 8-bit and 16-bit operation modes.  A pair of 8-bit reload counters can be configured as one 16-bit reload counter or as 8-bit prescaler + 8-bit reload counter.  Operation clock frequency: fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> or 128 µs@fosc = 4 MHz (fsys = Machine clock frequency, fosc = Oscillation clock frequency) |                        |                        |                          |                      |                   |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                              | 1 cha                  | 3 cha                  | annels                   |                      |                   |

| CAN interface                                 | Compliant with CAN standard Version 2.0 Part A and Part B. Automatic re-transmission in case of error Automatic transmission responding to Remote Frame 16 prioritized message buffers for data and ID Supports multiple messages. Flexible configuration of acceptance filtering: Full bit compare/Full bit mask/Two partial bit masks Supports up to 1 Mbps.                               |                        |                        |                          |                      |                   |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                              | 8 cha                  | innels                 |                          | 16 ch                | annels            |

| External interrupt                            | Can be used rising edge, falling edge, starting up by "H"/"L" level input, external interrupt, extended intelligent I/O services (El <sup>2</sup> OS) and DMA.                                                                                                                                                                                                                               |                        |                        |                          |                      |                   |

| D/A converter                                 |                                                                                                                                                                                                                                                                                                                                                                                              | -                      |                        |                          | 2 cha                | annels            |

| I/O ports                                     | Virtually all external pins can be used as general purpose I/O port. All push-pull outputs Bit-wise settable as input/output or peripheral signal Settable as CMOS schmitt trigger/ automotive inputs TTL input level settable for external bus (only for external bus pin)                                                                                                                  |                        |                        |                          |                      |                   |

| Flash memory                                  |                                                                                                                                                                                                                                                                                                                                                                                              |                        | -                      | _                        |                      |                   |

| Corresponding evaluation name                 | MB90V3                                                                                                                                                                                                                                                                                                                                                                                       | 40E-102                | MB90V3                 | 340E-101                 | -                    | _                 |

<sup>\*:</sup> It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to the Emulator hardware manual about details.

# 2. Product Lineup 2 (With Clock supervisor function)

■ Flash memory products

| Part Number                               | MB90F356E<br>MB90F357E                                                                                                                                                                                                                                                                                                                 | MB90F356TE<br>MB90F357TE    | MB90F356ES<br>MB90F357ES                     | MB90F356TES<br>MB90F357TES |  |  |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------|----------------------------|--|--|

| Parameter                                 | MID30L321E                                                                                                                                                                                                                                                                                                                             | MID90L3511E                 | INIDA0L391E9                                 | INIDA0L221 IE2             |  |  |

| Туре                                      |                                                                                                                                                                                                                                                                                                                                        | Flash memo                  | ory products                                 |                            |  |  |

| CPU                                       |                                                                                                                                                                                                                                                                                                                                        | F <sup>2</sup> MC-16        | 6LX CPU                                      |                            |  |  |

| System clock                              | On-chip PLL clock multiplier Minimum instruction execution                                                                                                                                                                                                                                                                             |                             |                                              |                            |  |  |

| ROM                                       | 64 Kbytes Flash memory : N<br>128 Kbytes Dual operation I<br>same time) : MB90F357E(\$                                                                                                                                                                                                                                                 | Flash memory (Erase/write a | TE(S)<br>and read can be operated at         | the                        |  |  |

| RAM                                       |                                                                                                                                                                                                                                                                                                                                        | 4 Kt                        | oytes                                        |                            |  |  |

| Emulator-specific power supply*           |                                                                                                                                                                                                                                                                                                                                        | -                           | _                                            |                            |  |  |

| Sub clock pin<br>(X0A, X1A)               | Ye                                                                                                                                                                                                                                                                                                                                     | Yes No                      |                                              |                            |  |  |

| Clock supervisor                          |                                                                                                                                                                                                                                                                                                                                        | Y                           | es                                           |                            |  |  |

| Low voltage/CPU operation detection reset | No                                                                                                                                                                                                                                                                                                                                     | Yes                         | No                                           | Yes                        |  |  |

| Operating voltage range                   | 3.5 V to 5.5 V : at normal op<br>3.5 V to 5.5 V : at using A/D<br>3.5 V to 5.5 V : at using exte                                                                                                                                                                                                                                       | converter/Flash programmi   | •                                            |                            |  |  |

| Operating temperature range               |                                                                                                                                                                                                                                                                                                                                        | -40°C to                    | o +125°C                                     |                            |  |  |

| Package                                   |                                                                                                                                                                                                                                                                                                                                        | LQF                         | P-64                                         |                            |  |  |

|                                           |                                                                                                                                                                                                                                                                                                                                        | 2 cha                       | annels                                       |                            |  |  |

| LIN-UART                                  | Wide range of baud rate settings using a dedicated baud rate generator (reload timer) Special synchronous options for adapting to different synchronous serial protocols LIN functionality working either as master or slave LIN device                                                                                                |                             |                                              |                            |  |  |

| I <sup>2</sup> C (400 kbps)               |                                                                                                                                                                                                                                                                                                                                        | 1 cha                       | annel                                        |                            |  |  |

|                                           |                                                                                                                                                                                                                                                                                                                                        | 15 ch                       | annels                                       |                            |  |  |

| A/D converter                             | 10-bit or 8-bit resolution<br>Conversion time : Min 3 μs i                                                                                                                                                                                                                                                                             | . "                         | ,                                            |                            |  |  |

| 16-bit reload timer<br>(4 channels)       | Operation clock frequency :<br>Supports External Event Co                                                                                                                                                                                                                                                                              |                             | ys = Machine clock frequenc                  | cy)                        |  |  |

| dC hit from a roun times                  | Free-run Timer 0 (clock input FRCK0) corresponds to ICU 0/1. Free-run Timer 1 (clock input FRCK1) corresponds to ICU 4/5/6/7, OCU 4/5/6/7.                                                                                                                                                                                             |                             |                                              |                            |  |  |

| 16-bit free-run timer (2 channels)        | Signals an interrupt when overflowing. Supports Timer Clear when a match with Output Compare (Channel 0, 4). Operation clock frequency: fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> , fsys/2 <sup>5</sup> , fsys/2 <sup>6</sup> , fsys/2 <sup>7</sup> (fsys = Machine clock frequency) |                             |                                              |                            |  |  |