# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

The following document contains information on Cypress products. The document has the series name, product name, and ordering part numbering with the prefix "MB". However, Cypress will offer these products to new and existing customers with the series name, product name, and ordering part number with the prefix "CY".

### How to Check the Ordering Part Number

- 1. Go to <u>www.cypress.com/pcn</u>.

- 2. Enter the keyword (for example, ordering part number) in the **SEARCH PCNS** field and click **Apply**.

- 3. Click the corresponding title from the search results.

- 4. Download the Affected Parts List file, which has details of all changes

### For More Information

Please contact your local sales office for additional information about Cypress products and solutions.

### About Cypress

Cypress is the leader in advanced embedded system solutions for the world's most innovative automotive, industrial, smart home appliances, consumer electronics and medical products. Cypress' microcontrollers, analog ICs, wireless and USB-based connectivity solutions and reliable, high-performance memories help engineers design differentiated products and get them to market first. Cypress is committed to providing customers with the best support and development resources on the planet enabling them to disrupt markets by creating new product categories in record time. To learn more, go to www.cypress.com.

### MB90387/387S/F387/F387S MB90V495G

## 16-bit Microcontrollers F<sup>2</sup>MC-16LX MB90385 Series

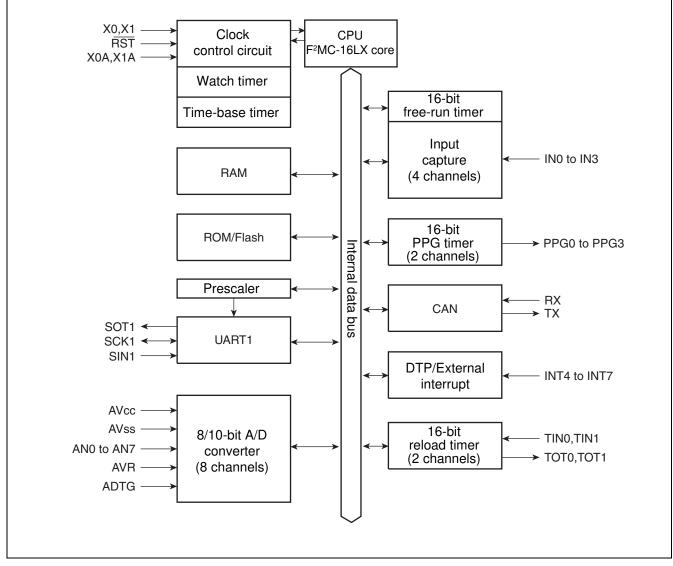

MB90385 series devices are general-purpose high-performance 16-bit micro controllers designed for process control of consumer products, which require high-speed real-time processing. The devices of this series have the built-in full-CAN interface.

The system, inheriting the architecture of F<sup>2</sup>MC family, employs additional instruction ready for high-level languages, expanded addressing mode, enhanced multiply-divide instructions, and enriched bit-processing instructions. Furthermore, employment of 32-bit accumulator achieves processing of long-word data (32 bits).

The peripheral resources of MB90385 series include the following:

8/10-bit Å/D converter, UART (SCI), 8/16-bit PPG timer, 16-bit input-output timer (16-bit free-run timer, input capture 0, 1, 2, 3 (ICU)), and CAN controller.

### Features

### Clock

- Built-in PLL clock frequency multiplication circuit

- Selection of machine clocks (PLL clocks) is allowed among frequency division by two on oscillation clock, and multiplication of 1 to 4 times of oscillation clock (for 4-MHz oscillation clock, 4 MHz to 16 MHz).

- Operation by sub-clock (8.192 kHz) is allowed. (MB90387, MB90F387)

- Minimum execution time of instruction: 62.5 ns (when operating with 4-MHz oscillation clock, and 4-time multiplied PLL clock).

### 16 Mbyte CPU memory Space

24-bit internal addressing

### Instruction System Best Suited to Controller

- Wide choice of data types (bit, byte, word, and long word)

- Wide choice of addressing modes (23 types)

- Enhanced multiply-divide instructions and RETI instructions

- Enhanced high-precision computing with 32-bit accumulator

## Instruction System Compatible with High-level Language (C language) and Multitask

- Employing system stack pointer

- Enhanced various pointer indirect instructions

- Barrel shift instructions

### **Increased Processing Speed**

4-byte instruction queue

## Powerful Interrupt Function with 8 Levels and 34 Factors

### Automatic Data Transfer Function Independent of CPU

Expanded intelligent I/O service function (EI<sup>2</sup> OS): Maximum of 16 channels

### Low Power Consumption (standby) Mode

■ Sleep mode (a mode that halts CPU operating clock)

- Time-base timer mode (a mode that operates oscillation clock, sub clock, time-base timer and watch timer only)

- Watch mode (a mode that operates sub clock and watch timer only)

- Stop mode (a mode that stops oscillation clock and sub clock)

- CPU blocking operation mode

#### Process

CMOS technology

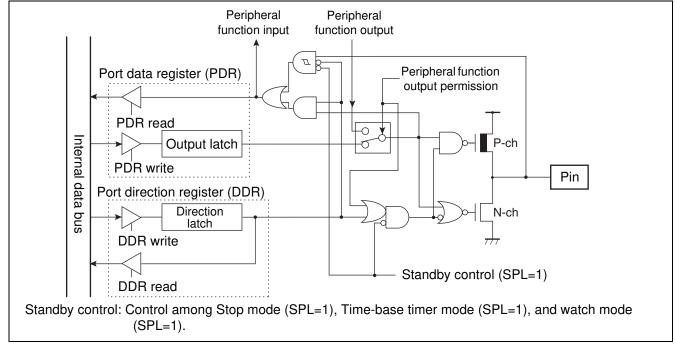

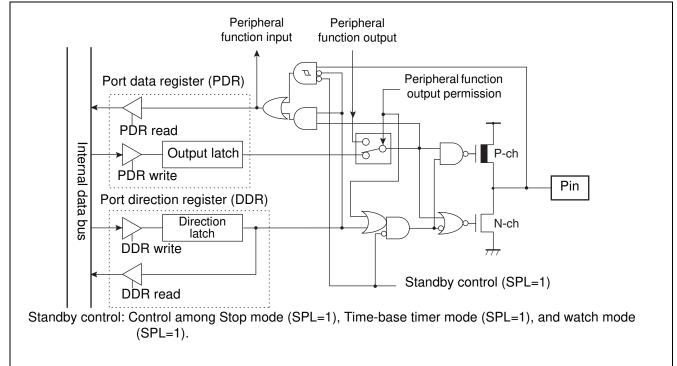

### I/O Port

General-purpose input/output port (CMOS output):

MB90387, MB90F387: 34 ports (including 4 high-current output ports) MB90387S, MB90F387S: 36 ports (including 4 high-current output ports)

### Timer

- Time-base timer, watch timer, watchdog timer: 1 channel

- 8/16-bit PPG timer: 8-bit x 4 channels, or 16-bit x 2 channels

- 16-bit reload timer: 2 channels

- 16-bit input/output timer

- 16-bit free run timer: 1 channel

- □ 16-bit input capture: (ICU): 4 channels

Interrupt request is issued upon latching a count value of 16bit free run timer by detection of an edge on pin input.

### CAN Controller: 1 channel

- Compliant with Ver2.0A and Ver2.0B CAN specifications

- 8 built-in message buffers

- Transmission rate of 10 kbps to 1 Mbps (by 16 MHz machine clock)

- CAN wake-up

### UART (SCI): 1 channel

- Equipped with full-duplex double buffer

- Clock-asynchronous or clock-synchronous serial transmission is available.

### Cypress Semiconductor Corporation

Document Number: 002-07765 Rev. \*A

## DTP/External Interrupt: 4 channels, CAN wakeup: 1channel

Module for activation of expanded intelligent I/O service (EI<sup>2</sup>OS), and generation of external interrupt.

### **Delay Interrupt Generator Module**

Generates interrupt request for task switching.

### 8/10-bit A/D Converter: 8 channels

- Resolution is selectable between 8-bit and 10-bit.

- Activation by external trigger input is allowed.

- Conversion time: 6.125 µs (at 16 MHz machine clock, including sampling time)

### **Program Patch Function**

Address matching detection for 2 address pointers.

### MB90387/387S/F387/F387S MB90V495G

### Contents

| 8/10-bit A/D Converter                                       | 43<br>45<br>47<br>49<br>51<br>52 |

|--------------------------------------------------------------|----------------------------------|

| Electrical Characteristics                                   |                                  |

| Absolute Maximum Rating5<br>Recommended Operating Conditions |                                  |

| DC Characteristics                                           |                                  |

| AC Characteristics                                           |                                  |

| A/D Converter 6                                              |                                  |

| Definition of A/D Converter Terms 6                          |                                  |

| Notes on A/D Converter Section 7                             |                                  |

| Flash Memory Program/Erase Characteristics                   | 70                               |

| Example Characteristics                                      | 71                               |

| Ordering Information                                         | 77                               |

| Package Dimension 7                                          | 78                               |

| Major Changes 7                                              | 79                               |

| Document History 8                                           |                                  |

| Sales, Solutions, and Legal Information 8                    |                                  |

### 1. Product Lineup

| Part Number<br>Parameter         |                          | MB90F387<br>MB90F387S                                                                                                                                                                                                                                                                      | MB90387<br>MB90387S                                                                           | MB90V495G                 |  |  |

|----------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------|--|--|

| Classification                   |                          | Flash ROM                                                                                                                                                                                                                                                                                  | Mask ROM                                                                                      | Evaluation product        |  |  |

| ROM capacity                     |                          | 64 Kby                                                                                                                                                                                                                                                                                     | tes                                                                                           | _                         |  |  |

| RAM capacity                     |                          | 2 Kbyt                                                                                                                                                                                                                                                                                     | es                                                                                            | 6 Kbytes                  |  |  |

| Process                          |                          |                                                                                                                                                                                                                                                                                            | CMOS                                                                                          | I                         |  |  |

| Package                          |                          | LQFP-48 (pin pit                                                                                                                                                                                                                                                                           | ch 0.50 mm)                                                                                   | PGA-256                   |  |  |

| Operating power                  | supply voltage           | 3.5 V to                                                                                                                                                                                                                                                                                   | 5.5 V                                                                                         | 4.5 V to 5.5 V            |  |  |

| Special power su<br>emulator*1   | upply for                | -                                                                                                                                                                                                                                                                                          |                                                                                               | None                      |  |  |

| CPU functions                    |                          | Number of basic instructions<br>Instruction bit length<br>Instruction length<br>Data bit length                                                                                                                                                                                            | : 351 instructions<br>: 8 bits and 16 bits<br>: 1 byte to 7 bytes<br>: 1 bit, 8 bits, 16 bits |                           |  |  |

|                                  |                          | Minimum instruction execution ti                                                                                                                                                                                                                                                           | me: 62.5 ns (at 16 MHz macł                                                                   | nine clock)               |  |  |

|                                  |                          | Interrupt processing time: 1.5 $\mu$ s                                                                                                                                                                                                                                                     | at minimum (at 16 MHz mac                                                                     | hine clock)               |  |  |

| Low power cons<br>(standby) mode | umption                  | Sleep mode / Watch mode / Tim                                                                                                                                                                                                                                                              | e-base timer mode / Stop mo                                                                   | de / CPU intermittent     |  |  |

| I/O port                         |                          | General-purpose input/output ports (CMOS output): 34 ports (36 ports <sup>*2</sup> ) including 4 high-current output ports (P14 to P17)                                                                                                                                                    |                                                                                               |                           |  |  |

| Time-base timer                  |                          | 18-bit free-run counter<br>Interrupt cycle: 1.024 ms, 4.096 ms, 16.834 ms, 131.072 ms<br>(with oscillation clock frequency at 4 MHz)                                                                                                                                                       |                                                                                               |                           |  |  |

| Watchdog timer                   |                          | Reset generation cycle: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms<br>(with oscillation clock frequency at 4 MHz)                                                                                                                                                                              |                                                                                               |                           |  |  |

| 16-bit input/<br>output timer    | 16-bit free-run<br>timer | Number of channels: 1<br>Interrupt upon occurrence of ove                                                                                                                                                                                                                                  | erflow                                                                                        |                           |  |  |

|                                  | Input capture            | Number of channels: 4<br>Retaining free-run timer value se                                                                                                                                                                                                                                 | t by pin input (rising edge, falli                                                            | ing edge, and both edges) |  |  |

| 16-bit reload time               | er                       | Number of channels: 2<br>16-bit reload timer operation<br>Count clock cycle: 0.25 μs, 0.5 μs, 2.0 μs<br>(at 16-MHz machine clock frequency)<br>External event count is allowed.                                                                                                            |                                                                                               |                           |  |  |

| Watch timer                      |                          | 15-bit free-run counter<br>Interrupt cycle: 31.25 ms, 62.5 ms, 12 ms, 250 ms, 500 ms, 1.0 s, 2.0 s<br>(with 8.192 kHz sub clock)                                                                                                                                                           |                                                                                               |                           |  |  |

| 8/16-bit PPG timer               |                          | Number of channels: 2 (four 8-bit channels are available also.)<br>PPG operation is allowed with four 8-bit channels or two 16-bit channels.<br>Outputting pulse wave of arbitrary cycle or arbitrary duty is allowed.<br>Count clock: 62.5 ns to 1 $\mu$ s<br>(with 16 MHz machine clock) |                                                                                               |                           |  |  |

| Delay interrupt g                | enerator module          | Interrupt generator module for task switching. Used for realtime OS.                                                                                                                                                                                                                       |                                                                                               |                           |  |  |

| DTP/External int                 | errupt                   | Number of inputs: 4<br>Activated by rising edge, falling edge, "H" level or "L" level input.<br>External interrupt or expanded intelligent I/O service (EI <sup>2</sup> OS) is available.                                                                                                  |                                                                                               |                           |  |  |

| Part Number<br>Parameter | MB90F387<br>MB90F387S                                                                                                                                                      | MB90387<br>MB90387S                                                                                         | MB90V495G                 |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------|--|--|

| 8/10-bit A/D converter   | Sequential conversion of two or<br>maximum of 8 channels is allowed<br>Single conversion mode: Selected<br>Sequential conversion mode: Se                                  | (at 16 MHz machine clock, including sampling time)<br>wo or more successive channels is allowed. (Setting a |                           |  |  |

| UART(SCI)                | Number of channels: 1<br>Clock-synchronous transfer: 62.<br>Clock-asynchronous transfer: 9,<br>Communication is allowed by bi-<br>slave type connection.                   | 615 bps to 500 kbps                                                                                         | tion function and master/ |  |  |

| CAN                      | Compliant with Ver 2.0A and Ver 2.0B CAN specifications.<br>8 built-in message buffers.<br>Transmission rate of 10 kbps to 1 Mbps (by 16 MHz machine clock)<br>CAN wake-up |                                                                                                             |                           |  |  |

\*1: Settings of DIP switch S2 for using emulation pod MB2145-507. For details, see MB2145-507 Hardware Manual (2.7 Power Pin solely for Emulator).

(2.7 Power Pin solely for Emulato

\*2: MB90387S, MB90F387S

### 2. Packages And Product Models

| Package | MB90F387, MB90F387S | MB90387, MB90387S |

|---------|---------------------|-------------------|

| LQA048  | 0                   | $\bigcirc$        |

$\bigcirc$ : Yes  $\times$ : No

Note: Refer to Package Dimension for details of the package.

### 3. Product Comparison

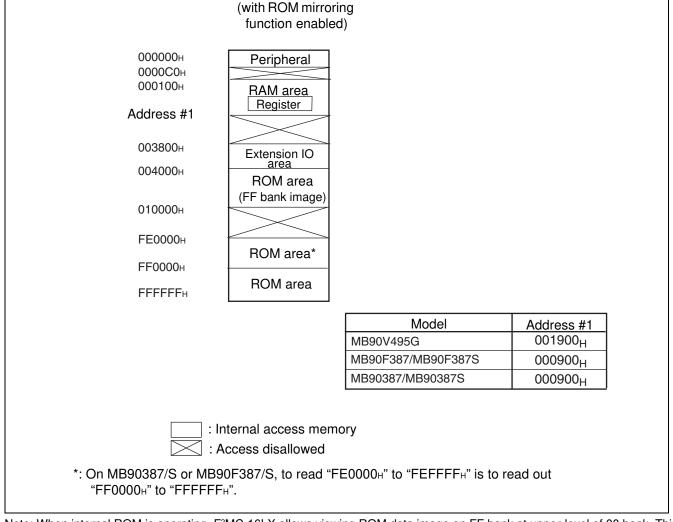

### Memory Space

When testing with test product for evaluation, check the differences between the product and a product to be used actually. Pay attention to the following points:

- The MB90V495G has no built-in ROM. However, a special-purpose development tool allows the operations as those of one with built-in ROM. ROM capacity depends on settings on a development tool.

- On MB90V495G, an image from FF4000<sup>H</sup> to FFFFF<sup>H</sup> is viewed on 00 bank and an image of FE0000<sup>H</sup> to FF3FFF<sup>H</sup> is viewed only on FE bank and FF bank. (Modified on settings of a development tool.)

- On MB90F387/F387S/387/387S, an image from FF4000H to FFFFFFH is viewed on 00 bank and an image of FE0000H to FF3FFFH is viewed only on FF bank.

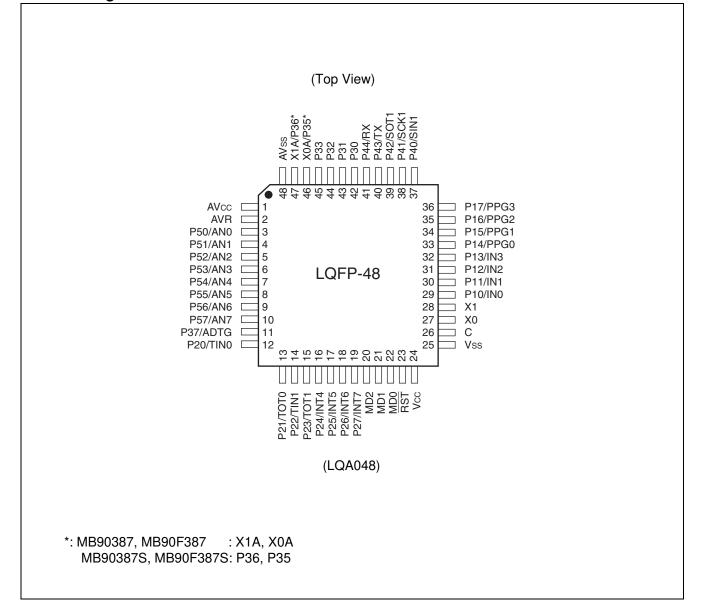

### 4. Pin Assignment

### 5. Pin Description

| Pin No.  | Pin Name     | Circuit<br>Type | Function                                                                                                    |  |  |

|----------|--------------|-----------------|-------------------------------------------------------------------------------------------------------------|--|--|

| 1        | AVcc         | -               | Vcc power input pin for A/D converter.                                                                      |  |  |

| 2        | AVR          | -               | Power (Vref+) input pin for A/D converter. Use as input for Vcc or lower.                                   |  |  |

| 3 to 10  | P50 to P57   | E               | General-purpose input/output ports.                                                                         |  |  |

|          | AN0 to AN7   |                 | Functions as analog input pins for A/D converter. Valid when analog input setting is "enabled."             |  |  |

| 11       | P37          | D               | General-purpose input/output port.                                                                          |  |  |

|          | ADTG         |                 | Function as an external trigger input pin for A/D converter. Use the pin by setting as input port.          |  |  |

| 12       | P20          | D               | General-purpose input/output port.                                                                          |  |  |

|          | TIN0         |                 | Function as an event input pin for reload timer 0. Use the pin by setting as input port.                    |  |  |

| 13       | P21          | D               | General-purpose input/output port.                                                                          |  |  |

|          | TOT0         |                 | Function as an event output pin for reload timer 0. Valid only when output setting is "enabled."            |  |  |

| 14       | P22          | D               | General-purpose input/output port.                                                                          |  |  |

|          | TIN1         |                 | Function as an event input pin for reload timer 1. Use the pin by setting as input port.                    |  |  |

| 15       | P23          | D               | General-purpose input/output port.                                                                          |  |  |

|          | TOT1         |                 | Function as an event output pin for reload timer 1. Valid only when output setting "enabled."               |  |  |

| 16 to 19 | P24 to P27   | D               | General-purpose input/output ports.                                                                         |  |  |

|          | INT4 to INT7 |                 | Functions as external interrupt input pins. Use the pins by setting as input port.                          |  |  |

| 20       | MD2          | F               | Input pin for specifying operation mode. Connect directly to Vss.                                           |  |  |

| 21       | MD1          | С               | Input pin for specifying operation mode. Connect directly to Vcc.                                           |  |  |

| 22       | MD0          | С               | Input pin for specifying operation mode. Connect directly to Vcc.                                           |  |  |

| 23       | RST          | В               | External reset input pin.                                                                                   |  |  |

| 24       | Vcc          | _               | Power source (5 V) input pin.                                                                               |  |  |

| 25       | Vss          | Ι               | Power source (0 V) input pin.                                                                               |  |  |

| 26       | С            | Ι               | Capacitor pin for stabilizing power source. Connect a ceramic capacitor of approximately 0.1 $\mu\text{F}.$ |  |  |

| 27       | X0           | Α               | Pin for high-rate oscillation.                                                                              |  |  |

| 28       | X1           | А               | Pin for high-rate oscillation.                                                                              |  |  |

| 29 to 32 | P10 to P13   | D               | General-purpose input/output ports.                                                                         |  |  |

|          | IN0 to IN3   |                 | Functions as trigger input pins of input capture ch.0 to ch.3. Use the pins by setting as input ports.      |  |  |

| 33 to 36 | P14 to P17   | G               | General-purpose input/output ports. High-current output ports.                                              |  |  |

|          | PPG0 to PPG3 |                 | Functions as output pins of PPG timers 01 and 23. Valid when output setting is "enabled."                   |  |  |

| 37       | P40          | D               | General-purpose input/output port.                                                                          |  |  |

|          | SIN1         |                 | Serial data input pin for UART. Use the pin by setting as input port.                                       |  |  |

| 38       | P41          | D               | General-purpose input/output port.                                                                          |  |  |

|          | SCK1         |                 | Serial clock input pin for UART. Valid only when serial clock input/output setting on UART is "enabled."    |  |  |

### MB90387/387S/F387/F387S MB90V495G

| Pin No.  | Pin Name   | Circuit<br>Type | Function                                                                                               |  |  |

|----------|------------|-----------------|--------------------------------------------------------------------------------------------------------|--|--|

| 39       | P42        | D               | General-purpose input/output port.                                                                     |  |  |

|          | SOT1       |                 | Serial data input pin for UART. Valid only when serial data input/output setting on UART is "enabled." |  |  |

| 40       | P43        | D               | General-purpose input/output port.                                                                     |  |  |

|          | ТХ         |                 | Transmission output pin for CAN. Valid only when output setting is "enabled."                          |  |  |

| 41       | P44        | D               | General-purpose input/output port.                                                                     |  |  |

|          | RX         |                 | Transmission output pin for CAN. Valid only when output setting is "enabled."                          |  |  |

| 42 to 45 | P30 to P33 | D               | General-purpose input/output ports.                                                                    |  |  |

| 46       | X0A*       | А               | Pin for low-rate oscillation.                                                                          |  |  |

|          | P35*       |                 | General-purpose input/output port.                                                                     |  |  |

| 47       | X1A*       | А               | Pin for low-rate oscillation.                                                                          |  |  |

|          | P36*       |                 | General-purpose input/output port.                                                                     |  |  |

| 48       | AVss       | -               | Vss power source input pin for A/D converter.                                                          |  |  |

\*: MB90387, MB90F387: X1A, X0A MB90387S, MB90F387S: P36, P35

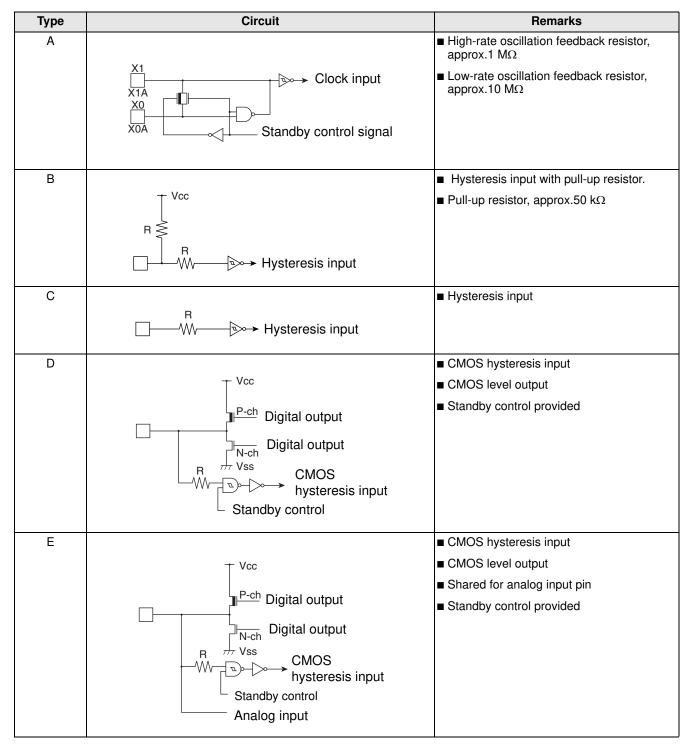

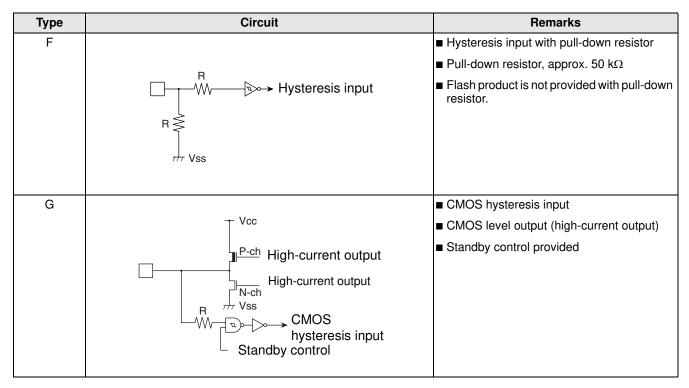

### 6. I/O Circuit Type

### 7. Handling Devices

### Do Not Exceed Maximum Rating (preventing "latch up")

- On a CMOS IC, latch-up may occur when applying a voltage higher than Vcc or a voltage lower than Vss to input or output pin, which has no middle or high withstand voltage. Latch-up may also occur when a voltage exceeding maximum rating is applied across Vcc pin and Vss pin.

- Latch-up causes drastic increase of power current, which may lead to destruction of elements by heat. Extreme caution must be taken not to exceed maximum rating.

- When turning on and off analog power source, take extra care not to apply an analog power voltages (AVcc and AVR) and analog input voltage that are higher than digital power voltage (Vcc).

### Handling Unused Pins

Leaving unused input pins open may cause permanent destruction by malfunction or latch-up. Apply pull-up or pull-down process to the unused pins using resistors of 2 kΩ or higher. Leave unused input/output pins open under output status, or process as input pins if they are under input status.

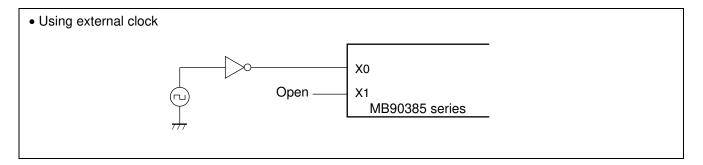

### **Using External Clock**

When using an external clock, drive only X0 pin and leave X1 pin open. An example of using an external clock is shown below.

### Notes When Using No Sub Clock

■ If an oscillator is not connected to X0A and X1A pin, apply pull-down resistor to X0A pin and leave X1A pin open.

#### About Power Supply Pins

- If two or more Vcc and Vss pins exist, the pins that should be at the same potential are connected to each other inside the device. For reducing unwanted emissions and preventing malfunction of strobe signals caused by increase of ground level, however, be sure to connect the Vcc and Vss pins to the power source and the ground externally.

- Pay attention to connect a power supply to Vcc and Vss of MB90385 series device in a lowest-possible impedance.

- Near pins of MB90385 series device, connecting a bypass capacitor is recommended at 0.1 µF across Vcc pin and Vss pin.

#### **Crystal Oscillator Circuit**

- Noises around X0 and X1 pins cause malfunctions on a MB90385 series device. Design a print circuit so that X0 and X1 pins, an crystal oscillator (or a ceramic oscillator), and bypass capacitor to the ground become as close as possible to each other. Furthermore, avoid wires to X0 and X1 pins crossing each other as much as possible.

- Print circuit designing that surrounds X0 and X1 pins with grounding wires, which ensures stable operation, is strongly recommended.

#### Caution on Operations during PLL Clock Mode

If the PLL clock mode is selected, the microcontroller attempt to be working with the self-oscillating circuit even when there is no external oscillator or external clock input is stopped. Performance of this operation, however, cannot be guaranteed.

#### Sequence of Turning on Power of A/D Converter and Applying Analog Input

- Be sure to turn on digital power (Vcc) before applying signals to the A/D converter and applying analog input signals (AN0 to AN7 pins).

- Be sure to turn off the power of A/D converter and analog input before turning off the digital power source.

- Be sure not to apply AVR exceeding AVcc when turning on and off. (No problems occur if analog and digital power is turned on and off simultaneously.)

### Handling Pins When A/D Converter is Not Used

■ If the A/D converter is not used, connect the pins under the following conditions: "AVcc=AVR=Vcc," and "AVss=Vss"

#### Note on Turning on Power

For preventing malfunctions on built-in step-down circuit, maintain a minimum of 50 μs of voltage rising time (between 0.2 V and 2.7V) when turning on the power.

### Stabilization of Supply Voltage

■ A sudden change in the supply voltage may cause the device to malfunction even within the specified Vcc supply voltage operating range. Therefore, the Vcc supply voltage should be stabilized.

For reference, the supply voltage should be controlled so that  $V_{CC}$  ripple variations (peak-to-peak values) at commercial frequencies (50 Hz / 60 Hz) fall below 10% of the standard  $V_{CC}$  supply voltage and the coefficient of fluctuation does not exceed 0.1 V/ms at instantaneous power switching.

### 8. Block Diagram

### 9. Memory Map

MB90385 series allows specifying a memory access mode "single chip mode."

### 9.1 Memory Allocation of MB90385

MB90385 series model has 24-bit wide internal address bus and up to 24-bit bus of external address bus. A maximum of 16-Mbyte memory space of external access memory is accessible.

### 9.2 Memory Map

Note: When internal ROM is operating, F<sup>2</sup>MC-16LX allows viewing ROM data image on FF bank at upper-level of 00 bank. This function is called "mirroring ROM," which allows effective use of C compiler small model.

F<sup>2</sup>MC-16LX assigns the same low order 16-bit address to FF bank and 00 bank, which allows referencing table in ROM without specifying "far" using pointer.

For example, when accessing to "00C000H", ROM data at "FFC000H" is accessed actually. However, because ROM area of FF bank exceeds 48 Kbytes, viewing all areas is not possible on 00 bank image. Because ROM data of "FF4000H" to "FFFFFH" is viewed on "004000H" to "00FFFFH" image, store a ROM data table in area "FF4000H" to "FFFFFH."

### 10. I/O Map

| Address                  | Register<br>Abbreviation | Register                                                    | Read/<br>Write | Resource                  | Initial Value         |  |  |  |  |

|--------------------------|--------------------------|-------------------------------------------------------------|----------------|---------------------------|-----------------------|--|--|--|--|

| 00000н                   | (Reserved area) *        |                                                             |                |                           |                       |  |  |  |  |

| 000001н                  | PDR1                     | Port 1 data register                                        | R/W            | Port 1                    | XXXXXXXXB             |  |  |  |  |

| 000002н                  | PDR2                     | Port 2 data register                                        | R/W            | Port 2                    | XXXXXXXXB             |  |  |  |  |

| 00003н                   | PDR3                     | Port 3 data register                                        | R/W            | Port 3                    | XXXXXXXXB             |  |  |  |  |

| 000004н                  | PDR4                     | Port 4 data register                                        | R/W            | Port 4                    | XXXXXXXXB             |  |  |  |  |

| 000005н                  | PDR5                     | Port 5 data register                                        | R/W            | Port 5                    | XXXXXXXXB             |  |  |  |  |

| 000006н<br>to<br>000010н |                          | (Reserve                                                    | ed area) *     |                           |                       |  |  |  |  |

| <b>000011</b> н          | DDR1                     | Port 1 direction data register                              | R/W            | Port 1                    | 0000000в              |  |  |  |  |

| 000012н                  | DDR2                     | Port 2 direction data register                              | R/W            | Port 2                    | 0000000в              |  |  |  |  |

| 000013н                  | DDR3                     | Port 3 direction data register                              | R/W            | Port 3                    | 000Х000в              |  |  |  |  |

| <b>000014</b> н          | DDR4                     | Port 4 direction data register                              | R/W            | Port 4                    | ХХХ00000в             |  |  |  |  |

| 000015н                  | DDR5                     | Port 5 direction data register                              | R/W            | Port 5                    | 0000000в              |  |  |  |  |

| 000016н<br>to<br>00001Ан |                          | (Reserve                                                    | ed area) *     | 1                         |                       |  |  |  |  |

| 00001Bн                  | ADER                     | Analog input permission register                            | R/W            | 8/10-bit A/D<br>converter | 11111111в             |  |  |  |  |

| 00001Снto<br>000025н     |                          | (Reserve                                                    | ed area) *     |                           |                       |  |  |  |  |

| 000026н                  | SMR1                     | Serial mode register 1                                      | R/W            | UART1                     | 0000000в              |  |  |  |  |

| 000027н                  | SCR1                     | Serial control register 1                                   | R/W, W         |                           | 00000100в             |  |  |  |  |

| 000028н                  | SIDR1/<br>SODR1          | Serial input data register 1/ Serial output data register 1 | R, W           |                           | XXXXXXXXB             |  |  |  |  |

| 000029н                  | SSR1                     | Serial status data register 1                               | R, R/W         | ]                         | 00001000в             |  |  |  |  |

| 00002Ан                  |                          | (Reserve                                                    | ed area) *     |                           | ·                     |  |  |  |  |

| 00002Вн                  | CDCR1                    | Communication prescaler control<br>register 1               | R/W            | UART1                     | 0XXX0000 <sub>B</sub> |  |  |  |  |

| 00002Cнto<br>00002Fн     |                          | (Reserve                                                    | ed area) *     |                           |                       |  |  |  |  |

| 000030н                  | ENIR                     | DTP/External interrupt permission register                  | R/W            | DTP/External interrupt    | 0000000B              |  |  |  |  |

| 000031н                  | EIRR                     | DTP/External interrupt permission register                  | R/W            |                           | XXXXXXXXB             |  |  |  |  |

| 000032н                  | ELVR                     | Detection level setting register                            | R/W            | 1                         | 0000000в              |  |  |  |  |

| 000033н                  | 1                        |                                                             | R/W            | 1                         | 0000000в              |  |  |  |  |

| 000034н                  | ADCS                     | A/D control status register                                 | R/W            | 8/10-bit A/D              | 0000000в              |  |  |  |  |

| 000035н                  | 1                        | _                                                           | R/W, W         | converter                 | 0000000в              |  |  |  |  |

| 000036н                  | ADCR                     | A/D data register                                           | W, R           | 1                         | XXXXXXXXB             |  |  |  |  |

| 000037н                  | 1                        |                                                             | R              | 1                         | 00101XXXв             |  |  |  |  |

| Address               | Register<br>Abbreviation | Register                                  | Read/<br>Write | Resource                                      | Initial Value         |  |  |  |

|-----------------------|--------------------------|-------------------------------------------|----------------|-----------------------------------------------|-----------------------|--|--|--|

| 000038н               |                          | (Reserve                                  | ed area) *     | · · ·                                         |                       |  |  |  |

| to<br>00003F⊦         |                          |                                           |                |                                               |                       |  |  |  |

| 000040н               | PPGC0                    | PPG0 operation mode control register      | R/W, W         | 8/16-bit PPG timer 0/                         | 0X000XX1в             |  |  |  |

| <b>000041</b> н       | PPGC1                    | PPG1 operation mode control register      | R/W, W         | 1                                             | 0Х00001в              |  |  |  |

| 000042н               | PPG01                    | PPG0/1 count clock selection register     | R/W            | -                                             | 000000XXB             |  |  |  |

| 000043н               |                          | (Reserve                                  | ed area) *     |                                               |                       |  |  |  |

| 000044н               | PPGC2                    | PPG2 operation mode control register      | R/W, W         | 8/16-bit PPG timer 2/                         | 0X000XX1 <sub>B</sub> |  |  |  |

| <b>000045</b> н       | PPGC3                    | PPG3 operation mode control register      | R/W, W         | 3                                             | 0Х00001в              |  |  |  |

| 000046н               | PPG23                    | PPG2/3 count clock selection register     | R/W            | 1                                             | 000000XXB             |  |  |  |

| 000047н to<br>00004Fн |                          | (Reserve                                  | ed area) *     |                                               |                       |  |  |  |

| 000050н               | IPCP0                    | Input capture data register 0             | R              | 16-bit input/output                           | XXXXXXXXB             |  |  |  |

| <b>000051</b> н       |                          |                                           |                | timer                                         | XXXXXXXXB             |  |  |  |

| 000052н               | IPCP1                    | Input capture data register 1             | R              |                                               | XXXXXXXXB             |  |  |  |

| 000053н               |                          |                                           |                |                                               | XXXXXXXXB             |  |  |  |

| <b>000054</b> н       | ICS01                    | Input capture control status register     | R/W            |                                               | 0000000в              |  |  |  |

| 000055н               | ICS23                    |                                           |                |                                               | 0000000в              |  |  |  |

| 000056н               | TCDT                     | Timer counter data register               | R/W            |                                               | 0000000в              |  |  |  |

| 000057н               |                          |                                           |                |                                               | 0000000в              |  |  |  |

| <b>000058</b> н       | TCCS                     | Timer counter control status register     | R/W            | 1                                             | 0000000в              |  |  |  |

| 000059н               |                          | (Reserve                                  | ed area) *     |                                               |                       |  |  |  |

| 00005Ан               | IPCP2                    | Input capture data register 2             | R              | 16-bit input/output                           | XXXXXXXXB             |  |  |  |

| 00005Вн               |                          |                                           |                | timer                                         | XXXXXXXXB             |  |  |  |

| 00005Сн               | IPCP3                    | Input capture data register 3             | R              | 1                                             | XXXXXXXXB             |  |  |  |

| 00005Dн               |                          |                                           |                |                                               | XXXXXXXXB             |  |  |  |

| 00005Eнto<br>000065н  |                          | (Reserve                                  | ed area) *     | ·                                             |                       |  |  |  |

| 000066н               | TMCSR0                   | Timer control status register             | R/W            | 16-bit reload timer 0                         | 0000000в              |  |  |  |

| 000067н               |                          |                                           | R/W            | 1                                             | ХХХХ0000в             |  |  |  |

| 000068н               | TMCSR1                   |                                           | R/W            | 16-bit reload timer 1                         | 0000000в              |  |  |  |

| 000069н               |                          |                                           | R/W            | 1                                             | ХХХХ0000в             |  |  |  |

| 00006Aнto<br>00006Eн  | (Reserved area) *        |                                           |                |                                               |                       |  |  |  |

| 00006Fн               | ROMM                     | ROM mirroring function selection register | W              | ROM mirroring<br>function selection<br>module | XXXXXXX1B             |  |  |  |

| 000070н               |                          | (Reserve                                  | ed area) *     | ·                                             |                       |  |  |  |

| to<br>00007F⊦         |                          |                                           |                | · · · · · · · · · · · · · · · · · · ·         |                       |  |  |  |

| 000080н               | BVALR                    | Message buffer enabling register          | R/W            | CAN controller                                | 0000000в              |  |  |  |

| <b>000081</b> н       |                          | (Reserve                                  | ed area) *     | T                                             |                       |  |  |  |

| 000082н               | TREQR                    | Send request register                     | R/W            | CAN controller                                | 0000000в              |  |  |  |

| Address                  | Register<br>Abbreviation | Register                                                | Read/<br>Write | Resource                            | Initial Value         |  |  |  |  |

|--------------------------|--------------------------|---------------------------------------------------------|----------------|-------------------------------------|-----------------------|--|--|--|--|

| 000083н                  | (Reserved area) *        |                                                         |                |                                     |                       |  |  |  |  |

| 000084н                  | TCANR                    | Send cancel register                                    | W              | CAN controller                      | 0000000в              |  |  |  |  |

| 000085н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |  |  |  |  |

| 000086н                  | TCR                      | Send completion register                                | R/W            | CAN controller                      | 0000000в              |  |  |  |  |

| 000087н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |  |  |  |  |

| 000088н                  | RCR                      | Receive completion register                             | R/W            | CAN controller                      | 0000000в              |  |  |  |  |

| 000089н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |  |  |  |  |

| 00008Ан                  | RRTRR                    | Receive RTR register                                    | R/W            | CAN controller                      | 0000000в              |  |  |  |  |

| 00008Bн                  |                          | (Reserve                                                | ed area) *     |                                     |                       |  |  |  |  |

| 00008Сн                  | ROVRR                    | Receive overrun register                                | R/W            | CAN controller                      | 0000000в              |  |  |  |  |

| 00008Dн                  |                          | (Reserve                                                | ed area) *     |                                     |                       |  |  |  |  |

| 00008Eн                  | RIER                     | Receive completion interrupt<br>permission register     | R/W            | CAN controller                      | 0000000в              |  |  |  |  |

| 00008Fн<br>to<br>00009Dн |                          | (Reserv                                                 | ed area) *     |                                     |                       |  |  |  |  |

| 00009Eн                  | PACSR                    | Address detection control register                      | R/W            | Address matching detection function | 0000000в              |  |  |  |  |

| 00009Fн                  | DIRR                     | Delay interrupt request generation/<br>release register | R/W            | Delay interrupt generation module   | XXXXXXX0 <sub>B</sub> |  |  |  |  |

| 0000 <b>A0</b> н         | LPMCR                    | Lower power consumption mode control register           | W,R/W          | Lower power consumption mode        | 00011000в             |  |  |  |  |

| 0000A1н                  | CKSCR                    | Clock selection register                                | R,R/W          | Clock                               | 11111100в             |  |  |  |  |

| 0000A2н<br>to<br>0000A7н |                          | (Reserv                                                 | ed area) *     |                                     |                       |  |  |  |  |

| 0000 <b>А</b> 8н         | WDTC                     | Watchdog timer control register                         | R,W            | Watchdog timer                      | XXXXX111 <sub>B</sub> |  |  |  |  |

| 0000 <b>А</b> 9н         | TBTC                     | Time-base timer control register                        | R/W,W          | Time-base timer                     | 1XX00100в             |  |  |  |  |

| 0000ААн                  | WTC                      | Watch timer control register                            | R,R/W          | Watch timer                         | 1X001000в             |  |  |  |  |

| 0000ABн<br>to<br>0000ADн | (Reserved area) *        |                                                         |                |                                     |                       |  |  |  |  |

| 0000AEн                  | FMCS                     | Flash memory control status register                    | R,W,R/W        | 512k-bit Flash<br>memory            | 000Х0000в             |  |  |  |  |

| 0000AFн                  |                          | (Reserv                                                 | ed area) *     |                                     |                       |  |  |  |  |

| Address                  | Register<br>Abbreviation | Register                                            | Read/<br>Write | Resource                            | Initial Value |

|--------------------------|--------------------------|-----------------------------------------------------|----------------|-------------------------------------|---------------|

| 0000В0н                  | ICR00                    | Interrupt control register 00                       | R/W            | Interrupt controller                | 00000111в     |

| 0000B1н                  | ICR01                    | Interrupt control register 01                       |                |                                     | 00000111в     |

| 0000В2н                  | ICR02                    | Interrupt control register 02                       |                |                                     | 00000111в     |

| 0000ВЗн                  | ICR03                    | Interrupt control register 03                       |                |                                     | 00000111в     |

| 0000B4н                  | ICR04                    | Interrupt control register 04                       |                |                                     | 00000111в     |

| 0000B5н                  | ICR05                    | Interrupt control register 05                       |                |                                     | 00000111в     |

| 0000В6н                  | ICR06                    | Interrupt control register 06                       |                |                                     | 00000111в     |

| 0000B7н                  | ICR07                    | Interrupt control register 07                       |                |                                     | 00000111в     |

| 0000B8н                  | ICR08                    | Interrupt control register 08                       |                |                                     | 00000111в     |

| 0000В9н                  | ICR09                    | Interrupt control register 09                       | _              |                                     | 00000111в     |

| 0000ВАн                  | ICR10                    | Interrupt control register 10                       | _              |                                     | 00000111в     |

| 0000ВВн                  | ICR11                    | Interrupt control register 11                       | _              |                                     | 00000111в     |

| 0000ВСн                  | ICR12                    | Interrupt control register 12                       | _              |                                     | 00000111в     |

| 0000BDн                  | ICR13                    | Interrupt control register 13                       | _              |                                     | 00000111в     |

| 0000BEн                  | ICR14                    | Interrupt control register 14                       | _              |                                     | 00000111в     |

| 0000BFн                  | ICR15                    | Interrupt control register 15                       | _              |                                     | 00000111в     |

| 0000C0н<br>to<br>0000FFн |                          | (Reser                                              | ved area) *    |                                     |               |

| 001FF0⊦                  | PADR0                    | Detection address setting register 0 (low-order)    | R/W            | Address matching detection function | XXXXXXXXB     |

| 001FF1⊦                  |                          | Detection address setting register 0 (middle-order) |                |                                     | XXXXXXXXB     |

| 001FF2⊦                  |                          | Detection address setting register 0 (high-order)   |                |                                     | XXXXXXXXB     |

| 001FF3⊦                  | PADR1                    | Detection address setting register 1 (low-order)    | R/W            |                                     | XXXXXXXXB     |

| 001FF4н                  |                          | Detection address setting register 1 (middle-order) |                | -                                   | XXXXXXXXB     |

| 001FF5н                  |                          | Detection address setting register 1 (high-order)   |                |                                     | XXXXXXXXB     |

| 003900н                  | TMR0/                    | 16-bit timer register 0/16-bit reload               | R,W            | 16-bit reload timer 0               | XXXXXXXXB     |

| <b>003901</b> н          | TMRLR0                   | register                                            |                |                                     | XXXXXXXXB     |

| 003902н                  | TMR1/                    | 16-bit timer register 1/16-bit reload               | R,W            | 16-bit reload timer 1               | XXXXXXXXB     |

| 003903н                  | TMRLR1                   | register                                            |                |                                     | XXXXXXXXB     |

| 003904н<br>to<br>00390Fн |                          | (Reser                                              | ved area) *    | · · · · ·                           |               |

\_\_\_\_\_

| Address                  | Register<br>Abbreviation | Register               | Read/<br>Write | Resource           | Initial Value                |

|--------------------------|--------------------------|------------------------|----------------|--------------------|------------------------------|

| <b>003910</b> н          | PRLL0                    | PPG0 reload register L | R/W            | 8/16-bit PPG timer | XXXXXXXXB                    |

| <b>003911</b> н          | PRLH0                    | PPG0 reload register H | R/W            |                    | XXXXXXXXB                    |

| 003912н                  | PRLL1                    | PPG1 reload register L | R/W            |                    | XXXXXXXXB                    |

| <b>003913</b> н          | PRLH1                    | PPG1 reload register H | R/W            |                    | XXXXXXXXB                    |

| <b>003914</b> н          | PRLL2                    | PPG2 reload register L | R/W            |                    | XXXXXXXXB                    |

| 003915 <sub>H</sub>      | PRLH2                    | PPG2 reload register H | R/W            |                    | XXXXXXXXB                    |

| <b>003916</b> н          | PRLL3                    | PPG3 reload register L | R/W            |                    | XXXXXXXXB                    |

| <b>003917</b> н          | PRLH3                    | PPG3 reload register H | R/W            |                    | XXXXXXXXB                    |

| 003918н<br>to<br>00392Fн |                          | ·                      | served area) * |                    |                              |

| 003930н<br>to<br>003BFFн |                          | ·                      | served area) * |                    |                              |

| 003C00н<br>to<br>003C0Fн |                          | RAM (Ger               | eral-purpose R | AM)                |                              |

| 003С10н<br>to<br>003С13н | IDR0                     | ID register 0          | R/W            | CAN controller     | XXXXXXXXB<br>to<br>XXXXXXXXB |

| 003C14н<br>to<br>003C17н | IDR1                     | ID register 1          | R/W            |                    | XXXXXXXXB<br>to<br>XXXXXXXXB |

| 003C18н<br>to<br>003C1Bн | IDR2                     | ID register 2          | R/W            |                    | XXXXXXXXB<br>to<br>XXXXXXXB  |

| 003C1Cн<br>to<br>003C1Fн | IDR3                     | ID register 3          | R/W            |                    | XXXXXXXXB<br>to<br>XXXXXXXB  |

| 003C20н<br>to<br>003C23н | IDR4                     | ID register 4          | R/W            |                    | XXXXXXXXB<br>to<br>XXXXXXXB  |

| 003C24н<br>to<br>003C27н | IDR5                     | ID register 5          | R/W            |                    | XXXXXXXXB<br>to<br>XXXXXXXXB |

| 003C28н<br>to<br>003C2Bн | IDR6                     | ID register 6          | R/W            |                    | XXXXXXXXB<br>to<br>XXXXXXXB  |

| 003C2Cн<br>to<br>003C2Fн | IDR7                     | ID register 7          | R/W            |                    | XXXXXXXXB<br>to<br>XXXXXXXXB |

| 003C30н,<br>003C31н      | DLCR0                    | DLC register 0         | R/W            |                    | XXXXXXXXB,<br>XXXXXXXB       |

| 003С32н,<br>003С33н      | DLCR1                    | DLC register 1         | R/W            |                    | XXXXXXXXB,<br>XXXXXXXB       |

| 003C34н,<br>003C35н      | DLCR2                    | DLC register 2         | R/W            |                    | XXXXXXXXB,<br>XXXXXXXB       |

| 003С36н,<br>003С37н      | DLCR3                    | DLC register 3         | R/W            |                    | XXXXXXXXB,<br>XXXXXXXB       |

| Address                  | Register<br>Abbreviation | Register                           | Read/<br>Write | Resource       | Initial Value                        |

|--------------------------|--------------------------|------------------------------------|----------------|----------------|--------------------------------------|

| 003С38н,<br>003С39н      | DLCR4                    | DLC register 4                     | R/W            | CAN controller | XXXXXXXXB,<br>XXXXXXXB               |

| 003СЗАн,<br>003СЗВн      | DLCR5                    | DLC register 5                     | R/W            |                | XXXXXXXXB,<br>XXXXXXXB               |

| 003С3Сн,<br>003С3Dн      | DLCR6                    | DLC register 6                     | R/W            | _              | XXXXXXXXB,<br>XXXXXXXB               |

| 003C3Eн,<br>003C3Fн      | DLCR7                    | DLC register 7                     | R/W            |                | XXXXXXXXB,<br>XXXXXXXB               |

| 003C40н<br>to<br>003C47н | DTR0                     | Data register 0                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB         |

| 003C48н<br>to<br>003C4Fн | DTR1                     | Data register 1                    | R/W            | -              | XXXXXXXXB<br>to<br>XXXXXXXXB         |

| 003C50н<br>to<br>003C57н | DTR2                     | Data register 2                    | R/W            | -              | XXXXXXXXB<br>to<br>XXXXXXXXB         |

| 003C58н<br>to<br>003C5Fн | DTR3                     | Data register 3                    | R/W            | -              | XXXXXXXXB<br>to<br>XXXXXXXXB         |

| 003C60н<br>to<br>003C67н | DTR4                     | Data register 4                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB         |

| 003C68н<br>to<br>003C6Fн | DTR5                     | Data register 5                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB         |

| 003C70н<br>to<br>003C77н | DTR6                     | Data register 6                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB         |

| 003C78н<br>to<br>003C7Fн | DTR7                     | Data register 7                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB         |

| 003C80н<br>to<br>003CFFн |                          | (Rese                              | rved area) *   |                |                                      |

| 003D00н,<br>003D01н      | CSR                      | Control status register            | R/W, R         | CAN controller | 0XXXX001в,<br>00XXX000в              |

| 003D02н                  | LEIR                     | Last event display register        | R/W            | 1              | 000XX000 <sub>B</sub>                |

| 003D03н                  |                          | (Rese                              | rved area) *   | •              | - •                                  |

| 003D04н,<br>003D05н      | RTEC                     | Send/receive error counter         | R              | CAN controller | 0000000в,<br>0000000в                |

| 003D06н,<br>003D07н      | BTR                      | Bit timing register                | R/W            |                | 11111111 <sub>в</sub> ,<br>X1111111в |

| 003D08н                  | IDER                     | IDE register                       | R/W            |                | XXXXXXXXB                            |

| 003D09н                  |                          | (Rese                              | rved area) *   | •              | · ·                                  |

| 003D0Aн                  | TRTRR                    | Send RTR register                  | R/W            | CAN controller | 0000000в                             |

| 003D0Bн                  |                          | (Rese                              | rved area) *   | •              |                                      |

| 003D0CH                  | RFWTR                    | Remote frame receive wait register | R/W            | CAN controller | XXXXXXXXB                            |

| Address                  | Register<br>Abbreviation | Register                                      | Read/<br>Write | Resource       | Initial Value                |

|--------------------------|--------------------------|-----------------------------------------------|----------------|----------------|------------------------------|

| 003D0Dн                  |                          | (Reserv                                       | ed area) *     | ·              |                              |

| 003D0Eн                  | TIER                     | Send completion interrupt permission register | R/W            | CAN controller | 00000008                     |

| 003D0Fн                  |                          | (Reserv                                       | ed area) *     |                |                              |

| 003D10н,<br>003D11н      | AMSR                     | Acceptance mask selection register            | R/W            | CAN controller | XXXXXXXXB,<br>XXXXXXXB       |

| 003D12н,<br>003D13н      |                          | (Reserv                                       | ed area) *     | ·              | ·                            |

| 003D14н<br>to<br>003D17н | AMR0                     | Acceptance mask register 0                    | R/W            | CAN controller | XXXXXXXXB<br>to<br>XXXXXXXXB |

| 003D18н<br>to<br>003D1Bн | AMR1                     | Acceptance mask register 1                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB |

| 003D1Cн<br>to<br>003DFFн |                          | (Reserv                                       | ed area) *     |                |                              |

| 003E00н<br>to<br>003EFFн |                          | (Reserv                                       | ed area) *     |                |                              |

| 003FF0н<br>to<br>003FFFн |                          | (Reserv                                       | ed area) *     |                |                              |

Initial values:

0: Initial value of this bit is "0."

1: Initial value of this bit is "1."

X: Initial value of this bit is undefined.

\*: "Reserved area" should not be written anything. Result of reading from "Reserved area" is undefined.

### 11. Interrupt Sources, Interrupt Vectors, And Interrupt Control Registers

| Intervient Courses                                                             | El <sup>2</sup> OS | I      | Interrupt Vector Interrupt Control Register |                     |       |                        | Priority*3   |  |

|--------------------------------------------------------------------------------|--------------------|--------|---------------------------------------------|---------------------|-------|------------------------|--------------|--|

| Interrupt Source                                                               | Readiness          | Number |                                             | Address             | ICR   | Address                |              |  |

| Reset                                                                          | ×                  | #08    | 08н                                         | <b>FFFFDC</b> H     | -     | _                      | High         |  |

| INT 9 instruction                                                              | ×                  | #09    | 09н                                         | FFFFD8H             | -     | _                      | $\uparrow$   |  |

| Exceptional treatment                                                          | ×                  | #10    | 0Ан                                         | FFFFD4H             | -     | _                      |              |  |

| CAN controller reception completed (RX)                                        | ,                  | #11    | 0Вн                                         | FFFFD0H             | ICR00 | 0000B0н*1              |              |  |

| CAN controller transmission<br>completed (TX) / Node status<br>transition (NS) | ,                  | #12    | 0Сн                                         | FFFFCCH             |       |                        |              |  |

| Reserved                                                                       | ×                  | #13    | 0Dн                                         | FFFFC8H             | ICR01 | 0000B1н                |              |  |

| Reserved                                                                       | ×                  | #14    | 0Ен                                         | FFFFC4H             | -     |                        |              |  |

| CAN wakeup                                                                     | Δ                  | #15    | 0 <b>F</b> н                                | FFFFC0H             | ICR02 | 0000B2н*1              |              |  |

| Time-base timer                                                                | ×                  | #16    | 10н                                         | <b>FFFFBC</b> H     | -     |                        |              |  |

| 16-bit reload timer 0                                                          | Δ                  | #17    | 11н                                         | FFFFB8H             | ICR03 | 0000B3н*1              | -            |  |

| 8/10-bit A/D converter                                                         | Δ                  | #18    | 12н                                         | FFFFB4н             | -     |                        |              |  |

| 16-bit free-run timer overflow                                                 | Δ                  | #19    | 13н                                         | FFFFB0H             | ICR04 | 0000B4н*1              |              |  |

| Reserved                                                                       | ×                  | #20    | <b>14</b> н                                 | <b>FFFFAC</b> H     | -     |                        |              |  |

| Reserved                                                                       | ×                  | #21    | 15н                                         | FFFFA8H             | ICR05 | 0000B5н*1              |              |  |

| PPG timer ch0, ch1 underflow                                                   | ,                  | #22    | 16н                                         | FFFFA4H             |       |                        |              |  |

| Input capture 0-input                                                          | Δ                  | #23    | 17н                                         | FFFFA0H             | ICR06 | 0000B6н*1              |              |  |

| External interrupt (INT4/INT5)                                                 | Δ                  | #24    | 18 <sub>H</sub>                             | FFFF9CH             | -     |                        |              |  |

| Input capture 1-input                                                          | Δ                  | #25    | <b>19</b> н                                 | FFFF98⊦             | ICR07 | 0000B7н*2              |              |  |

| PPG timer ch2, ch3 underflow                                                   | ,                  | #26    | <b>1А</b> н                                 | FFFF94⊦             |       |                        |              |  |

| External interrupt (INT6/INT7)                                                 | Δ                  | #27    | 1Bн                                         | FFFF90⊦             | ICR08 | 0000B8н*1              |              |  |

| Watch timer                                                                    | Δ                  | #28    | 1Сн                                         | FFFF8CH             | -     |                        |              |  |

| Reserved                                                                       | ×                  | #29    | 1Dн                                         | FFFF88⊦             | ICR09 | 0000B9н*1              |              |  |

| Input capture 2-input<br>Input capture 3-input                                 | ,                  | #30    | 1Ен                                         | FFFF84 <sub>H</sub> |       |                        |              |  |

| Reserved                                                                       | ×                  | #31    | 1Fн                                         | FFFF80H             | ICR10 | 0000BAH*1              |              |  |

| Reserved                                                                       | ×                  | #32    | 20н                                         | FFFF7CH             | 1     |                        |              |  |

| Reserved                                                                       | ×                  | #33    | 21н                                         | FFFF78н             | ICR11 | 0000BB <sub>H</sub> *1 |              |  |