Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

The following document contains information on Cypress products. Although the document is marked with the name "Spansion" and "Fujitsu", the company that originally developed the specification, Cypress will continue to offer these products to new and existing customers.

#### **Continuity of Specifications**

There is no change to this document as a result of offering the device as a Cypress product. Any changes that have been made are the result of normal document improvements and are noted in the document history page, where supported. Future revisions will occur when appropriate, and changes will be noted in a document history page.

#### **Continuity of Ordering Part Numbers**

Cypress continues to support existing part numbers. To order these products, please use only the Ordering Part Numbers listed in this document.

#### For More Information

Please contact your local sales office for additional information about Cypress products and solutions.

#### **About Cypress**

Cypress (NASDAQ: CY) delivers high-performance, high-quality solutions at the heart of today's most advanced embedded systems, from automotive, industrial and networking platforms to highly interactive consumer and mobile devices. With a broad, differentiated product portfolio that includes NOR flash memories, F-RAM™ and SRAM, Traveo™ microcontrollers, the industry's only PSoC® programmable system-on-chip solutions, analog and PMIC Power Management ICs, CapSense® capacitive touch-sensing controllers, and Wireless BLE Bluetooth® Low-Energy and USB connectivity solutions, Cypress is committed to providing its customers worldwide with consistent innovation, best-in-class support and exceptional system value.

### 16-bit Microcontroller

**CMOS**

## F<sup>2</sup>MC-16LX MB90920 Series

# MB90F922NC/F922NCS/922NCS/F923NC/F923NCS/MB90F924NC/F924NCS/V920-101/V920-102

#### **■ DESCRIPTION**

The MB90920 series is a family of general-purpose FUJITSU SEMICONDUCTOR 16-bit microcontrollers designed for applications such as vehicle instrument panel control.

The instruction set retains the AT architecture from the F<sup>2</sup>MC-8L and F<sup>2</sup>MC-16LX families, with further refinements including high-level language instructions, extended addressing modes, improved multiplication and division operations (signed), and bit processing. In addition, long word processing is made possible by the inclusion of a built-in 32-bit accumulator.

Note: F<sup>2</sup>MC is the abbreviation of FUJITSU Flexible Microcontroller.

#### **■ FEATURES**

Clock

Built-in PLL clock frequency multiplication circuit.

Selection of machine clocks (PLL clocks) is allowed among frequency division by two on oscillation clock, and multiplication of 1 to 8 times of oscillation clock (for 4 MHz oscillation clock, 4 MHz to 32 MHz).

Operation by sub clock (up to 50 kHz : 100 kHz oscillation clock divided by two) is allowed.

• 16-bit input capture (8 channels)

Detects rising, falling, or both edges.

16-bit capture register  $\times$  8

The value of a 16-bit free-run timer counter is latched upon detection of an edge input to pin and an interrupt request is generated.

(Continued)

For the information for microcontroller supports, see the following web site.

This web site includes the "Customer Design Review Supplement" which provides the latest cautions on system development and the minimal requirements to be checked to prevent problems before the system development.

http://edevice.fujitsu.com/micom/en-support/

#### (Continued)

• 16-bit reload timer (4 channels)

16-bit reload timer operation (select toggle output or one-shot output)

Selectable event count function

• Real time watch timer (main clock)

Operates directly from oscillator clock.

Interrupt can be generated by second/minute/hour/date counter overflow.

• PPG timer (6 channels)

Output pins (3 channels), external trigger input pin (1 channel)

Operation clock frequencies: fcp, fcp/22, fcp/24, fcp/26

Delay interrupt

Generates interrupt for task switching.

Interrupts to CPU can be generated/cleared by software setting.

• External interrupts (8 channels)

8-channel independent operation

Interrupt source setting available: "L" to "H" edge/ "H" to "L" edge/ "L" level/ "H" level.

• 8/10-bit A/D converter (8 channels)

Conversion time :  $3 \mu s$  (at  $f_{CP} = 32 \text{ MHz}$ )

External trigger activation available (P50/INT0/ADTG)

Internal timer activation available (16-bit reload timer 1)

• UART(LIN/SCI) (4 channels)

Equipped with full duplex double buffer

Clock-asynchronous or clock-synchronous serial transfer is available

• CAN interface (4 channels: CAN0 and CAN2, and CAN1 and CAN3 share transmission and reception pins, and interrupt control registers).

Conforms to CAN specifications version 2.0 Part A and B.

Automatic resend in case of error.

Automatic transfer in response to remote frame.

16 prioritized message buffers for data and ID

Multiple message support

Flexible configuration for receive filter: Full bit compare/full bit mask/two partial bit masks

Supports up to 1 Mbps

CAN wakeup function (RX connected to INT0 internally)

• LCD controller/driver (32 segment x 4 common)

Segment driver and command driver with direct LCD panel (display) drive capability

Reset on detection of low voltage/program loop

Automatic reset when low voltage is detected

Program looping detection function

Stepping motor controller (4 channels)

High current output for each channel × 4

Synchronized 8/10-bit PWM for each channel × 2

• Sound generator (2 channels)

8-bit PWM signal mixed with tone frequency from 8-bit reload counter.

PWM frequencies: 125 kHz, 62.5 kHz, 31.2 kHz, 15.6 kHz (at fcp = 32 MHz)

Tone frequencies: PWM frequency /2/, divided by (reload frequency +1)

· Input/output ports

General-purpose input/output port (CMOS output) 93 ports

• Function for port input level selection

Automotive/CMOS-Schmitt

• Flash memory security function

Protects the contents of Flash memory (Flash memory product only)

### **■ PRODUCT LINEUP**

| Part number                                      | MB90           | MB90                             | MB90     | MB90                             | MB90              | MB90             | MB90           | MB90     | MB90               |  |

|--------------------------------------------------|----------------|----------------------------------|----------|----------------------------------|-------------------|------------------|----------------|----------|--------------------|--|

| Parameter                                        | F922NC         | F922NCS                          | F923NC   | F923NCS                          | F924NC            | F924NCS          | 922NCS         | V920-101 | V920-102           |  |

| Туре                                             |                | Flash memory product ROM product |          |                                  |                   |                  |                |          | Evaluation product |  |

| CPU                                              |                |                                  |          | F <sup>2</sup> M                 | IC-16LX C         | PU               |                |          |                    |  |

| System clock                                     |                |                                  | •        | rcuit ( $\times$ 1, ecution time |                   |                  |                |          | ,                  |  |

| Sub clock pins (X0A, X1A)                        | Yes            | No                               | Yes      | No                               | Yes               | No               | No             | No       | Yes                |  |

| ROM                                              |                | nemory<br>Kbytes                 |          | memory<br>Kbytes                 |                   | memory<br>Kbytes | 256 K<br>bytes | Exte     | ernal              |  |

| RAM                                              | 10 K           | bytes                            | 16 K     | bytes                            | 24 K              | bytes            | 10 K<br>bytes  | 30 K     | bytes              |  |

| I/O port                                         | 91 ports       | 93 ports                         | 91 ports | 93 ports                         | 91 ports          | 93 ports         | 93 ports       | 93 ports | 91 ports           |  |

| LCD controller                                   |                |                                  |          | 32 segr                          | $nent \times 4 c$ | ommon            |                |          |                    |  |

| LIN-UART                                         |                |                                  |          | UART (LI                         | N/SCI) 4          | channels         |                |          |                    |  |

| CAN interface                                    |                | 4 channels                       |          |                                  |                   |                  |                |          |                    |  |

| 16-bit input capture                             | 8 channels     |                                  |          |                                  |                   |                  |                |          |                    |  |

| 16-bit reload timer                              | 4 channels     |                                  |          |                                  |                   |                  |                |          |                    |  |

| 16-bit free-run<br>timer                         | 1 channel      |                                  |          |                                  |                   |                  |                |          |                    |  |

| Real time watch timer                            | 1 channel      |                                  |          |                                  |                   |                  |                |          |                    |  |

| 16-bit PPG timer                                 |                |                                  |          | (                                | 6 channels        | 3                |                |          |                    |  |

| External interrupt                               |                |                                  |          | 8                                | 3 channels        | 6                |                |          |                    |  |

| 8/10-bit<br>A/D converter                        |                |                                  |          | 8                                | 3 channels        | 6                |                |          |                    |  |

| Low-voltage/<br>CPU operating<br>detection reset | Yes No         |                                  |          |                                  |                   |                  |                |          |                    |  |

| Stepping motor controller                        | 4 channels     |                                  |          |                                  |                   |                  |                |          |                    |  |

| Sound generator                                  |                |                                  |          | 2                                | 2 channels        | S                |                |          |                    |  |

| Flash memory security                            | Yes —          |                                  |          |                                  |                   |                  |                |          |                    |  |

| Operating voltage                                | 4.0 V to 5.5 V |                                  |          |                                  |                   |                  | 4.5 V t        | o 5.5 V  |                    |  |

| Package                                          |                | LQFP-120 PGA-299                 |          |                                  |                   |                  |                |          |                    |  |

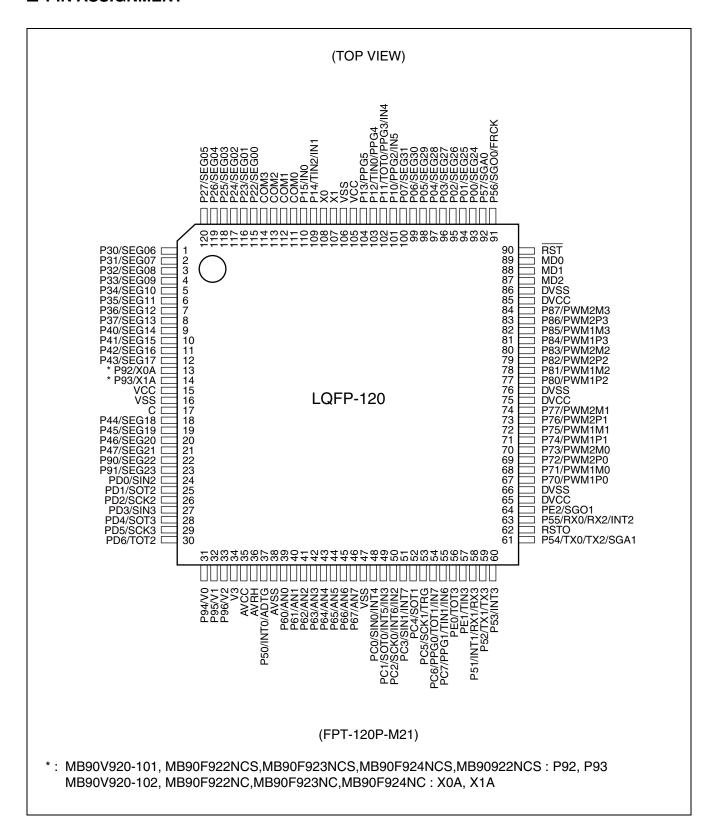

#### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTIONS**

| Pin no. | Pin name | I/O circuit<br>type*1 | Function                                 |  |

|---------|----------|-----------------------|------------------------------------------|--|

| 108     | X0       | Λ                     | High-speed oscillation input pin         |  |

| 107     | X1       | A                     | High-speed oscillation output pin        |  |

| 10      | X0A      | В                     | Low-speed oscillation input pin          |  |

| 13      | P92      | I                     | General-purpose I/O port                 |  |

| 14      | X1A      | В                     | Low-speed oscillation output pin         |  |

| 14      | P93      | I                     | General-purpose I/O port                 |  |

| 90      | RST      | С                     | Reset input pin                          |  |

| 93      | P00      | F                     | General-purpose I/O port                 |  |

| 93      | SEG24    | <del>-</del> Г        | LCD controller/driver segment output pin |  |

| 94      | P01      | F                     | General-purpose I/O port                 |  |

| 94      | SEG25    | <del>-</del> Г        | LCD controller/driver segment output pin |  |

| 95 -    | P02      | Е                     | General-purpose I/O port                 |  |

| 95      | SEG26    | F                     | LCD controller/driver segment output pin |  |

| 96 -    | P03      | - F                   | General-purpose I/O port                 |  |

| 90      | SEG27    |                       | LCD controller/driver segment output pin |  |

| 97 -    | P04      | F                     | General-purpose I/O port                 |  |

| 97      | SEG28    | -<br>-                | LCD controller/driver segment output pin |  |

| 98 -    | P05      | - F                   | General-purpose I/O port                 |  |

| 90      | SEG29    |                       | LCD controller/driver segment output pin |  |

| 99 -    | P06      | F                     | General-purpose I/O port                 |  |

| 99      | SEG30    |                       | LCD controller/driver segment output pin |  |

| 100     | P07      | F                     | General-purpose I/O port                 |  |

| 100     | SEG31    |                       | LCD controller/driver segment output pin |  |

|         | P10      |                       | General-purpose I/O port                 |  |

| 101     | PPG2     | I                     | 16-bit PPG ch.2 output pin               |  |

|         | IN5      |                       | Input capture ch.5 trigger input pin     |  |

|         | P11      |                       | General-purpose I/O port                 |  |

| 102     | TOT0     |                       | 16-bit reload timer ch.0 TOT output pin  |  |

| 102     | PPG3     | _ '                   | 16-bit PPG ch.3 output pin               |  |

|         | IN4      |                       | Input capture ch.4 trigger input pin     |  |

|         | P12      |                       | General-purpose I/O port                 |  |

| 103     | TIN0     | ı                     | 16-bit reload timer ch.0 TIN input pin   |  |

|         | PPG4     |                       | 16-bit PPG ch.4 output pin               |  |

| Pin no.   | Pin name | I/O circuit<br>type*1 | Function                                 |

|-----------|----------|-----------------------|------------------------------------------|

| 101       | P13      | ,                     | General-purpose I/O port                 |

| 104       | PPG5     | - I                   | 16-bit PPG ch.5 output pin               |

|           | P14      |                       | General-purpose I/O port                 |

| 109       | TIN2     | I                     | 16-bit reload timer ch.2 TIN input pin   |

|           | IN1      |                       | Input capture ch.1 trigger input pin     |

| 110       | P15      |                       | General-purpose I/O port                 |

| 110       | IN0      | - I                   | Input capture ch.0 trigger input pin     |

| 111       | COM0     | Р                     | LCD controller/driver common output pin  |

| 112       | COM1     | Р                     | LCD controller/driver common output pin  |

| 113       | COM2     | Р                     | LCD controller/driver common output pin  |

| 114       | COM3     | Р                     | LCD controller/driver common output pin  |

| 445       | P22      | _                     | General-purpose I/O port                 |

| 115       | SEG00    | - F                   | LCD controller/driver segment output pin |

| 110       | P23      | _                     | General-purpose I/O port                 |

| 116 SEG01 |          | F                     | LCD controller/driver segment output pin |

| 117       | P24      | - F                   | General-purpose I/O port                 |

| 117       | SEG02    |                       | LCD controller/driver segment output pin |

| 110       | P25      | F                     | General-purpose I/O port                 |

| 118       | SEG03    |                       | LCD controller/driver segment output pin |

| 110       | P26      | F                     | General-purpose I/O port                 |

| 119       | SEG04    |                       | LCD controller/driver segment output pin |

| 100       | P27 _    | F                     | General-purpose I/O port                 |

| 120       | SEG05    |                       | LCD controller/driver segment output pin |

| 4         | P30      | _                     | General-purpose I/O port                 |

| 1         | SEG06    | F                     | LCD controller/driver segment output pin |

| 2         | P31      | F                     | General-purpose I/O port                 |

| 2         | SEG07    | = r                   | LCD controller/driver segment output pin |

| 0         | P32      | _                     | General-purpose I/O port                 |

| 3         | SEG08    | F                     | LCD controller/driver segment output pin |

| 4         | P33      | _                     | General-purpose I/O port                 |

| 4         | SEG09    | F                     | LCD controller/driver segment output pin |

| E         | P34      | F                     | General-purpose I/O port                 |

| 5         | SEG10    |                       | LCD controller/driver segment output pin |

| 6         | P35      | F                     | General-purpose I/O port                 |

| Ö         | SEG11    | F                     | LCD controller/driver segment output pin |

| Pin no. | Pin name | I/O circuit<br>type*1 | Function                                 |

|---------|----------|-----------------------|------------------------------------------|

| 7       | P36      | F                     | General-purpose I/O port                 |

| 7       | SEG12    | - F                   | LCD controller/driver segment output pin |

|         | P37      | _                     | General-purpose I/O port                 |

| 8       | SEG13    | - F                   | LCD controller/driver segment output pin |

| 0       | P40      | F                     | General-purpose I/O port                 |

| 9       | SEG14    | - F                   | LCD controller/driver segment output pin |

| 10      | P41      | F                     | General-purpose I/O port                 |

| 10      | SEG15    | - F                   | LCD controller/driver segment output pin |

| 11      | P42      | - F                   | General-purpose I/O port                 |

|         | SEG16    | <del>-</del> Г        | LCD controller/driver segment output pin |

| 12      | P43      | - F                   | General-purpose I/O port                 |

| 12      | SEG17    | <del>-</del> Г        | LCD controller/driver segment output pin |

| 18      | P44      | F                     | General-purpose I/O port                 |

| 10      | SEG18    | <del>-</del> Г        | LCD controller/driver segment output pin |

| 19      | P45      | - F                   | General-purpose I/O port                 |

| 19      | SEG19    |                       | LCD controller/driver segment output pin |

| 20      | P46      | F                     | General-purpose I/O port                 |

| 20      | SEG20    |                       | LCD controller/driver segment output pin |

| 21      | P47      | F                     | General-purpose I/O port                 |

| 21      | SEG21    |                       | LCD controller/driver segment output pin |

|         | P50      |                       | General-purpose I/O port                 |

| 37      | INT0     | I                     | INT0 external interrupt input pin        |

|         | ADTG     |                       | A/D converter external trigger input pin |

|         | P51      |                       | General-purpose I/O port                 |

| 58      | INT1     |                       | INT1 external interrupt input pin        |

| 30      | RX1      | _                     | CAN interface 1 RX input pin             |

|         | RX3      |                       | CAN interface 3 RX input pin             |

|         | P52      |                       | General-purpose I/O port                 |

| 59      | TX1      | I                     | CAN interface 1 TX output pin            |

|         | TX3      |                       | CAN interface 3 TX output pin            |

| 60      | P53      |                       | General-purpose I/O port                 |

| 00      | INT3     | '                     | INT3 external interrupt input pin        |

| Pin no. | Pin name | I/O circuit<br>type*1 | Function                                  |

|---------|----------|-----------------------|-------------------------------------------|

|         | P54      |                       | General-purpose I/O port                  |

| 61      | TX0      | 1 .                   | CAN interface 0 TX output pin             |

| 61      | TX2      |                       | CAN interface 2 TX output pin             |

|         | SGA1     |                       | Sound generator ch.1 SGA output pin       |

|         | P55      |                       | General-purpose I/O port                  |

| 60      | RX0      | 1 .                   | CAN interface 0 RX input pin              |

| 63      | RX2      |                       | CAN interface 2 RX input pin              |

|         | INT2     |                       | INT2 external interrupt input pin         |

|         | P56      |                       | General-purpose I/O port                  |

| 91      | SGO0     | I                     | Sound generator ch.0 SGO output pin       |

|         | FRCK     |                       | Free-run timer clock input pin            |

| 00      | P57      |                       | General-purpose I/O port                  |

| 92      | SGA0     |                       | Sound generator ch.0 SGA output pin       |

| 20      | P60      | 11                    | General-purpose I/O port                  |

| 39      | AN0      | - H                   | A/D converter input pin                   |

| 40      | P61      | - н                   | General-purpose I/O port                  |

| 40      | AN1      |                       | A/D converter input pin                   |

| 41      | P62      | - Н                   | General-purpose I/O port                  |

| 41      | AN2      | <b></b>               | A/D converter input pin                   |

| 42      | P63      | - Н                   | General-purpose I/O port                  |

| 42      | AN3      | <b></b>               | A/D converter input pin                   |

| 40      | P64      | - Н                   | General-purpose I/O port                  |

| 43      | AN4      | - n                   | A/D converter input pin                   |

| 4.4     | P65      | 11                    | General-purpose I/O port                  |

| 44      | AN5      | - H                   | A/D converter input pin                   |

| 45      | P66      | Ш                     | General-purpose I/O port                  |

| 45      | AN6      | - H                   | A/D converter input pin                   |

| 46      | P67      | ы                     | General-purpose I/O port                  |

| 46      | AN7      | - H                   | A/D converter input pin                   |

| 67      | P70      |                       | General-purpose output-only port          |

| 67      | PWM1P0   | - L                   | Stepping motor controller ch.0 output pin |

| 60      | P71      |                       | General-purpose output-only port          |

| 68 –    | PWM1M0   | - L                   | Stepping motor controller ch.0 output pin |

| 60      | P72      | 1                     | General-purpose output-only port          |

| 69      | PWM2P0   | - L                   | Stepping motor controller ch.0 output pin |

| Pin no. | Pin name | I/O circuit<br>type*1 | Function                                         |

|---------|----------|-----------------------|--------------------------------------------------|

| 70 –    | P73      | L                     | General-purpose output-only port                 |

| 70      | PWM2M0   |                       | Stepping motor controller ch.0 output pin        |

| 74      | P74      |                       | General-purpose output-only port                 |

| 71      | PWM1P1   | -  L                  | Stepping motor controller ch.1 output pin        |

| 70      | P75      |                       | General-purpose output-only port                 |

| 72 –    | PWM1M1   | - L                   | Stepping motor controller ch.1 output pin        |

| 70      | P76      |                       | General-purpose output-only port                 |

| 73      | PWM2P1   | -  L                  | Stepping motor controller ch.1 output pin        |

| 74      | P77      |                       | General-purpose output-only port                 |

| 74 –    | PWM2M1   | - L                   | Stepping motor controller ch.1 output pin        |

| 77      | P80      |                       | General-purpose output-only port                 |

| 77      | PWM1P2   | - L                   | Stepping motor controller ch.2 output pin        |

| 70      | P81      | 1                     | General-purpose output-only port                 |

| 78 –    | PWM1M2   | - L                   | Stepping motor controller ch.2 output pin        |

| 79 –    | P82      | - L                   | General-purpose output-only port                 |

| 79      | PWM2P2   |                       | Stepping motor controller ch.2 output pin        |

| 80 -    | P83      |                       | General-purpose output-only port                 |

| 80      | PWM2M2   | - L                   | Stepping motor controller ch.2 output pin        |

| 81 –    | P84      | L                     | General-purpose output-only port                 |

| 01      | PWM1P3   | <u>_</u>              | Stepping motor controller ch.3 output pin        |

| 82 –    | P85      | L                     | General-purpose output-only port                 |

| 02      | PWM1M3   |                       | Stepping motor controller ch.3 output pin        |

| 83 –    | P86      |                       | General-purpose output-only port                 |

| 83      | PWM2P3   | - L                   | Stepping motor controller ch.3 output pin        |

| 84 –    | P87      |                       | General-purpose output-only port                 |

| 04      | PWM2M3   | - L                   | Stepping motor controller ch.3 output pin        |

| 00      | P90      | F                     | General-purpose I/O port                         |

| 22      | SEG22    |                       | LCD controller/driver segment output pin         |

| 00      | P91      | F                     | General-purpose I/O port                         |

| 23      | SEG23    |                       | LCD controller/driver segment output pin         |

| 21      | P94      | G                     | General-purpose I/O port                         |

| 31      | V0       | G                     | LCD controller/driver reference power supply pin |

| 20      | P95      |                       | General-purpose I/O port                         |

| 32      | V1       | G                     | LCD controller/driver reference power supply pin |

| Pin no. | Pin name | I/O circuit<br>type*1 | Function                                           |  |

|---------|----------|-----------------------|----------------------------------------------------|--|

| 00      | P96      | 0                     | General-purpose I/O port                           |  |

| 33      | V2       | G                     | LCD controller/driver reference power supply pin   |  |

| 34      | V3       | _                     | LCD controller/driver reference power supply pin   |  |

|         | PC0      |                       | General-purpose I/O port                           |  |

| 48      | SIN0     | J                     | UART ch.0 serial data input pin                    |  |

|         | INT4     | 1                     | INT4 external interrupt input pin                  |  |

|         | PC1      |                       | General-purpose I/O port                           |  |

| 40      | SOT0     | 1 .                   | UART ch.0 serial data output pin                   |  |

| 49      | INT5     | - I                   | INT5 external interrupt input pin                  |  |

|         | IN3      |                       | Input capture ch.3 trigger input pin               |  |

|         | PC2      |                       | General-purpose I/O port                           |  |

| 50      | SCK0     | 1 .                   | UART ch.0 serial clock I/O pin                     |  |

| 50      | INT6     | - I                   | INT6 external interrupt input pin                  |  |

|         | IN2      |                       | Input capture ch.2 trigger input pin               |  |

|         | PC3      | J                     | General-purpose I/O port                           |  |

| 51      | SIN1     |                       | UART ch.1 serial data input pin                    |  |

|         | INT7     |                       | INT7 external interrupt input pin                  |  |

| 52      | PC4      | ı                     | General-purpose I/O port                           |  |

| 52      | SOT1     | -<br>                 | UART ch.1 serial data output pin                   |  |

|         | PC5      |                       | General-purpose I/O port                           |  |

| 53      | SCK1     | -<br>                 | UART ch.1 serial clock I/O pin                     |  |

|         | TRG      |                       | 16-bit PPG ch.0 to ch.5 external trigger input pin |  |

|         | PC6      |                       | General-purpose I/O port                           |  |

| 54      | PPG0     | ]<br>  I              | 16-bit PPG ch.0 output pin                         |  |

| 54      | TOT1     | ] '                   | 16-bit reload timer ch.1 TOT output pin            |  |

|         | IN7      | 1                     | Input capture ch.7 trigger input pin               |  |

|         | PC7      |                       | General-purpose I/O port                           |  |

| 55      | PPG1     | ]                     | 16-bit PPG ch.1 output pin                         |  |

| 55      | TIN1     |                       | 16-bit reload timer ch.1 TIN input pin             |  |

|         | IN6      |                       | Input capture ch.6 trigger input pin               |  |

| 24      | PD0      | 1                     | General-purpose I/O port                           |  |

| 24      | SIN2     | J                     | UART ch.2 serial data input pin                    |  |

| 25      | PD1      | ı                     | General-purpose I/O port                           |  |

| 20      | SOT2     | ] '                   | UART ch.2 serial data output pin                   |  |

| Pin no.     | Pin name | I/O circuit<br>type*1 | Function                                                                                  |  |

|-------------|----------|-----------------------|-------------------------------------------------------------------------------------------|--|

| 00          | PD2      | ,                     | General-purpose I/O port                                                                  |  |

| 26          | SCK2     | '                     | UART ch.2 serial clock I/O pin                                                            |  |

| 27          | PD3      |                       | General-purpose I/O port                                                                  |  |

| 21          | SIN3     | - J                   | UART ch.3 serial data input pin                                                           |  |

| 28          | PD4      |                       | General-purpose I/O port                                                                  |  |

| 20          | SOT3     | -<br>                 | UART ch.3 serial data output pin                                                          |  |

| 20          | PD5      |                       | General-purpose I/O port                                                                  |  |

| 29          | SCK3     | · '                   | UART ch.3 serial clock I/O pin                                                            |  |

| 30          | PD6      |                       | General-purpose I/O port                                                                  |  |

| 30          | TOT2     | · '                   | 16-bit reload timer ch.2 TOT output pin                                                   |  |

| 56          | PE0      |                       | General-purpose I/O port                                                                  |  |

| 30          | ТОТ3     | · !                   | 16-bit reload timer ch.3 TOT output pin                                                   |  |

| 57          | PE1      |                       | General-purpose I/O port                                                                  |  |

| 5/          | TIN3     | - !<br>               | 16-bit reload timer ch.3 TIN input pin                                                    |  |

| 64          | PE2      |                       | General-purpose I/O port                                                                  |  |

| SGO1        |          | 1                     | Sound generator ch.1 SGO output pin                                                       |  |

| 62          | RSTO     | N                     | Internal reset signal output pin                                                          |  |

| 65, 75, 85  | DVCC     | _                     | Power supply input pins dedicated for high current output buffer                          |  |

| 66, 76, 86  | DVSS     | _                     | Power supply GND pins dedicated for high current output buffer                            |  |

| 35          | AVCC     | _                     | A/D converter dedicated power supply input pin                                            |  |

| 38          | AVSS     | _                     | A/D converter dedicated power supply GND pin                                              |  |

| 36          | AVRH     | _                     | A/D converter Vref+ input pin. Vref- is fixed to AVSS.                                    |  |

| 89          | MD0      | D                     | Mode setting input pin. Connect to VCC pin.                                               |  |

| 88          | MD1      | D                     | Mode setting input pin. Connect to VCC pin.                                               |  |

| 87          | MD2      | D/E*2                 | Mode setting input pin. Connect to VSS pin.                                               |  |

| 17          | С        | _                     | External capacitor pin. Connect a 0.1 $\mu$ F capacitor between this pin and the VSS pin. |  |

| 15, 105     | VCC      | _                     | Power supply input pins                                                                   |  |

| 16, 47, 106 | VSS      | _                     | GND power supply pins                                                                     |  |

<sup>\*1 :</sup> For I/O circuit type, refer to "■ I/O CIRCUIT TYPES".

<sup>\*2 :</sup> The I/O circuit type is D for Flash memory products and E for evaluation products.

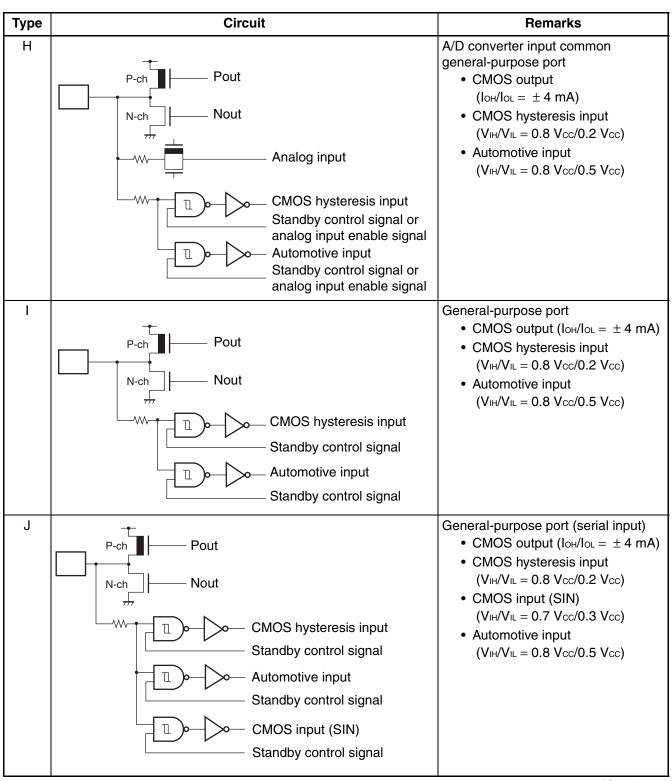

### ■ I/O CIRCUIT TYPE

| Туре | Circuit                                 | Remarks                                                                                                                                                          |

|------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A    | X1 Xout  Standby control signal         | Oscillation circuit High-speed oscillation feedback resistance: approx. 1 MΩ (Flash memory product/MASK ROM product/Evaluation product)                          |

| В    | X1A Xout  X0A Standby control signal    | Oscillation circuit Low-speed oscillation feedback resistance : approx. 10 MΩ                                                                                    |

| С    | Pull-up resistor  CMOS hysteresis input | Input-only pin (with pull-up resistance) • Attached pull-up resistor: approx. 50 kΩ • CMOS hysteresis input (V <sub>IH</sub> /V <sub>IL</sub> = 0.8 Vcc/0.2 Vcc) |

| D    | CMOS hysteresis input                   | Input-only pin  • CMOS hysteresis input (V⊩/V L = 0.8 Vcc/0.2 Vcc)  Note: The MD2 pin of the Flash memory products uses this circuit type.                       |

| Туре | Circuit                                                                                                                                                                               | Remarks                                                                                                                                                                                 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E    | CMOS hysteresis input                                                                                                                                                                 | Input-only pin (with pull-down resistance)  • Attached pull-down resistance: approx. 50 kΩ  • CMOS hysteresis input (ViH/ViL = 0.8 Vcc/0.2 Vcc)                                         |

|      | <del>///</del>                                                                                                                                                                        | Note: The MD2 pin of the evaluation products uses this circuit type.                                                                                                                    |

| F    | P-ch Nout  Nout  CMOS hysteresis input Standby control signal or LCD input enable signal Automotive input Standby control signal or LCD input enable signal                           | LCD output common general- purpose port  CMOS output (IoH/IoL = ± 4 mA)  Hysteresis input (VIH/VIL = 0.8 Vcc/0.2 Vcc)  Automotive input (VIH/VIL = 0.8 Vcc/0.5 Vcc)                     |

| G    | LCDC reference power supply input  CMOS hysteresis input Standby control signal or LCD output switching signal Automotive input Standby control signal or LCD output switching signal | LCDC reference power supply common general-purpose port  CMOS output (IoH/IoL = ±4 mA)  CMOS hysteresis input (VIH/VIL = 0.8 Vcc/0.2 Vcc)  Automotive input (VIH/VIL = 0.8 Vcc/0.5 Vcc) |

| Туре | Circuit                                                                                                                                                                                                                                                                                                       | Remarks                                                                                                                                                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K    | Analog output  CMOS hysteresis input Standby control signal or analog input enable signal                                 | A/D converter input common general-purpose port (serial input)  • CMOS output (IoH/IoL = ± 4 mA)  • CMOS hysteresis input (VIH/VIL = 0.8 Vcc/0.2 Vcc)  • CMOS input (SIN) (VIH/VIL = 0.7 Vcc/0.3 Vcc)  • Automotive input (VIH/VIL = 0.8 Vcc/0.5 Vcc) |

| L    | P-ch Pout High current N-ch Nout                                                                                                                                                                                                                                                                              | High current output port (SMC pin) CMOS output (IoH/IoL = ± 30 mA)                                                                                                                                                                                    |

| М    | Pout  CMOS hysteresis input Standby control signal or LCDC output switching signal  Automotive input Standby control signal or LCDC output switching signal  CMOS input (SIN) Standby control signal or LCDC output switching signal  CMOS input (SIN) Standby control signal or LCDC output switching signal | LCDC output common general- purpose port (serial input) )  • CMOS output (IoH/IoL = ± 4 mA)  • CMOS hysteresis input (VIH/VIL = 0.8 Vcc/0.2 Vcc)  • CMOS input (SIN) (VIH/VIL = 0.7 Vcc/0.3 Vcc)  • Automotive input (VIH/VIL = 0.8 Vcc/0.5 Vcc)      |

| Туре | Circuit                                 | Remarks                                                     |

|------|-----------------------------------------|-------------------------------------------------------------|

| N    | Evaluation product Flash memory product | N-ch open-drain pin IoL = 4 mA                              |

|      | N-ch Nout N-ch Nout                     |                                                             |

| 0    | Automotive input                        | Input-only pin Automotive input (VIH/VIL = 0.8 Vcc/0.5 Vcc) |

| Р    | LCDC output                             | LCDC output pin (COM pin)                                   |

#### **■ HANDLING DEVICES**

#### Strictly observe maximum rated voltages (preventing latch-up)

In CMOS IC devices, a condition known as latch-up may occur if voltages higher than Vcc or lower than Vss are applied to input or output pins other than medium or high withstand voltage pins, or if the voltage applied between VCC and VSS pins exceeds the rated voltage level. If a latch-up occurs, the power supply current may increase dramatically and may destroy semiconductor elements. When using semiconductor devices, always take sufficient care to avoid exceeding maximum ratings.

When the analog system power supply is switched on or off, be careful not to apply the analog power supply (AVcc, AVRH), the analog input voltages and the power supply voltage for the high current output buffer pins (DVcc) in excess of the digital power supply voltage (Vcc).

Once the digital power supply voltage (Vcc) has been disconnected, the analog power supply (AVcc, AVRH) and the power supply voltage for the high current output buffer pins (DVcc) may be turned on in any sequence.

#### Supply voltage stabilization

Rapid fluctuations in the power supply voltage can cause malfunctions even if the Vcc power supply voltage remains within the warranted operating range. It is recommended that the power supply be stabilized such that ripple fluctuations (P-P value) at commercial frequencies (50 Hz/60 Hz) be limited to within 10% of the standard Vcc value, and that transient fluctuations due to power supply switching, etc. be limited to a rate of 0.1 V/ms or less.

#### • Precautions when turning the power on

In order to prevent the built-in step-down circuits from malfunctioning, the time taken for the voltage to rise (0.2 V to 2.7 V) during power-on should be less than 50  $\mu$ s.

#### · Handling unused pins

If unused input pins are left open, they may cause malfunctions or latch-up which may lead to permanent damage to the semiconductor. Unused input pins should therefore be pulled up or pulled down through a resistor of at least  $2 \text{ k}\Omega$ .

Unused input/output pins may be set to the output state and left open, or set to the input state and connected to a pull-up or pull-down resistance of 2  $k\Omega$  or more.

#### • Handling A/D converter power supply pins

Even if the A/D converter is not used, the power supply pins should be connected such as  $AV_{CC} = V_{CC}$ , and  $AV_{SS} = AVRH = V_{SS}$ .

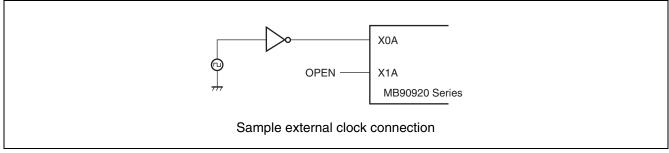

#### · Notes on using an external clock

Even when an external clock is used, an oscillation stabilization wait time is required following power-on reset or release from sub clock mode or stop mode. Furthermore, only the X0A pin should be driven when an external clock is used, with the X1A pin open as shown in the following diagram. Do not use high-speed oscillation pins (X0 and X1) for external clock input.

#### Notes on operating in PLL clock mode

On this microcontroller, if in case the crystal oscillator breaks off or an external reference clock input stops while the PLL clock mode is selected, a self-oscillator circuit contained in the PLL may continue its operation at its self-running frequency. However, FUJITSU SEMICONDUCTOR will not guarantee results of operations if such failure occurs.

#### Crystal oscillator circuit

Noise around the X0/X1, or X0A/X1A pins may cause this device to operate abnormally. In the interest of stable operation it is strongly recommended that printed circuit artwork places ground bypass capacitors as close as possible to the X0/X1, X0A/X1A and crystal oscillator (or ceramic oscillator) and that oscillator lines do not cross the lines of other circuits.

Please ask each crystal maker to evaluate the oscillational characteristics of the crystal and this device.

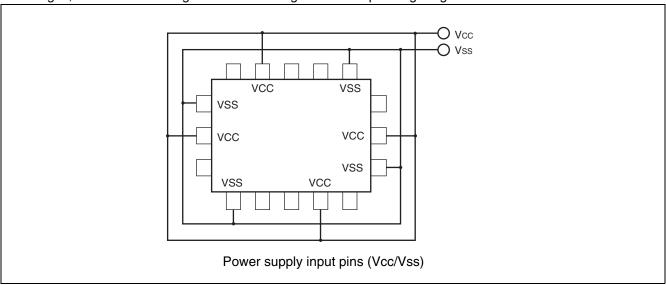

#### · Power supply pins

Devices including multiple VCC or VSS pins are designed such that pins that need to be at the same potential are interconnected internally to prevent malfunctions such as latch-up. To reduce unnecessary radiation, prevent malfunctioning of the strobe signal due to the rise of ground level, and observe the standard for total output current, be sure to connect the VCC and VSS pins to the power supply and ground externally.

Always connect all of the VCC pins to the same potential and all of the VSS pins to ground as shown in the following diagram. The device will not operate correctly if multiple VCC or VSS pins are connected to different voltages, even if those voltages are within the guaranteed operating ranges.

In addition, care must be given to connecting the VCC and VSS pins of this device to the current supply source with as low impedance as possible. It is recommended that a 1.0  $\mu$ F bypass capacitor be connected between the VCC and VSS pins as close to the pins as possible.

#### Sequence for connecting the A/D converter power supply and analog inputs

The A/D converter power supply (AVcc, AVRH) and analog inputs (AN0 to AN7) must be applied after the digital power supply (Vcc) is switched on. When turning the power off, the A/D converter power supply and analog inputs must be disconnected before the digital power supply is switched off (Vcc). Ensure that AVRH does not exceed AVcc during either power-on or power-off. Even when pins which double as analog input pins are used as input ports, be sure that the input voltage does not exceed AVcc (turning on/off the analog and digital power supplies simultaneously is acceptable).

#### Handling the power supply for high-current output buffer pins (DVcc, DVss)

## Flash memory products and MASK ROM products (MB90F922NC/F922NCS/922NCS/F923NC/F923NCS/F924NC/F924NCS)

In the Flash memory products and MASK ROM products, the power supply for the high-current output buffer pins (DVcc, DVss) is isolated from the digital power supply (Vcc).

Therefore, DVcc can therefore be set to a higher voltage than Vcc. If the power supply for the high-current output buffer pins (DVcc, DVss) is supplied before the digital power supply (Vcc), however, care needs to be taken because it is possible that the port 7 or port 8 stepping motor outputs may momentarily output an "H" or "L" level. In order to prevent this, connect the digital power supply (Vcc) prior to connecting the power supply for the high-current output buffer pins. Even when the high-current output buffer pins are used as general-purpose ports, power should be supplied to the power supply pins for the high-current output buffer pins (DVcc, DVss).

#### Evaluation product (MB90V920-101/MB90V920-102)

In the evaluation products, the power supply for the high-current output buffer pins (DVcc, DVss) is not isolated from the digital power supply (Vcc). Therefore, DVcc must therefore be set to a lower voltage than Vcc. The power supply for the high-current output buffer pins (DVcc, DVss) must always be applied after the digital power supply (Vcc) has been connected, and disconnected before the digital power supply (Vcc) is disconnected (the power supply for the high-current output buffer pins may also be connected and disconnected simultaneously with the digital power supply).

Even when the high-current output buffer pins are used as general-purpose ports, power should be supplied to the power supply pins for the high-current output buffer pins (DVcc, DVss).

#### • Pull-up/pull-down resistors

MB90920 series does not support internal pull-up/pull-down resistors. Use external components as necessary.

#### Precautions when not using a sub clock signal

If the X0A and X1A pins are not connected to an oscillator, apply a pull-down resistance to the X0A pin and leave the X1A pin open.

#### · Notes on operating when the external clock is stopped

The MB90920 series is not guaranteed to operate correctly using the internal oscillator circuit when there is no external oscillator or the external clock input is stopped.

#### Flash memory security function

A security bit is located within the Flash memory region. The security function is activated by writing the protection code 01<sub>H</sub> to the security bit.

Do not write the value 01H to this address if you are not using the security function.

Please refer to following table for the address of the security bit.

|                           | Flash memory size             | Address for security bit |

|---------------------------|-------------------------------|--------------------------|

| MB90F922NC<br>MB90F922NCS | Built-in 2 Mbits Flash Memory | FC0001н                  |

| MB90F923NCS               | Built-in 3 Mbits Flash Memory | F80001 <sub>H</sub>      |

| MB90F924NCS               | Built-in 4 Mbits Flash Memory | F80001 <sub>H</sub>      |

#### Serial communication

In serial communication, reception of wrong data may occur due to noise or other causes. Therefore, design a printed circuit board to prevent noise from occurring. Taking account of the reception of wrong data, detect errors by measures such as adding a checksum to the end of data. If an error is detected, retransmit the data.

#### Characteristic difference between flash device and MASK ROM device

In the flash device and the MASK ROM device, the electrical characteristic including current consumption, ESD, latch-up, the noise characteristic, and oscillation characteristic, etc. is different according to the difference between the chip layout and the memory structure.

Reconfirm the electrical characteristic when the product is replaced by another product of the same series.

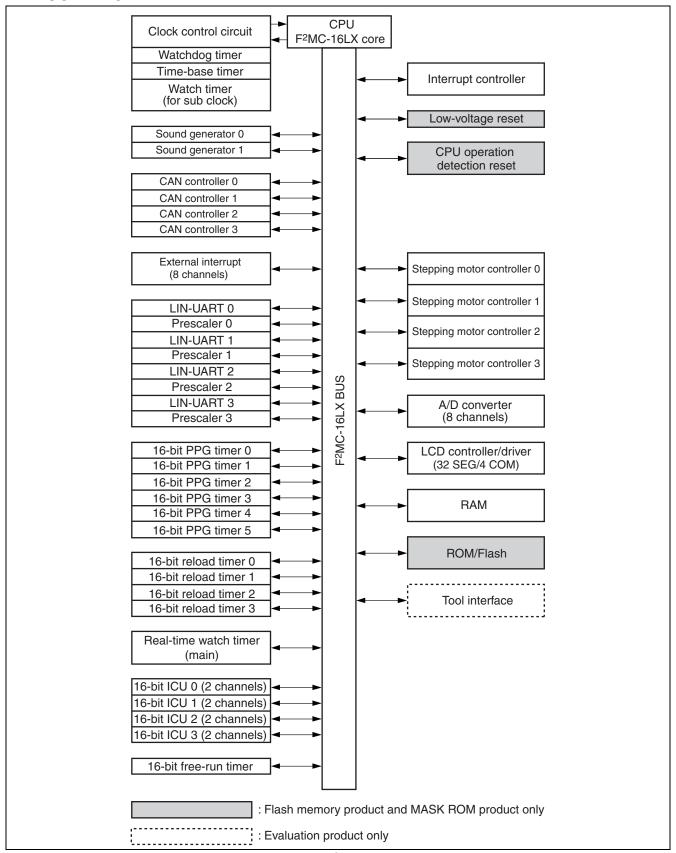

#### **■ BLOCK DIAGRAM**

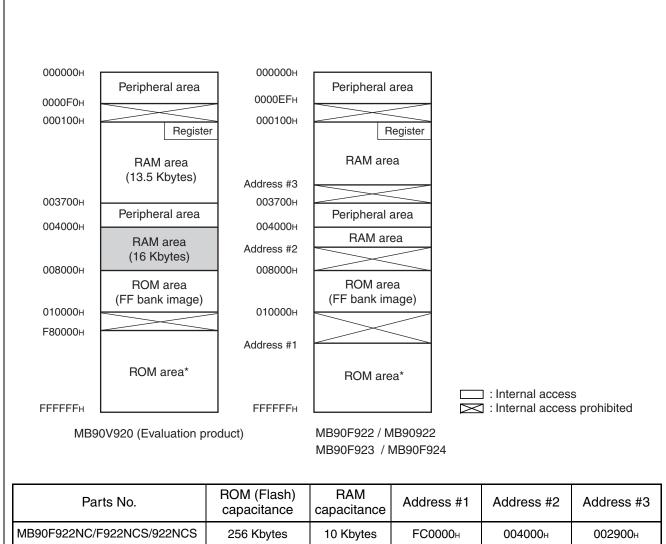

#### MEMORY MAP

| Parts No.                 | ROM (Flash)<br>capacitance | RAM capacitance | Address #1          | Address #2 | Address #3 |

|---------------------------|----------------------------|-----------------|---------------------|------------|------------|

| MB90F922NC/F922NCS/922NCS | 256 Kbytes                 | 10 Kbytes       | FC0000н             | 004000н    | 002900н    |

| MB90F923NC/F923NCS        | 384 Kbytes                 | 16 Kbytes       | FA0000 <sub>H</sub> | 004А00н    | 003700н    |

| MB90F924NC/F924NCS        | 512 Kbytes                 | 24 Kbytes       | F80000н             | 006А00н    | 003700н    |

<sup>\*:</sup> Evaluation products do not contain internal ROM. Treat this address as the ROM decode area used by the tools.

Note: To select models without the ROM mirror function, refer to the "ROM Mirror Function Selection Module" in Hardware Manual. The image of the ROM data in the FF bank appears at the top of the 00 bank, in order to enable efficient use of small C compiler models. The lower 16-bits of the FF bank addresses are allocated to the same addresses as the lower 16-bits of the 00 bank, making it possible to reference tables in ROM without declaring the "far" modifier with the pointers. For example, when an access is made to the address 00С000н, the actual address to be accessed is FFC000н in ROM. Because the size of the FF bank ROM area exceeds 32 Kbytes, it is not possible to view the entire region in the 00 bank image. Therefore because the ROM data from FF8000H to FFFFFFH appears in the image from 008000H to 00FFFFH, it is recommended that ROM data tables be stored in the area from FF8000H to FFFFFFH.

### ■ I/O MAP

| Address             | Register name                      | Symbol | Read/write | Resource name | Initial value         |  |

|---------------------|------------------------------------|--------|------------|---------------|-----------------------|--|

| 000000н             | Port 0 data register               | PDR0   | R/W        | Port 0        | XXXXXXXX              |  |

| 000001н             | Port 1 data register               | PDR1   | R/W        | Port 1        | XXXXXXXX              |  |

| 000002н             | Port 2 data register               | PDR2   | R/W        | Port 2        | XXXXXXXX              |  |

| 000003н             | Port 3 data register               | PDR3   | R/W        | Port 3        | XXXXXXXX              |  |

| 000004н             | Port 4 data register               | PDR4   | R/W        | Port 4        | XXXXXXXX              |  |

| 000005н             | Port 5 data register               | PDR5   | R/W        | Port 5        | XXXXXXXX              |  |

| 000006н             | Port 6 data register               | PDR6   | R/W        | Port 6        | XXXXXXXX              |  |

| 000007н             | Port 7 data register               | PDR7   | R/W        | Port 7        | XXXXXXXX              |  |

| 000008н             | Port 8 data register               | PDR8   | R/W        | Port 8        | XXXXXXXX              |  |

| 000009н             | Port 9 data register               | PDR9   | R/W        | Port 9        | XXXXXXX               |  |

| 00000Ан,<br>00000Вн | (Disabled)                         |        |            |               |                       |  |

| 00000Сн             | Port C data register               | PDRC   | R/W        | Port C        | XXXXXXXX              |  |

| 00000Дн             | Port D data register               | PDRD   | R/W        | Port D        | XXXXXXXX              |  |

| 00000Ен             | Port E data register               | PDRE   | R/W        | Port E        | XXXXXXXXB             |  |

| 00000Fн             | (Disabled)                         |        |            |               |                       |  |

| 000010н             | Port 0 direction register          | DDR0   | R/W        | Port 0        | 0000000В              |  |

| 000011н             | Port 1 direction register          | DDR1   | R/W        | Port 1        | ХХ000000в             |  |

| 000012н             | Port 2 direction register          | DDR2   | R/W        | Port 2        | 000000XXB             |  |

| 000013н             | Port 3 direction register          | DDR3   | R/W        | Port 3        | 0000000В              |  |

| 000014н             | Port 4 direction register          | DDR4   | R/W        | Port 4        | 0000000В              |  |

| 000015н             | Port 5 direction register          | DDR5   | R/W        | Port 5        | 0000000В              |  |

| 000016н             | Port 6 direction register          | DDR6   | R/W        | Port 6        | 0000000В              |  |

| 000017н             | Port 7 direction register          | DDR7   | R/W        | Port 7        | 0000000В              |  |

| 000018н             | Port 8 direction register          | DDR8   | R/W        | Port 8        | 0000000В              |  |

| 000019н             | Port 9 direction register          | DDR9   | R/W        | Port 9        | Х000000в              |  |

| 00001Ан             | Analog input enable                | ADER6  | R/W        | Port 6, A/D   | 111111111             |  |

| 00001Вн             | (Disabled)                         |        |            |               |                       |  |

| 00001Сн             | Port C direction register          | DDRC   | R/W        | Port C        | 0000000В              |  |

| 00001Dн             | Port D direction register          | DDRD   | R/W        | Port D        | Х000000в              |  |

| 00001Ен             | Port E direction register          | DDRE   | R/W        | Port E        | XXXXX000B             |  |

| 00001Fн             | (Disabled)                         |        |            |               |                       |  |

| 000020н             | Lower A/D control status register  | ADCS0  | R/W        |               | 000XXXX0 <sub>B</sub> |  |

| 000021н             | Higher A/D control status register | ADCS1  | R/W        | A/D converter | 000000XB              |  |

| 000022н             | Lower A/D control status register  | ADCR0  | R          | A/D Convented | 0000000В              |  |

| 000023н             | Higher A/D data register           | ADCR1  | R          |               | XXXXXX00 <sub>B</sub> |  |

| Address                  | Register name                                                    | Symbol          | Read/write | Resource name            | Initial value |

|--------------------------|------------------------------------------------------------------|-----------------|------------|--------------------------|---------------|

| 000024н                  |                                                                  |                 | R/W        |                          | XXXXXXXX      |

| 000025н                  | Compare clear register                                           | CPCLR           | R/W        |                          | XXXXXXXXB     |

| 000026н                  | Time and debt are sisten.                                        | TCDT            | R/W        | 16-bit<br>free-run timer | 00000000В     |

| 000027н                  | Timer data register                                              |                 | R/W        |                          | 00000000В     |

| 000028н                  | Lower timer control status register                              | TCCSL           | R/W        |                          | 00000000в     |

| 000029н                  | Higher timer control status register                             | TCCSH           | R/W        |                          | 01-00000в     |

| 00002Ан                  | Lower PPG0 control status register                               | PCNTL0          | R/W        | 16-bit PPG0              | 00000000в     |

| 00002Вн                  | Higher PPG0 control status register                              | PCNTH0          | R/W        |                          | 0000001в      |

| 00002Сн                  | Lower PPG1 control status register                               | PCNTL1          | R/W        | 16-bit PPG1              | 00000000в     |

| 00002Dн                  | Higher PPG1 control status register                              | PCNTH1          | R/W        |                          | 0000001в      |

| 00002Ен                  | Lower PPG2 control status register                               | PCNTL2          | R/W        | 16-bit PPG2              | 0000000В      |

| 00002Fн                  | Higher PPG2 control status register                              | PCNTH2          | R/W        |                          | 0000001в      |

| 000030н                  | External interrupt enable                                        | ENIR            | R/W        | External interrupt       | 0000000В      |

| 000031н                  | External interrupt request                                       | EIRR            | R/W        |                          | 00000000в     |

| 000032н                  | Lower external interrupt level                                   | ELVRL           | R/W        |                          | 00000000в     |

| 000033н                  | Higher external interrupt level                                  | ELVRH           | R/W        |                          | 00000000в     |

| 000034н                  | Serial mode register 0                                           | SMR0            | R/W, W     | UART<br>(LIN/SCI) 0      | 00000000в     |

| 000035н                  | Serial control register 0                                        | SCR0            | R/W, W     |                          | 00000000в     |

| 000036н                  | Reception/transmission data register 1                           | RDR0/<br>TDR0   | R/W        |                          | 0000000в      |

| 000037н                  | Serial status register 0                                         | SSR0            | R/W, R     |                          | 00001000в     |

| 000038н                  | Extended communication control register 0                        | ECCR0           | R/W, R     |                          | 000000XXB     |

| 000039н                  | Extended status control register 0                               | ESCR0           | R/W        |                          | 00000100в     |

| 00003Ан                  | Baud rate generator register 00                                  | BGR00           | R/W        |                          | 0000000В      |

| 00003Вн                  | Baud rate generator register 01                                  | BGR01           | R/W, R     |                          | 0000000В      |

| 00003Сн<br>to<br>00003Fн | (Disabled)                                                       |                 |            |                          |               |

| 000040н<br>to<br>00004Fн | Area reserved for CAN Controller 0. Refer to "■ CAN CONTROLLERS" |                 |            |                          |               |

| 000050н                  | Lower timer control status register 0                            | TMCSR0L         | R/W        |                          | 0000000В      |

| 000051н                  | Higher timer control status register 0                           | TMCSR0H         | R/W        | 16-bit reload timer      | ХХХ10000в     |

| 000052н                  | Timer register 0/relead register 0                               | TMR0/<br>TMRLR0 | R/W        | 0                        | XXXXXXXX      |

| 000053н                  | Timer register 0/reload register 0                               |                 |            |                          | XXXXXXXX      |