# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### Freescale Semiconductor Technical Data

MC100ES8111 Rev 2, 09/2004

# Low Voltage 1:10 Differential HSTL Clock Fanout Buffer

The MC100ES8111 is a bipolar monolithic differential clock fanout buffer. Designed for most demanding clock distribution systems, the MC100ES8111 supports various applications that require the distribution of precisely aligned differential clock signals. Using SiGe technology and a fully differential architecture, the device offers very low skew outputs and superior digital signal characteristics. Target applications for this clock driver are high performance clock distribution in computing, networking and telecommunication systems.

### Features

- 1:10 differential clock fanout buffer

- 80 ps maximum device skew

- SiGe technology

- · Supports DC to 625 MHz operation of clock or data signals

- · HSTL compatible differential clock outputs

- · PECL and HSTL compatible differential clock inputs

- 3.3 V power supply for device core, 1.5 V or 1.8 V HSTL output supply

- · Supports industrial temperature range

- Standard 32 lead LQFP package

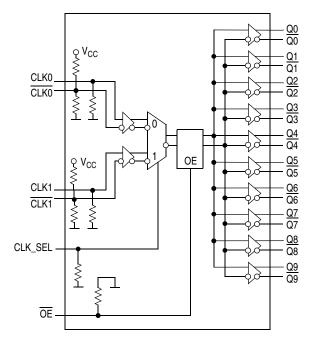

### **Functional Description**

The MC100ES8111 is designed for low skew clock distribution systems and supports clock frequencies up to 625 MHz. The device accepts two clock sources. The CLK0 input accepts HSTL compatible signals and CLK1 accepts PECL compatible signals. The selected input signal is distributed to 10 identical, differential HSTL compatible outputs.

In order to meet the tight skew specification of the device, both outputs of a differential output pair should be terminated, even if only one output is used. In the case where not all 10 outputs are used, the output pairs on the same package side as the parts being used on that side should be terminated.

The HSTL compatible output levels are generated with an open emitter architecture. This minimizes part-to-part and output-to-output skew. The open-emitter outputs require a 50  $\Omega$  DC termination to GND (0 V). The output supply voltage can be either 1.5 V or 1.8 V, the core voltage supply is 3.3 V. The output enable control is synchronized internally preventing output runt pulse generation. Outputs are only disabled or enabled when the outputs are already in logic low state (true outputs logic low, inverted outputs logic high). The internal synchronizer eliminates the setup and hold time requirements for the external clock enable signal. The device is packaged in a 7x7 mm<sup>2</sup> 32-lead LQFP package.

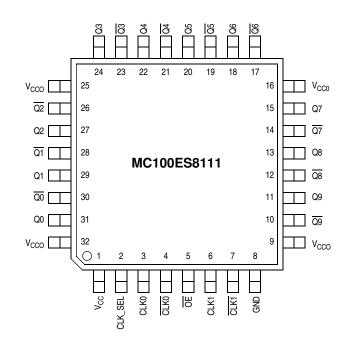

## MC100ES8111

LOW-VOLTAGE 1:10 DIFFERENTIAL HSTL CLOCK FANOUT BUFFER

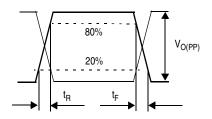

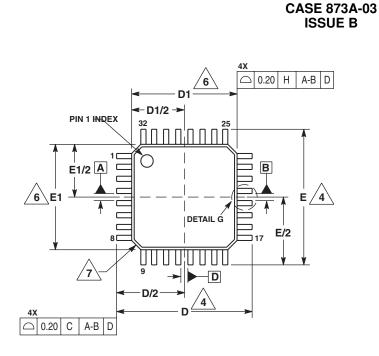

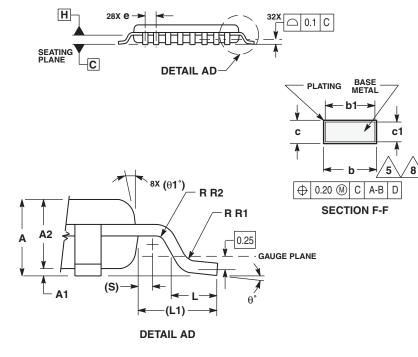

FA SUFFIX 32-LEAD LQFP PACKAGE CASE 873A-03

© Freescale Semiconductor, Inc., 2004. All rights reserved.

Figure 2. 23-Lead Package Pinout (Top View)

### Figure 1. MC100ES8111 Logic Diagram

### Table 1. Pin Configuration<sup>(1)</sup>

| Pin                   | I/O    | Туре   | Function                                                                                                                                                              |

|-----------------------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK0, CLK0            | Input  | HSTL   | Differential HSTL reference clock signal input                                                                                                                        |

| CLK1, CLK1            | Input  | PECL   | Differential PECL reference clock signal input                                                                                                                        |

| CLK_SEL               | Input  | LVCMOS | Reference clock input select                                                                                                                                          |

| OE                    | Input  | LVCMOS | Output enable/disable. OE is synchronous to the input reference clock which eliminates possible output runt pulses when the OE state is changed.                      |

| Q[0-9], <u>Q[0-9]</u> | Output | HSTL   | Differential clock outputs                                                                                                                                            |

| GND                   | Supply |        | Negative power supply                                                                                                                                                 |

| V <sub>CC</sub>       | Supply |        | Positive power supply of the device core (3.3 V)                                                                                                                      |

| V <sub>CCO</sub>      | Supply |        | Positive power supply of the HSTL outputs. All V <sub>CCO</sub> pins must be connected to the positive power supply (1.5 V or 1.8 V) for correct DC and AC operation. |

1. Input pull-up/pull-down resistors have a value of 75 k $\Omega$ .

### Table 2. Function Table

| Control | Default | 0                                                                                                                                                           | 1                                                                                                                                                                        |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_SEL |         | CLK0, CLK0 (HSTL) is the active differential clock input                                                                                                    | CLK1, CLK1 (PECL) is the active differential clock input                                                                                                                 |

| OE      |         | Q[0-9], $\overline{Q[0-9]}$ are active. Deassertion of $\overline{OE}$ can be asynchronous to the reference clock without generation of output runt pulses. | $\underline{Q[0-9]} = L, \overline{Q[0-9]} = H$ (outputs disabled). Assertion of OE can be asynchronous to the reference clock without generation of output runt pulses. |

### MC100ES8111

### Table 3. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol            | Characteristics              | Min                  | Max                   | Unit | Condition |

|-------------------|------------------------------|----------------------|-----------------------|------|-----------|

| V <sub>CC</sub>   | Supply Voltage               | -0.3                 | 3.6                   | V    |           |

| V <sub>CCO</sub>  | Supply Voltage               | -0.3                 | 3.1                   | V    |           |

| V <sub>IN</sub>   | DC Input Voltage             | -0.3                 | V <sub>CC</sub> + 0.3 | V    |           |

| V <sub>OUT</sub>  | DC Output Voltage            | -0.3                 | V <sub>CC</sub> + 0.3 | V    |           |

| I <sub>IN</sub>   | DC Input Current             |                      | ±20                   | mA   |           |

| I <sub>OUT</sub>  | DC Output Current            |                      | ±50                   | mA   |           |

| Τ <sub>S</sub>    | Storage Temperature          | -65                  | 125                   | °C   |           |

| T <sub>Func</sub> | Functional Temperature Range | T <sub>A</sub> = -40 | T <sub>J</sub> = +110 | °C   |           |

1. Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

### **Table 4. General Specifications**

| Symbol          | Characteristics                                                                                                       | Min  | Тур                                                          | Max                                                          | Unit                                                 | Condition                                                                                                                    |

|-----------------|-----------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| V <sub>TT</sub> | Output termination voltage                                                                                            |      | 0                                                            |                                                              | V                                                    |                                                                                                                              |

| MM              | ESD Protection (Machine model)                                                                                        | 200  |                                                              |                                                              | V                                                    |                                                                                                                              |

| HBM             | ESD Protection (Human body model)                                                                                     | 2000 |                                                              |                                                              | V                                                    |                                                                                                                              |

| CDM             | ESD Protection (Charged device model)                                                                                 | 2000 |                                                              |                                                              | V                                                    |                                                                                                                              |

| LU              | Latch-up Immunity                                                                                                     | 200  |                                                              |                                                              | mA                                                   |                                                                                                                              |

| C <sub>IN</sub> | Input Capacitance                                                                                                     |      | 4.0                                                          |                                                              | pF                                                   | Inputs                                                                                                                       |

| θ <sub>JA</sub> | Thermal resistance junction to ambient<br>JESD 51-3, single layer test board<br>JESD 51-6, 2S2P multilayer test board |      | 83.1<br>73.3<br>68.9<br>63.8<br>57.4<br>59.0<br>54.4<br>52.5 | 86.0<br>75.4<br>70.9<br>65.3<br>59.6<br>60.6<br>55.7<br>53.8 | °C/W<br>°C/W<br>°C/W<br>°C/W<br>°C/W<br>°C/W<br>°C/W | Natural convection<br>100 ft/min<br>200 ft/min<br>400 ft/min<br>800 ft/min<br>Natural convection<br>100 ft/min<br>200 ft/min |

|                 |                                                                                                                       |      | 50.4<br>47.8                                                 | 51.5<br>48.8                                                 | °C/W<br>°C/W                                         | 400 ft/min<br>800 ft/min                                                                                                     |

| $\theta_{JC}$   | Thermal Resistance Junction to Case                                                                                   |      | 23.0                                                         | 26.3                                                         | °C/W                                                 | MIL-SPEC 883E<br>Method 1012.1                                                                                               |

| Τ <sub>J</sub>  | Operating Junction Temperature <sup>(1)</sup><br>(continuous operation)MTBF = 9.1 years                               |      |                                                              | 110                                                          | °C                                                   |                                                                                                                              |

1. Operating junction temperature impacts device life time. Maximum continuous operating junction temperature should be selected according to the application life time requirements (See application note AN1545 and the application section in this datasheet for more information). The device AC and DC parameters are specified up to 110°C junction temperature allowing the MC100ES8111 to be used in applications requiring industrial temperature range. It is recommended that users of the MC100ES8111 employ thermal modeling analysis to assist in applying the junction temperature specifications to their particular application.

| Symbol           | Characteristics                                                           | Min                    | Тур        | Max                    | Unit | Condition                            |

|------------------|---------------------------------------------------------------------------|------------------------|------------|------------------------|------|--------------------------------------|

| Clock Inpl       | t Pair CLK0, CLK0 (HSTL differential signals)                             |                        | I          | 1                      |      |                                      |

| $V_{DIF}$        | Differential Input Voltage <sup>(1)</sup>                                 | 0.2                    |            |                        | V    |                                      |

| $V_{X, IN}$      | Differential Cross Point Voltage <sup>(2)</sup>                           | 0.25                   | 0.68 - 0.9 | V <sub>CC</sub> -1.3   | V    |                                      |

| V <sub>IH</sub>  | Input High Voltage                                                        | V <sub>X</sub> +0.1    |            |                        | V    |                                      |

| $V_{IL}$         | Input Low Voltage                                                         |                        |            | V <sub>X</sub> -0.1    | V    |                                      |

| I <sub>IN</sub>  | Input Current                                                             |                        |            | ±150                   | μA   | $V_{IN} = V_X \pm 0.1 V$             |

| Clock Inpu       | It Pair CLK1, CLK1 (PECL differential signals                             | ;)                     | •          | •                      |      |                                      |

| V <sub>PP</sub>  | Differential Input Voltage <sup>(3)</sup>                                 | 0.15                   |            | 1.0                    | V    | Differential operation               |

| V <sub>CMR</sub> | Differential Cross Point Voltage <sup>(4)</sup>                           | 1.0                    |            | V <sub>CC</sub> -0.6   | V    | Differential operation               |

| V <sub>IH</sub>  | Input Voltage High                                                        | V <sub>CC</sub> -1.165 |            | V <sub>CC</sub> -0.880 | V    |                                      |

| VIL              | Input Voltage Low                                                         | V <sub>CC</sub> -1.810 |            | V <sub>CC</sub> -1.475 | V    |                                      |

| I <sub>IN</sub>  | Input Current                                                             |                        |            | ±150                   | μA   | $V_{IN} = V_{IH} \text{ or } V_{IN}$ |

| LVCMOS           | Control Inputs OE, CLK_SEL                                                |                        | •          |                        | •    |                                      |

| V <sub>IL</sub>  | Input Voltage Low                                                         |                        |            | 0.8                    | V    |                                      |

| V <sub>IH</sub>  | Input Voltage High                                                        | 2.0                    |            |                        | V    |                                      |

| I <sub>IN</sub>  | Input Current                                                             |                        |            | ±150                   | μA   | $V_{IN} = V_{IH} \text{ or } V_{IN}$ |

| HSTL Cloo        | ck Outputs (Q[0-9], Q[0-9])                                               |                        |            | •                      |      |                                      |

| $V_{X,OUT}$      | Output Differential Crosspoint                                            | 0.68                   | 0.75       | 0.9                    | V    |                                      |

| V <sub>OH</sub>  | Output High Voltage                                                       | 1.0                    |            |                        | V    |                                      |

| V <sub>OL</sub>  | Output Low Voltage                                                        |                        |            | 0.4                    | V    |                                      |

| Supply Cu        | rrent                                                                     | ·                      |            | •                      | •    |                                      |

| I <sub>CC</sub>  | Maximum Supply Current without output termination current                 |                        | 80         | 105                    | mA   | V <sub>CC</sub> pin (core)           |

| $I_{CCO}^{(5)}$  | Maximum Supply Current, outputs terminated 50 $\Omega$ to V <sub>TT</sub> |                        | 350        | 410                    | mA   | V <sub>CCO</sub> pins (outputs)      |

| Table 5. DC Characteristics ( $V_{CC} = 3.3$ ) | V ± 5%, V <sub>CCO</sub> = 1.5 V ± 0.1 V | $V \text{ or } V_{CCO} = 1.8 \text{ V} \pm 0.1 \text{ V}$ | $T_{1} = 0^{\circ}C \text{ to } +110^{\circ}C$ |

|------------------------------------------------|------------------------------------------|-----------------------------------------------------------|------------------------------------------------|

|                                                |                                          | 0.00000000000000000000000000000000000                     | ,                                              |

1. V<sub>DIF</sub> (DC) is the minimum differential HSTL input voltage swing required for device functionality.

2. V<sub>X</sub> (DC) is the crosspoint of the differential HSTL input signal. Functional operation is obtained when the crosspoint is within the V<sub>X</sub> (DC) range and the input swing lies within the  $V_{PP}$  (DC) specification.

V<sub>PP</sub> (DC) is the minimum differential input voltage swing required to maintain device functionality.

V<sub>CMR</sub> (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the V<sub>CMR</sub> (DC) range and the input swing lies within the  $V_{PP}$  (DC) specification.

5. I<sub>CC</sub> includes current through the output resistors (all outputs terminated to V<sub>TT</sub>). See also "Power Consumption and Junction Temperature" on page 6.

| Symbol                          | Characteristics                                        |                                                         | Min                                                | Тур         | Max                     | Unit     | Condition    |

|---------------------------------|--------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------|-------------|-------------------------|----------|--------------|

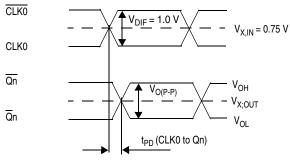

| REF_SEL                         | = 0, Active Clock Input Pair CLK0, CLK0                | (HSTL differential                                      | signals)                                           |             |                         |          |              |

| $V_{DIF}$                       | Differential Input Voltage <sup>(2)</sup> (Peak-to-Pea | ak)                                                     | 0.4                                                |             |                         | V        |              |

| $V_{X, IN}$                     | Differential Cross Point Voltage <sup>(3)</sup>        |                                                         | 0.68                                               |             | 0.9                     | V        |              |

| f <sub>CLK</sub>                | Input Frequency                                        |                                                         | 0                                                  |             | 625                     | MHz      |              |

| t <sub>PD</sub>                 | Propagation Delay CLK0 to Qn                           | V <sub>CCO</sub> = 1.8 V<br>V <sub>CCO</sub> = 1.5 V    | 700<br>700                                         | 990<br>1030 | 1270<br>1420            | ps<br>ps | Differential |

| $t_{\text{SK}(\text{PP})}$      | Output-to-Output Skew (Part-to-Part)                   | V <sub>CCO</sub> = 1.8 V<br>V <sub>CCO</sub> = 1.5 V    |                                                    |             | 570<br>720              | ps<br>ps | Differential |

| $t_{SK(P)}$                     | Output Pulse Skew <sup>(4)</sup>                       | V <sub>CCO</sub> = 1.8 V<br>V <sub>CCO</sub> = 1.5 V    |                                                    |             | 100<br>150              | ps<br>ps |              |

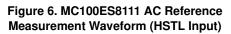

| REF_SEL                         | = 1, Active Clock Input Pair CLK1, CLK1                | (PECL differential                                      | signals)                                           |             |                         |          |              |

| V <sub>PP</sub>                 | Differential Input Voltage <sup>(5)</sup> (Peak-to-Pea | ak)                                                     | 0.2                                                |             | 1.0                     | V        |              |

| V <sub>CMR</sub>                | Differential Input Crosspoint Voltage <sup>(6)</sup>   |                                                         | 1.0                                                |             | V <sub>CC</sub> -0.6    | V        |              |

| f <sub>CLK</sub>                | Input Frequency                                        |                                                         | 0                                                  |             | 625                     | MHz      | Differential |

| t <sub>PD</sub>                 | Propagation Delay CLK1 to Qn                           | V <sub>CCO</sub> = 1.8 V<br>V <sub>CCO</sub> = 1.5 V    | 590<br>590                                         | 860<br>910  | 1220<br>1360            | ps<br>ps | Differential |

| t <sub>SK(PP)</sub>             | Output-to-Output Skew (Part-to-Part)                   | V <sub>CCO</sub> = 1.8 V<br>V <sub>CCO</sub> = 1.5 V    |                                                    |             | 630<br>770              | ps<br>ps | Differential |

| $t_{SK(P)}$                     | Output Pulse Skew <sup>(7)</sup>                       | V <sub>CCO</sub> = 1.8 V<br>V <sub>CCO</sub> = 1.5 V    |                                                    |             | 150<br>200              | ps<br>ps |              |

| ISTL Clo                        | ck Outputs (Qn, Qn)                                    |                                                         |                                                    |             |                         |          | 1            |

| V <sub>X, OUT</sub>             | Output Differential Crosspoint                         |                                                         | 0.68                                               | 0.91        | 1.1                     | V        |              |

| V <sub>OH</sub>                 | Output High Voltage                                    | V <sub>CCO</sub> = 1.8 V<br>V <sub>CCO</sub> = 1.5 V    | V <sub>CCO</sub> -0.8 V<br>V <sub>CCO</sub> -0.5 V |             | 1.5<br>1.5              | V<br>V   |              |

| V <sub>OL</sub>                 | Output Low Voltage                                     |                                                         | 0.2                                                |             | 0.8                     | V        |              |

| V <sub>O(P-P)</sub>             | Differential Output Voltage (Peak-to-Pea               | k) V <sub>CCO</sub> = 1.8 V<br>V <sub>CCO</sub> = 1.5 V | 0.45<br>0.40                                       |             | 1.0<br>1.0              | V<br>V   |              |

| $t_{SK(O)}$                     | Output-to-Output Skew                                  | V <sub>CCO</sub> = 1.8 V<br>V <sub>CCO</sub> = 1.5 V    |                                                    | 37<br>60    | 80<br>105               | ps<br>ps | Differential |

| t <sub>JIT(CC)</sub>            | Output Cycle-to-Cycle Jitter RMS (1 σ)                 |                                                         |                                                    |             | 1.0                     | ps       |              |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                                  |                                                         | 150                                                |             | 800                     | ps       | 20% to 80%   |

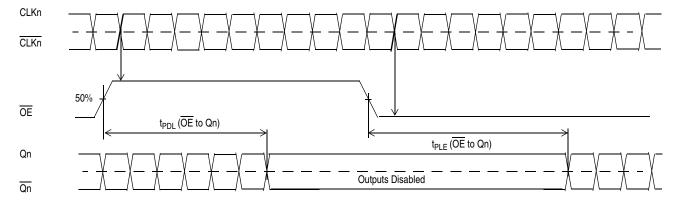

| t <sub>PDL</sub> <sup>(8)</sup> | Output Disable Time                                    |                                                         | 2.5·T + t <sub>PD</sub>                            |             | 3.5·T + t <sub>PD</sub> | ns       | T=CLKn perio |

| t <sub>PLE</sub> <sup>(9)</sup> | Output Enable Time                                     |                                                         | 3.0·T + t <sub>PD</sub>                            |             | 4.0·T + t <sub>PD</sub> | ns       | T=CLKn perio |

### Table 6. AC Characteristics ( $V_{CC} = 3.3 \text{ V} \pm 5\%$ , $V_{CCO} = 1.5 \text{ V} \pm 0.1 \text{ V}$ or $V_{CCO} = 1.8 \text{ V} \pm 0.1 \text{ V}$ ), $T_J = 0^{\circ}C$ to $+110^{\circ}C^{(1)}$

1. AC characteristics apply for parallel output termination of 50  $\Omega$  to V<sub>TT</sub> (GND).

2. V<sub>DIF</sub> (DC) is the minimum differential HSTL input voltage swing required for device functionality.

3.  $V_X(DC)$  is the crosspoint of the differential HSTL input signal. Functional operation is obtained when the crosspoint is within the  $V_X(DC)$  range and the input swing lies within the  $V_{DIF}(DC)$  specification.

4. Output duty cycle is DC =  $(0.5 \pm 150 \text{ ps} \cdot f_{OUT}) \cdot 100\%$ . E.g. the DC range at  $f_{OUT} = 100 \text{ MHz}$  is 48.5% < DC < 51.5%.

5. V<sub>PP</sub> (AC) is the minimum differential PECL input voltage swing required to maintain AC characteristics including tpd and device-to-device skew.

V<sub>CMR</sub> (AC) is the crosspoint of the differential HSTL input signal. Normal AC operation is obtained when the crosspoint is within the V<sub>CMR</sub> (AC) range and the input swing lies within the V<sub>PP</sub> (AC) specification. Violation of V<sub>CMR</sub> (AC) or V<sub>PP</sub> (AC) impacts the device propagation delay, device and part-to-part skew.

7. Output pulse skew is the absolute difference of the propagation delay times:  $|t_{PLH} - t_{PHL}|$ . The output duty cycle is DC = (0.5 ± 200 ps ·  $f_{OUT}$ ) · 100%. E.g. the DC range at  $f_{OUT}$  = 100 MHz and  $V_{CCO}$  = 1.5 V is 48.0% < DC < 52.0%.

8. Propagation delay OE deassertion to differential output disabled (differential low: true output low, complementary output high).

9. Propagation delay OE assertion to output enabled (active).

### **APPLICATIONS INFORMATION**

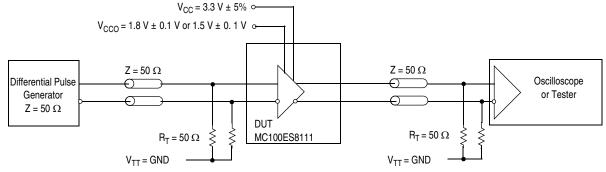

### **Test Reference and Output Termination**

The MC100ES8111 is designed for high-frequency and low-skew clock distribution. The high-speed differential outputs are capable of driving 50  $\Omega$  transmission lines and always require a DC termination to V<sub>TT</sub> (GND). In order to maintain the tight skew and timing specifications, it is recommend to terminate the differential outputs by 50  $\Omega$  to

GND, with the termination resistor located as close as possible to the end of the clock transmission line. All DC and AC specifications apply to this termination method (see the reference circuit shown in Figure 3 "MC100ES8111 AC Test Reference"). The MC100ES8111 does not support an output termination to V<sub>TT</sub> = V<sub>X</sub> = 0.75 V (center voltage termination).

### Power Consumption and the Junction Temperature

The power consumption  $\mathsf{P}_{\mathsf{TOT}}$  of the MC100ES8111 depends on the supply voltages and the DC output termination. The clock frequency has a negligible effect on  $\mathsf{P}_{\mathsf{TOT}}$ . If all outputs are terminated by 50  $\Omega$  to GND, the device power consumption is calculated by:

$$P_{TOT} = V_{CC} \cdot I_{CC} + I_{CCO} \cdot (V_{CCO} - V_X)$$

For instance, at a supply voltage of V<sub>CC</sub> = 3.3 V and a termination of 50  $\Omega$  to GND, the typical device power consumption is 579 mW at V<sub>CCO</sub> = 1.8 V and 474 mW at V<sub>CCO</sub> = 1.5 V.

| MC100ES8111              | P <sub>TOT, TYP</sub> <sup>(1)</sup> | P <sub>TOT, MAX</sub> <sup>(2)</sup> |

|--------------------------|--------------------------------------|--------------------------------------|

| V <sub>CCO</sub> = 1.5 V | 470 mW                               | 647 mW                               |

| V <sub>CCO</sub> = 1.8 V | 575 mW                               | 769 mW                               |

### **Table 7. Power Consumption**

2. Worst case:  $V_{CC},\,V_{CC}$  at max. values and using max.  $I_{CC},\,I_{CCO}$  limits.

To make the optimum use of high clock frequency and low skew capabilities of the MC100ES8111, the device is specified, characterized and tested for the junction temperature range of  $T_J = 0^{\circ}$ C to +110°C. Because the exact thermal performance depends on the PCB type, design, thermal management and natural or forced air convection, the junction temperature provides an exact way to correlate the application specific conditions to the published performance data of this datasheet. The correlation of the junction temperature range to the application ambient temperature range and vice versa can be done by calculation:

$$T_J = T_A + R_{thja} \cdot P_{tot}$$

Assuming a thermal resistance (junction to ambient) of 54.4°C/W (2s2p board, 100 ft/min airflow, see Table 8) and a

# typical power consumption of 575 mW (all outputs terminated 50 ohms to GND, $V_{CCO} = 1.8$ V), the junction temperature of the MC100ES8111 is approximately $T_A + 31^{\circ}$ C, and the minimum ambient temperature in this example case calculates to -31°C (the maximum ambient temperature is 79°C. See Table 8). Exceeding the minimum junction temperature specification of the MC100ES8111 does not have a significant impact on the device functionality. However, the continuous use the MC100ES8111 at high ambient temperatures requires thermal management to not exceed the specified maximum junction temperature.

| Table 8. Ambient | Temperature | Ranges | $(P_{tot} = 575 \text{ mW})$ |

|------------------|-------------|--------|------------------------------|

|------------------|-------------|--------|------------------------------|

| R <sub>thja</sub> (2s2p board) |          | T <sub>A, min</sub> <sup>(1)</sup> | T <sub>A, max</sub> |

|--------------------------------|----------|------------------------------------|---------------------|

| Natural convection             | 59.0°C/W | -34°C                              | 76°C                |

| 100 ft/min                     | 54.4°C/W | -31°C                              | 79°C                |

| 200 ft/min                     | 52.5°C/W | -30°C                              | 80°C                |

| 400 ft/min                     | 50.4°C/W | -29°C                              | 81°C                |

| 800 ft/min                     | 47.8°C/W | -27.5°C                            | 82.5°C              |

1. The MC100ES8111 device function is guaranteed from  $T_A$  = -40°C to  $T_J$  = 110°C.

### Maintaining Lowest Device Skew

The MC100ES8111 guarantees low output-to-output skew of max. 80 ps and a part-to-part skew of max. 630 ps  $(V_{CCO} = 1.8 \text{ V})$ . To ensure low skew clock signals in the application, both outputs of any differential output pair need to be terminated identically, even if only one output is used. When fewer than all ten output pairs are used, identical termination of all output pairs within the output bank (same package side) is recommended. If an entire output bank is not used, it is recommended to leave all of these outputs open and unterminated. This will reduce the device power consumption while maintaining minimum output skew.

### MC100ES8111

<sup>1.</sup> Typical case: V\_{CC}, V\_{CCO} at nominal values and using typical  $I_{CC},\,I_{CCO}$  data.

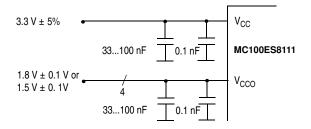

### **Power Supply Bypassing**

The MC100ES8111 is a mixed analog/digital product. The differential architecture of the MC100ES8111 supports low noise signal operation at high frequencies. In order to maintain its superior signal quality, all  $V_{CC}$  pins should be bypassed by high-frequency ceramic capacitors connected to GND. If the spectral frequencies of the internally generated switching noise on the supply pins cross the series resonant point of an individual bypass capacitor, its overall impedance begins to look inductive and thus increases with increasing frequency. The parallel capacitor combination shown ensures that a low impedance path to ground exists for frequencies well above the noise bandwidth.

Figure 4. V<sub>CC</sub>, V<sub>CCO</sub> Power Supply Bypass

### Output Enable/Disable Control

The MC100ES8111 enables and disables outputs synchronously to the input clock signal. The user may enable and disable the outputs by using the  $\overline{OE}$  control regardless of any hold and setup time constraints. Output runt pulses are prevented in any case. Outputs are disabled in logic low state (Qn=Low,  $\overline{Qn}$ =High) without a change of the output impedance.

Figure 5. MC100ES8111 Output Disable/Enable Timing

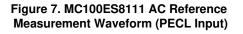

### AC MEASUREMENT REFERENCES

REF\_SEL = 0

Figure 8. Output-to-Output Skew

The output-to-output skew is defined as the worst case difference in propagation delay between any two similar delay paths within a single device.

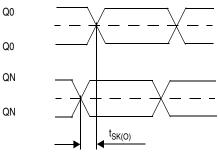

Figure 9. HSTL Output Rise/Fall Time

NOTES: 1. DIMENSIONS ARE IN MILLIMETERS. 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994. 3. DATUMP LANE H. 4. DIMENSIONS D AND TO BE DETERMINED AT DATUM PLANE H. 4. DIMENSIONS D AND E TO BE DETERMINED AT SEATING PLANE C. 5. DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM & DIMENSION BY MORE THAN 0.08-mm. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND DAJACENT LEAD OR PROTRUSIONS. 14ND ET NO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE DANIS INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.23-mm PER SIDE. D1 AND ET ARE MAXIMUM MOLD MISMATCH. EXAMPLE AND FE DE CONSENS INCLUDING MOLD MISMATCH. 2. EXACT SHAPE OF EACH CORNER IS OPTIONAL. 8. THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1-mm AND 0.25-mm FROM THE LEAD TIP.

|     | MILLIMETERS |          |  |  |

|-----|-------------|----------|--|--|

| DIM | MIN         | MAX      |  |  |

| Α   | 1.40        | 1.60     |  |  |

| A1  | 0.05        | 0.15     |  |  |

| A2  | 1.35        | 1.45     |  |  |

| b   | 0.30        | 0.45     |  |  |

| b1  | 0.30        | 0.40     |  |  |

| С   | 0.09        | 0.20     |  |  |

| c1  | 0.09        | 0.16     |  |  |

| D   | 9.00 BSC    |          |  |  |

| D1  | 7.00 BSC    |          |  |  |

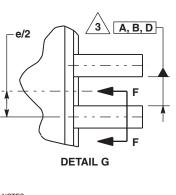

| е   | 0.80        | 0.80 BSC |  |  |

| E   | 9.00        | BSC      |  |  |

| E1  | 7.00        | BSC      |  |  |

| L   | 0.50        | 0.70     |  |  |

| L1  | 1.00        | REF      |  |  |

| q   | 0°          | 7°       |  |  |

| q1  |             | REF      |  |  |

| R1  | 0.08        | 0.20     |  |  |

| R2  | 0.08        |          |  |  |

| S   | 0.20        | REF      |  |  |

### NOTES

### MC100ES8111

## NOTES

### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

### Japan:

Freescale Semiconductor Japan Ltd. Technical Information Center 3-20-1, Minami-Azabu, Minato-ku Tokyo 106-0047, Japan 0120 191014 or +81 3 3440 3569 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale ™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2004. All rights reserved.

MC100ES8111 Rev. 2 09/2004