Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Document Number: MC10XS3435

Rev. 11.0, 5/2014

# **Quad High-side Switch** (Dual 10 mOhm, Dual 35 mOhm)

The 10XS3435 is one in a family of devices designed for low voltage automotive lighting applications. Its four low  $\mathsf{R}_{\mathsf{DS}(\mathsf{on})}\,\mathsf{MOSFETs}$  (dual 10 mOhm/dual 35 mOhm) can control four separate 55/28 W bulbs, and/or Xenon modules, and/or LEDs.

Programming, control and diagnostics are accomplished using a 16-bit SPI interface. Its output with selectable slew rate improves electromagnetic compatibility (EMC) behavior. Additionally, each output has its own parallel input or SPI control for pulse-width modulation (PWM) control. The 10XS3435 allows the user to program via the SPI the fault current trip levels and duration of acceptable lamp inrush. The device has Fail-safe mode to provide functionality of the outputs in case of MCU damage. This device is powered using SMARTMOS technology.

#### **Features**

- Four protected 10 mOhm and 35 mOhm high side switches (at

- Operating voltage range of 6.0 to 20 V with sleep current  $< 5.0 \mu A$ , extended mode from 4.0 to 28 V

- 8.0 MHz 16-bit 3.3 V and 5.0 V SPI control and status reporting with daisy chain capability

- PWM module using external clock or calibratable internal oscillator with programmable outputs delay management

- Smart overcurrent shutdown, severe short-circuit, overtemperature protections with time limited autoretry, and Failsafe mode in case of MCU damage

- Output OFF or ON open-load detection compliant to bulbs or LEDs and short to battery detection

- Analog current feedback with selectable ratio and board temperature feedback

## 10XS3435

#### **High-side Switch**

**FK SUFFIX** 98ARL10596D 24-PIN PQFN

#### **Applications**

- Low-voltage automotive lighting

- Xenon bulbs

- Halogen bulbs

- Light-emitting diodes (LEDs)

- High beam

- Low beam

- Flashers

- Low-voltage industrial lighting

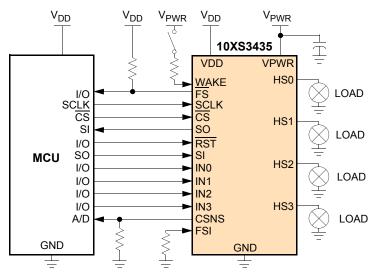

Figure 1. 10XS3435 Simplified Application Diagram

## **ORDERABLE PARTS**

## **Table 1. Orderable Part Variations**

| Part Number(1) | Temperature   | Package |

|----------------|---------------|---------|

| MC10XS3435BHFK | 40 to 125 °C  | 24 PQFN |

| MC10XS3435DHFK | -40 to 125 °C | 24 PQFN |

#### Notes

1. To order parts in Tape & Reel, add the R2 suffix to the part number.

## **DEVICE VARIATIONS**

**Table 2. Device Variations**

| Characteristic                                                                | Symbol                | Min    | Тур | Max | Unit |

|-------------------------------------------------------------------------------|-----------------------|--------|-----|-----|------|

| Wake Input Clamp Voltage, I <sub>CL(WAKE)</sub> < 2.5 mA                      | V <sub>CL(WAKE)</sub> |        |     |     | V    |

| 10XS3435B                                                                     |                       | 18     | 25  | 32  |      |

| 10XS3435D                                                                     |                       | 20     | 27  | 35  |      |

| Fault Detection Blanking Time                                                 | t <sub>FAULT</sub>    |        |     |     | μS   |

| 10XS3435B                                                                     |                       | -      | 5.0 | 20  |      |

| 10XS3435D                                                                     |                       | -      | 5.0 | 10  |      |

| Output Shutdown Delay Time                                                    | t <sub>DETECT</sub>   |        |     |     | μS   |

| 10XS3435B                                                                     |                       | -      | 7.0 | 30  |      |

| 10XS3435D                                                                     |                       | -      | 7.0 | 20  |      |

| Peak Package Reflow Temperature During Reflow <sup>(2)</sup> , <sup>(3)</sup> | T <sub>PPRT</sub>     | Note 3 |     |     | °C   |

- 2. Pin soldering temperature limit is for 40 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 3. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts (i.e. MC33xxxD enter 33xxx), and review parametrics.

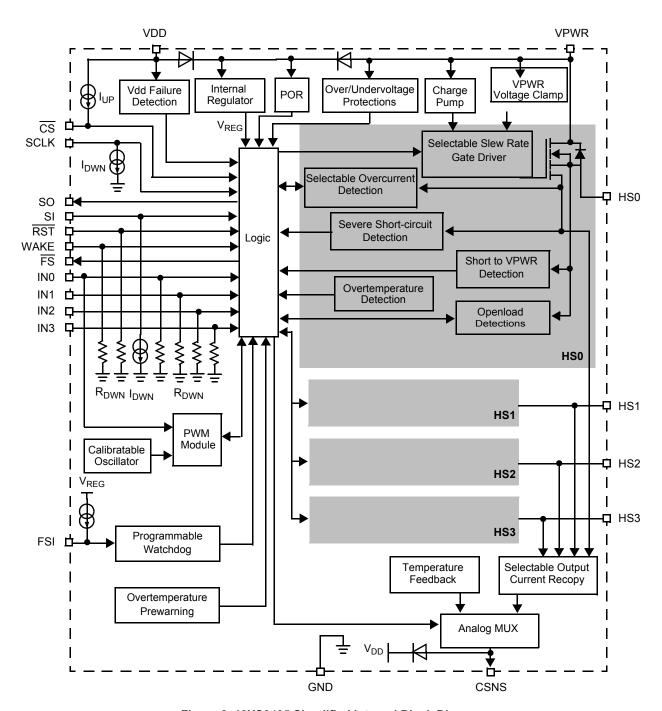

## INTERNAL BLOCK DIAGRAM

Figure 2. 10XS3435 Simplified Internal Block Diagram

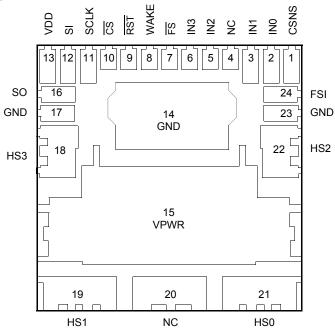

## **PIN CONNECTIONS**

## **Transparent Top View of Package**

Figure 3. 10XS3435 Pin Connections

Table 3. 10XS3435 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 25.

| Pin<br>Number    | Pin Name                 | Pin<br>Function | Formal Name                  | Definition                                                                                                                                                                                                                                                                                    |

|------------------|--------------------------|-----------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | CSNS                     | Output          | Output Current<br>Monitoring | This pin reports an analog value proportional to the designated HS[0:3] output current or the temperature of the GND flag (pin 14). It is used externally to generate a ground-referenced voltage for the microcontroller (MCU). Current recopy and temperature feedback is SPI programmable. |

| 2<br>3<br>5<br>6 | IN0<br>IN1<br>IN2<br>IN3 | Input           | Direct Inputs                | Each direct input controls the device mode. The IN[0:3] high side input pins are used to directly control HS0:HS3 high side output pins.  The PWM frequency can be generated from IN0 pin to PWM module in case of external clock is set.                                                     |

| 7                | FS                       | Output          | Fault Status<br>(Active Low) | This pin is an open drain configured output requiring an external pull-up resistor to $V_{\rm DD}$ for fault reporting.                                                                                                                                                                       |

| 8                | WAKE                     | Input           | Wake                         | This input pin controls the device mode.                                                                                                                                                                                                                                                      |

| 9                | RST                      | Input           | Reset                        | This input pin is used to initialize the device configuration and fault registers, as well as place the device in a low-current sleep mode.                                                                                                                                                   |

| 10               | <u>cs</u>                | Input           | Chip Select<br>(Active Low)  | This input pin is connected to a chip select output of a master microcontroller (MCU).                                                                                                                                                                                                        |

| 11               | SCLK                     | Input           | Serial Clock                 | This input pin is connected to the MCU providing the required bit shift clock for SPI communication.                                                                                                                                                                                          |

| 12               | SI                       | Input           | Serial Input                 | This pin is a command data input pin connected to the SPI Serial Data Output of the MCU or to the SO pin of the previous device of a daisy-chain of devices.                                                                                                                                  |

| 13               | VDD                      | Power           | Digital Drain Voltage        | This pin is an external voltage input pin used to supply power interfaces to the SPI bus.                                                                                                                                                                                                     |

10XS3435

## Table 3. 10XS3435 Pin Definitions (continued)

A functional description of each pin can be found in the Functional Pin Description section beginning on page  $\underline{25}$ .

| Pin<br>Number        | Pin Name                 | Pin<br>Function | Formal Name           | Definition                                                                                                                                            |

|----------------------|--------------------------|-----------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14, 17, 23           | GND                      | Ground          | Ground                | These pins, internally shorted, are the ground for the logic and analog circuitry of the device. These ground pins must be also shorted in the board. |

| 15                   | VPWR                     | Power           | Positive Power Supply | This pin connects to the positive power supply and is the source of operational power for the device.                                                 |

| 16                   | SO                       | Output          | Serial Output         | This output pin is connected to the SPI Serial Data Input pin of the MCU or to the SI pin of the next device of a daisy-chain of devices.             |

| 18<br>19<br>21<br>22 | HS3<br>HS1<br>HS0<br>HS2 | Output          | High Side Outputs     | Protected 10 mOhm (HS0 and HS1) 35 mOhm (HS2 and HS3) high side power output pins to the load.                                                        |

| 4, 20                | NC                       | N/A             | No Connect            | These pins may not be connected.                                                                                                                      |

| 24                   | FSI                      | Input           | Fail-safe Input       | This input enables the watchdog timeout feature.                                                                                                      |

## **ELECTRICAL CHARACTERISTICS**

## **MAXIMUM RATINGS**

#### **Table 4. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                              | Symbol                | Value                        | Unit |

|----------------------------------------------------------------------|-----------------------|------------------------------|------|

| ELECTRICAL RATINGS                                                   | ,                     |                              | •    |

| V <sub>PWR</sub> Supply Voltage Range                                | V <sub>PWR(SS)</sub>  |                              | V    |

| Load Dump at 25°C (400 ms)                                           |                       | 41                           |      |

| Maximum Operating Voltage                                            |                       | 28                           |      |

| Reverse Battery                                                      |                       | -18                          |      |

| V <sub>DD</sub> Supply Voltage Range                                 | V <sub>DD</sub>       | -0.3 to 5.5                  | V    |

| Input/Output Voltage                                                 | (7)                   | -0.3 to V <sub>DD</sub> +0.3 | V    |

| WAKE Input Clamp Current                                             | I <sub>CL(WAKE)</sub> | 2.5                          | mA   |

| CSNS Input Clamp Current                                             | I <sub>CL(CSNS)</sub> | 2.5                          | mA   |

| HS [0:3] Voltage                                                     | V <sub>HS[0:3]</sub>  |                              | V    |

| Positive                                                             |                       | 41                           |      |

| Negative                                                             |                       | -24                          |      |

| Output Current <sup>(4)</sup>                                        | I <sub>HS[0:3]</sub>  | 6.0                          | Α    |

| HS[0,1] Output Clamp Energy using single pulse method <sup>(5)</sup> | E <sub>CL[0:1]</sub>  | 100                          | mJ   |

| HS[2,3] Output Clamp Energy using single pulse method <sup>(5)</sup> | E <sub>CL[2:3]</sub>  | 35                           | mJ   |

| ESD Voltage <sup>(6)</sup>                                           |                       |                              | V    |

| Human Body Model (HBM) for HS[0:3], VPWR and GND                     | V <sub>ESD1</sub>     | ±8000                        |      |

| Human Body Model (HBM) for other pins                                | V <sub>ESD2</sub>     | ±2000                        |      |

| Charge Device Model (CDM)                                            | 2002                  |                              |      |

| Corner Pins (1, 13, 19, 21)                                          | V <sub>ESD3</sub>     | ±750                         |      |

| All Other Pins (2-12, 14-18, 20, 22-24)                              | V <sub>ESD4</sub>     | ±500                         |      |

| THERMAL RATINGS                                                      | E3D4                  |                              |      |

| Operating Temperature                                                |                       |                              | °C   |

| Ambient                                                              | T <sub>A</sub>        | -40 to 125                   |      |

| Junction                                                             | T <sub>J</sub>        | -40 to 150                   |      |

| Storage Temperature                                                  | T <sub>STG</sub>      | -55 to 150                   | °C   |

|                                                                      |                       |                              | 1    |

- 4. Continuous high side output current rating so long as maximum junction temperature is not exceeded. Calculation of maximum output current using package thermal resistance is required.

- 5. Active clamp energy using single-pulse method (L = 2.0 mH,  $R_L = 0 \text{ Ohm}$ ,  $V_{PWR} = 14 \text{ V}$ ,  $T_J = 150 \,^{\circ}\text{C}$  initial).

- 6. ESD testing is performed in accordance with the Human Body Model (HBM) ( $C_{ZAP} = 100 \text{ pF}$ ,  $R_{ZAP} = 1500 \text{ Ohm}$ ), the Machine Model (MM) ( $C_{ZAP} = 200 \text{ pF}$ ,  $R_{ZAP} = 0 \text{ Ohm}$ ), and the Charge Device Model (CDM), Robotic ( $C_{ZAP} = 4.0 \text{ pF}$ ).

- 7. Input/Output pins are: IN[0:3], RST, FSI, CSNS, SI, SCLK, CS, SO, FS

#### Table 4. Maximum Ratings (continued)

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                        | Symbol            | Value   | Unit |

|--------------------------------------------------------------------------------|-------------------|---------|------|

| THERMAL RESISTANCE                                                             |                   |         |      |

| Thermal Resistance <sup>(8)</sup>                                              |                   |         | °C/W |

| Junction to Case                                                               | $R_{	hetaJC}$     | <1.0    |      |

| Junction to Ambient                                                            | $R_{	hetaJA}$     | 30      |      |

| Peak Package Reflow Temperature During Reflow <sup>(9)</sup> , <sup>(10)</sup> | T <sub>PPRT</sub> | Note 10 | °C   |

- 8. Device mounted on a 2s2p test board per JEDEC JESD51-2. 15 °C/W of R<sub>θ,JA</sub> can be reached in a real application case (4 layers board).

- 9. Pin soldering temperature limit is for 40 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 10. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts (i.e. MC33xxxD enter 33xxx), and review parametrics.

#### STATIC ELECTRICAL CHARACTERISTICS

#### **Table 5. Static Electrical Characteristics**

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                                                                     | Symbol                   | Min | Тур | Max | Unit                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|-----|-----|----------------------|

| POWER INPUTS                                                                                                                                                                       | l l                      |     |     | l . |                      |

| Battery Supply Voltage Range                                                                                                                                                       | $V_{PWR}$                |     |     |     | V                    |

| Fully Operational                                                                                                                                                                  |                          | 6.0 | _   | 20  |                      |

| Extended mode <sup>(11)</sup>                                                                                                                                                      |                          | 4.0 | _   | 28  |                      |

| Battery Clamp Voltage <sup>(12)</sup>                                                                                                                                              | V <sub>PWR(CLAMP)</sub>  | 41  | 47  | 53  | V                    |

| V <sub>PWR</sub> Operating Supply Current                                                                                                                                          | I <sub>PWR(ON)</sub>     |     |     |     | mA                   |

| Outputs commanded ON, HS[0:3] open, $IN[0:3] > V_{IH}$                                                                                                                             | , ,                      | -   | 6.5 | 20  |                      |

| V <sub>PWR</sub> Supply Current                                                                                                                                                    | I <sub>PWR(SBY)</sub>    |     |     |     | mA                   |

| Outputs commanded OFF, OFF Open-load Detection Disabled, HS[0:3] shorted to the ground with $V_{DD}$ = 5.5 V WAKE > $V_{IH}$ or $\overline{RST}$ > $V_{IH}$ and IN[0:3] < $V_{IL}$ |                          | -   | 6.5 | 7.5 |                      |

| Sleep State Supply Current $V_{PWR}$ = 12V, $\overline{RST}$ = WAKE = IN[0:3] < $V_{IL}$ , HS[0:3] shorted to the ground $T_A$ = 25°C                                              | I <sub>PWR(SLEEP)</sub>  |     |     |     | μА                   |

| T <sub>A</sub> = 85°C                                                                                                                                                              |                          | _   | 1.0 | 5.0 |                      |

|                                                                                                                                                                                    |                          | _   | _   | 30  |                      |

| V <sub>DD</sub> Supply Voltage                                                                                                                                                     | $V_{DD(ON)}$             | 3.0 | _   | 5.5 | V                    |

| V <sub>DD</sub> Supply Current at V <sub>DD</sub> = 5.5 V                                                                                                                          | I <sub>DD(ON)</sub>      |     |     |     | mA                   |

| No SPI Communication                                                                                                                                                               |                          | _   | 1.6 | 2.2 |                      |

| 8.0 MHz SPI Communication <sup>(13)</sup>                                                                                                                                          |                          | _   | 5.0 | _   |                      |

| V <sub>DD</sub> Sleep State Current at V <sub>DD</sub> = 5.5 V                                                                                                                     | I <sub>DD(SLEEP)</sub>   | -   | _   | 5.0 | μА                   |

| Overvoltage Shutdown Threshold                                                                                                                                                     | V <sub>PWR(OV)</sub>     | 28  | 32  | 36  | V                    |

| Overvoltage Shutdown Hysteresis                                                                                                                                                    | V <sub>PWR(OVHYS)</sub>  | 0.2 | 0.8 | 1.5 | V                    |

| Undervoltage Shutdown Threshold <sup>(14)</sup>                                                                                                                                    | V <sub>PWR(UV)</sub>     | 3.3 | 3.9 | 4.3 | V                    |

| V <sub>PWR</sub> and V <sub>DD</sub> Power on Reset Threshold                                                                                                                      | V <sub>SUPPLY(POR)</sub> | 0.5 | -   | 0.9 | V <sub>PWR(UV)</sub> |

| Recovery Undervoltage Threshold                                                                                                                                                    | V <sub>PWR(UV)_UP</sub>  | 3.4 | 4.1 | 4.5 | V                    |

| $V_{DD}$ Supply Failure Threshold (for $V_{PWR} > V_{PWR(UV)}$ )                                                                                                                   | V <sub>DD(FAIL)</sub>    | 2.2 | 2.5 | 2.8 | ٧                    |

- 11. In extended mode, the functionality is guaranteed but not the electrical parameters. From 4.0 V to 6.0 V voltage range, the device is only protected with the thermal shutdown detection.

- 12. Measured with the outputs open.

- 13. Typical value guaranteed per design.

- 14. Output will automatically recover with time limited autoretry to instructed state when V<sub>PWR</sub> voltage is restored to normal as long as the V<sub>PWR</sub> degradation level did not go below the undervoltage power-ON reset threshold. This applies to all internal device logic that is supplied by V<sub>PWR</sub> and assumes that the external V<sub>DD</sub> supply is within specification.

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                  | Symbol                 | Min | Тур | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------|------------------------|-----|-----|------|------|

| OUTPUTS HS0 TO HS3                                                                                              |                        |     |     | •    | •    |

| HS[0,1] Output Drain-to-Source ON Resistance (I <sub>HS</sub> = 5.0 A, T <sub>A</sub> = 25°C)                   | R <sub>DS_01(ON)</sub> |     |     |      | mOhm |

| V <sub>PWR</sub> = 4.5 V                                                                                        | _ ` '                  | _   | _   | 36   |      |

| V <sub>PWR</sub> = 6.0 V                                                                                        |                        | -   | _   | 16   |      |

| V <sub>PWR</sub> = 10 V                                                                                         |                        | _   | _   | 10   |      |

| V <sub>PWR</sub> = 13 V                                                                                         |                        | -   | -   | 10   |      |

| HS[0,1] Output Drain-to-Source ON Resistance (I <sub>HS</sub> = 5.0 A, T <sub>A</sub> = 150°C)                  | R <sub>DS_01(ON)</sub> |     |     |      | mOhm |

| V <sub>PWR</sub> = 4.5 V                                                                                        | _ ` ,                  | -   | _   | 62   |      |

| V <sub>PWR</sub> = 6.0 V                                                                                        |                        | -   | _   | 27   |      |

| V <sub>PWR</sub> = 10 V                                                                                         |                        | _   | _   | 17   |      |

| V <sub>PWR</sub> = 13 V                                                                                         |                        | -   | -   | 17   |      |

| HS[0,1] Output Source-to-Drain ON Resistance (I <sub>HS</sub> = -5.0 A, V <sub>PWR</sub> = -18) <sup>(15)</sup> | R <sub>SD_01(ON)</sub> |     |     |      | mOhm |

| T <sub>A</sub> = 25°C                                                                                           | _ ` '                  | _   | _   | 15   |      |

| T <sub>A</sub> = 150°C                                                                                          |                        | _   | -   | 20   |      |

| HS[2,3] Output Drain-to-Source ON Resistance (I <sub>HS</sub> = 5.0 A, T <sub>A</sub> = 25°C)                   | R <sub>DS_23(ON)</sub> |     |     |      | mOhm |

| V <sub>PWR</sub> = 4.5 V                                                                                        | _ ` ,                  | _   | _   | 126  |      |

| V <sub>PWR</sub> = 6.0 V                                                                                        |                        | -   | _   | 56   |      |

| V <sub>PWR</sub> = 10 V                                                                                         |                        | _   | _   | 35   |      |

| V <sub>PWR</sub> = 1.0 V                                                                                        |                        | -   | -   | 35   |      |

| HS[2,3] Output Drain-to-Source ON Resistance (I <sub>HS</sub> = 5.0 A, T <sub>A</sub> = 150°C)                  | R <sub>DS_23(ON)</sub> |     |     |      | mOhm |

| V <sub>PWR</sub> = 4.5 V                                                                                        |                        | -   | _   | 217  |      |

| V <sub>PWR</sub> = 6.0 V                                                                                        |                        | -   | _   | 94.5 |      |

| V <sub>PWR</sub> = 10 V                                                                                         |                        | -   | _   | 59.5 |      |

| V <sub>PWR</sub> = 13 V                                                                                         |                        | _   | -   | 59.5 |      |

| HS[2,3] Output Source-to-Drain ON Resistance (I <sub>HS</sub> = -5.0 A, V <sub>PWR</sub> = -18) <sup>(15)</sup> | R <sub>SD_23(ON)</sub> |     |     |      | mOhm |

| T <sub>A</sub> = 25°C                                                                                           | = · /                  | _   | _   | 52.5 |      |

| T <sub>A</sub> = 150°C                                                                                          |                        | -   | _   | 70   |      |

| HS[0,1] Maximum Severe Short-Circuit Impedance Detection <sup>(16)</sup>                                        | R <sub>SHORT_01</sub>  | 28  | 64  | 100  | mOhm |

| HS[2,3] Maximum Severe Short-Circuit Impedance Detection <sup>(16)</sup>                                        | R <sub>SHORT_23</sub>  | 70  | 160 | 200  | mOhm |

- 15. Source-Drain ON Resistance (Reverse Drain-to-Source ON Resistance) with negative polarity  $V_{PWR}$ .

- 16. Short-circuit impedance calculated from HS[0:3] to GND pins. Value guaranteed per design.

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                    | Symbol                 | Min        | Тур     | Max        | Unit |

|---------------------------------------------------------------------------------------------------|------------------------|------------|---------|------------|------|

| OUTPUTS HS0 TO HS3 (CONTINUED)                                                                    | <u> </u>               |            |         |            |      |

| HS[0,1] Output Overcurrent Detection Levels (6.0 V ≤ V <sub>HS[0:3]</sub> ≤ 20 V)                 |                        |            |         |            | Α    |

| 28 W bit = 0                                                                                      | OCHI1_0                | 78         | 94.0    | 110        |      |

|                                                                                                   | OCHI2_0                | 50         | 60.0    | 70         |      |

|                                                                                                   | OC1_0                  | 44.1       | 52.5    | 60.9       |      |

|                                                                                                   | OC2_0                  | 37.8       | 45.0    | 52.2       |      |

|                                                                                                   | OC3_0                  | 31.5       | 37.5    | 43.5       |      |

|                                                                                                   | OC4_0                  | 25.2       | 30.0    | 34.8       |      |

|                                                                                                   | OCLO4_0                | 18.9       | 22.5    | 26.1       |      |

|                                                                                                   | OCLO3_0                | 12.6       | 15.0    | 17.4       |      |

|                                                                                                   | OCLO2_0                | 10.0       | 12.0    | 14.0       |      |

|                                                                                                   | OCLO1_0                | 6.4        | 8.0     | 9.6        |      |

|                                                                                                   | 00201_0                | 0.1        | 0.0     | 0.0        |      |

| 20 M bit = 4                                                                                      | OCHI1_1                | 39         | 47.0    | 55         |      |

| 28 W bit = 1                                                                                      | OCHI2_1                | 25         | 30.0    | 35         |      |

|                                                                                                   | OC1_1                  | 22.0       | 26.2    | 30.5       |      |

|                                                                                                   | OC1_1<br>OC2_1         | 18.9       | 22.5    | 26.1       |      |

|                                                                                                   | OC2_1                  | 15.7       | 18.7    | 21.8       |      |

|                                                                                                   | OC3_1<br>OC4_1         | 12.6       | 15.0    | 17.4       |      |

|                                                                                                   | OC4_1                  | 4.5        | 6.0     | 7.5        |      |

|                                                                                                   | OCLO4_1<br>OCLO3_1     |            | 6.0     | 7.5<br>7.5 |      |

|                                                                                                   | OCLO3_1<br>OCLO2_1     | 4.5<br>4.5 |         | 7.5<br>7.5 |      |

|                                                                                                   | _                      |            | 6.0     |            |      |

| (47)                                                                                              | OCLO1_1                | 3.0        | 4.0     | 5.0        |      |

| HS[0,1] Current Sense Ratio (6.0 V $\leq$ HS[0:3] $\leq$ 20 V, CSNS $\leq$ 5.0 V) <sup>(17)</sup> |                        |            |         |            | _    |

| 28 W bit = 0                                                                                      |                        |            |         |            |      |

| CSNS_ratio bit = 0                                                                                | C <sub>SR0_0</sub>     | -          | 1/8900  | -          |      |

| CSNS_ratio bit = 1                                                                                | C <sub>SR1_0</sub>     | _          | 1/53000 | _          |      |

| 28 W bit = 1                                                                                      | C <sub>SR0_1</sub>     | _          | 1/4450  | _          |      |

| CSNS_ratio bit = 0                                                                                | C <sub>SR1_1</sub>     | _          | 1/26500 | _          |      |

| CSNS_ratio bit = 1                                                                                |                        |            |         |            |      |

| HS[0,1] Current Sense Ratio (CSR0) Accuracy (6.0 V $\leq$ VHS[0:3] $\leq$ 20 V) with 28W bit = 0  | C <sub>SR0_0_ACC</sub> |            |         |            | %    |

| Output Current                                                                                    |                        | -12        | _       | 12         |      |

| 12.5 A                                                                                            |                        | -13        | _       | 13         |      |

| 5.0 A                                                                                             |                        | -16        | _       | 16         |      |

| 3.0 A                                                                                             |                        | -20        | _       | 20         |      |

| 1.5 A                                                                                             |                        | 20         |         | 20         |      |

## Notes

17. Current sense ratio =  $I_{CSNS}/I_{HS[0:3]}$

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                       | Symbol                          | Min                       | Тур                   | Max                   | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------|-----------------------|-----------------------|------|

| OUTPUTS HS0 TO HS3 (CONTINUED)                                                                                                       |                                 |                           |                       |                       |      |

| HS[0,1] Current Sense Ratio ( $C_{SR0}$ ) Accuracy (6.0 V $\leq$ V <sub>HS</sub> $\leq$ 20 V) with 28 W bit = 1                      | C <sub>SR0_1_ACC</sub>          |                           |                       |                       | %    |

| Output Current                                                                                                                       |                                 |                           |                       |                       |      |

| 3.0 A                                                                                                                                |                                 | -16                       | _                     | 16                    |      |

| 1.5 A                                                                                                                                |                                 | -20                       | _                     | 20                    |      |

| HS[0,1] Current Recopy Accuracy with one calibration point (6.0 V $\leq$ V <sub>HS[0:3]</sub> $\leq$ 20 V) <sup>(18)</sup>           | C <sub>SR0_0_ACC(</sub>         | -5.0                      | _                     | 5.0                   | %    |

| Output Current                                                                                                                       | ,                               |                           |                       |                       |      |

| 5.0 A                                                                                                                                |                                 |                           |                       |                       |      |

| HS[0,1] $C_{SR0}$ Current Recopy Temperature Drift (6.0 V $\leq$ V <sub>HS[0:3]</sub> $\leq$ 20 V) with 28 W bit = 0 <sup>(19)</sup> | Δ(C <sub>SR0_0</sub> )/<br>Δ(T) |                           |                       |                       | %/°C |

| Output Current                                                                                                                       |                                 |                           |                       | 0.04                  |      |

| 5.0 A                                                                                                                                |                                 |                           |                       |                       |      |

| HS[0,1] Current Sense Ratio ( $C_{SR1}$ ) Accuracy (6.0 V $\leq$ V <sub>HS[0:3]</sub> $\leq$ 20 V) with 28 W bit = 0                 | C <sub>SR1_0_ACC</sub>          |                           |                       |                       | %    |

| Output Current                                                                                                                       |                                 | -17                       | _                     | +17                   |      |

| 12.5 A                                                                                                                               |                                 | -12                       | _                     | +12                   |      |

| 75 A                                                                                                                                 |                                 | . –                       |                       |                       |      |

| Current Sense Clamp Voltage                                                                                                          | V <sub>CL(CSNS)</sub>           |                           |                       |                       | V    |

| CSNS Open; $I_{HS[0:3]} = 5.0 \text{ A with } C_{SR0} \text{ ratio}$                                                                 |                                 | V <sub>DD</sub> +0.2<br>5 | -                     | V <sub>DD</sub> +1.0  |      |

| OFF Open-Load Detection Source Current <sup>(20)</sup>                                                                               | I <sub>OLD(OFF)</sub>           | 30                        | _                     | 100                   | μА   |

| OFF Open-Load Fault Detection Voltage Threshold                                                                                      | V <sub>OLD(THRES)</sub>         | 2.0                       | 3.0                   | 4.0                   | V    |

| ON Open-Load Fault Detection Current Threshold                                                                                       | I <sub>OLD(ON)</sub>            | 100                       | 300                   | 600                   | mA   |

| ON Open-Load Fault Detection Current Threshold with LED                                                                              | I <sub>OLD(ON LED)</sub>        |                           |                       |                       | mA   |

| $V_{HS[0:3]} = V_{PWR} - 0.75 V$                                                                                                     | 015(011_125)                    | 2.5                       | 5.0                   | 10                    |      |

| Output Short to V <sub>PWR</sub> Detection Voltage Threshold                                                                         | V <sub>OSD(THRES)</sub>         |                           |                       |                       | V    |

| Output programmed OFF                                                                                                                | 555(1111120)                    | V <sub>PWR</sub> -<br>1.2 | V <sub>PWR</sub> -0.8 | V <sub>PWR</sub> -0.4 |      |

| Output Negative Clamp Voltage                                                                                                        | V <sub>CL</sub>                 |                           |                       |                       | V    |

| $0.5~\text{A} \le \text{I}_{\text{HS}[0:3]} \le 5.0~\text{A}$ , Output programmed OFF                                                | 32                              | -22                       | _                     | -16                   |      |

| Output Overtemperature Shutdown for 4.5 V < VPWR < 28 V                                                                              | T <sub>SD</sub>                 | 155                       | 175                   | 195                   | °C   |

- 18. Based on statistical analysis. It is not production tested.

- Based on statistical data: delta(C<sub>SR0</sub>)/delta(T) = {(measured I<sub>CSNS</sub> at T<sub>1</sub> measured I<sub>CSNS</sub> at T<sub>2</sub>)/measured I<sub>CSNS</sub> at room}/{T<sub>1</sub>-T<sub>2</sub>}.

No production tested.

- 20. Output OFF Open-Load Detection Current is the current required to flow through the load for the purpose of detecting the existence of an open-load condition when the specific output is commanded OFF. Pull-up current is measured for V<sub>HS</sub> = V<sub>OLD(THRES)</sub>.

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                             | Symbol                  | Min  | Тур     | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------|------|---------|------|------|

| OUTPUTS HS0 TO HS3 (CONTINUED)                                                                                             |                         |      | •       |      |      |

| HS[2,3] Output Overcurrent Detection Levels (6.0 V ≤ V <sub>HS[0:3]</sub> ≤ 20 V)                                          |                         |      |         |      | Α    |

|                                                                                                                            | OCHI1_1                 | 39.5 | 47.0    | 54.5 |      |

|                                                                                                                            | OCHI2_1                 | 25.2 | 30.0    | 34.8 |      |

|                                                                                                                            | OC1_1                   | 22.0 | 26.2    | 30.5 |      |

|                                                                                                                            | OC2_1                   | 18.9 | 22.5    | 26.1 |      |

|                                                                                                                            | OC3_1                   | 15.7 | 18.7    | 21.7 |      |

|                                                                                                                            | OC4_1                   | 12.6 | 15.0    | 17.4 |      |

|                                                                                                                            | OCLO4_1                 | 9.4  | 11.2    | 13.0 |      |

|                                                                                                                            | OCLO3_1                 | 6.3  | 7.5     | 8.7  |      |

|                                                                                                                            | OCLO2_1                 | 5.0  | 6.0     | 7.0  |      |

|                                                                                                                            | OCLO1_1                 | 3.2  | 4.0     | 4.8  |      |

| HS[2,3] Current Sense Ratio $(6.0 \text{ V} \le \text{HS}[0:3] \le 20 \text{ V}, \text{ CSNS} \le 5.0 \text{ V})^{(21)}$   |                         |      |         |      | _    |

| CSNS_ratio bit = 0                                                                                                         | C <sub>SR0_1</sub>      | _    | 1/4350  | _    |      |

| CSNS_ratio bit = 1                                                                                                         | C <sub>SR1_1</sub>      | _    | 1/25500 | _    |      |

| HS[2,3] Current Sense Ratio (C <sub>SR0</sub> ) Accuracy (6.0 V ≤ V <sub>HS[0:3]</sub> ≤ 20 V)                             | C <sub>SR0_0_ACC</sub>  |      |         |      | %    |

| Output Current                                                                                                             | 0.10_0_1.00             |      |         |      |      |

| 6.25 A                                                                                                                     |                         | -12  | _       | 12   |      |

| 2.5 A                                                                                                                      |                         | -13  | _       | 13   |      |

| 1.5 A                                                                                                                      |                         | -16  | _       | 16   |      |

| 0.75 A                                                                                                                     |                         | -20  | _       | 20   |      |

| HS[2,3] Current Recopy Accuracy with one calibration point (6.0 V $\leq$ V <sub>HS[0:3]</sub> $\leq$ 20 V) <sup>(22)</sup> | C <sub>SR0_0_ACC(</sub> | -5.0 | _       | 5.0  | %    |

| Output Current                                                                                                             | OAL)                    |      |         |      |      |

| 2.5 A                                                                                                                      |                         |      |         |      |      |

- 21. Current sense ratio =  $I_{CSNS}/I_{HS[0:3]}$

- 22. Based on statistical analysis. It is not production tested.

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

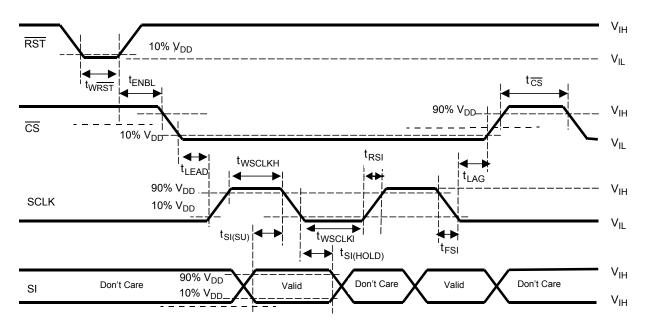

| Characteristic                                                                                                                                      | Symbol                | Min                  | Тур      | Max                  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|----------|----------------------|------|

| CONTROL INTERFACE                                                                                                                                   | •                     |                      |          |                      |      |

| Input Logic High Voltage <sup>(23)</sup>                                                                                                            | V <sub>IH</sub>       | 2.0                  | _        | V <sub>DD</sub> +0.3 | V    |

| Input Logic Low Voltage <sup>(23)</sup>                                                                                                             | V <sub>IL</sub>       | -0.3                 | 1        | 0.8                  | V    |

| Input Logic Pull-down Current (SCLK, SI) <sup>(26)</sup>                                                                                            | I <sub>DWN</sub>      | 5.0                  | -        | 20                   | μА   |

| Input Logic Pull-up Current (CS) (27)                                                                                                               | I <sub>UP</sub>       | 5.0                  | -        | 20                   | μА   |

| SO, FS Tri-State Capacitance <sup>(24)</sup>                                                                                                        | C <sub>SO</sub>       | _                    | -        | 20                   | pF   |

| Input Logic Pull-down Resistor (RST, WAKE and IN[0:3])                                                                                              | R <sub>DWN</sub>      | 125                  | 250      | 500                  | kOhm |

| Input Capacitance <sup>(24)</sup>                                                                                                                   | C <sub>IN</sub>       | _                    | 4.0      | 12                   | pF   |

| Wake Input Clamp Voltage <sup>(25)</sup> , I <sub>CL(WAKE)</sub> < 2.5 mA                                                                           | V <sub>CL(WAKE)</sub> |                      |          |                      | V    |

| 10XS3435B                                                                                                                                           |                       | 18                   | 25       | 32                   |      |

| 10XS3435D                                                                                                                                           |                       | 20                   | 27       | 35                   |      |

| Wake Input Forward Voltage                                                                                                                          | V <sub>F(WAKE)</sub>  |                      |          |                      | V    |

| $I_{CL(WAKE)} = -2.5 \text{ mA}$                                                                                                                    |                       | -2.0                 | _        | -0.3                 |      |

| SO High-state Output Voltage                                                                                                                        | V <sub>SOH</sub>      |                      |          |                      | V    |

| I <sub>OH</sub> = 1.0 mA                                                                                                                            |                       | V <sub>DD</sub> -0.4 | _        | -                    |      |

| SO and FS Low-state Output Voltage                                                                                                                  | V <sub>SOL</sub>      |                      |          |                      | V    |

| I <sub>OL</sub> = -1.0 mA                                                                                                                           |                       | -                    | _        | 0.4                  |      |

| SO, CSNS and FS Tri-state Leakage Current                                                                                                           | I <sub>SO(LEAK)</sub> |                      |          |                      | μА   |

| $\overline{\text{CS}}$ = V <sub>IH</sub> and 0 V $\leq$ V <sub>SO</sub> $\leq$ V <sub>DD</sub> , or $\overline{\text{FS}}$ = 5.5 V, or CSNS = 0.0 V |                       | -2.0                 | 0        | 2.0                  |      |

| FSI External Pull-down Resistance <sup>(28)</sup>                                                                                                   |                       |                      |          |                      | kOhm |

| Watchdog Disabled                                                                                                                                   | RFS                   | _                    | 0        | 1.0                  |      |

| Watchdog Enabled                                                                                                                                    |                       | 10                   | Infinite | _                    |      |

- 23. Upper and lower logic threshold voltage range applies to SI,  $\overline{\text{CS}}$ , SCLK,  $\overline{\text{RST}}$ , IN[0:3] and WAKE input signals. The WAKE and  $\overline{\text{RST}}$  signals may be supplied by a derived voltage referenced to V<sub>PWR</sub>.

- 24. Input capacitance of SI, CS, SCLK, RST, IN[0:3] and WAKE. This parameter is guaranteed by process monitoring but is not production tested.

- 25. The current must be limited by a series resistance when using voltages > 7.0 V.

- 26. Pull-down current is with  $V_{SI} \ge 1.0 \text{ V}$  and  $V_{SCLK} \ge 1.0 \text{ V}$ .

- 27. Pull-up current is with  $V_{\overline{CS}} \le 2.0 \text{ V}$ .  $\overline{CS}$  has an active internal pull-up to  $V_{DD}$ .

- 28. In Fail-Safe HS[0:3] depends respectively on ON[0:3]. FSI has an active internal pull-up to  $V_{REG} \sim 3.0 \text{ V}$ .

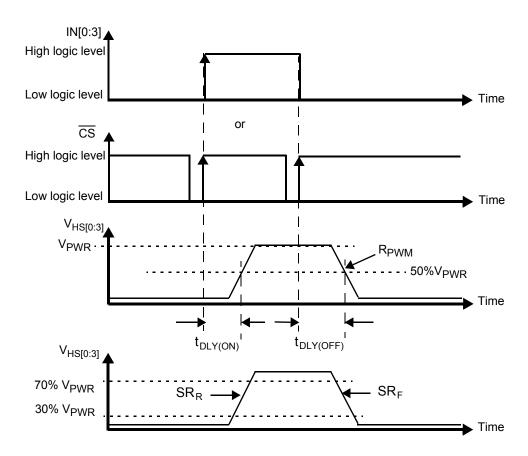

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

#### **Table 6. Dynamic Electrical Characteristics**

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                                                                                                   | Symbol              | Min  | Тур  | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|-----|------|

| POWER OUTPUT TIMING HS0 TO HS3                                                                                                                                                                                   |                     |      |      | l   | .1   |

| Output Rising Medium Slew Rate (medium speed slew rate/SR[1:0] = $00$ ) <sup>(29)</sup> $V_{PWR}$ = 14 V                                                                                                         | SR <sub>R_00</sub>  | 0.15 | 0.3  | 0.6 | V/µs |

| Output Rising Slow Slew Rate (low speed slew rate/SR[1:0] = 01) $^{(29)}$<br>V <sub>PWR</sub> = 14 V                                                                                                             | SR <sub>R_01</sub>  | 0.07 | 0.15 | 0.3 | V/μs |

| Output Falling Fast Slew Rate (high speed slew rate/SR[1:0] = 10) <sup>(29)</sup> $V_{PWR} = 14 \text{ V}$                                                                                                       | SR <sub>R_10</sub>  | 0.3  | 0.6  | 1.2 | V/μs |

| Output Falling Medium Slew Rate (medium speed slew rate/SR[1:0] = $00$ ) <sup>(29)</sup> $V_{PWR}$ = 14 V                                                                                                        | SR <sub>F_00</sub>  | 0.15 | 0.3  | 0.6 | V/μs |

| Output Falling Slow Slew Rate (low speed slew rate/SR[1:0] = 01) <sup>(29)</sup> V <sub>PWR</sub> = 14 V                                                                                                         | SR <sub>F_01</sub>  | 0.07 | 0.15 | 0.3 | V/μs |

| Output Rising Fast Slew Rate (high speed slew rate/SR[1:0] = 10) <sup>(29)</sup> $V_{PWR} = 14 \text{ V}$                                                                                                        | SR <sub>F_10</sub>  | 0.3  | 0.6  | 1.2 | V/μs |

| HS[2:3] Outputs Turn-ON and OFF Delay Times <sup>(30)(31)</sup> V <sub>PWR</sub> = 14 V for medium speed slew rate (SR[1:0] = 00)                                                                                | t <sub>DLY_23</sub> | 35   | 60   | 85  | μs   |

| HS[0:1] Outputs Turn-ON and OFF Delay Times <sup>(30)(31)</sup> V <sub>PWR</sub> = 14 V for medium speed slew rate (SR[1:0] = 00)                                                                                | t <sub>DLY_12</sub> | 45   | 70   | 95  | μs   |

| Driver Output Matching Slew Rate ( $SR_R/SR_F$ )<br>$V_{PWR} = 14 \text{ V} @ 25^{\circ}\text{C}$ and for medium speed slew rate ( $SR[1:0] = 00$ )                                                              | ΔSR                 | 0.8  | 1.0  | 1.2 |      |

| HS[0:1] Driver Output Matching Time ( $t_{DLY(ON)} - t_{DLY(OFF)}$ ) $V_{PWR} = 14 \text{ V}, f_{PWM} = 240 \text{ Hz}, \text{ PWM duty cycle} = 50\%, @ 25°C \text{ for medium speed slew rate (SR[1:0] = 00)}$ | Δt <sub>RF_01</sub> | -25  | 0    | 25  | μs   |

| HS[2:3] Driver Output Matching Time $(t_{DLY(ON)} - t_{DLY(OFF)})$<br>$V_{PWR} = 14 \text{ V}, f_{PWM} = 240 \text{ Hz}, PWM duty cycle} = 50\%, @ 25°C for medium speed slew rate (SR[1:0] = 00)$               | Δt <sub>RF_23</sub> | -20  | 5    | 30  | μs   |

- 29. Rise and Fall Slew Rates measured across a 5.0 Ohm resistive load at high side output = 30% to 70% (see Figure 4, page 22).

- 30. Turn-ON delay time measured from rising edge of any signal (IN[0:3] and  $\overline{\text{CS}}$ ) that would turn the output ON to  $V_{\text{HS}[0:3]} = V_{\text{PWR}}/2$  with  $R_L = 5.0$  Ohm resistive load.

- 31. Turn-OFF delay time measured from falling edge of any signal (IN[0:3] and  $\overline{\text{CS}}$ ) that would turn the output OFF to  $V_{\text{HS}[0:3]} = V_{\text{PWR}}/2$  with  $R_L = 5.0$  Ohm resistive load.

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                    |           | Symbol              | Min | Тур                  | Max | Unit |

|---------------------------------------------------|-----------|---------------------|-----|----------------------|-----|------|

| POWER OUTPUT TIMING HS0 TO HS3 (CONTINUED)        |           | •                   |     |                      |     |      |

| Fault Detection Blanking Time <sup>(32)</sup>     |           | t <sub>FAULT</sub>  |     |                      |     | μS   |

|                                                   | 10XS3435B |                     | -   | 5.0                  | 20  |      |

|                                                   | 10XS3435D |                     | -   | 5.0                  | 10  |      |

| Output Shutdown Delay Time <sup>(33)</sup>        |           | t <sub>DETECT</sub> |     |                      |     | μS   |

|                                                   | 10XS3435B |                     | -   | 7.0                  | 30  |      |

|                                                   | 10XS3435D |                     | -   | 7.0                  | 20  |      |

| CSNS Valid Time <sup>(34)</sup>                   |           | t <sub>CNSVAL</sub> | -   | 70                   | 100 | μS   |

| Watchdog Time-out <sup>(35)</sup>                 |           | t <sub>WDTO</sub>   | 217 | 310                  | 400 | ms   |

| ON Open-Load Fault Cyclic Detection Time with LED |           |                     | -   | f <sub>IN0/128</sub> | -   | ms   |

- 32. Time necessary to report the fault to  $\overline{FS}$  pin.

- 33. Time necessary to switch-off the output in case of OT or OC or SC or UV fault detection (from negative edge of  $\overline{FS}$  pin to HS voltage = 50% of  $V_{PWR}$

- 34. Time necessary for CSNS to be within  $\pm 5\%$  of the targeted value (from HS voltage = 50% of  $V_{PWR}$  to  $\pm 5\%$  of the targeted CSNS value).

- 35. For FSI open, the Watchdog timeout delay measured from the rising edge of RST, to HS[0,2] output state depend on the corresponding input command.

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                        | Symbol                                     | Min   | Тур   | Max   | Unit |

|-------------------------------------------------------|--------------------------------------------|-------|-------|-------|------|

| POWER OUTPUT TIMING HS0 TO HS3 (CONTINUED)            | <b>-</b>                                   |       |       |       |      |

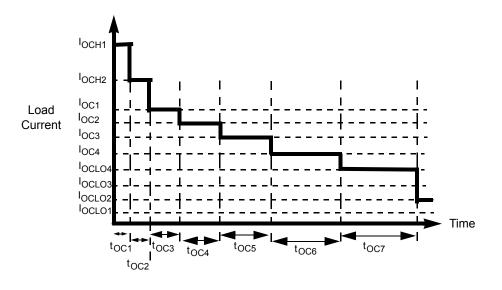

| HS[0,1] Output Overcurrent Time Step for 28 W bit = 0 |                                            |       |       |       | ms   |

| OC[1:0] = 00 (slow by default)                        | t <sub>OC1_00</sub>                        | 4.40  | 6.30  | 8.02  |      |

|                                                       | t <sub>OC2_00</sub>                        | 1.62  | 2.32  | 3.00  |      |

|                                                       | t <sub>OC3_00</sub>                        | 2.10  | 3.00  | 3.90  |      |

|                                                       | t <sub>OC4_00</sub>                        | 2.88  | 4.12  | 5.36  |      |

|                                                       | t <sub>OC5_00</sub>                        | 4.58  | 6.56  | 8.54  |      |

|                                                       | t <sub>OC6_00</sub>                        | 10.16 | 14.52 | 18.88 |      |

|                                                       | t <sub>OC7_00</sub>                        | 73.2  | 104.6 | 134.0 |      |

| OC[1:0] = 01 (fast)                                   | t <sub>OC1_01</sub>                        | 1.10  | 1.57  | 2.00  |      |

|                                                       | t <sub>OC2_01</sub>                        | 0.40  | 0.58  | 0.75  |      |

|                                                       | t <sub>OC3_01</sub>                        | 0.52  | 0.75  | 0.98  |      |

|                                                       | t <sub>OC4_01</sub>                        | 0.72  | 1.03  | 1.34  |      |

|                                                       | t <sub>OC5_01</sub>                        | 1.14  | 1.64  | 2.13  |      |

|                                                       | t <sub>OC6_01</sub>                        | 2.54  | 3.63  | 4.72  |      |

|                                                       | t <sub>OC7_01</sub>                        | 18.2  | 26.1  | 34.0  |      |

| OC[1:0] = 10 (medium)                                 | t <sub>OC1_10</sub>                        | 2.20  | 3.15  | 4.01  |      |

|                                                       | t <sub>OC2_10</sub>                        | 0.81  | 1.16  | 1.50  |      |

|                                                       | t <sub>OC3_10</sub>                        | 1.05  | 1.50  | 1.95  |      |

|                                                       | t <sub>OC4_10</sub>                        | 1.44  | 2.06  | 2.68  |      |

|                                                       | t <sub>OC5_10</sub>                        | 2.29  | 3.28  | 4.27  |      |

|                                                       | t <sub>OC6_10</sub>                        | 5.08  | 7.26  | 9.44  |      |

|                                                       | t <sub>OC7_10</sub>                        | 36.6  | 52.3  | 68.0  |      |

| OC[1:0] = 11 (very slow)                              | too                                        | 8.8   | 12.6  | 16.4  |      |

|                                                       | t <sub>OC1_11</sub>                        | 3.2   | 4.6   | 21.4  |      |

|                                                       | t <sub>OC2_11</sub>                        | 4.2   | 6.0   | 7.8   |      |

|                                                       | t <sub>OC3_11</sub>                        | 5.7   | 8.2   | 10.7  |      |

|                                                       | t <sub>OC4_11</sub>                        | 9.1   | 13.1  | 17.0  |      |

|                                                       | <sup>t</sup> oc5_11<br>t <sub>oc6_11</sub> | 20.3  | 29.0  | 37.7  |      |

|                                                       | t <sub>OC7_11</sub>                        | 146.4 | 209.2 | 272.0 |      |

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                        | Symbol              | Min   | Тур   | Max   | Unit |

|-------------------------------------------------------|---------------------|-------|-------|-------|------|

| POWER OUTPUT TIMING HS0 TO HS3 (CONTINUED)            |                     |       |       | •     |      |

| HS[0,1] Output Overcurrent Time Step for 28 W bit = 1 |                     |       |       |       | ms   |

| HS[2,3] Output Overcurrent Time Step                  | t <sub>OC1_00</sub> | 3.4   | 4.9   | 6.4   |      |

| OC[1:0] = 00 (slow by default)                        | t <sub>OC2_00</sub> | 1.1   | 1.6   | 2.1   |      |

|                                                       | t <sub>OC3_00</sub> | 1.4   | 2.1   | 2.8   |      |

|                                                       | t <sub>OC4_00</sub> | 2.0   | 2.9   | 3.8   |      |

|                                                       | t <sub>OC5_00</sub> | 3.4   | 4.9   | 6.4   |      |

|                                                       | t <sub>OC6_00</sub> | 8.5   | 12.2  | 15.9  |      |

|                                                       | t <sub>OC7_00</sub> | 62.4  | 89.2  | 116.0 |      |

|                                                       | t <sub>OC1_01</sub> | 0.86  | 1.24  | 1.61  |      |

| OC[1:0] = 01 (fast)                                   | t <sub>OC2_01</sub> | 0.28  | 0.40  | 0.52  |      |

|                                                       | t <sub>OC3_01</sub> | 0.36  | 0.52  | 0.68  |      |

|                                                       | t <sub>OC4_01</sub> | 0.51  | 0.74  | 0.96  |      |

|                                                       | t <sub>OC5_01</sub> | 0.78  | 1.12  | 1.46  |      |

|                                                       | t <sub>OC6_01</sub> | 2.14  | 3.06  | 3.98  |      |

|                                                       | t <sub>OC7_01</sub> | 20.2  | 22.2  | 28.9  |      |

|                                                       | t <sub>OC1_10</sub> | 1.7   | 2.5   | 3.3   |      |

| OC[1:0] = 10 (medium)                                 | t <sub>OC2_10</sub> | 0.5   | 0.8   | 1.0   |      |

|                                                       | t <sub>OC3_10</sub> | 0.7   | 1.0   | 1.3   |      |

|                                                       | t <sub>OC4_10</sub> | 1.0   | 1.5   | 2.0   |      |

|                                                       | t <sub>OC5_10</sub> | 1.7   | 2.5   | 3.3   |      |

|                                                       | t <sub>OC6_10</sub> | 4.2   | 6.1   | 6.0   |      |

|                                                       | t <sub>OC7_10</sub> | 31.2  | 44.6  | 58.0  |      |

|                                                       | t <sub>OC1_11</sub> | 6.8   | 9.8   | 12.8  |      |

| OC[1:0] = 11 (very slow)                              | t <sub>OC2_11</sub> | 2.2   | 3.2   | 16.7  |      |

|                                                       | t <sub>OC3_11</sub> | 2.9   | 4.2   | 5.5   |      |

|                                                       | t <sub>OC4_11</sub> | 4.0   | 5.8   | 7.6   |      |

|                                                       | t <sub>OC5_11</sub> | 6.8   | 9.8   | 12.8  |      |

|                                                       | t <sub>OC6_11</sub> | 17.0  | 24.4  | 31.8  |      |

|                                                       | t <sub>OC7_11</sub> | 124.8 | 178.4 | 232.0 |      |

Table 6. Dynamic Electrical Characteristics (continued)

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                  | Symbol              | Min | Тур | Max  | Unit |

|-------------------------------------------------|---------------------|-----|-----|------|------|

| POWER OUTPUT TIMING HS0 TO HS3 (CONTINUED)      | 1                   |     |     | l    |      |

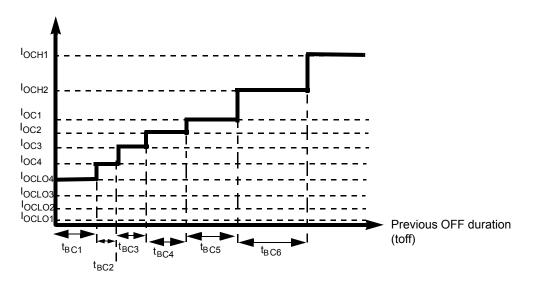

| HS[0,1] Bulb Cooling Time Step for 28 W bit = 0 |                     |     |     |      | ms   |

| CB[1:0] = 00 or 11 (medium)                     | t <sub>BC1_00</sub> | 242 | 347 | 452  |      |

|                                                 | t <sub>BC2_00</sub> | 126 | 181 | 236  |      |

|                                                 | t <sub>BC3_00</sub> | 140 | 200 | 260  |      |

|                                                 | t <sub>BC4_00</sub> | 158 | 226 | 294  |      |

|                                                 | t <sub>BC5_00</sub> | 181 | 259 | 337  |      |

|                                                 | t <sub>BC6_00</sub> | 211 | 302 | 393  |      |

| CB[1:0] = 01 (fast)                             | tagen               | 121 | 173 | 226  |      |

| - ( )                                           | t <sub>BC1_01</sub> | 63  | 90  | 118  |      |

|                                                 | t <sub>BC2_01</sub> | 70  | 100 | 130  |      |

|                                                 | t <sub>BC3_01</sub> | 79  | 113 | 147  |      |

|                                                 | t <sub>BC4_01</sub> | 90  | 129 | 169  |      |

|                                                 | t <sub>BC5_01</sub> | 105 | 151 | 197  |      |