# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## NXP Semiconductors

Data Sheet: Advance Information

## Dual 24 V, 22 mOhm high-side switch

The 22XSD200 device is part of a 24 V dual high-side switch product family with integrated control, and a high number of protective and diagnostic functions. It is designed for industrial applications. The low  $R_{DS(on)}$  channels (<22 m $\Omega$ ) can control different load types; bulbs, solenoids, or DC motors. Control, device configuration, and diagnostics are performed through a 16-bit serial peripheral interface (SPI), allowing easy integration into existing applications. This device is powered by SMARTMOS technology.

Both channels can be controlled individually by external/internal clock signals, or by direct inputs. Using the internal clock allows fully autonomous device operation. Programmable output voltage slew rates (individually programmable) helps improve electromagnetic compatibility (EMC) performance. To avoid shutting off the device upon inrush current, while still being able to closely track the load current, a dynamic overcurrent threshold profile is featured. Switching current of each channel can be sensed with a programmable sensing ratio. Whenever communication with the external microcontroller is lost, the device enters a Fail-safe operation mode, but remains operational, controllable, and protected.

#### Features

- Two fully-protected 22 m $\Omega$  (at 25 °C) high-side switches

- Up to 3.0 A steady-state current per channel

- Separate bulb and DC motor latched overcurrent handling

- Individually programmable internal/external PWM clock signals

Overcurrent, short-circuit, and overtemperature protection with

- programmable autoretry functionsAccurate temperature and current sensing

- Open load detection (channel in OFF and ON state), also for LED applications (7.0 mA typ.)

- Normal operating range: 8.0 V to 36 V, extended range: 6.0 V to 58 V

- 3.3 V and 5.0 V compatible 16-bit SPI port for device control, configuration and diagnostics at rates up to 8.0 MHz

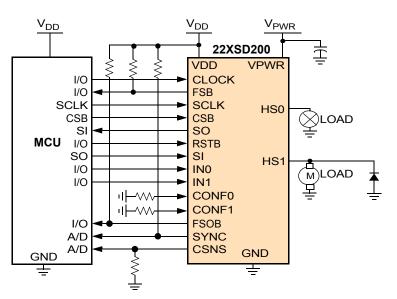

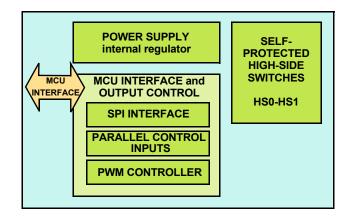

Figure 1. Simplified application diagram

**HIGH-SIDE SWITCH**

#### Applications

- 24 V industrial systems

- Resistive, capacitive, and inductive loads

- Industrial

\* This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

## Orderable parts

#### Table 1. Orderable part variations

| Part number <sup>(1)</sup> | Temperature (T <sub>A</sub> ) | Package    |

|----------------------------|-------------------------------|------------|

| MC22XSD200BEK              | -40 °C to 125 °C              | 32 SOIC-EP |

Notes

1. To order parts in Tape & Reel, add the R2 suffix to the part number.

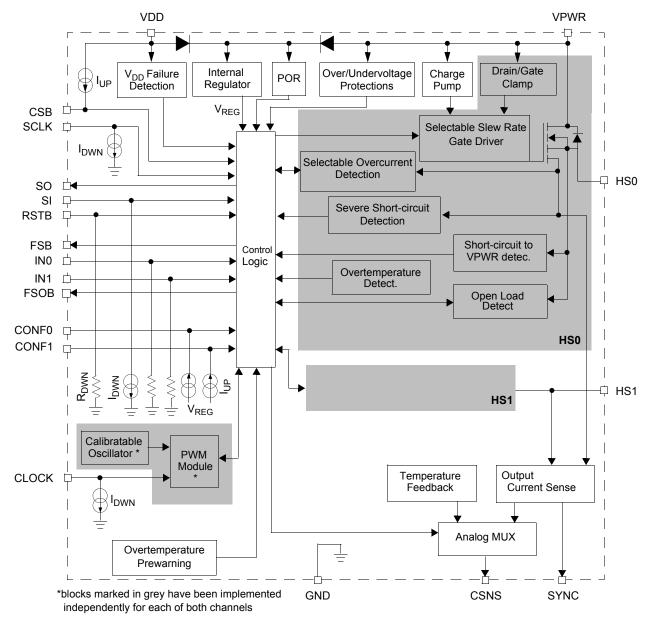

### Internal block diagram

Figure 2. Internal block diagram

## **Table of Contents**

| nternal block diagram                 | .3  |

|---------------------------------------|-----|

| Pin assignment                        | .5  |

| Electrical characteristics            | .7  |

| Maximum ratings                       | .7  |

| Static electrical characteristics     | .9  |

| Dynamic electrical characteristics    | .15 |

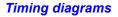

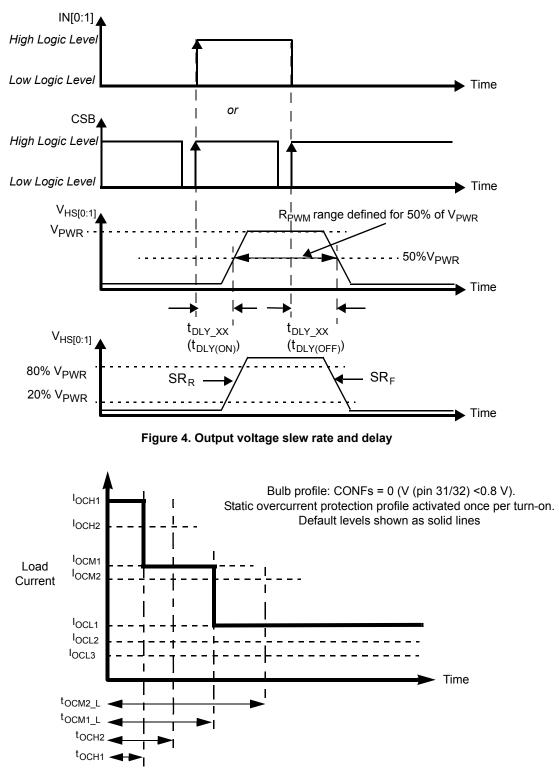

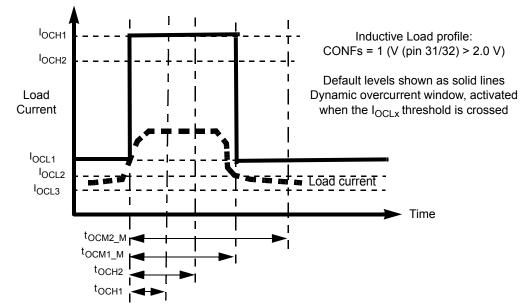

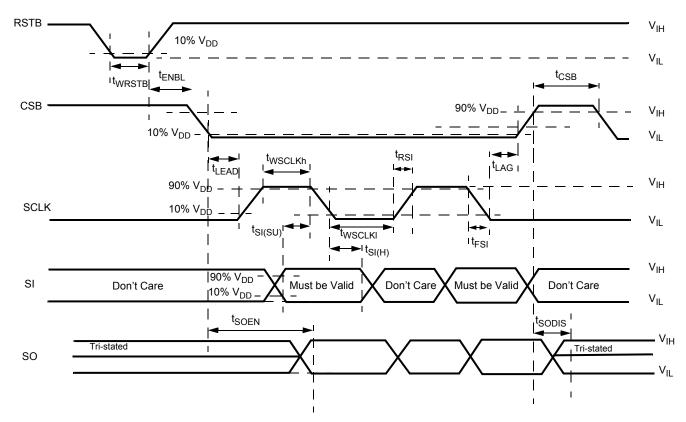

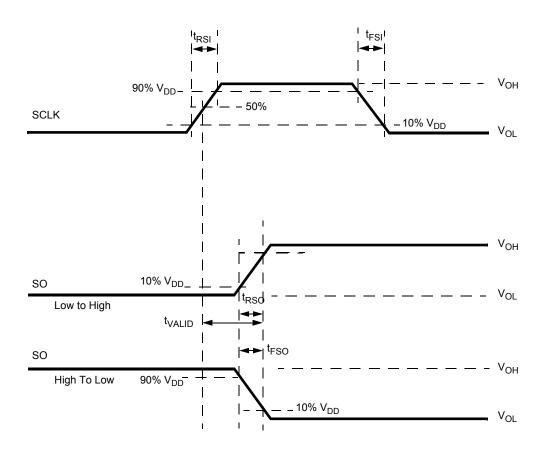

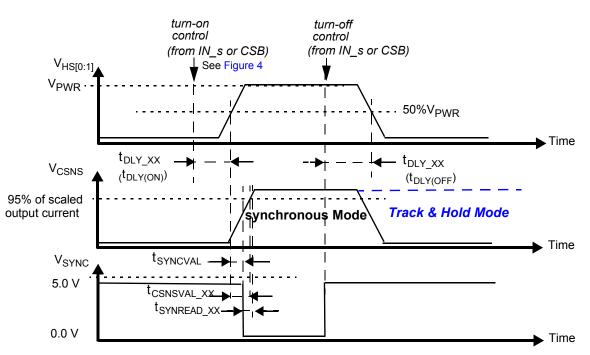

| Timing diagrams                       | .20 |

| Functional description                | .23 |

| Introduction                          | .23 |

| Pin assignment and functions          | .23 |

| Functional internal block description | .25 |

| Functional Device Operation           | .26 |

| Operation and Operating Modes         | .26 |

| Logic commands and SPI registers      |     |

| Typical applications                  |     |

| Packaging                             |     |

| Package mechanical dimensions         |     |

| Revision history                      |     |

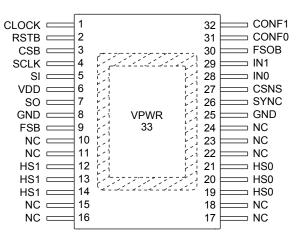

## Pin assignment

#### **Transparent Top View**

#### Figure 3. Device pin assignments

The function of each pin is described in the section Functional description

#### Table 2. 22XSD200 pin description

| Pin<br>number                            | Pin name   | Function | Formal name                                     | Definition                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------|------------|----------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                        | CLOCK      | Input    | PWM Clock                                       | The clock input gives the time-base when the device is operated in external clock/<br>internal PWM mode. This pin has an internal pull-down current source.                                                                                                                                                                          |

| 2                                        | RSTB       | Input    | Reset                                           | This input pin is used to initialize the device's configuration - and fault registers. Reset puts the device in Sleep mode (low current consumption) provided it is not stimulated by direct input signals. This pin is connected to GND by an internal pull-down resistor.                                                          |

| 3                                        | CSB        | Input    | Chip Select (Active<br>Low)                     | This input pin is connected to the SPI chip-select output of an external microcontroller. CSB is internally pulled up to $V_{\text{DD}}$ by a current source $I_{\text{UP}}.$                                                                                                                                                        |

| 4                                        | SCLK       | Input    | Serial Clock                                    | This input pin is to be connected to an external SPI Clock signal. The SCLK pin is internally connected to a pull-down current source I <sub>DWN</sub> .                                                                                                                                                                             |

| 5                                        | SI         | Input    | Serial Input                                    | This input pin receives the SPI input data from an external device (microcontroller or another extreme switch device in case of daisy-chaining). The SI pin is internally connected to a pull-down current source $I_{DWN}$ .                                                                                                        |

| 6                                        | VDD        | Power    | Digital Drain Voltage                           | This is the positive supply pin of the SPI interface.                                                                                                                                                                                                                                                                                |

| 7                                        | SO         | Output   | Serial Output                                   | This output pin transmits SPI data to an external device (external microcontroller or the SI pin of the next SPI device in case of daisy-chaining). The pin doesn't require external pull-up or pull-down resistors, but a series resistor is recommended to limit current consumption in case of GND disconnection.                 |

| 8, 25                                    | GND        | Ground   | Ground                                          | These pins are the ground for the logic and analog circuitries of the device. For ESD and electrical parameter accuracy purpose, the ground pins must be shorted in the board.                                                                                                                                                       |

| 9                                        | FSB        | Output   | Fault Status<br>(Active Low)                    | This open drain output pin (external pull-up resistor to $V_{DD}$ required) is set when the device enters Fault mode (see Fault mode).                                                                                                                                                                                               |

| 10, 11, 15,<br>16, 17, 18,<br>22, 23, 24 | NC         | N/A      | Not connected                                   | These pins may not be connected.                                                                                                                                                                                                                                                                                                     |

| 12, 13, 14,<br>19, 20, 21                | HS1<br>HS0 | Output   | Power Switch Outputs                            | Output pins of the switches, to be connected to the load.                                                                                                                                                                                                                                                                            |

| 26                                       | SYNC       | Output   | Output Current<br>Monitoring<br>Synchronization | This output pin is asserted (active low) when the Current Sense (CS) output signal is within the specified accuracy range. Reading the SYNC pin allows the external microprocessor to synchronize to the device when operating in autonomous operating mode. SYNC is open drain and requires a pull-up resistor to $V_{\text{DD}}$ . |

Table 2. 22XSD200 pin description (continued)

| Pin<br>number | Pin name       | Function | Formal name                                  | Definition                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|----------------|----------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27            | CSNS           | Output   | Output Current/<br>Temperature<br>Monitoring | This pin either outputs a current proportional to the channel's output current or a voltage proportional to the temperature of the GND pin (pin 14). Selection between current and temperature sensing, as well as setting the current sensing sensitivity are performed through the SPI interface. An external pull-down resistor must be connected between CSNS and GND. |

| 28, 29        | IN0<br>IN1     | Input    | Direct Inputs                                | The IN[0: 1] input pins are used to directly control the switching state of both switches and consequently the voltage on the HS0: HS1 output pins. The pins are connected to GND by internal pull-down resistors.                                                                                                                                                         |

| 30            | FSOB           | Output   | Fail-safe Output<br>(Active Low)             | FSOB is asserted (active-low) upon entering Fail-safe mode (see Functional description) This open drain output requires an external pull-up resistor to $V_{PWR}$ .                                                                                                                                                                                                        |

| 31, 32        | CONF0<br>CONF1 | Input    | Configuration Input                          | The CONF[0: 1] input pins are used to select the appropriate overcurrent detection profile (bulb/DC motor) for each of both channels. CONF requires a pull-down resistor to GND.                                                                                                                                                                                           |

| 33            | VPWR           | Power    | Positive Power Supply                        | This exposed pad connects to the positive power supply and is the drain of both internal MOSFET switches.                                                                                                                                                                                                                                                                  |

## **Electrical characteristics**

#### Maximum ratings

#### Table 3. Maximum ratings

All voltages are relative to ground unless mentioned otherwise. Exceeding these ratings may cause permanent damage.

| Symbol                                                                           | Parameter                                                                                                                                                                                      | Maximum ratings                | Unit | Notes   |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|---------|

| Electrical ratings                                                               | 5                                                                                                                                                                                              |                                |      |         |

| V <sub>PWR</sub>                                                                 | VPWR Supply Voltage Range<br>Voltage transient at 25 °C (500 ms)<br>Reverse Voltage at 25 °C<br>Fast Negative Transient Pulses (ISO 7637-2 pulse #1, V <sub>PWR</sub> =14 V & Ri=10 Ω)         | 58<br>-32<br>-60               | V    |         |

| V <sub>DD</sub>                                                                  | VDD Supply Voltage Range                                                                                                                                                                       | -0.3 to 5.5                    | V    |         |

| V <sub>MAX,LOGIC</sub>                                                           | Voltage on Input pins (except IN[0:1]) and Output pins) (except HS[0:1])                                                                                                                       | -0.3 to 5.5                    | V    | (2) (3) |

| V <sub>FSO</sub>                                                                 | Voltage on Fail-safe Output (FSOB)                                                                                                                                                             | -0.3 to 58                     | V    |         |

| V <sub>SO</sub>                                                                  | Voltage on SO pin                                                                                                                                                                              | -0.3 to V <sub>DD</sub> +0.3   | V    |         |

| V <sub>IN,MAX</sub>                                                              | Voltage (continuous, max. allowable) on IN[0:1] Inputs                                                                                                                                         | 58                             | V    |         |

| V <sub>HS[0:1]</sub>                                                             | Voltage (continuous, max. allowable) on output pins (HS [0:1]),                                                                                                                                | -32 to 58                      | V    |         |

| I <sub>HS[0:1]</sub>                                                             | Rated Continuous Output Current per channel                                                                                                                                                    | 3.0                            | А    | (4)     |

| E <sub>CL[0:1]_SING</sub>                                                        | Maximum allowable energy dissipation per channel and two parallel channels, single-pulse method                                                                                                | 36                             | mJ   | (5)     |

| V <sub>ESD1</sub><br>V <sub>ESD2</sub><br>V <sub>ESD3</sub><br>V <sub>ESD4</sub> | ESD Voltage<br>Human Body Model (HBM) for HS[0:1], VPWR and GND<br>Human Body Model (HBM) for other pins<br>Charge Device Model (CDM)<br>Package Corner pins (1, 13, 19, 20)<br>All Other pins | ±8000<br>±2000<br>±750<br>±500 | V    | (6)     |

Notes:

2. Concerned Input pins are: CONF[0:1], RSTB, SI, SCLK, Clock, and CSB.

3. Concerned Output pins are: CSNS, SYNC, and FSB.

4. Output current rating valid as long as maximum junction temperature is not exceeded. For computation of the maximum allowable output current, the thermal resistance of the package & the underlying heatsink must be taken into account

5. Single pulse Energy dissipation, Single-pulse short-circuit method ( $L_L$  = 0.5 mH, R = 48 m $\Omega$  V<sub>PWR</sub> = 28 V, T<sub>J</sub> = 150 °C initial).

ESD testing is performed in accordance with the Human Body Model (HBM) (C<sub>ZAP</sub> = 100 pF, R<sub>ZAP</sub> = 1500 Ω), and the Charge Device Model (CDM), Robotic (C<sub>ZAP</sub> = 4.0 pF).

#### Table 3. Maximum ratings (continued)

All voltages are relative to ground unless mentioned otherwise. Exceeding these ratings may cause permanent damage.

| Symbol | Parameter | Maximum ratings | Unit | Notes |

|--------|-----------|-----------------|------|-------|

|        |           |                 |      |       |

| Thermal ratings                  |                                                   |                          |      |          |

|----------------------------------|---------------------------------------------------|--------------------------|------|----------|

| T <sub>A</sub><br>T <sub>J</sub> | Operating Temperature<br>Ambient<br>Junction      | -40 to 125<br>-40 to 150 | °C   | (7)      |

| T <sub>STG</sub>                 | Storage Temperature                               | -55 to 150               | °C   |          |

| R <sub>θJC</sub>                 | Thermal Resistance Junction to Case (Exposed pad) | 1.4                      | °C/W |          |

| R <sub>θJA</sub>                 | Thermal Resistance Junction to Ambient            | 22                       | °C/W | (8)      |

| T <sub>PPRT</sub>                | Peak package reflow temperature during reflow     | Note 10                  | °C   | (9),(10) |

Notes:

7. To achieve high reliability over 10 years of continuous operation, the device's continuous operating junction temperature should not exceed 125 °C.

8. Four layer board (2s2p), per JEDEC JESD51-6 with the board (JESD51-7) horizontal

- 9. Pin soldering temperature limit is for 40 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 10. NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.nxp.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

#### Static electrical characteristics

#### Table 4. Static electrical characteristics

Unless specified otherwise: 8.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V. Typical values are average values evaluated under nominal conditions T<sub>A</sub> = 25 °C, V<sub>PWR</sub> = 28 V & V<sub>DD</sub> = 5.0 V, unless specified otherwise.

| Symbol                  | Parameter                                                                                                                                                                                      | Min.        | Тур.                 | Max.         | Unit | Notes |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|--------------|------|-------|

| Supply electrical       | characteristics                                                                                                                                                                                |             | 1                    |              | 1    |       |

| V <sub>PWR</sub>        | Supply Voltage Range:<br>Full Specification compliant<br>Extended Mode                                                                                                                         | 8.0<br>6.0  | 24<br>-              | 36<br>58     | V    | (11)  |

| I <sub>PWR(ON)</sub>    | V <sub>PWR</sub> Supply Current, device in wake-up mode, channel On, Open<br>Load Outputs in ON-state, HS[0:1] open, IN[0:1] > V <sub>IH</sub>                                                 | _           | 6.5                  | 8.5          | mA   |       |

| I <sub>PWR(SBY)</sub>   | $V_{PWR}$ Supply Current, device in wake-up mode (Standby), channel Off<br>Open Load in OFF-state detection disabled, HS[0:1] shorted to ground<br>with $V_{DD}$ = 5.5 V and RSTB > $V_{WAKE}$ | _           | 6.5                  | 8.5          | mA   |       |

| I <sub>PWR(SLEEP)</sub> | Sleep State Supply Current<br>$V_{PWR} = 24 \text{ V}, \text{RSTB} = \text{IN}[0:1] < V_{WAKE}, \text{HS}[0:1] \text{ connected to ground}$<br>$T_A = 25 \text{ °C}$<br>$T_A = 125 \text{ °C}$ |             | 3.0<br>-             | 10.0<br>60.0 | μΑ   |       |

| V <sub>DD(ON)</sub>     | V <sub>DD</sub> Supply Voltage                                                                                                                                                                 | 3.0         | _                    | 5.5          | V    |       |

| I <sub>DD(ON)</sub>     | V <sub>DD</sub> Supply Current at V <sub>DD =</sub> 5.5 V<br>No SPI Communication<br>8.0 MHz SPI Communication                                                                                 | -           | _<br>5.0             | 2.2          | mA   | (12)  |

| I <sub>DD(SLEEP)</sub>  | $V_{DD}$ Sleep State Current at $V_{DD}$ = 5.5 V with or without $V_{PWR}$                                                                                                                     | -           | _                    | 5.0          | μA   |       |

| V <sub>PWR(OV)</sub>    | Overvoltage Shutdown Threshold                                                                                                                                                                 | 39          | 42                   | 45.5         | V    |       |

| V <sub>PWR(OVHYS)</sub> | Overvoltage Shutdown Hysteresis                                                                                                                                                                | 0.2         | 0.8                  | 1.5          | V    |       |

| V <sub>PWR(UV)</sub>    | Undervoltage Shutdown Threshold                                                                                                                                                                | 5.0         | _                    | 6.0          | V    | (13)  |

| V <sub>PWR(POR)</sub>   | V <sub>PWR</sub> Power-On-Reset (POR) Voltage Threshold                                                                                                                                        | 2.2         | 2.6                  | 4.0          | V    | (13)  |

| V <sub>DD(POR)</sub>    | V <sub>DD</sub> Power-On-Reset (POR) Voltage Threshold                                                                                                                                         | 1.5         | 2.0                  | 2.5          | V    | (13)  |

| V <sub>DD(FAIL)</sub>   | $V_{DD}$ Supply Failure Voltage Threshold (assumed $V_{PWR} > V_{PWR(UV)}$ )                                                                                                                   | 2.2         | 2.5                  | 2.8          | V    |       |

| R <sub>DS(on)25</sub>   | ON-Resistance, Drain-to-Source ( $I_{HS}$ = 1.0 A, $T_J$ = 25 °C)<br>CSNS_ratio = 0<br>$V_{PWR}$ = 8.0 V<br>$V_{PWR}$ = 28 V<br>$V_{PWR}$ = 36 V                                               | -<br>-<br>- | 18.7<br>18.7<br>18.7 | -<br>-<br>-  | mΩ   |       |

Notes

11. In extended mode, availability of several device functions (channel control, value of R<sub>DS(on)</sub>, overtemperature protection) is guaranteed, but compliance with the specified values in this document is not. Below 6.0 V, the device is only protected from overheating (thermal shutdown). Above V<sub>PWR(OV)</sub>, the channels can only be turned ON when the overvoltage detection function has been disabled.

12. Typical value guaranteed per design.

When the device recovers from undervoltage and returns to normal mode (6.0 V < V<sub>PWR</sub> < 58 V) before the end of the auto-retry period (see Auto-retry), the device performs normally. When V<sub>PWR</sub> drops below V<sub>PWR(UV)</sub>, undervoltage is detected (see Undervoltage fault (latchable fault) and EMC performances).

Unless specified otherwise: 8.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V. Typical values are average values evaluated under nominal conditions T<sub>A</sub> = 25 °C, V<sub>PWR</sub> = 28 V & V<sub>DD</sub> = 5.0 V, unless specified otherwise.

| Symbol                                                                           | Parameter                                                                                                                                                                                                                                                                                                                     | Min.                                             | Тур.                                             | Max.                                             | Unit | Notes |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------|-------|

| Electrical charact                                                               | eristics of the output stage (HS0 and HS1)                                                                                                                                                                                                                                                                                    |                                                  | 1                                                | 1                                                | 1    |       |

| R <sub>DS(on)150</sub>                                                           | $      ON-Resistance, Drain-to-Source (I_{HS} = 1.0 \text{ A}, T_J = 150 \ ^{\circ}\text{C}) \\ CSNS_ratio = 0 \\ V_{PWR} = 8.0 \text{ V} \\ V_{PWR} = 28 \text{ V} \\ V_{PWR} = 28 \text{ V} \\ V_{PWR} = 36 \text{ V}      $                                                                                                | -<br>-<br>-                                      | -<br>-<br>-                                      | 43<br>43<br>43                                   | mΩ   |       |

| $\Delta R_{DS(on)150}$                                                           | ON-Resistance, Drain-to-Source difference from one channel to the other in parallel mode ( $I_{HS}$ = 1.0 A,T <sub>J</sub> = 150 °C) CSNS_ratio = X                                                                                                                                                                           | -0.9                                             | _                                                | 0.9                                              | mΩ   |       |

| R <sub>SD(on)150</sub>                                                           | ON-Resistance, Source-Drain (I <sub>HS</sub> = -1.0 A, T <sub>J</sub> = 150 °C, $V_{PWR}$ = -24 V)                                                                                                                                                                                                                            | _                                                | _                                                | 43                                               | mΩ   |       |

| L <sub>SHORT</sub>                                                               | Max. detectable wiring length (2.5 mm <sup>2</sup> ) for severe short-circuit<br>detection (see Severe short-circuit fault (latchable fault)):<br>High slew rate selected<br>Medium slew rate selected<br>Low slew rate selected                                                                                              | 30<br>55<br>110                                  | 100<br>175<br>365                                | 180<br>300<br>620                                | cm   |       |

| I_OCH1_0<br>I_OCH2_0<br>I_OCM1_0<br>I_OCM2_0<br>I_OCL1_0<br>I_OCL2_0<br>I_OCL3_0 | Overcurrent Detection thresholds with CSNS_ratio bit = 0 (CSR0)                                                                                                                                                                                                                                                               | 26.4<br>16.3<br>10.4<br>6.4<br>4.3<br>2.9<br>1.4 | 32<br>20.1<br>12.6<br>7.7<br>5.3<br>3.6<br>1.8   | 38.5<br>24.5<br>15.2<br>9.3<br>6.3<br>4.3<br>2.2 | A    |       |

| I_OCH1_1<br>I_OCH2_1<br>I_OCM1_1<br>I_OCM2_1<br>I_OCL1_1<br>I_OCL2_1<br>I_OCL3_1 | Overcurrent Detection thresholds with CSNS_ratio bit = 1(CSR1)                                                                                                                                                                                                                                                                | 8.9<br>5.6<br>3.5<br>2.2<br>1.45<br>0.98<br>0.48 | 10.7<br>6.8<br>4.25<br>2.7<br>1.75<br>1.2<br>0.6 | 12.8<br>8.2<br>5.1<br>3.2<br>2.1<br>1.45<br>0.72 | A    |       |

| I <sub>OUT_LEAK</sub>                                                            |                                                                                                                                                                                                                                                                                                                               | _<br>-120<br>-1400                               | -<br>-<br>-                                      | +5.0<br>+5.0<br>+5.0                             | μΑ   |       |

| I <sub>OUT_OFF</sub>                                                             | Output biasing current in off-state (positive value = outgoing)<br>with OL_OFF disabled (worst case for V <sub>PWR</sub> = 36 V, V <sub>HS,OFF</sub> = 34 V)<br>Fast slew rate selected<br>Medium slew rate selected<br>Slow slew rate selected<br>With OL_OFF disabled and ECU ground disconnected (V <sub>PWR</sub> = 32 V) | -620<br>-440<br>-330<br>0                        | -495<br>-360<br>-280<br>-                        | -380<br>-280<br>-230<br>1000                     | μΑ   |       |

| V <sub>D_GND(CLAMP)</sub>                                                        | Switch Turn-on threshold for Supply overvoltage (V <sub>PWR</sub> -GND)                                                                                                                                                                                                                                                       | 58                                               | -                                                | 67                                               | V    |       |

| V <sub>DS(CLAMP)</sub>                                                           | Switch turn-on threshold for Drain-Source overvoltage (measured at ${\rm I}_{\rm OUT}$ = 500 mA                                                                                                                                                                                                                               | 58                                               | _                                                | 66                                               | V    |       |

| $\Delta V_{DS(CLAMP)}$                                                           | Switch turn-on threshold for Drain-Source overvoltage difference from one channel to the other in parallel mode (at $I_{\rm HS}$ = 500 mA)                                                                                                                                                                                    | -2.0                                             | _                                                | +2.0                                             | v    |       |

Unless specified otherwise: 8.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V. Typical values are average values evaluated under nominal conditions T<sub>A</sub> = 25 °C, V<sub>PWR</sub> = 28 V & V<sub>DD</sub> = 5.0 V, unless specified otherwise.

| Symbol                               | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Min.                                                                              | Тур.            | Max.                                                                  | Unit | Notes |  |  |  |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------|------|-------|--|--|--|--|

| Electrical characte                  | Electrical characteristics of the output stage (HS0 and HS1) (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                   |                 |                                                                       |      |       |  |  |  |  |

| C <sub>SR0</sub><br>C <sub>SR1</sub> | Current Sensing Ratio<br>CSNS_ratio bit = 0 (high current mode)<br>CSNS_ratio bit = 1 (low current mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                   | 1/1500<br>1/500 |                                                                       | _    | (14)  |  |  |  |  |

| I_LOAD_MIN                           | Minimum measurable load current with compensated error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                                 | _               | 50                                                                    | mA   | (15)  |  |  |  |  |

| I <sub>CSR_LEAK</sub>                | CSNS leakage current in OFF state (CSNSx_en = 0, CSNS_ratio bit_x = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -4.0                                                                              | _               | +4.0                                                                  | μA   |       |  |  |  |  |

| I_LOAD_ERR_SYS                       | Systematic offset error (see Current sense errors)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                 | -4.0            | _                                                                     | mA   |       |  |  |  |  |

| I_LOAD_ERR_RAND                      | Random offset error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -125                                                                              | -               | 125                                                                   | mA   |       |  |  |  |  |

| I <sub>CSNS,MAX</sub>                | CSNS pin current sourcing capability, absolute upper limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.15                                                                              | -               | -                                                                     | mA   |       |  |  |  |  |

| E <sub>SR0_ERR</sub>                 | $ \begin{array}{l} {\sf E}_{SR0} \mbox{ Output Current Sensing Error (\%), uncompensated at output Current level (Sense ratio C_{SR0} selected):  T_J = -40 \ ^\circ C \\ 3.0 \ A \\ 1.5 \ A \\ 0.75 \ A \\ 0.375 \ A \\ T_J = 125 \ ^\circ C \\ 3.0 \ A \\ 1.5 \ A \\ 0.75 \ A \\ 0.375 \ A \\ T_J = 25 \ ^\circ C \ to \ 125 \ ^\circ C \\ 3.0 \ A \\ 1.5 \ A \\ 0.375 \ A \\ T_J = 25 \ ^\circ C \ to \ 125 \ ^\circ C \\ 3.0 \ A \\ 1.5 \ A \\ 0.375 \$ | -13<br>-12<br>-17<br>-26<br>-10<br>-9.0<br>-12<br>-15<br>-10<br>-10<br>-12<br>-16 |                 | 13<br>12<br>17<br>26<br>10<br>9.0<br>12<br>15<br>10<br>10<br>12<br>16 | %    | (16)  |  |  |  |  |

Notes:

14. Current Sense Ratio  $C_{SRx} = I_{CSNS} / (I_{HS[x]} + I_{LOAD\_ERR\_SYS})$

15. See note <sup>(16)</sup>, but with I<sub>CSNS\_MEAS</sub> obtained after compensation of I<sub>LOAD\_ERR\_RAND</sub> (see Activation and use of offset compensation). Further accuracy improvements can be obtained by performing a 1 or 2 point calibration (see Application Note)

16. E<sub>SRx\_ERR</sub>=(I<sub>CSNS\_MEAS</sub> / I<sub>CSNS\_MODEL</sub>) -1, with I<sub>CSNS\_MODEL</sub> = (I(HS[x])+ I<sub>\_LOAD\_ERR\_SYS</sub>) \* C<sub>SRx</sub>, (I<sub>\_LOAD\_ERR\_SYS</sub> defined above, see section Current Sense Error Model). With this model, load current becomes: I(HS[x]) = I<sub>CSNS</sub> / C<sub>SRx</sub> - I<sub>\_LOAD\_ERR\_SYS</sub>

Unless specified otherwise: 8.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V. Typical values are average values evaluated under nominal conditions T<sub>A</sub> = 25 °C, V<sub>PWR</sub> = 28 V & V<sub>DD</sub> = 5.0 V, unless specified otherwise.

| Symbol                      | Parameter                                                                                                                                                 | Min.       | Тур. | Max. | Unit | Notes |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------|------|-------|

| Electrical characte         | ristics of the output stage (HS0 and HS1) (continued)                                                                                                     |            |      |      |      |       |

|                             | $E_{SR0}$ Output Current Sensing Error (%) after offset compensation at output Current level (Sense ratio $C_{SR0}$ selected):                            |            |      |      |      |       |

|                             | $T_J = -40 \ ^{\circ}C$                                                                                                                                   |            |      |      |      |       |

|                             | 3.0 A                                                                                                                                                     | -11        | -    | 11   |      |       |

|                             | 1.5 A                                                                                                                                                     | -11        | -    | 11   |      |       |

|                             | 0.75 A                                                                                                                                                    | -11        | _    | 11   |      |       |

|                             | 0.375 A                                                                                                                                                   | -11        | _    | 11   |      |       |

|                             | $T_J = 125 \ ^{\circ}C$                                                                                                                                   |            |      |      |      |       |

| E <sub>SR0_ERR</sub> (Comp) | 3.0 A                                                                                                                                                     | -9.0       | -    | 9.0  | %    | (17)  |

|                             | 1.5 A                                                                                                                                                     | -9.0       | -    | 9.0  |      |       |

|                             | 0.75 A                                                                                                                                                    | -9.0       | _    | 9.0  |      |       |

|                             | 0.375 A                                                                                                                                                   | -10        | _    | 10   |      |       |

|                             | $T_J = 25 \text{ °C to } 125 \text{ °C}$                                                                                                                  |            |      |      |      |       |

|                             | 3.0 A                                                                                                                                                     | -10        | -    | 10   |      |       |

|                             | 1.5 A                                                                                                                                                     | -9.0       | _    | 9.0  |      |       |

|                             | 0.75 A                                                                                                                                                    | -9.0       | _    | 9.0  |      |       |

|                             | 0.375 A                                                                                                                                                   | -10        | -    | 10   |      |       |

|                             | $E_{SR1}$ Output Current Sensing Error (%), uncompensated at output Current level (Sense ratio $C_{SR1}$ selected):<br>T <sub>J</sub> = -40 °C            |            |      |      |      |       |

| E <sub>SR1_ERR</sub>        | 0.75 A<br>T <sub>J</sub> = 125 °C                                                                                                                         | -16        | _    | 16   | %    | (17)  |

|                             | 0.75 A                                                                                                                                                    | -10        | -    | 10   |      |       |

|                             | T <sub>J</sub> = 25 °C to 125 °C<br>0.75 A                                                                                                                | -12        | -    | 12   |      |       |

|                             | $E_{SR1}$ Output Current Sensing Error (%) after offset compensation at output Current level (Sense ratio $C_{SR1}$ selected):<br>T <sub>1</sub> = -40 °C |            |      |      |      |       |

|                             | 0.75 A                                                                                                                                                    | -11        |      | 11   |      |       |

|                             | 0.25 A                                                                                                                                                    | -14        | _    | 14   |      |       |

|                             | 0.125 A<br>0.125 A                                                                                                                                        | -14<br>-19 | _    | 14   |      |       |

|                             | 0.075 A                                                                                                                                                   | -19        | _    | 29   |      |       |

|                             | $T_{\rm J} = 125 ^{\circ}{\rm C}$                                                                                                                         | -29        | _    | 29   |      |       |

| Comp)                       | -                                                                                                                                                         | 0.0        |      | 0.0  | 0/   | (10)  |

| E <sub>SR1_ERR</sub> (Comp) | 0.75 A<br>0.25 A                                                                                                                                          | -9.0       | -    | 9.0  | %    | (18)  |

|                             | 0.25 A<br>0.125 A                                                                                                                                         | -10        | -    | 10   |      |       |

|                             | 0.125 A<br>0.075 A                                                                                                                                        | -12        | -    | 12   |      |       |

|                             |                                                                                                                                                           | -16        | -    | 16   |      |       |

|                             | $T_J = 25$ °C to 125 °C                                                                                                                                   | 0.0        |      | 0.0  |      |       |

|                             | 0.75 A                                                                                                                                                    | -9.0       | -    | 9.0  |      |       |

|                             | 0.25 A                                                                                                                                                    | -11        | -    | 11   |      |       |

|                             | 0.125 A                                                                                                                                                   | -13        | -    | 13   |      |       |

|                             | 0.075 A                                                                                                                                                   | -21        | -    | 21   |      |       |

Notes:

17. E<sub>SRx\_ERR</sub>=(I<sub>CSNS\_MEAS</sub> / I<sub>CSNS\_MODEL</sub>) -1, with I<sub>CSNS\_MODEL</sub> = (I(HS[x])+ I<sub>\_LOAD\_ERR\_SYS</sub>) \* C<sub>SRx</sub>, (I<sub>\_LOAD\_ERR\_SYS</sub> defined above, see section Current Sense Error Model). With this model, load current becomes: I(HS[x]) = I<sub>CSNS</sub> / C<sub>SRx</sub> - I<sub>\_LOAD\_ERR\_SYS</sub>

See note <sup>(19)</sup>, but with I<sub>CSNS\_MEAS</sub> obtained after compensation of I<sub>LOAD\_ERR\_RAND</sub> (see Activation and use of offset compensation). Further accuracy improvements can be obtained by performing a 1 or 2 point calibration

Unless specified otherwise: 8.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V. Typical values are average values evaluated under nominal conditions T<sub>A</sub> = 25 °C, V<sub>PWR</sub> = 28 V & V<sub>DD</sub> = 5.0 V, unless specified otherwise.

| Symbol                   | Parameter                                                                                                                                                                                                    | Min.                  | Тур.                  | Max.                  | Unit | Notes |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|------|-------|

| Electrical charact       | eristics of the output stage (HS0 and HS1) (continued)                                                                                                                                                       |                       |                       |                       |      |       |

|                          | E <sub>SR0</sub> Output Current Sensing Error in parallel mode (%),<br>uncompensated) at outputs Current level (Sense ratio C <sub>SR0</sub> selected):<br>$T_1 = -40$ °C                                    |                       |                       |                       |      |       |

|                          | 6.0 A<br>3.0 A                                                                                                                                                                                               | -10                   | _                     | 10                    |      |       |

| E <sub>SR0_ERR_PAR</sub> | $T_{ij} = 125 ^{\circ}\text{C}$                                                                                                                                                                              | -11                   | _                     | 11                    | %    | (19)  |

| -SRU_ERR_PAR             | 6.0 A                                                                                                                                                                                                        | -8.0                  | _                     | 8.0                   | 70   |       |

|                          | 3.0 A                                                                                                                                                                                                        | -8.0                  | _                     | 8.0                   |      |       |

|                          | $T_J = 25 ^{\circ}\text{C} \text{ to } 125 ^{\circ}\text{C}$                                                                                                                                                 |                       |                       |                       |      |       |

|                          | 6.0 A                                                                                                                                                                                                        | -9.0                  | -                     | 9.0                   |      |       |

|                          | 3.0 A                                                                                                                                                                                                        | -9.0                  | -                     | 9.0                   |      |       |

| V <sub>CL(CSNS)</sub>    | Current Sense Clamping Voltage (condition: $R(CSNS) > 10 \text{ k}\Omega$ )                                                                                                                                  | 5.5                   | -                     | 7.5                   | V    |       |

| I <sub>OLD(OFF)</sub>    | Open Load detection Current threshold in OFF state                                                                                                                                                           | 30                    | _                     | 100                   | μA   |       |

| V <sub>OLD(THRES)</sub>  | Open Load Fault Detection Voltage Threshold                                                                                                                                                                  | 4.0                   | -                     | 5.5                   | V    |       |

| I <sub>OLD(ON)</sub>     | Open Load detection Current threshold in ON state (see Open load<br>detection in on state (OL_ON)):<br>CSNS_ratio bit = 0<br>CSNS_ratio bit = 1 (fast slew rate SR[1:0] = 10 mandatory for this<br>function) | 40<br>4.0             | 150<br>7.0            | 300<br>10             | mA   |       |

| tolled                   | Time period of the periodically activated Open Load in ON state detection for CSNS_ratio bit = 1                                                                                                             | 105                   | 150                   | 195                   | ms   |       |

| V <sub>OSD(THRES)</sub>  | Output Shorted-to-V $_{\rm PWR}$ Detection Voltage Threshold (channel in OFF state)                                                                                                                          | V <sub>PWR</sub> -1.2 | V <sub>PWR</sub> -0.8 | V <sub>PWR</sub> -0.4 | V    |       |

| V <sub>CL</sub>          | Switch turn-on threshold for Negative Output Voltages (protects against negative transients) - (measured at I <sub>OUT</sub> = 100mA, Channel in OFF state)                                                  | -38                   | _                     | -32                   | V    |       |

| $\Delta V_{CL}$          | Switch turn-on threshold for Negative Output Voltages difference from one channel to the other in parallel mode - (measured at $I_{OUT}$ = 100 mA, Channel in OFF state)                                     | -2.0                  | _                     | +2.0                  | V    |       |

| V <sub>HS_TH</sub>       | Switching State (On/Off) discrimination thresholds                                                                                                                                                           | 0.45*V <sub>PWR</sub> | 0.5*V <sub>PWR</sub>  | 0.55*V <sub>PWR</sub> | V    |       |

| T <sub>SD</sub>          | Shutdown temperature (Power MOSFET junction; 6.0 V < V_{PWR} < 58 V)                                                                                                                                         | 160                   | 175                   | 190                   | °C   |       |

Notes:

19. Minimum required value of open load impedance for detection of open load in OFF-state: 200 kΩ.(V<sub>OLD(THRES)</sub> = V<sub>HS</sub> at I<sub>OLD(OFF)</sub>)

Unless specified otherwise: 8.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V. Typical values are average values evaluated under nominal conditions T<sub>A</sub> = 25 °C, V<sub>PWR</sub> = 28 V & V<sub>DD</sub> = 5.0 V, unless specified otherwise.

| Symbol                | Parameter                                                                                                                                                                                            | Min.                 | Тур. | Max.           | Unit | Notes |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|----------------|------|-------|