Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications Rev. 1.0 — 14 February 2018 Data sheet: technical data

Data sheet: technical data

# **General description**

The PF4210 high performance power management integrated circuit (PMIC) provides a highly programmable/configurable architecture with fully integrated power devices and minimal external components. With up to six buck converters, six linear regulators, an RTC supply, and a coin cell charger, the PF4210 can provide power for a complete system, including applications processors, memory, and system peripherals, in a wide range of applications.

With on-chip one-time programmable (OTP) memory, the PF4210 is available in preprogrammed standard version or nonprogrammed to support custom programming. The PF4210 is defined to power low-cost audio/video applications using the i.MX 8M family of applications processors.

### 2 Features and benefits

- Four to six buck converters, depending on configuration

- Single/dual phase/parallel options

- DDR termination tracking mode option

- Boost regulator to 5.0 V output

- Six general purpose linear regulators

- Programmable output voltage, sequence, and timing

- OTP (one-time programmable) memory for device configuration

- Coin cell charger and RTC supply

- · DDR termination reference voltage

- Power control logic with processor interface and event detection

- I<sup>2</sup>C control

- Individually programmable on, off, and standby modes

14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

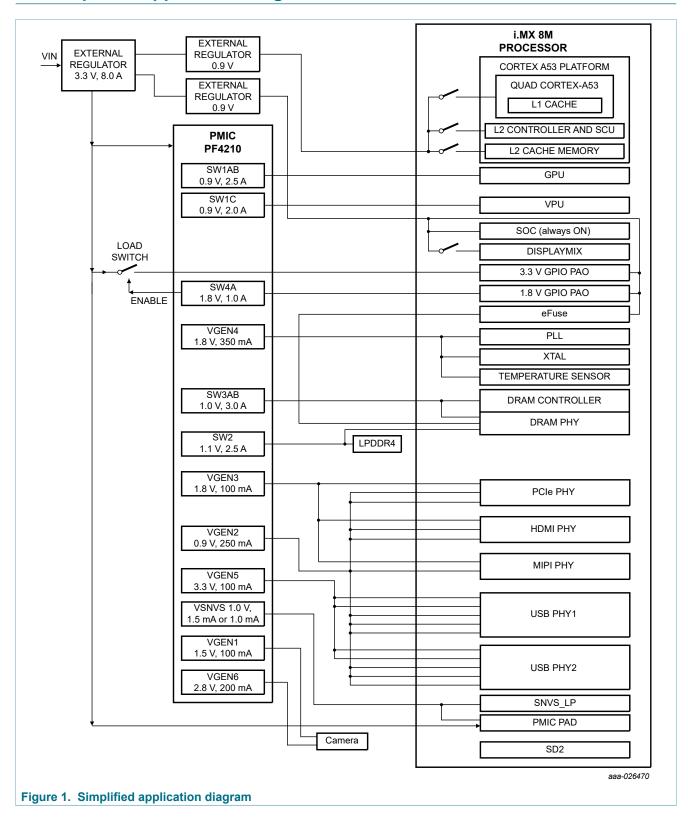

# 3 Simplified application diagram

14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

# **Applications**

- OTT STB

- · Wireless audio

- · Voice recognition assistant

- A/V receivers

- Sound bars

- · General embedded

# **Orderable parts**

The PF4210 is available with both preprogrammed and nonprogrammed OTP memory configurations. The nonprogrammed device uses A0 as the programming code. The preprogrammed devices are identified using the program codes from Table 1, which also list the associated NXP reference designs where applicable.

Details of the OTP programming for each device can be found in Table 8.

Table 1. Orderable part variations

| Part number <sup>[1]</sup> | Temperature (T <sub>A</sub> )              | Package                                               | Programming <sup>[2]</sup> | Reference designs |

|----------------------------|--------------------------------------------|-------------------------------------------------------|----------------------------|-------------------|

| MC32PF4210A0ES             | 0 °C to 85 °C (for use in consumer         | 56 QFN 8x8 mm - 0.5 mm<br>pitch WF-type QFN (wettable | A0 (Nonprogrammed)         | N/A               |

| MC32PF4210A1ES             | applications)                              | flank)                                                | A1                         | MCIMX8M-EVK       |

| MC32PF4210A2ES             |                                            |                                                       | A2                         | N/A               |

| MC32PF4210A3ES             |                                            |                                                       | A3                         | N/A               |

| MC34PF4210A0ES             | -40 °C to 105 °C<br>(for use in industrial |                                                       | A0 (Nonprogrammed)         | N/A               |

| MC34PF4210A1ES             | applications)                              |                                                       | A1                         | MCIMX8M-EVK       |

| MC34PF4210A2ES             |                                            |                                                       | A2                         | N/A               |

| MC34PF4210A3ES             |                                            |                                                       | A3                         | N/A               |

For tape and reel, add an R2 suffix to the part number.

For programming details see <u>Table 8</u>. The available OTP options are not restricted to the listed reference designs. They can be used in any application where the listed voltage and sequence details are acceptable.

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

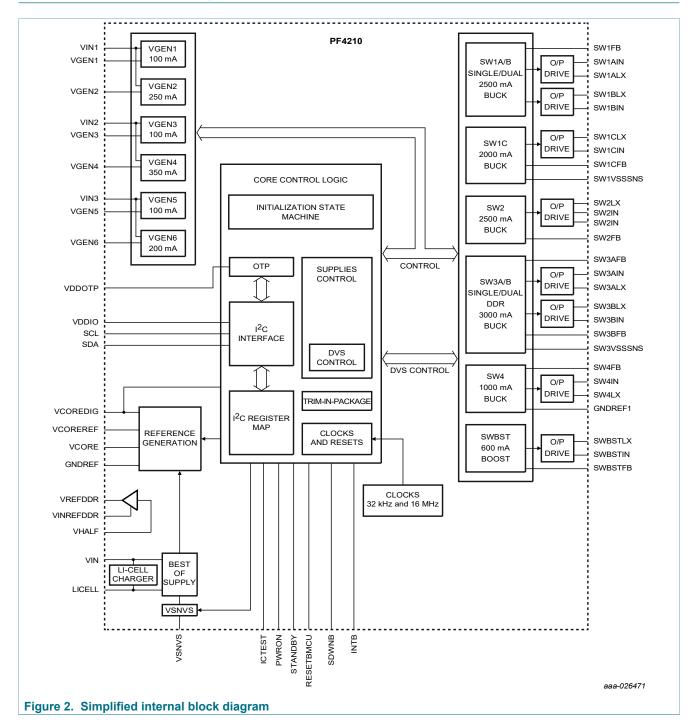

# 6 Internal block diagram

14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

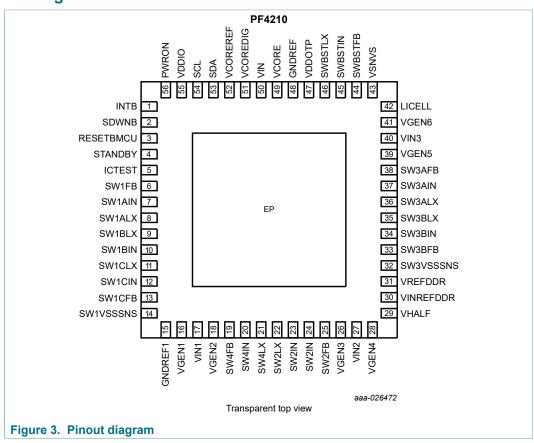

# 7 Pinning information

# 7.1 Pinning

# 7.2 Pin definitions

Table 2. Pin definitions

| Number | Name                 | Function | Max rating | Туре               | Definition                                                                                                                          |

|--------|----------------------|----------|------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1      | INTB                 | Output   | 3.6 V      | Digital            | Open drain interrupt signal to processor                                                                                            |

| 2      | SDWNB                | Output   | 3.6 V      | Digital            | Open drain signal to indicate an imminent system shutdown                                                                           |

| 3      | RESETBMCU            | Output   | 3.6 V      | Digital            | Open drain reset output to processor. Alternatively can be used as a power output.                                                  |

| 4      | STANDBY              | Input    | 3.6 V      | Digital            | Standby input signal from processor                                                                                                 |

| 5      | ICTEST               | Input    | 7.5 V      | Digital/<br>Analog | Reserved pin. Connect to GND in application.                                                                                        |

| 6      | SW1FB <sup>[1]</sup> | Input    | 3.6 V      | Analog             | Output voltage feedback for SW1A/B. Route this trace separately from the high current path and terminate at the output capacitance. |

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

| Number | Name                  | Function | Max rating | Туре   | Definition                                                                                                                                            |

|--------|-----------------------|----------|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | SW1AIN [1]            | Input    | 4.8 V      | Analog | Input to SW1A regulator. Bypass with at least a 4.7 $\mu$ F ceramic capacitor and a 0.1 $\mu$ F decoupling capacitor as close to the pin as possible. |

| 8      | SW1ALX [1]            | Output   | 4.8 V      | Analog | Regulator 1A switch node connection                                                                                                                   |

| 9      | SW1BLX [1]            | Output   | 4.8 V      | Analog | Regulator 1B switch node connection                                                                                                                   |

| 10     | SW1BIN [1]            | Input    | 4.8 V      | Analog | Input to SW1B regulator. Bypass with at least a 4.7 $\mu$ F ceramic capacitor and a 0.1 $\mu$ F decoupling capacitor as close to the pin as possible. |

| 11     | SW1CLX [1]            | Output   | 4.8 V      | Analog | Regulator 1C switch node connection                                                                                                                   |

| 12     | SW1CIN [1]            | Input    | 4.8 V      | Analog | Input to SW1C regulator. Bypass with at least a 4.7 $\mu$ F ceramic capacitor and a 0.1 $\mu$ F decoupling capacitor as close to the pin as possible. |

| 13     | SW1CFB <sup>[1]</sup> | Input    | 3.6 V      | Analog | Output voltage feedback for SW1C. Route this trace separately from the high current path and terminate at the output capacitance.                     |

| 14     | SW1VSSSNS             | GND      | _          | GND    | Ground reference for regulators SW1ABC. It is connected externally to GNDREF through a board ground plane.                                            |

| 15     | GNDREF1               | GND      | _          | GND    | Ground reference for regulators SW2 and SW4. It is connected externally to GNDREF, via board ground plane.                                            |

| 16     | VGEN1                 | Output   | 2.5 V      | Analog | VGEN1 regulator output. Bypass with a 2.2 μF ceramic output capacitor.                                                                                |

| 17     | VIN1                  | Input    | 3.6 V      | Analog | VGEN1, 2 input supply. Bypass with a 1.0 µF decoupling capacitor as close to the pin as possible.                                                     |

| 18     | VGEN2                 | Output   | 2.5 V      | Analog | VGEN2 regulator output. Bypass with a 4.7 µF ceramic output capacitor.                                                                                |

| 19     | SW4FB <sup>[1]</sup>  | Input    | 3.6 V      | Analog | Output voltage feedback for SW4. Route this trace separately from the high current path and terminate at the output capacitance.                      |

| 20     | SW4IN <sup>[1]</sup>  | Input    | 4.8 V      | Analog | Input to SW4 regulator. Bypass with at least a 4.7 $\mu$ F ceramic capacitor and a 0.1 $\mu$ F decoupling capacitor as close to the pin as possible.  |

| 21     | SW4LX [1]             | Output   | 4.8 V      | Analog | Regulator 4 switch node connection                                                                                                                    |

| 22     | SW2LX [1]             | Output   | 4.8 V      | Analog | Regulator 2 switch node connection                                                                                                                    |

| 23     | SW2IN [1]             | Input    | 4.8 V      | Analog | Input to SW2 regulator. Connect pin 23 together with pin                                                                                              |

| 24     | SW2IN <sup>[1]</sup>  | Input    | 4.8 V      | Analog | 24 and bypass with at least a 4.7 μF ceramic capacitor and a 0.1 μF decoupling capacitor as close to these pins as possible.                          |

| 25     | SW2FB <sup>[1]</sup>  | Input    | 3.6 V      | Analog | Output voltage feedback for SW2. Route this trace separately from the high current path and terminate at the output capacitance.                      |

| 26     | VGEN3                 | Output   | 3.6 V      | Analog | VGEN3 regulator output. Bypass with a 2.2 µF ceramic output capacitor.                                                                                |

| 27     | VIN2                  | Input    | 3.6 V      | Analog | VGEN3, 4 input. Bypass with a 1.0 $\mu F$ decoupling capacitor as close to the pin as possible.                                                       |

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

| Number | Name                  | Function         | Max rating          | Type               | Definition                                                                                                                                             |

|--------|-----------------------|------------------|---------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28     | VGEN4                 | Output           | 3.6 V               | Analog             | VGEN4 regulator output. Bypass with a 4.7 µF ceramic output capacitor.                                                                                 |

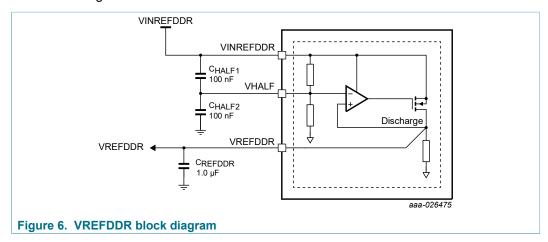

| 29     | VHALF                 | Input            | 3.6 V               | Analog             | Half supply reference for VREFDDR                                                                                                                      |

| 30     | VINREFDDR             | Input            | 3.6 V               | Analog             | VREFDDR regulator input. Bypass with at least 1.0 μF decoupling capacitor as close to the pin as possible.                                             |

| 31     | VREFDDR               | Output           | 3.6 V               | Analog             | VREFDDR regulator output                                                                                                                               |

| 32     | SW3VSSSNS             | GND              | _                   | GND                | Ground reference for the SW3 regulator. Connect to GNDREF externally via the board ground plane.                                                       |

| 33     | SW3BFB <sup>[1]</sup> | Input            | 3.6 V               | Analog             | Output voltage feedback for SW3B. Route this trace separately from the high current path and terminate at the output capacitance.                      |

| 34     | SW3BIN <sup>[1]</sup> | Input            | 4.8 V               | Analog             | Input to SW3B regulator. Bypass with at least a 4.7 $\mu$ F ceramic capacitor and a 0.1 $\mu$ F decoupling capacitor as close to the pin as possible.  |

| 35     | SW3BLX [1]            | Output           | 4.8 V               | Analog             | Regulator 3B switch node connection                                                                                                                    |

| 36     | SW3ALX [1]            | Output           | 4.8 V               | Analog             | Regulator 3A switch node connection                                                                                                                    |

| 37     | SW3AIN <sup>[1]</sup> | Input            | 4.8 V               | Analog             | Input to SW3A regulator. Bypass with at least a 4.7 $\mu$ F ceramic capacitor and a 0.1 $\mu$ F decoupling capacitor as close to the pin as possible.  |

| 38     | SW3AFB <sup>[1]</sup> | Input            | 3.6 V               | Analog             | Output voltage feedback for SW3A. Route this trace separately from the high current path and terminate at the output capacitance.                      |

| 39     | VGEN5                 | Output           | 3.6 V               | Analog             | VGEN5 regulator output. Bypass with a 2.2 µF ceramic output capacitor.                                                                                 |

| 40     | VIN3                  | Input            | 4.8 V               | Analog             | VGEN5, 6 input. Bypass with a 1.0 µF decoupling capacitor as close to the pin as possible.                                                             |

| 41     | VGEN6                 | Output           | 3.6 V               | Analog             | VGEN6 regulator output. Bypass with a 2.2 µF ceramic output capacitor.                                                                                 |

| 42     | LICELL                | Input/Out<br>put | 3.6 V               | Analog             | Coin cell supply input/output                                                                                                                          |

| 43     | VSNVS                 | Output           | 3.6 V               | Analog             | LDO or coin cell output to processor                                                                                                                   |

| 44     | SWBSTFB [1]           | Input            | 5.5 V               | Analog             | Boost regulator feedback. Connect this pin to the output rail close to the load. Keep this trace away from other noisy traces and planes.              |

| 45     | SWBSTIN [1]           | Input            | 4.8 V               | Analog             | Input to SWBST regulator. Bypass with at least a 2.2 $\mu$ F ceramic capacitor and a 0.1 $\mu$ F decoupling capacitor as close to the pin as possible. |

| 46     | SWBSTLX [1]           | Output           | 7.5 V               | Analog             | SWBST switch node connection                                                                                                                           |

| 47     | VDDOTP                | Input            | 10 V <sup>[2]</sup> | Digital/<br>Analog | Supply to program OTP fuses                                                                                                                            |

| 48     | GNDREF                | GND              | _                   | GND                | Ground reference for the main band gap regulator                                                                                                       |

| 49     | VCORE                 | Output           | 3.6 V               | Analog             | Analog core supply                                                                                                                                     |

| 50     | VIN                   | Input            | 4.8 V               | Analog             | Main chip supply                                                                                                                                       |

| 51     | VCOREDIG              | Output           | 1.5 V               | Analog             | Digital core supply                                                                                                                                    |

PF4210

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2018. All rights reserved.

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

| Number | Name     | Function         | Max rating | Туре    | Definition                                                                                                                                                            |

|--------|----------|------------------|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52     | VCOREREF | Output           | 1.5 V      | Analog  | Main band gap reference                                                                                                                                               |

| 53     | SDA      | Input/Out<br>put | 3.6 V      | Digital | I <sup>2</sup> C data line (open drain)                                                                                                                               |

| 54     | SCL      | Input            | 3.6 V      | Digital | I <sup>2</sup> C clock                                                                                                                                                |

| 55     | VDDIO    | Input            | 3.6 V      | Analog  | Supply for I <sup>2</sup> C bus. Bypass with 0.1 µF ceramic capacitor                                                                                                 |

| 56     | PWRON    | Input            | 3.6 V      | Digital | Power on/off from processor                                                                                                                                           |

| _      | EP       | GND              | _          | GND     | Expose pad. Functions as ground return for buck regulators. Tie this pad to the inner and external ground planes through vias to allow effective thermal dissipation. |

<sup>[1]</sup> Unused switching regulators should be connected as follow: Pins SWxLX and SWxFB should be unconnected and pin SWxIN should be connected to VIN with a 0.1 µF bypass capacitor.

# 8 General product characteristics

# 8.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

All voltages are with respect to ground, unless otherwise noted. Exceeding these ratings may cause malfunction or permanent damage to the device. For maximum voltage rating for each pin see Section 7.2 "Pin definitions".

| Symbol              | Description                                      | Value         | Unit |  |  |  |

|---------------------|--------------------------------------------------|---------------|------|--|--|--|

| Electrical ratings  |                                                  |               |      |  |  |  |

| V <sub>IN</sub>     | Main input supply voltage                        | -0.3 to 4.8   | V    |  |  |  |

| V <sub>DDOTP</sub>  | OTP programming input supply voltage             | -0.3 to 10    | V    |  |  |  |

| V <sub>LICELL</sub> | Coin cell voltage                                | -0.3 to 3.6   | V    |  |  |  |

| V <sub>ESD</sub>    | ESD ratings Human body model Charge device model | ±2000<br>±500 | V    |  |  |  |

<sup>[1]</sup> ESD testing is performed in accordance with the human body model (HBM) (C<sub>ZAP</sub> = 100 pF, R<sub>ZAP</sub> = 1500 Ω), and the charge device model (CDM), robotic (C<sub>ZAP</sub> = 4.0 pF).

# 8.2 Thermal characteristics

Table 4. Thermal ratings

| Symbol            | Description (rating)                                      | Min      | Max       | Unit |  |  |  |

|-------------------|-----------------------------------------------------------|----------|-----------|------|--|--|--|

| Thermal ratings   |                                                           |          |           |      |  |  |  |

| T <sub>A</sub>    | Ambient operating temperature range MC32PF4210 MC34PF4210 | 0<br>-40 | 85<br>105 | °C   |  |  |  |

| T <sub>J</sub>    | Operating junction temperature range [1]                  | -40      | 125       | °C   |  |  |  |

| T <sub>ST</sub>   | Storage temperature range                                 | -65      | 150       | °C   |  |  |  |

| T <sub>PPRT</sub> | Peak package reflow temperature [2]                       | _        | [3]       | °C   |  |  |  |

Data sheet: technical data

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2018. All rights reserved.

<sup>[2] 10</sup> V maximum voltage rating during OTP fuse programming. 7.5 V maximum DC voltage rated otherwise.

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

| Symbol                  | Description (rating)                     | Description (rating) |   | Max | Unit |

|-------------------------|------------------------------------------|----------------------|---|-----|------|

| QFN56 thermal re        | sistance and package dissipation ratings |                      |   | -   |      |

| $R_{\Theta JA}$         | Junction to ambient  Natural convection  | [4] [5] [6]          |   |     | °C/W |

|                         | Four layer board (2s2p)                  |                      | _ | 28  |      |

|                         | Eight layer board (2s6p)                 |                      |   | 15  |      |

| R <sub>⊝JMA</sub>       | Junction to ambient (@200 ft/min)        | [4] [6]              |   |     | °C/W |

|                         | Four layer board (2s2p)                  |                      | _ | 22  |      |

| $R_{\Theta JB}$         | Junction to board                        | [7]                  | _ | 10  | °C/W |

| R <sub>Ө</sub> ЈСВОТТОМ | Junction to case bottom                  | [8]                  | _ | 1.2 | °C/W |

| ΨJT                     | Junction to package top                  | [9]                  |   |     | °C/W |

|                         | Natural convection                       |                      | _ | 2.0 |      |

- [1] Do not operate beyond 125 °C for extended period of time. Operation above 150 °C may cause permanent damage to the IC. See <u>Table 5</u> for thermal protection features.

- [2] Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause a malfunction or permanent damage to the device.

- [3] NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), go to <a href="https://www.nxp.com">www.nxp.com</a>, search by part number (remove prefixes/suffixes) and enter the core ID to view all orderable parts (MC33xxxD enter 33xxx), and review parametrics.

- [4] Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- [5] The board uses the JEDEC specifications for thermal testing (and simulation) JESD51-7 and JESD51-5.

- Per JEDEC JESD51-6 with the board horizontal

- Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- [8] Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- [9] Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letter (Ψ) is not available, the thermal characterization parameter is written as Psi-JT.

# 8.3 Power dissipation

During operation, the temperature of the die should not exceed the operating junction temperature noted in <u>Table 4</u>. To optimize the thermal management and to avoid overheating, the PF4210 provides thermal protection.

An internal comparator monitors the die temperature. Interrupts THERM110I, THERM120I, THERM125I, and THERM130I are generated when the respective thresholds specified in <a href="Table 5">Table 5</a> are crossed in either direction. The temperature range can be determined by reading the THERMxxxS bits in register INTSENSE0.

In the event of excessive power dissipation, thermal protection circuitry shuts down the PF4210. This thermal protection acts above the thermal protection threshold listed in Table 5. To avoid any unwanted power-down resulting from internal noise, the protection is debounced for 8.0 ms. This protection should be considered as a fail-safe mechanism and therefore the system should be configured so protection is not tripped under normal conditions.

Table 5. Thermal protection thresholds

| Parameter                           | Min | Тур | Max | Units |

|-------------------------------------|-----|-----|-----|-------|

| Thermal 110 °C threshold (THERM110) | 100 | 110 | 120 | °C    |

| Thermal 120 °C threshold (THERM120) | 110 | 120 | 130 | °C    |

PF4210

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2018. All rights reserved

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

| Parameter                           | Min | Тур | Max | Units |

|-------------------------------------|-----|-----|-----|-------|

| Thermal 125 °C threshold (THERM125) | 115 | 125 | 135 | °C    |

| Thermal 130 °C threshold (THERM130) | 120 | 130 | 140 | °C    |

| Thermal warning hysteresis          | 2.0 | _   | 4.0 | °C    |

| Thermal protection threshold        | 130 | 140 | 150 | °C    |

# 8.4 Electrical characteristics

# 8.4.1 General specifications

**Table 6. General PMIC static characteristics**

$T_{MIN}$  to  $T_{MAX}$  (see <u>Table 4</u>), VIN = 2.8 to 4.5 V, VDDIO = 1.7 to 3.6 V, typical external component values and full load current range, unless otherwise noted.

| Pin name  | Parameter       | Load condition | Min         | Max         | Unit |

|-----------|-----------------|----------------|-------------|-------------|------|

| PWRON     | V <sub>IL</sub> | _              | 0           | 0.2 * VSNVS | V    |

|           | $V_{IH}$        | _              | 0.8 * VSNVS | 3.6         | V    |

| RESETBMCU | V <sub>OL</sub> | −2.0 mA        | 0.0         | 0.4         | V    |

|           | V <sub>OH</sub> | Open drain     | 0.7* VIN    | VIN         | V    |

| SCL       | V <sub>IL</sub> | _              | 0.0         | 0.2 * VDDIO | V    |

|           | V <sub>IH</sub> | _              | 0.8 * VDDIO | 3.6         | V    |

| SDA       | V <sub>IL</sub> | _              | 0           | 0.2 * VDDIO | V    |

|           | V <sub>IH</sub> | _              | 0.8 * VDDIO | 3.6         | V    |

|           | $V_{OL}$        | −2.0 mA        | 0.0         | 0.4         | V    |

|           | V <sub>OH</sub> | Open drain     | 0.7 * VDDIO | VDDIO       | V    |

| NTB       | V <sub>OL</sub> | −2.0 mA        | 0.0         | 0.4         | V    |

|           | V <sub>OH</sub> | Open drain     | 0.7 * VIN   | VIN         | V    |

| SDWNB     | V <sub>OL</sub> | −2.0 mA        | 0.0         | 0.4         | V    |

|           | V <sub>OH</sub> | Open drain     | 0.7 * VIN   | VIN         | V    |

| STANDBY   | V <sub>IL</sub> | _              | 0           | 0.2 * VSNVS | V    |

|           | V <sub>IH</sub> | _              | 0.8 * VSNVS | 3.6         | V    |

| /DDOTP    | V <sub>IL</sub> | _              | 0           | 0.3         | V    |

|           | V <sub>IH</sub> | _              | 1.1         | 1.7         | V    |

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

# 8.4.2 Current consumption

### **Table 7. Current consumption summary**

$T_{MIN}$  to  $T_{MAX}$  (see Table 4), VIN = 3.6 V, VDDIO = 1.7 V to 3.6 V, LICELL = 1.8 V to 3.3 V, VSNVS = 3.0 V, typical external component values, unless otherwise noted. Typical values are characterized at VIN = 3.6 V, VDDIO = 3.3 V, LICELL = 3.0 V, VSNVS = 3.0 V and 25 °C, unless otherwise noted.

| Mode      | PF4210 conditions                                                                                                                                                                                               | System conditions                                                                                     |         | Тур        | Max                                      | Unit |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------|------------|------------------------------------------|------|

| Coin cell | VSNVS from LICELL All other blocks off VIN = 0.0 V VSNVSVOLT[2:0] = 110                                                                                                                                         | No load on VSNVS                                                                                      | [1] [2] | 4.0        | 7.0                                      | μА   |

| Off       | VSNVS from VIN or LICELL Wake-up from PWRON active 32 kHz RC on All other blocks off VIN ≥ UVDET                                                                                                                | No load on VSNVS, PMIC able to wake-up                                                                | [1] [3] | 17         | 25                                       | μА   |

| Sleep     | VSNVS from VIN Wake-up from PWRON active Trimmed reference active SW3A/B PFM Trimmed 16 MHz RC off 32 kHz RC on VREFDDR disabled                                                                                | No load on VSNVS. DDR memories in self refresh                                                        | [1]     | 122<br>122 | 220 <sup>[4]</sup><br>250 <sup>[5]</sup> | μΑ   |

| Standby   | VSNVS from either VIN or LICELL SW1A/B combined in PFM SW1C in PFM SW2 in PFM SW3A/B combined in PFM SW4 in PFM SWBST off Trimmed 16 MHz RC enabled Trimmed reference active VGEN1 to 6 enabled VREFDDR enabled | No load on VSNVS. Processor enabled in lowpower mode. All rails powered on except boost (load = 0 mA) | [1]     | 297<br>297 | 450 <sup>[4]</sup><br>550 <sup>[5]</sup> | μΑ   |

For PFM operation, headroom should be 300 mV or greater.

### **Detailed description** 9

The PF4210 is the power management integrated circuit (PMIC) designed primarily for use with NXP's i.MX 8M family of applications processors.

# 9.1 Features

This section summarizes the PF4210 features.

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2018. All rights reserved.

Additional current may be drawn in the coin cell mode when RESETBMCU is pulled up to VSNVS due to an internal path from RESETBMCU to V<sub>IN</sub>. The additional current is < 30  $\mu A$  with a pullup resistor of 100 k $\!\Omega.$

When VIN is below the UVDET threshold, in the range of 1.8 V  $\leq$  V<sub>IN</sub> < 2.65 V, the quiescent current increases by 50  $\mu$ A, typically.

<sup>[4]</sup> [5] From -40 °C to 85 °C

From -40 °C to 105 °C

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

- Input voltage range to PMIC: 2.8 V to 4.5 V

- · Buck regulators

- Four to six channel configurable

- SW1A/B/C, 4.5 A (single); 0.3 V to 1.875 V

- SW1A/B, 2.5 A (single/dual); SW1C 2.0 A (independent); 0.3 V to 1.875 V

- SW2, 2.5 A; 0.4 V to 3.3 V

- SW3A/B, 3.0 A (single/dual); 0.4 V to 3.3 V

- SW3A, 1.5 A (independent); SW3B, 1.5 A (independent); 0.4 V to 3.3 V

- SW4, 1.0 A; 0.4 V to 3.3 V

- SW4, VTT mode provide DDR termination at 50 % of SW3A

- Dynamic voltage scaling

- Modes: PWM, PFM, APS

- Programmable output voltage

- Programmable current limit

- Programmable soft start

- Programmable PWM switching frequency

- Programmable OCP with fault interrupt

- · Boost regulator

- SWBST, 5.0 V to 5.15 V, 0.6 A, OTG support

- Modes: PFM and auto

- OCP fault interrupt

- LDOs

- Six user-programmable LDOs

- VGEN1, 0.80 V to 1.55 V, 100 mA

- VGEN2, 0.80 V to 1.55 V, 250 mA

- VGEN3, 1.8 V to 3.3 V, 100 mA

- VGEN4, 1.8 V to 3.3 V, 350 mA

- VGEN5, 1.8 V to 3.3 V, 100 mA

- VGEN6, 1.8 V to 3.3 V, 200 mA

- · Soft start

- LDO/switch supply

- VSNVS (1.0/1.1/1.2/1.3/1.5/1.8/3.0 V), 1.5 mA (consumer version), 1.0 mA (industrial version)

- DDR memory reference voltage

- VREFDDR, 0.6 V to 0.9 V, 10 mA

- 16 MHz internal master clock

- OTP (one time programmable) memory for device configuration

- User programmable start-up sequence and timing

- · Battery backed memory including coin cell charger

- I<sup>2</sup>C interface

- · User programmable standby, sleep, and off modes

14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

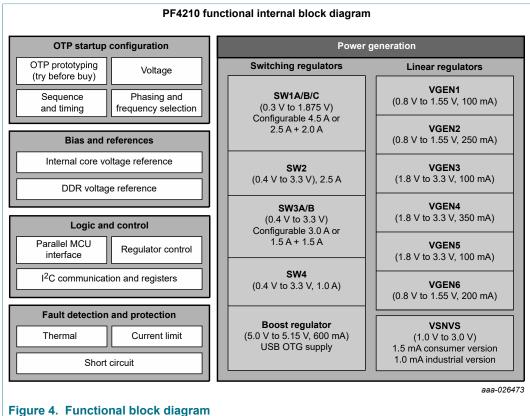

# 9.2 Functional block diagram

# 9.3 Functional description

# 9.3.1 Power generation

The PF4210 PMIC features four buck regulators (up to six independent outputs), one boost regulator, six general purpose LDOs, one switch/LDO combination and a DDR voltage reference to supply voltage for the application processor and peripheral devices.

The number of independent buck regulator outputs can be configured from four to six, thereby providing flexibility to operate with higher current capability, or to operate as independent outputs for applications requiring more voltage rails with lower current demands. SW1 and SW3 regulators can be configured as single/dual phase and/or independent converters. One of the buck regulators, SW4, can also operate as a tracking regulator when used for memory termination.

The buck regulators provide supply to processor cores and to other low voltage circuits such as IO and memory. Dynamic voltage scaling is provided to allow controlled supply rail adjustments for the processor cores and/or other circuitry.

Depending on the system power path configuration, the six general purpose LDO regulators can be directly supplied from the main input supply or from the switching regulators to power peripherals, such as audio, camera, bluetooth, and wireless LAN. A specific VREFDDR voltage reference is included to provide an accurate reference voltage for DDR memories operating with or without VTT termination. The VSNVS block

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2018. All rights reserved.

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

behaves as an LDO, or as a bypass switch to supply the SNVS/SRTC circuitry in the i.MX processors; VSNVS may be powered from VIN, or from a coin cell.

# 9.3.2 Control logic

The PF4210 PMIC is fully programmable via the I<sup>2</sup>C interface. Additional communication is provided by direct logic interfacing including interrupt and reset. Startup sequence of the device is selected based on the initial OTP configuration explained in the Section 10.1 "Startup", or by configuring the Try Before Buy feature to test different power up sequences before choosing the final OTP configuration.

The PF4210 PMIC has interfaces for the power buttons and a dedicated signaling interface with the processor. It also ensures supply of critical internal logic and other circuits from the coin cell, in case of brief interruptions from the main battery. A charger for the coin cell is included as well.

# 9.3.2.1 Interface signals

### 9.3.2.1.1 PWRON

PWRON is an input signal to the IC generating a turn on event. It can be configured to detect a level, or an edge using the PWRON\_CFG bit. See <u>Section 10.4.2.1 "Turn on events"</u> for more details.

### 9.3.2.1.2 STANDBY

STANDBY is an input signal to the IC. When it is asserted, the part enters standby mode and when deasserted, the part exits standby mode. STANDBY can be configured as active high or active low using the STANDBYINV bit. See <a href="Section 10.4.1.3">Section 10.4.1.3</a> "Standby mode" for more details.

**Note:** When operating the PMIC at VIN  $\leq$  2.85 V and VSNVS is programmed for a 3.0 V output, a coin cell must be present to provide VSNVS, or the PMIC does not reliably enter and exit the standby mode.

### 9.3.2.1.3 RESETBMCU

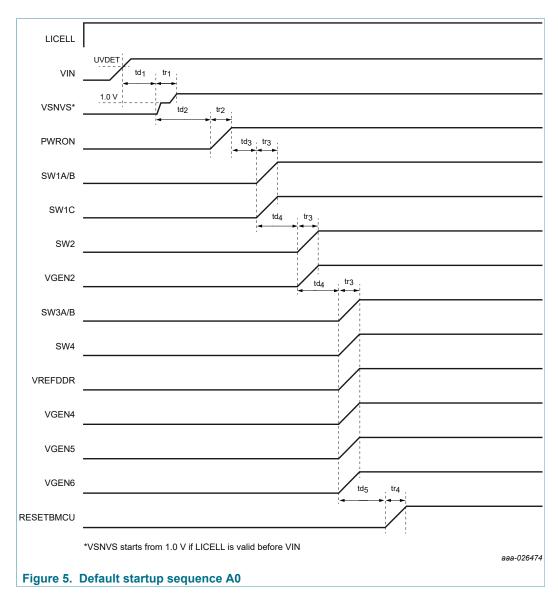

RESETBMCU is an open drain, active low output configurable for two modes of operation. In default mode, it is deasserted 2.0 ms to 4.0 ms after the last regulator if the startup sequence is enabled (see <a href="Figure 5">Figure 5</a>). In this mode, the signal can be used to bring the processor out of reset, or as an indicator that all supplies have been enabled; it is only asserted for a turn off event.

When configured for fault mode, RESETBMCU is deasserted after the startup sequence is completed only if no faults occurred during startup. At anytime, if a fault occurs and persists for 1.8 ms typically, RESETBMCU is asserted, LOW. The PF4210 is turned off if the fault persists for more than 100 ms typically.

The PWRON signal restarts the part, though if the fault persists, the sequence described above is repeated. To enter the fault mode, set bit OTP\_PG\_EN of register OTP PWRGD EN to 1. This register, 0xE8, is located in <u>Table 135</u> of the register map. To test the fault mode, the bit may be set during TBB prototyping, or the mode may be permanently chosen by programming OTP fuses.

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

### 9.3.2.1.4 SDWNB

SDWNB is an open drain, active low output notifying the processor of an imminent PMIC shut down. It is asserted low for one 32 kHz clock cycle before powering down and is then deasserted in the OFF state.

### 9.3.2.1.5 INTB

INTB is an open drain, active low output. It is asserted when any fault occurs, provided the fault interrupt is unmasked. INTB is deasserted after the fault interrupt is cleared by software, which requires writing a 1 to the fault interrupt bit.

# 10 Functional block requirements and behaviors

# 10.1 Startup

The PF4210 can be configured to start up from either the internal OTP configuration, or with a hard coded configuration built into the device. The internal hard coded configuration is enabled by connecting the VDDOTP pin to VCOREDIG through a 100 k $\Omega$  resistor. The OTP configuration is enabled by connecting VDDOTP to GND.

For NP (nonprogrammed) devices, selecting the OTP configuration causes the PF4210 to not start up. However, the PF4210 can be controlled through the I<sup>2</sup>C port for prototyping and programming. Once programmed, the NP device starts up with the customer programmed configuration.

# 10.1.1 Device startup configuration

<u>Table 8</u> shows the default configuration for all devices and the preprogrammed OTP configurations.

Table 8. Startup configuration

| Registers        | Default configuration | Preprogrammed OTP configuration |       |        |  |

|------------------|-----------------------|---------------------------------|-------|--------|--|

|                  | A0                    | <b>A</b> 1                      | A2    | А3     |  |

| Default I2C addr |                       | 0x                              | 08    |        |  |

| VSNVS_VOLT       | 3.0 V                 | 1.0 V                           | 1.0 V | 1.0 V  |  |

| SW1AB_VOLT       | 1.375 V               | 0.9 V                           | 0.9 V | 0.9 V  |  |

| SW1AB_SEQ        | 1                     | 4                               | 4     | 4      |  |

| SW1C_VOLT        | 1.375 V               | 0.9 V                           | 0.9 V | 0.9 V  |  |

| SW1C_SEQ         | 1                     | 4                               | 4     | 4      |  |

| SW2_VOLT         | 3.0 V                 | 1.1 V                           | 1.2 V | 1.35 V |  |

| SW2_SEQ          | 2                     | 6                               | 6     | 6      |  |

| SW3A_VOLT        | 1.5 V                 | 1.0 V                           | 1.0 V | 1.0 V  |  |

| SW3A_SEQ         | 3                     | 4                               | 4     | 4      |  |

| SW3B_VOLT        | 1.5 V                 | 1.0 V                           | 1.0 V | 1.0 V  |  |

| SW3B_SEQ         | 3                     | 4                               | 4     | 4      |  |

PF4210

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2018. All rights reserved

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

| Registers                   | Default configuration | Preprogra        | mmed OTP con     | figuration   |  |

|-----------------------------|-----------------------|------------------|------------------|--------------|--|

|                             | Α0                    | <b>A</b> 1       | A2               | А3           |  |

| SW4_VOLT                    | 1.8 V                 | 1.8 V            | 1.8 V            | 1.8 V        |  |

| SW4_SEQ                     | 3                     | 6                | 6                | 6            |  |

| SWBST_VOLT                  | _                     | <del>_</del>     | <del></del>      | <del>_</del> |  |

| SWBST_SEQ                   | _                     | _                | _                | _            |  |

| VREFDDR_SEQ                 | 3                     | 6                | 6                | 6            |  |

| VGEN1_VOLT                  | _                     | 1.5 V            | 1.5 V            | 1.5 V        |  |

| VGEN1_SEQ                   | _                     | 31               | 31               | 31           |  |

| VGEN2_VOLT                  | 1.5 V                 | 0.9 V            | 0.9 V            | 0.9 V        |  |

| VGEN2_SEQ                   | 2                     | 7                | 7                | 7            |  |

| VGEN3_VOLT                  | _                     | 1.8 V            | 1.8 V            | 1.8 V        |  |

| VGEN3_SEQ                   | _                     | 7                | 7                | 7            |  |

| VGEN4_VOLT                  | 1.8 V                 | 1.8 V            | 1.8 V            | 1.8 V        |  |

| VGEN4_SEQ                   | 3                     | 5                | 5                | 5            |  |

| VGEN5_VOLT                  | 2.5 V                 | 3.3 V            | 3.3 V            | 3.3 V        |  |

| VGEN5_SEQ                   | 3                     | 7                | 7                | 7            |  |

| VGEN6_VOLT                  | 2.8 V                 | 2.8 V            | 2.8 V            | 2.8 V        |  |

| VGEN6_SEQ                   | 3                     | 31               | 31               | 31           |  |

| PU CONFIG,<br>SEQ_CLK_SPEED | 1.0 ms                | 2.0 ms           | 2.0 ms           | 2.0 ms       |  |

| PU CONFIG,<br>SWDVS_CLK     | 6.25 mV/ms            | 1.5625 mV/ms     | 1.5625 mV/ms     | 1.5625 mV/ms |  |

| PU CONFIG, PWRON            |                       | Level se         | ensitive         |              |  |

| SW1AB CONFIG                | SW1AB sin             | gle phase, SW1C  | independent mod  | e, 2.0 MHz   |  |

| SW1C CONFIG                 | 2.0 MHz               |                  |                  |              |  |

| SW2 CONFIG                  |                       |                  |                  |              |  |

| SW3A CONFIG                 | 5                     | SW3AB single pha | se mode, 2.0 MHz | <u> </u>     |  |

| SW3B CONFIG                 |                       | 2.01             | MHz              |              |  |

| SW4 CONFIG                  |                       |                  |                  |              |  |

| PG EN                       |                       | RESETBMCU i      | n default mode   |              |  |

### Notes:

- Keep bit SW2ILIM = 0 for A1, A2, and A3 for max. rated output load current.

- Keep bit SW3xILIM = 0 for A1, A2, and A3 for max. rated output load current.

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

Table 9. Default startup sequence timing

| Parameter       | Description                                                                                                                              | Min              | Тур                      | Max              | Unit |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------|------------------|------|

| t <sub>D1</sub> | Turn-on delay of VSNVS                                                                                                                   |                  | 5.0                      |                  | ms   |

| t <sub>R1</sub> | Rise time of VSNVS                                                                                                                       | _                | 3.0                      | _                | ms   |

| t <sub>D2</sub> | User determined delay                                                                                                                    | _                | 1.0                      |                  | ms   |

| t <sub>R2</sub> | Rise time of PWRON                                                                                                                       | _                | [2]                      | _                | ms   |

| t <sub>D3</sub> | Turn-on delay of first regulator  SEQ_CLK_SPEED[1:0] = 00  SEQ_CLK_SPEED[1:0] = 01 [3]  SEQ_CLK_SPEED[1:0] = 10  SEQ_CLK_SPEED[1:0] = 11 | _<br>_<br>_<br>_ | 2.0<br>2.5<br>4.0<br>7.0 | _<br>_<br>_<br>_ | ms   |

| t <sub>R3</sub> | Rise time of regulators [4                                                                                                               | _                | 0.2                      | _                | ms   |

PF4210

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2018. All rights reserved.

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

| Parameter       | Description                | Min | Тур | Max | Unit |

|-----------------|----------------------------|-----|-----|-----|------|

| t <sub>D4</sub> | Delay between regulators   |     |     |     | ms   |

|                 | SEQ_CLK_SPEED[1:0] = 00    |     | 0.5 | _   |      |

|                 | SEQ_CLK_SPEED[1:0] = 01    | _   | 1.0 | _   |      |

|                 | SEQ_CLK_SPEED[1:0] = 10    | _   | 2.0 | _   |      |

|                 | SEQ_CLK_SPEED[1:0] = 11    | _   | 4.0 | _   |      |

| t <sub>R4</sub> | Rise time of RESETBMCU     | _   | 0.2 | _   | ms   |

| t <sub>D5</sub> | Turn-on delay of RESETBMCU | _   | 2.0 | _   | ms   |

<sup>[1]</sup> Assume LICELL voltage is valid before VIN is applied. If LICELL is not valid before VIN is applied, then VSNVS turn on delay may extend to a maximum of 24 ms.

# 10.1.2 One time programmability (OTP)

OTP allows the programming of startup configurations for a variety of applications. Before permanently programming the IC by programming fuses, a configuration may be prototyped by using the Try Before Buy (TBB) feature. An error correction code (ECC) algorithm is available to correct a single bit error and to detect multiple bit errors when fuses are programmed.

The parameters which can be configured by OTP are listed below.

- General: I<sup>2</sup>C slave address, PWRON pin configuration, startup sequence and timing

- Output voltage, dual/single phase or independent mode configuration, switching frequency, and soft start ramp rate

- Boost regulator and LDOs: output voltage

**Note:** When prototyping or programming fuses, ensure register settings are consistent with the hardware configuration. This is important for the buck regulators, where the quantity, size, and value of the inductors depend on the configuration (single/ dual phase or independent mode) and the switching frequency. Additionally, if an LDO is powered by a buck regulator, it is gated by the buck regulator in the startup sequence.

# 10.1.2.1 Startup sequence and timing

Each regulator has 5-bit allocated to program its startup time slot from a turn on event; therefore, each can be placed from position one to thirty-one in the startup sequence.

The all zeros code indicates a regulator is not part of the startup sequence and remains off (see <u>Table 10</u>). The delay between each position is equal; however, four delay options are available (see <u>Table 11</u>). The startup sequence terminates at the last programmed regulator.

Table 10. Startup sequence

| SWxx_SEQ[4:0]/ VGENx_SEQ[4:0]/<br>VREFDDR_SEQ[4:0] | Sequence               |

|----------------------------------------------------|------------------------|

| 00000                                              | Off                    |

| 00001                                              | SEQ_CLK_SPEED[1:0] * 1 |

| 00010                                              | SEQ_CLK_SPEED[1:0] * 2 |

<sup>[2]</sup> Depends on the external signal driving PWRON.

<sup>[3]</sup> Default configuration

<sup>[4]</sup> Rise time is a function of slew rate of regulators and nominal voltage selected.

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

| SWxx_SEQ[4:0]/ VGENx_SEQ[4:0]/<br>VREFDDR_SEQ[4:0] | Sequence                |

|----------------------------------------------------|-------------------------|

| *                                                  | *                       |

| *                                                  | *                       |

| *                                                  | *                       |

| *                                                  | *                       |

| 11111                                              | SEQ_CLK_SPEED[1:0] * 31 |

Table 11. Startup sequence clock speed

| SEQ_CLK_SPEED[1:0] | Time (µs) |

|--------------------|-----------|

| 00                 | 500       |

| 01                 | 1000      |

| 10                 | 2000      |

| 11                 | 4000      |

# 10.1.2.2 PWRON pin configuration

The PWRON pin can be configured as either a level sensitive input (PWRON\_CFG = 0), or as an edge sensitive input (PWRON\_CFG = 1). As a level sensitive input, an active high signal turns on the part and an active low signal turns off the part, or puts it into sleep mode.

As an edge sensitive input, such as when connected to a mechanical switch, a falling edge turns on the part and if the switch is held low for greater than or equal to 4.0 seconds, the part turns off or enters sleep mode.

**Table 12. PWRON configuration**

| PWRON_CFG | Mode                                                                                    |

|-----------|-----------------------------------------------------------------------------------------|

| 0         | PWRON pin HIGH = ON PWRON pin LOW = OFF or sleep mode                                   |

| 1         | PWRON pin pulled LOW momentarily = ON PWRON pin LOW for 4.0 seconds = OFF or sleep mode |

# 10.1.2.3 I<sup>2</sup>C address configuration

The I<sup>2</sup>C device address can be programmed from 0x08 to 0x0F. This allows flexibility to change the I<sup>2</sup>C address to avoid bus conflicts.

Address bit, I2C\_SLV\_ADDR[3] in OTP\_I2C\_ADDR register is hard coded to 1 while the lower three LSBs of the I $^2$ C address (I2C\_SLV\_ADDR[2:0]) are programmable as shown in Table 13.

Table 13. I<sup>2</sup>C address configuration

| I2C_SLV_ADDR[3] hard coded | I2C_SLV_ADDR[2:0] | I <sup>2</sup> C device address (Hex) |

|----------------------------|-------------------|---------------------------------------|

| 1                          | 000               | 0x08                                  |

PF4210

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2018. All rights reserved

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

| I2C_SLV_ADDR[3] hard coded | I2C_SLV_ADDR[2:0] | I <sup>2</sup> C device address (Hex) |

|----------------------------|-------------------|---------------------------------------|

| 1                          | 001               | 0x09                                  |

| 1                          | 010               | 0x0A                                  |

| 1                          | 011               | 0x0B                                  |

| 1                          | 100               | 0x0C                                  |

| 1                          | 101               | 0x0D                                  |

| 1                          | 110               | 0x0E                                  |

| 1                          | 111               | 0x0F                                  |

# 10.1.2.4 Soft start ramp rate

The startup ramp rate or soft start ramp rate can be selected from the options shown in Section 10.4.4.2.1 "Dynamic voltage scaling".

# 10.1.3 OTP prototyping

Before permanently programming fuses, it is possible to test the desired configuration by using the Try Before Buy feature. With this feature, the configuration is loaded from the OTP registers. These registers serve as temporary storage for the values to be written to the fuses, for the values read from the fuses, or for the values read from the default configuration. To avoid confusion, these registers are referred to as the TBBOTP registers. The portion of the register map concerned with OTP is shown in Table 135 and Table 136.

The contents of the TBBOTP registers are initialized to zero when a valid  $V_{\text{IN}}$  is first applied. The values loaded into the TBBOTP registers depend on the setting of the VDDOTP pin and on the value of the TBB\_POR and FUSE\_POR\_XOR bits (see Table 14).

- If VDDOTP = VCOREDIG (1.5 V), the values are loaded from the default configuration.

- If VDDOTP = 0.0 V, TBB\_POR = 0 and FUSE\_POR\_XOR = 1, the values are loaded from the fuses. In the PF4210, FUSE\_POR1, FUSE\_POR2, and FUSE\_POR3 are XOR'ed into the FUSE\_POR\_XOR bit. The FUSE\_POR\_XOR has to be 1 for fuses to be loaded. This can be achieved by setting any one or all of the FUSE\_PORx bits. It is required to set all of the FUSE\_PORx bits to be able to load the fuses.

- If VDDOTP = 0.0 V, TBB\_POR = 0 and FUSE\_POR\_XOR = 0, the TBBOTP registers remain initialized at zero.

The initial value of TBB\_POR is always 0; only when VDDOTP = 0.0 V and TBB\_POR is set to 1 and the values from the TBBOTP registers maintained and not loaded from a different source.

The contents of the TBBOTP registers are modified by  $I^2C$ . To communicate with  $I^2C$ , VIN must be valid and VDDIO to which SDA and SCL are pulled up, must be powered by a 1.7 V to 3.6 V supply. VIN or the coin cell voltage must be valid to maintain the contents of the registers. To power on with the contents of the TBBOTP registers, the following conditions must exist:

- · VIN is valid

- VDDOTP = 0.0 V

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

- TBB POR = 1

- Valid turn on event

# 10.1.4 Reading OTP fuses

As described in the previous section, the contents of the fuses are loaded to the TBBOTP registers when the following conditions are met:

- · VIN is valid

- VDDOTP = 0.0 V

- TBB POR = 0

- FUSE POR XOR = 1

If ECC were enabled at the time the fuses were programmed, the error corrected values can be loaded into the TBBOTP registers if desired. Once the fuses are loaded and a turn on event occurs, the PMIC powers on with the configuration programmed in the fuses.

# 10.1.5 Programming OTP fuses

The parameters which can be programmed are shown in the TBBOTP registers in <u>Table 135</u> of the register map. The PF4210 offers ECC, the control registers for which functions are located in <u>Table 136</u> of the register map.

There are ten banks of twenty-six fuses each that can be programmed. Programming the fuses requires an 8.25 V, 100 mA supply powering the VDDOTP pin, bypassed with 10 to  $20~\mu\text{F}$  of capacitance.

Table 14. Source of startup sequence

| The state of the s |         |              |                       |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|-----------------------|--|--|

| VDDOTP (V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TBB_POR | FUSE_POR_XOR | Startup sequence      |  |  |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0       | 0            | None                  |  |  |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0       | 1            | OTP fuses             |  |  |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1       | х            | TBBOTP registers      |  |  |

| 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | х       | х            | Default configuration |  |  |

### 10.2 16 MHz and 32 kHz clocks

There are two clocks: a trimmed 16 MHz, RC oscillator, and an untrimmed 32 kHz, RC oscillator. The 16 MHz oscillator is specified within -8.0/+8.0 %.

The 32 kHz untrimmed clock is only used in the following conditions:

- VIN < UVDET

- · All regulators are in sleep mode

- · All regulators are in PFM switching mode

A 32 kHz clock, derived from the 16 MHz trimmed clock, is used when accurate timing is needed under the following conditions:

- During start up, VIN > UVDET

- PWRON\_CFG = 1, for power button debounce timing

PF4210

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2018. All rights reserved

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

In addition, when the 16 MHz is active in the ON mode, the debounce time in <u>Table 25</u> are referenced to the 32 kHz derived from the 16 MHz clock. The exceptions are the LOWVINI and PWRONI interrupts, which are referenced to the 32 kHz untrimmed clock.

# Table 15. 16 MHz clock specifications

$T_{MIN}$  to  $T_{MAX}$  (see <u>Table 4</u>),  $V_{IN}$  = 2.8 V to 4.5 V, LICELL = 1.8 V to 3.3 V and typical external component values. Typical values are characterized at  $V_{IN}$  = 3.6 V, LICELL = 3.0 V, and 25 °C, unless otherwise noted.

| Symbol               | Parameters                  | Min  | Тур | Max  | Units |

|----------------------|-----------------------------|------|-----|------|-------|

| V <sub>IN16MHz</sub> | Operating voltage from VIN  | 2.8  | _   | 4.5  | V     |

| f <sub>16MHZ</sub>   | 16 MHz clock frequency      | 14.7 | 16  | 17.2 | MHz   |

| f <sub>2MHZ</sub>    | 2.0 MHz clock frequency [1] | 1.84 | _   | 2.15 | MHz   |

<sup>[1] 2.0</sup> MHz clock is derived from the 16 MHz clock.

# 10.2.1 Clock adjustment

The 16 MHz clock and hence the switching frequency of the regulators, can be adjusted to improve the noise integrity of the system. By changing the factory trim values of the 16 MHz clock, the user may add an offset as small as  $\pm 3.0$  % of the nominal frequency. Contact your NXP representative for detailed information on this feature.

# 10.3 Bias and references block description

# 10.3.1 Internal core voltage references

All regulators use the main band gap as the reference. The main band gap is bypassed with a capacitor at VCOREREF. The band gap and the rest of the core circuitry are supplied from VCORE.

The performance of the regulator is directly dependent on the performance of the band gap. No external DC loading is allowed on VCORE, VCOREDIG, or VCOREREF. VCOREDIG is powered as long as there is a valid supply and/or valid coin cell. <u>Table 16</u> shows the main characteristics of the core circuitry.

Table 16. Core voltages electrical specifications

$T_{MIN}$  to  $T_{MAX}$  (see Table 4),  $V_{IN}$  = 2.8 V to 4.5 V, LICELL = 1.8 V to 3.3 V, and typical external component values. Typical values are characterized at  $V_{IN}$  = 3.6 V, LICELL = 3.0 V, and 25 °C, unless otherwise noted. [1]

| Symbol                                    | Parameters                                                 | Min           | Тур          | Max | Units |  |  |  |  |

|-------------------------------------------|------------------------------------------------------------|---------------|--------------|-----|-------|--|--|--|--|

| VCOREDIG (digi                            | VCOREDIG (digital core supply)                             |               |              |     |       |  |  |  |  |

| VCOREDIG                                  | Output voltage ON mode Coin cell mode and OFF              | [2]<br>—<br>— | 1.5<br>1.3   |     | V     |  |  |  |  |

| VCORE (analog                             | core supply)                                               |               |              |     | J     |  |  |  |  |

| V <sub>CORE</sub>                         | Output voltage ON mode and charging OFF and coin cell mode |               | 2.775<br>0.0 |     | V     |  |  |  |  |

| VCOREREF (band gap / regulator reference) |                                                            |               |              |     |       |  |  |  |  |

PF4210

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2018. All rights reserved

# 14-channel Power Management Integrated Circuit (PMIC) for audio/video applications

| Symbol                   | Parameters        | Min | Тур  | Max | Units |

|--------------------------|-------------------|-----|------|-----|-------|