Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Document Number: MC33663

Rev. 2.0, 12/2013

# LIN 2.1 / SAEJ2602-2 Dual LIN Physical Layer

The local interconnect network (LIN) is a serial communication protocol designed to support automotive networks in conjunction with controller area network (CAN). As the lowest level of a hierarchical network, LIN enables cost-effective communication with sensors and actuators when all the features of CAN are not required.

The 33663 product line integrates two physical layer LIN bus dedicated to automotive LIN sub-bus applications. The MC33663LEF and MC33663SEF devices offer normal baud rate (20 kbps) and the MC33663JEF slow baud rate (10 kbps). Both devices integrate fast baud rate (above 100 kbps) for test and programming modes. They present excellent electromagnetic compatibility (EMC) and radiated emission performance, electrostatic discharge (ESD) robustness and safe behavior, in the event of LIN bus short-to-ground or LIN bus leakage during low-power mode.

#### **Features**

- Operational from  $V_{SUP}\ 7.0$  to 18 V DC, functional up to 27 V DC, and handles 40 V during load dump

- Compatible with LIN protocol specification 2.1, and SAEJ2602-2

- · Very high immunity against electromagnetic interference

- · Low standby current in Sleep mode

- · Over-temperature protection

- · Permanent dominant state detection

- · Fast baud rate mode selection reported by RXD

- Active bus waveshaping offering excellent radiated emission performance

- Sustains ±15.0 kV ESD IEC6100-4-2 on LIN BUS and VSUP pins

- 5.0 and 3.3 V compatible digital inputs without any external components required

## 33663

#### **DUAL LIN TRANSCEIVER**

EF SUFFIX (PB-FREE) 98ASB42565B 14-PIN SOICN

| ORDERING INFORMATION                                                                             |              |          |  |  |

|--------------------------------------------------------------------------------------------------|--------------|----------|--|--|

| Device (add an R2 suffix for Tape and reel orders)  Temperature Range (T <sub>A</sub> )  Package |              |          |  |  |

| MC33663ALEF                                                                                      |              |          |  |  |

| MC33663AJEF                                                                                      | -40 to 125°C | 14 SOICN |  |  |

| MC33663ASEF                                                                                      |              |          |  |  |

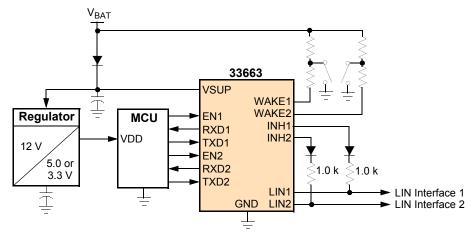

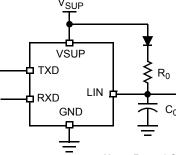

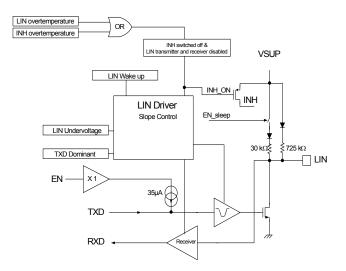

Figure 1. 33663 Simplified Application Diagram

<sup>\*</sup> This document contains certain information on a new product.

Specifications and information herein are subject to change without notice.

## **DEVICE VARIATIONS**

**Table 1. Device Variations**

| Freescale Part No.<br>(Add an R2 suffix for<br>Tape and reel orders) | Maximum Baud Rate                                                    | Temperature Range (T <sub>A</sub> ) | Package  |

|----------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|----------|

| MC33663ALEF                                                          | 20 kbps                                                              |                                     |          |

| MC33663ASEF                                                          | 20 kbps with restricted limits for transmitter and receiver symmetry | -40 to 125 °C                       | 14 SOICN |

| MC33663AJEF                                                          | 10 kbps                                                              |                                     |          |

### INTERNAL BLOCK DIAGRAM

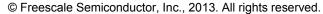

Figure 2. 33663 Simplified Internal Block Diagram

### **PIN CONNECTIONS**

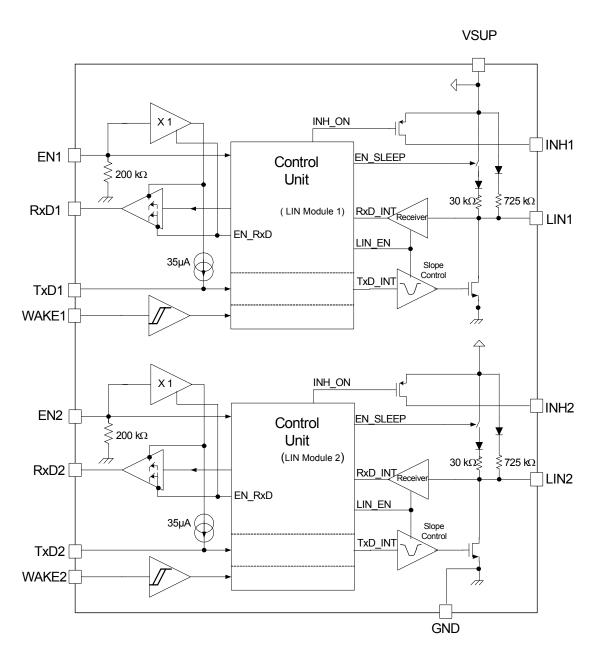

Figure 3. 33663 14-SOIC Pin Connections

Table 2. 33663 Pin Definitions

| Pin | Pin Name | Formal Name    | Definition                                                                                                                                                                                                |

|-----|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | WAKE1    | Wake Input     | This pin is a high-voltage input used to wake-up the LIN1 from Sleep mode.                                                                                                                                |

| 2   | TXD1     | Data Input     | This pin is the transmitter input of the LIN1 interface which controls the state of the bus output.                                                                                                       |

| 3   | LIN1     | LIN Bus        | This bidirectional pin represents the LIN1 single-wire bus transmitter and receiver.                                                                                                                      |

| 4   | LIN2     | LIN Bus        | This bidirectional pin represents the LIN2 single-wire bus transmitter and receiver.                                                                                                                      |

| 5   | INH2     | Inhibit Output | This pin can have two main functions: controlling an external switchable voltage regulator having an inhibit input, or driving an external bus resistor connected to LIN2 in the master node application. |

| 6   | RXD2     | Data Output    | This pin is the receiver output of the LIN2 interface, which reports the state of the bus voltage to the MCU interface.                                                                                   |

| 7   | EN2      | Enable Control | This pin controls the operation mode of the LIN2 interface.                                                                                                                                               |

| 8   | WAKE2    | Wake Input     | This pin is a high-voltage input used to wake-up the LIN2 device from Sleep mode.                                                                                                                         |

| 9   | GND      | Ground         | This pin is the device ground pin.                                                                                                                                                                        |

| 10  | TXD2     | Data Input     | This pin is the transmitter input of the LIN2 interface, which controls the state of the bus output.                                                                                                      |

| 11  | VSUP     | Power Supply   | This pin is device battery level power supply.                                                                                                                                                            |

| 12  | INH1     | Inhibit Output | This pin can have two main functions: controlling an external switchable voltage regulator having an inhibit input, or driving an external bus resistor connected to LIN1 in the master node application. |

| 13  | RXD1     | Data Output    | This pin is the receiver output of the LIN1 interface, which reports the state of the bus voltage to the MCU interface.                                                                                   |

| 14  | EN1      | Enable Control | This pin controls the operation mode of the LIN1 interface.                                                                                                                                               |

#### **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

#### **Table 3. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                                                                                                                                                                                                                    | Symbol                                        | Value       | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------|------|

| ELECTRICAL RATINGS                                                                                                                                                                                                                                                         |                                               |             |      |

| Power Supply Voltage (VSUP)                                                                                                                                                                                                                                                |                                               |             | V    |

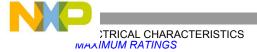

| Normal Operation (DC)  Transient input voltage with external component (according to ISO7637-2 & ISO7637-3 & "Hardware Requirements for LIN, CAN, and Flexray Interfaces in Automotive Applications" specification Rev. 1.1/December 2nd, 2009) (See Table 4 and Figure 4) | V <sub>SUP(SS)</sub>                          | -0.3 to 27  |      |

| - Pulse 1 (test up to the limit for Damage - Class A <sup>(1)</sup> )                                                                                                                                                                                                      | V                                             | -100        |      |

| - Pulse 2a (test up to the limit for Damage - Class $A^{\left(1\right)}$ )                                                                                                                                                                                                 | V <sub>SUP(S1)</sub><br>V <sub>SUP(S2A)</sub> | +75         |      |

| - Pulse 3a (test up to the limit for Damage - Class $A^{(1)}$ )                                                                                                                                                                                                            | V <sub>SUP(S2A)</sub>                         | -150        |      |

| - Pulse 3b (test up to the limit for Damage - Class A <sup>(1)</sup> )                                                                                                                                                                                                     | V <sub>SUP(S3B)</sub>                         | +100        |      |

| - Pulse 5b (Class A) <sup>(1)</sup>                                                                                                                                                                                                                                        | V <sub>SUP(S5B)</sub>                         | -0.3 to 40  |      |

| Logic Voltage (RXD <sub>1,2</sub> , TXD <sub>1,2</sub> , EN <sub>1,2</sub> Pins)                                                                                                                                                                                           | V <sub>LOG</sub>                              | -0.3 to 5.5 | V    |

| WAKE (V <sub>WAKE1</sub> ,V <sub>WAKE2</sub> )                                                                                                                                                                                                                             |                                               |             | V    |

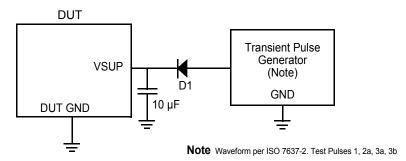

| Normal Operation with in series $2*18 \text{ k}\Omega$ resistor (DC)                                                                                                                                                                                                       | V <sub>WAKE(SS)</sub>                         | -27 to 40   |      |

| Transient input voltage with external component (according to ISO7637-2 & ISO7637-3 & "Hardware Requirements for LIN, CAN and Flexray Interfaces in Automotive Applications" specification Rev1.1 / December 2nd, 2009) (See Table 4 and Figure 5)                         |                                               |             |      |

| - Pulse 1 (test up to the limit for Damage - Class D <sup>(2)</sup> )                                                                                                                                                                                                      | V <sub>WAKE(S1)</sub>                         | -100        |      |

| - Pulse 2a (test up to the limit for Damage - Class D <sup>(2)</sup> )                                                                                                                                                                                                     | V <sub>WAKE(S2A)</sub>                        | +75         |      |

| - Pulse 3a (test up to the limit for Damage - Class D <sup>(2)</sup> )                                                                                                                                                                                                     | V <sub>WAKE(S3A)</sub>                        | -150        |      |

| - Pulse 3b (test up to the limit for Damage - Class $D^{(2)}$ )                                                                                                                                                                                                            | V <sub>WAKE(S3B)</sub>                        | +100        |      |

| LIN Bus Voltage (V <sub>LIN1</sub> , V <sub>LIN2</sub> )                                                                                                                                                                                                                   |                                               |             | V    |

| Normal Operation (DC)                                                                                                                                                                                                                                                      | V <sub>LIN(SS)</sub>                          | -27 to 40   |      |

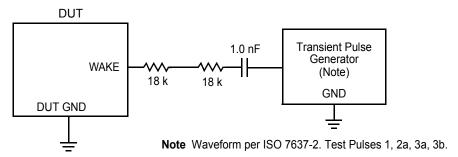

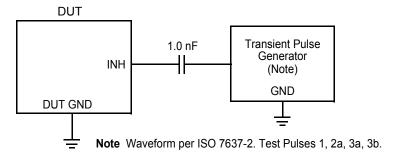

| Transient (Coupled Through 1.0 nF Capacitor) (according to ISO7637-2 & ISO7637-3) (See <u>Table 4</u> and <u>Figure 6</u> )                                                                                                                                                |                                               |             |      |

| - Pulse 1 (test up to the limit for Damage - Class D <sup>(2)</sup> )                                                                                                                                                                                                      | V <sub>LIN(S1)</sub>                          | -100        |      |

| - Pulse 2a (test up to the limit for Damage - Class $D^{(2)}$ )                                                                                                                                                                                                            | V <sub>LIN(S2A)</sub>                         | +75         |      |

| - Pulse 3a (test up to the limit for Damage - Class $D^{(2)}$ )                                                                                                                                                                                                            | V <sub>LIN(S3A)</sub>                         | -150        |      |

| - Pulse 3b (test up to the limit for Damage - Class D <sup>(2)</sup> )                                                                                                                                                                                                     | V <sub>LIN(S3B)</sub>                         | +100        |      |

- 1. Class A: All functions of a device/system perform as designed during and after exposure to disturbance.

- 2. Class D: At least one function of the Transceiver stops working properly during the test and will return into proper operation automatically when the exposure to the disturbance has ended. No physical damage of the IC occurs.

#### **Table 3. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                                                                                                                                                                                        | Symbol                | Value                          | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------|------|

| ELECTRICAL RATINGS                                                                                                                                                                                                                             |                       |                                |      |

| INH Voltage/Current (V <sub>INH1</sub> , V <sub>INH2</sub> )                                                                                                                                                                                   |                       |                                | V    |

| DC Voltage                                                                                                                                                                                                                                     | $V_{INH}$             | -0.3 to V <sub>SUP</sub> + 0.3 |      |

| Transient (Coupled Through 1.0 nF Capacitor, according to ISO7637-2 & ISO7637-3 & "Hardware Requirements for LIN, CAN and Flexray Interfaces in Automotive Applications" specification Rev1.1 / December 2nd, 2009) (See Table 4 and Figure 7) |                       |                                |      |

| - Pulse 1 (test up to the limit for Damage - Class D <sup>(3)</sup> )                                                                                                                                                                          | V <sub>INH(S1)</sub>  | -100                           |      |

| - Pulse 2a (test up to the limit for Damage - Class D <sup>(3)</sup> )                                                                                                                                                                         | V <sub>INH(S2a)</sub> | +75                            |      |

| - Pulse 3a (test up to the limit for Damage - Class D <sup>(3)</sup> )                                                                                                                                                                         | V <sub>INH(S3a)</sub> | -150                           |      |

| - Pulse 3b (test up to the limit for Damage - Class D <sup>(3)</sup> )                                                                                                                                                                         | V <sub>INH(S3b)</sub> | +100                           |      |

#### Notes

3. Class D: At least one function of the Transceiver stops working properly during the test and will return into proper operation automatically when the exposure to the disturbance has ended. No physical damage of the IC occurs.

### Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                                                                                       | Symbol                         | Value          | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|------|

| ELECTRICAL RATINGS                                                                                                                            |                                |                |      |

| ESD Capability                                                                                                                                |                                |                | V    |

| AECQ100                                                                                                                                       |                                |                |      |

| Human Body Model - JESD22/A114 ( $C_{ZAP}$ = 100 pF, $R_{ZAP}$ = 1500 $\Omega$ )                                                              |                                |                |      |

| LIN1, LIN2 pins versus GND                                                                                                                    | V <sub>ESD1-1</sub>            | ±10.0 k        |      |

| WAKE1, WAKE2 pins versus GND                                                                                                                  | V <sub>ESD1-2</sub>            | ±8.0 k         |      |

| All other Pins                                                                                                                                | V <sub>ESD1-4</sub>            | ±4.0 k         |      |

| Charge Device Model - JESD22/C101 (C <sub>ZAP</sub> = 4.0 pF)                                                                                 |                                |                |      |

| Corner pins (Pins 1, 7, 8 and 14)                                                                                                             | V <sub>ESD2-1</sub>            | ±750           |      |

| All other pins (Pins 2-6, 9-13)                                                                                                               | V <sub>ESD2-2</sub>            | ±750           |      |

| Machine Model - JESD22/A115 ( $C_{ZAP}$ = 220 pF, $R_{ZAP}$ = 0 $\Omega$ )                                                                    |                                |                |      |

| All pins                                                                                                                                      | V <sub>ESD3-1</sub>            | ±200           |      |

| According to "Hardware Requirements for LIN, CAN and Flexray Interfaces in Automotive Applications" specification Rev1.1 / December 2nd, 2009 |                                |                |      |

| $(C_{ZAP} = 150 \text{ pF}, R_{ZAP} = 330 \Omega)$                                                                                            |                                |                |      |

| Contact Discharge, Unpowered                                                                                                                  |                                |                |      |

| LIN1, LIN2 pins without capacitor                                                                                                             | V <sub>ESD4-1</sub>            | ±15 k          |      |

| LIN1, LIN2 pins with 220 pF capacitor                                                                                                         | V <sub>ESD4-2</sub>            | ±15 k          |      |

| VSUP (10 μF to ground)                                                                                                                        | V <sub>ESD4-3</sub>            | ±25 k          |      |

| WAKE1, WAKE2 (2*18 kΩ serial resistor)                                                                                                        | V <sub>ESD4-4</sub>            | ±20 k          |      |

| LIN1, LIN2 pins with 220 pF capacitor and indirect ESD coupling (according to ISO10605 - Annex F)                                             | V <sub>ESD4-5</sub>            | ±15 k          |      |

| According to ISO10605 - Rev 2008 test specification                                                                                           |                                |                |      |

| (2.0 kΩ / 150 pF) - Unpowered - Contact discharge                                                                                             | V <sub>ESD5-1</sub>            | ±25 k          |      |

| LIN1, LIN2 pins without capacitor                                                                                                             |                                | ±25 k          |      |

| LIN1, LIN2 pins with 220 pF capacitor                                                                                                         | V <sub>ESD5-2</sub>            | ±25 k          |      |

| VSUP (10 μF to ground)                                                                                                                        | V <sub>ESD5-3</sub>            | ±25 k<br>±25 k |      |

| WAKE1, WAKE2 (2*18 kΩ serial resistor)                                                                                                        | V <sub>ESD5-4</sub>            | IZU K          |      |

| (2.0 kΩ / 330 pF) - Powered - Contact discharge                                                                                               | V <sub>ESD6-1</sub>            | ±8 k           |      |

| LIN1, LIN2 pins without capacitor                                                                                                             | VESD6-1<br>V <sub>ESD6-2</sub> | ±8 k           |      |

| LIN1, LIN2 pins with 220 pF capacitor                                                                                                         | VESD6-2<br>V <sub>ESD6-3</sub> | ±25 k          |      |

| VSUP (10 μF to ground)                                                                                                                        | VESD6-3<br>V <sub>ESD6-4</sub> | ±25 k          |      |

| WAKE1, WAKE2 (2*18 kΩ serial resistor)                                                                                                        | *ESD6-4                        | TZJ K          |      |

#### Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                          | Symbol            | Value                    | Unit |

|------------------------------------------------------------------|-------------------|--------------------------|------|

| Thermal Ratings                                                  |                   |                          |      |

| Operating Temperature Ambient Junction                           | T <sub>A</sub>    | -40 to 125<br>-40 to 150 | °C   |

| Storage Temperature                                              | T <sub>STG</sub>  | -40 to 150               | °C   |

| Thermal Resistance, Junction to Ambient                          | $R_{	hetaJA}$     | 150                      | °C/W |

| Peak package reflow temperature during reflow <sup>(4),(5)</sup> | T <sub>PPRT</sub> | Note 5                   | °C   |

| Thermal Shutdown Temperature                                     | T <sub>SHUT</sub> | 150 to 200               | °C   |

| Thermal Shutdown Hysteresis Temperature                          | T <sub>HYST</sub> | 20                       | °C   |

- 4. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 5. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

Table 4. Limits / Maximum test voltage for transient immunity tests

| Test Pulse | V <sub>S</sub> [V] | Pulse repetition<br>frequency [Hz] (1/T <sub>1</sub> ) | Test duration [min] | <b>R</b> <sub>i</sub> [Ω] | Remarks             |

|------------|--------------------|--------------------------------------------------------|---------------------|---------------------------|---------------------|

| 1          | -100               | 2                                                      | 1 for function test | 10                        | t <sub>2</sub> = 0s |

| 2a         | +75                | 2                                                      | 10 for damage test  | 2                         |                     |

| 3a         | -150               | 10                                                     |                     | 50                        |                     |

| 3b         | +100               | 10                                                     |                     | 50                        |                     |

Figure 4. Test Circuit for Transient Test Pulses (V<sub>SUP</sub>)

Figure 5. Test Circuit for Transient Test Pulses (WAKE1,WAKE2)

Figure 6. Test Circuit for Transient Test Pulses (LIN1,LIN2)

Figure 7. Test Circuit for Transient Test Pulses (INH1,INH2)

#### STATIC ELECTRICAL CHARACTERISTICS

#### **Table 5. Static Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                               | Symbol                                                                                                               | Min         | Тур                         | Max                         | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------|-----------------------------|------|

| VSUP PIN (DEVICE POWER SUPPLY)                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      |             |                             |                             |      |

| Nominal Operating Voltage                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>SUP</sub>                                                                                                     | 7.0         | 13.5                        | 18.0                        | V    |

| Functional Operating Voltage <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>SUPOP</sub>                                                                                                   | 6.7         | _                           | 27                          | ٧    |

| Load Dump                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>SUPLD</sub>                                                                                                   | 1           | _                           | 40                          | ٧    |

| Power-On Reset (POR) Threshold  V <sub>SUP</sub> Ramp Down and INH1, INH2 goes High to Low                                                                                                                                                                                                                                                                                                                                                   | V <sub>POR</sub>                                                                                                     | 3.5         | _                           | 5.3                         | V    |

| Power-On Reset (POR) Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>PORHYST</sub>                                                                                                 | -           | 270                         | -                           | mV   |

| V <sub>SUP</sub> Under-voltage Threshold (positive and negative) Transmission disabled and LIN1,LIN2 bus goes in recessive                                                                                                                                                                                                                                                                                                                   | $V_{UVL}, V_{UVH}$                                                                                                   | 5.8         | _                           | 6.7                         | V    |

| V <sub>SUP</sub> Under-voltage Hysteresis (V <sub>UVL</sub> - V <sub>UVH</sub> )                                                                                                                                                                                                                                                                                                                                                             | V <sub>UVHYST</sub>                                                                                                  | -           | 130                         | -                           | mV   |

| Supply Current LIN1 and LIN2 in Sleep Mode $V_{SUP} \leq 13.5 \text{ V}, \text{ Recessive State} \\ 13.5 \text{ V} < V_{SUP} < 27 \text{ V} \\ V_{SUP} \leq 13.5 \text{ V}, \text{ Shorted to GND}$                                                                                                                                                                                                                                          | <sub>S1</sub><br>  <sub>S2</sub><br>  <sub>S3</sub>                                                                  | -<br>-<br>- | 12.0<br>-<br>48             | 22<br>36<br>140             | μА   |

| Supply Current LIN1 Normal Mode - LIN2 Sleep Mode (and vice versa)  Bus <sub>1</sub> Recessive, BUS <sub>2</sub> Sleep, Excluding INH1,INH2  OR (Bus <sub>2</sub> Recessive, BUS <sub>1</sub> Sleep, Excluding INH1,INH2)                                                                                                                                                                                                                    | ls_N_REC1,2                                                                                                          | -           | 4.0                         | 5.0                         | mA   |

| ${\sf Bus}_1$ Dominant, ${\sf BUS}_2$ Sleep, Excluding INH1,INH2 OR ( ${\sf Bus}_2$ Dominant, ${\sf BUS}_1$ Sleep, Excluding INH1,INH2)                                                                                                                                                                                                                                                                                                      | I <sub>S_N_DOM1,2</sub>                                                                                              | -           | 6.0                         | 8.0                         |      |

| Supply Current when LIN1 and LIN2 are in Normal or Slow or Fast Mode Bus <sub>1</sub> Recessive, Bus <sub>2</sub> Recessive, Excluding INH1,INH2 Output Current Bus <sub>1</sub> Recessive, Bus <sub>2</sub> Dominant, Excluding INH1,INH2 Output Current Bus <sub>1</sub> Dominant, Bus <sub>2</sub> Recessive, Excluding INH1,INH2 Output Current Bus <sub>1</sub> Dominant, Bus <sub>2</sub> Dominant, Excluding INH1,INH2 Output Current | I <sub>S</sub> (REC1,REC2)<br>I <sub>S</sub> (REC1,DOM2)<br>I <sub>S</sub> (DOM1,REC2)<br>I <sub>S</sub> (DOM1,DOM2) |             | 8.0<br>12.0<br>12.0<br>12.0 | 9.0<br>13.0<br>13.0<br>16.0 | mA   |

| RXD1, RXD2 OUTPUT PINS (LOGIC)                                                                                                                                                                                                                                                                                                                                                                                                               | , , ,                                                                                                                |             |                             |                             |      |

| Low Level Output Voltage $I_{\text{IN}} \leq 1.5 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>OL</sub>                                                                                                      | 0.0         | -                           | 0.9                         | V    |

| High Level Output Voltage $V_{EN}$ = 5.0 V, $I_{OUT} \le 250 \ \mu A$ $V_{EN}$ = 3.3 V, $I_{OUT} \le 250 \ \mu A$                                                                                                                                                                                                                                                                                                                            | V <sub>OH</sub>                                                                                                      | 4.25<br>3.0 |                             | 5.25<br>3.5                 | V    |

#### Notes

6. Device is functional. All features are operating. Electrical parameters are not guaranteed.

#### **Table 5. Static Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                                                      | Symbol                   | Min  | Тур | Max | Unit             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-----|-----|------------------|

| TXD1, TXD2 INPUT PINS (LOGIC)                                                                                                                                                                       |                          |      |     |     |                  |

| Low Level Input Voltage                                                                                                                                                                             | V <sub>IL</sub>          | _    | _   | 0.8 | V                |

| High Level Input Voltage                                                                                                                                                                            | V <sub>IH</sub>          | 2.0  | _   | _   | V                |

| Input Threshold Voltage Hysteresis                                                                                                                                                                  | V <sub>INHYST</sub>      | 100  | 300 | 600 | mV               |

| Pull-up Current Source<br>V <sub>EN</sub> = 5.0 V, 1.0 V < V <sub>TXD</sub> < 3.5 V                                                                                                                 | I <sub>PU</sub>          | -60  | -35 | -20 | μА               |

| EN1, EN2 INPUT PINS (LOGIC)                                                                                                                                                                         |                          |      |     | l   |                  |

| Low Level Input Voltage                                                                                                                                                                             | V <sub>IL</sub>          | -    | _   | 0.8 | V                |

| High Level Input Voltage                                                                                                                                                                            | V <sub>IH</sub>          | 2.0  | -   | -   | V                |

| Input Voltage Threshold Hysteresis                                                                                                                                                                  | V <sub>INHYST</sub>      | 100  | 400 | 600 | mV               |

| Pull-down Resistor                                                                                                                                                                                  | R <sub>PD</sub>          | 100  | 230 | 350 | kohm             |

| LIN PHYSICAL LAYER - TRANSCEIVER LIN (LIN1, LIN2) <sup>(7)</sup>                                                                                                                                    |                          |      |     |     |                  |

| Operating Voltage Range <sup>(8)</sup>                                                                                                                                                              | V <sub>BAT</sub>         | 8.0  | _   | 18  | V                |

| Supply Voltage Range                                                                                                                                                                                | V <sub>SUP</sub>         | 7.0  | _   | 18  | V                |

| Voltage Range (within which the device is not destroyed)                                                                                                                                            | V <sub>SUP_NON_OP</sub>  | -0.3 | _   | 40  | V                |

| Current Limitation for Driver Dominant State Driver ON, V <sub>BUS</sub> = 18 V                                                                                                                     | I <sub>BUS_LIM</sub>     | 40   | 90  | 200 | mA               |

| Input Leakage Current at the Receiver Driver off; V <sub>BUS</sub> = 0 V; V <sub>BAT</sub> = 12 V                                                                                                   | I <sub>BUS_PAS_DOM</sub> | -1.0 | _   | _   | mA               |

| Leakage Output Current to GND $ \begin{aligned} &\text{Driver Off; 8.0 V} < V_{BAT} < 18 \text{ V; 8.0 V} < V_{BUS} < 18 \text{ V; } V_{BUS} \geq V_{BAT}; \\ &V_{BUS} \geq V_{SUP} \end{aligned} $ | IBUS_PAS_REC             | -    | -   | 20  | μА               |

| Control Unit Disconnected from Ground <sup>(9)</sup> GND <sub>DEVICE</sub> = V <sub>SUP</sub> ; V <sub>BAT</sub> = 12 V; 0 < V <sub>BUS</sub> < 18 V                                                | I <sub>BUS_NO_GND</sub>  | -1.0 | _   | 1.0 | mA               |

| V <sub>BAT</sub> Disconnected; V <sub>SUP_DEVICE</sub> = GND; 0 V < V <sub>BUS</sub> < 18 V <sup>(10)</sup>                                                                                         | I <sub>BUSNO_BAT</sub>   | -    | -   | 10  | μΑ               |

| Receiver Dominant State <sup>(11)</sup>                                                                                                                                                             | V <sub>BUSDOM</sub>      | -    | -   | 0.4 | V <sub>SUP</sub> |

| Receiver Recessive State <sup>(12)</sup>                                                                                                                                                            | V <sub>BUSREC</sub>      | 0.6  | _   | _   | V <sub>SUP</sub> |

- 7. Parameters guaranteed for 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V.

- 8. Voltage range at the battery level, including the reverse battery diode.

- 9. Loss of local ground must not affect communication in the residual network.

- 10. Node has to sustain the current that can flow under this condition. The bus must remain operational under this condition.

- 11. LIN threshold for a dominant state.

- 12. LIN threshold for a recessive state.

#### **Table 5. Static Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                           | Symbol                    | Min   | Тур | Max   | Unit             |

|------------------------------------------------------------------------------------------|---------------------------|-------|-----|-------|------------------|

| Receiver Threshold Center                                                                | V <sub>BUS_CNT</sub>      |       |     |       | V <sub>SUP</sub> |

| (V <sub>TH_DOM</sub> + V <sub>TH_REC</sub> )/2                                           |                           | 0.475 | 0.5 | 0.525 |                  |

| Receiver Threshold Hysteresis                                                            | V <sub>HYS</sub>          |       |     |       | V <sub>SUP</sub> |

| (V <sub>TH_REC</sub> - V <sub>TH_DOM</sub> )                                             |                           | _     | _   | 0.175 |                  |

| LIN dominant level with 500 $\Omega,$ 680 $\Omega$ and 1.0 $k\Omega$ load on the LIN bus | V <sub>LINDOM_LEVEL</sub> | -     | _   | 0.25  | V <sub>SUP</sub> |

| V <sub>BAT_</sub> SHIFT                                                                  | V <sub>SHIFT_BAT</sub>    | 0.0   | _   | 11.5% | $V_{BAT}$        |

| GND_SHIFT                                                                                | V <sub>SHIFT_GND</sub>    | 0.0   | _   | 11.5% | $V_{BAT}$        |

| LIN Wake-up Threshold from Sleep Mode                                                    | V <sub>BUSWU</sub>        | 1     | 4.3 | 5.3   | <b>V</b>         |

| LIN Pull-up Resistor to V <sub>SUP</sub>                                                 | R <sub>SLAVE</sub>        | 20    | 30  | 60    | kΩ               |

| LIN internal capacitor <sup>(13)</sup>                                                   | C <sub>LIN</sub>          | _     | _   | 30    | pF               |

| Over-temperature Shutdown <sup>(14)</sup>                                                | T <sub>LINSD</sub>        | 150   | 160 | 200   | °C               |

| Over-temperature Shutdown Hysteresis                                                     | T <sub>LINSD_HYS</sub>    | -     | 20  | _     | °C               |

#### INH1, INH2 OUTPUT PINS

| Driver ON Resistance (Normal Mode)        | INH <sub>ON</sub>      |      |     |     | Ω  |

|-------------------------------------------|------------------------|------|-----|-----|----|

| I <sub>INH</sub> = 50 mA                  |                        | _    | _   | 50  |    |

| Current load capability                   | I <sub>INH_load</sub>  |      |     |     | mA |

| From 7.0 V < V <sub>SUP</sub> < 18 V      |                        | _    | -   | 30  |    |

| Leakage Current (Sleep Mode)              | I <sub>LEAK</sub>      |      |     |     | μΑ |

| 0 < V <sub>INH</sub> < V <sub>SUP</sub>   |                        | -5.0 | -   | 5.0 |    |

| Over-temperature Shutdown <sup>(15)</sup> | T <sub>INHSD</sub>     | 150  | 160 | 200 | °C |

| Over-temperature Shutdown Hysteresis      | T <sub>INHSD_HYS</sub> | _    | 20  | -   | °C |

- 13. This parameter is guaranteed by process monitoring but not production tested.

- 14. When an over-temperature shutdown occurs, the LIN transmitter and receiver are in recessive state and INH switched off. This parameter is tested with a test mode on ATE and characterized at laboratory.

- 15. When an over-temperature shutdown occurs, the INH1, INH2 high side are switched off and the LIN transmitter and receiver are in recessive state. This parameter is tested with a test mode on ATE and characterized at laboratory.

#### **Table 5. Static Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                         | Symbol              | Min | Тур | Max | Unit |

|------------------------------------------------------------------------|---------------------|-----|-----|-----|------|

| WAKE1, WAKE2 INPUT PINS                                                | ·                   |     |     |     |      |

| High to Low Detection Threshold (5.5 V < V <sub>SUP</sub> < 7 V)       | V <sub>WUHL1</sub>  | 2.0 | _   | 3.9 | V    |

| Low to High Detection Threshold (5.5 V < V <sub>SUP</sub> < 7 V)       | V <sub>WULH1</sub>  | 2.4 | -   | 4.3 | V    |

| Hysteresis (5.5 V < V <sub>SUP</sub> < 7 V)                            | V <sub>WUHYS1</sub> | 0.2 | -   | 0.8 | V    |

| High to Low Detection Threshold (7 V $\leq$ V <sub>SUP</sub> $<$ 27 V) | V <sub>WUHL2</sub>  | 2.4 | -   | 3.9 | V    |

| Low to High Detection Threshold (7 V $\leq$ V <sub>SUP</sub> $<$ 27 V) | V <sub>WULH2</sub>  | 2.9 | -   | 4.3 | V    |

| Hysteresis (7 V ≤ V <sub>SUP</sub> < 27 V)                             | V <sub>WUHYS2</sub> | 0.2 | -   | 0.8 | V    |

| Wake-up Input Current (V <sub>WAKE</sub> < 27 V)                       | I <sub>WU</sub>     | _   | -   | 5.0 | μΑ   |

#### **DYNAMIC ELECTRICAL CHARACTERISTIC**

#### **Table 6. Dynamic Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted.

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Symbol                                              | Min               | Тур                                   | Max   | Unit     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------|---------------------------------------|-------|----------|

| LIN1, LIN2 PHYSICAL LAYER<br>DRIVERS CHARACTERISTICS FOR NORMAL SLEW RATE - 20.0 KBIT/S<br>SPECIFICATION <sup>(16)(17)</sup><br>33663L AND 33663S DEVICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SEC ACCORDING TO                                    | LIN PHYSIC        | AL LAYE                               | R     |          |

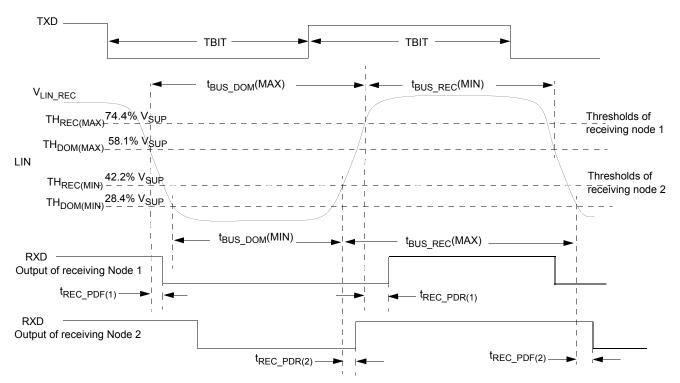

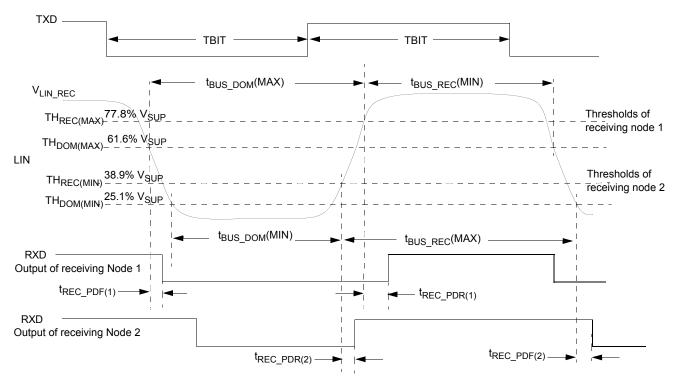

| Duty Cycle 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | D1                                                  |                   |                                       |       |          |

| $TH_{REC(MAX)} = 0.744 * V_{SUP}; TH_{DOM(MAX)} = 0.581 * V_{SUP}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     |                   |                                       |       |          |

| D1 = $t_{BUS\_REC(MIN)}/(2 \text{ x } t_{BIT})$ , $t_{BIT}$ = 50 $\mu s$ , 7.0 $V \leq V_{SUP} \leq$ 18 $V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     | 0.396             | _                                     | _     |          |

| Duty Cycle 2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | D2                                                  |                   |                                       |       |          |

| $TH_{REC(MIN)} = 0.422 * V_{SUP}; TH_{DOM(MIN)} = 0.284 * V_{SUP}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     |                   |                                       |       |          |

| D2 = $t_{BUS\_REC(MAX)}/(2 \times t_{BIT})$ , $t_{BIT}$ = 50 $\mu s$ , 7.6 $V \le V_{SUP} \le$ 18 $V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     | _                 | _                                     | 0.581 |          |

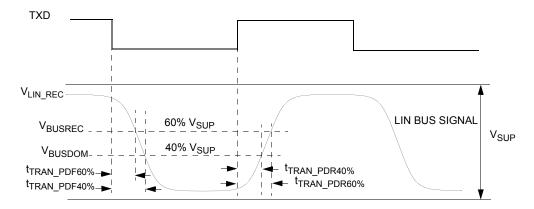

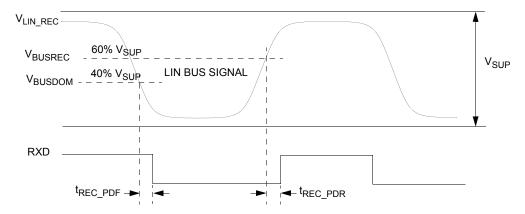

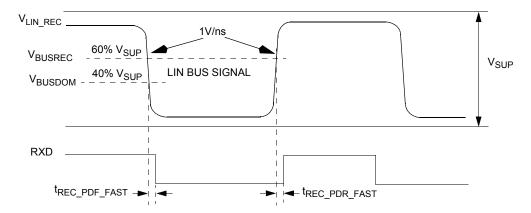

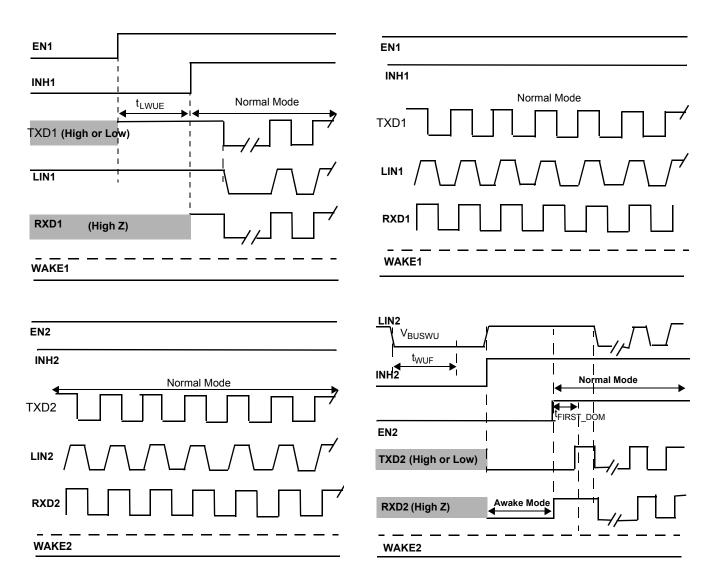

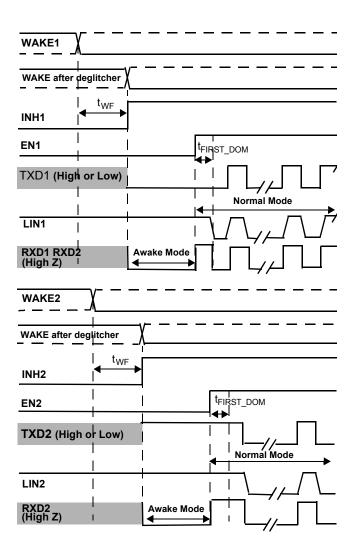

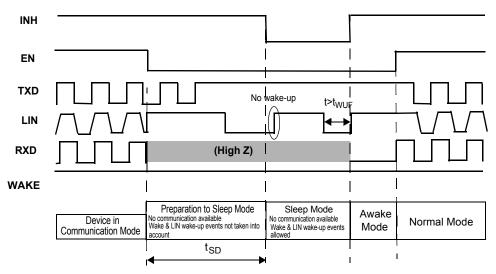

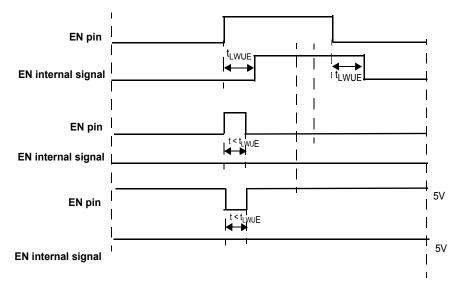

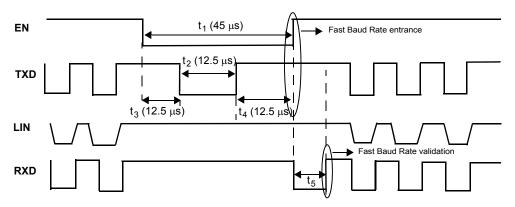

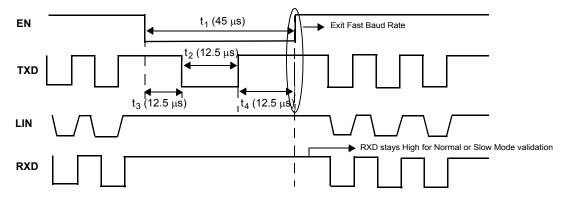

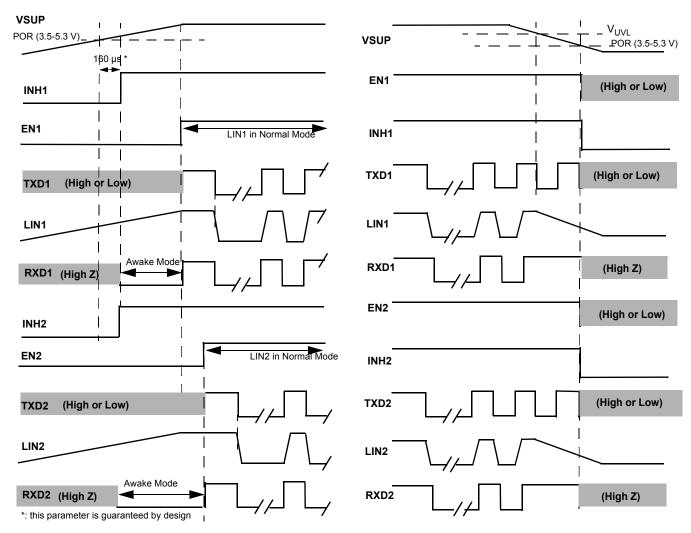

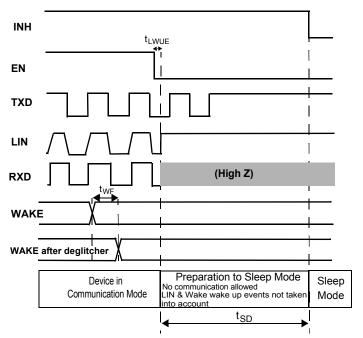

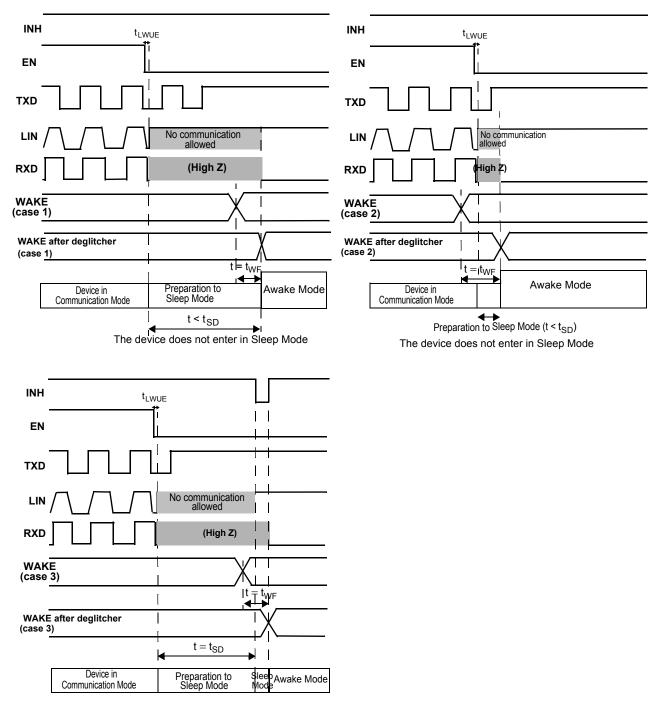

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |                   |                                       |       |          |