# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

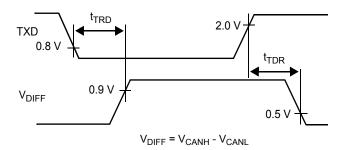

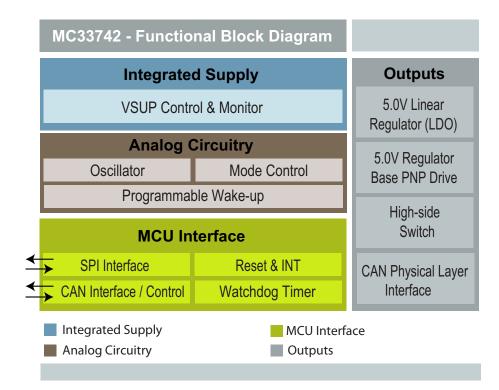

# System Basis Chip with Enhanced High Speed CAN Transceiver

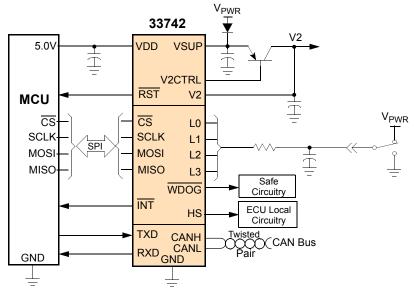

The 33742 and the 33742S SMARTMOS devices are SPI-controlled System Basis Chips (SBCs), combining many frequently used functions, along with a CAN 2.0-compliant transceiver, used in many automotive electronic control units (ECUs). The 33742 SBC has a fully protected fixed 5.0 V low dropout internal regulator, with current limiting, overtemperature prewarning, and reset. A second 5.0 V regulator can be implemented using external pass PNP bipolar junction pass transistor, driven by the SBC's external V2 sense input and V2 output drive pins.

The SBC has four main operating modes: Normal, Standby, Stop, and Sleep mode. Additionally, there is an internally switched high side power supply output, four wake-up inputs pins, a programmable window watchdog, interrupt, reset, and a SPI module for communication and control. The high speed CAN A and B transceiver is available for intermodule communication.

#### Features

- 1.0 Mbps CAN transceiver bus interface with bus diagnostic capability

- SPI control at frequencies up to 4.0 MHz

- 5.0 V low dropout voltage regulator with current limiting, overtemperature prewarning, and output monitoring and reset

- A second 5.0 V regulator capability using an external series pass transistor

- Normal, Standby, Stop, and Sleep modes of operation with low Sleep and Stop mode current

- · A high side switch output driver for controlling external circuitry

EP SUFFIX (PB-FREE) 98ASA00757D 48-PIN QFN

| ORDERING INFORMATION                               |                  |          |  |  |  |

|----------------------------------------------------|------------------|----------|--|--|--|

| Device Temperature Range (T <sub>A</sub> ) Package |                  |          |  |  |  |

| MC33742PEG/R2                                      |                  | 28 SOICW |  |  |  |

| MC33742SPEG/R2                                     | -40 °C to 125 °C |          |  |  |  |

| MC33742PEP/R2                                      |                  | 48 QFN   |  |  |  |

Figure 1. 33742 Simplified Application Diagram

# **DEVICE VARIATIONS**

| Part No. | Reset Duration   | Device Differences                                                                                                                                                                                                                   | See Page       |

|----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 33742    | 15 ms (typical)  | The duration the $\overline{\text{RST}}$ pin is asserted low when the Reset mode is entered after the SBC is powered up, a V <sub>DD</sub> under-voltage condition is detected, and the watchdog register is not properly triggered. | <u>page 18</u> |

| 33742S   | 3.5 ms (typical) | The duration the $\overline{\text{RST}}$ pin is asserted low when the Reset mode is entered after the SBC is powered up, a V <sub>DD</sub> under-voltage condition is detected, and the watchdog register is not properly triggered. | <u>page 18</u> |

# Table 1. Device Differences During a Reset Condition

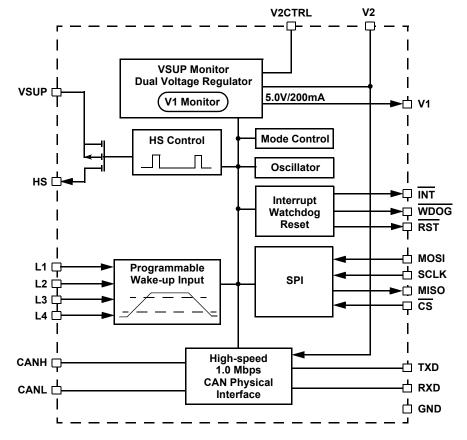

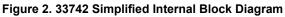

# INTERNAL BLOCK DIAGRAM

3

# **PIN CONNECTIONS**

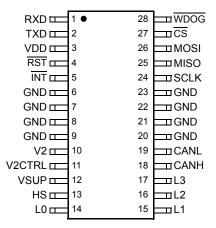

Figure 3. 33742 28-Pin Connections

# Table 2. 33742 28-Pin Definitions

A functional description of each pin can be found in the Functional Pin description section beginning on page 22.

| Pin          | Pin Name | Formal Name                      | Definition                                                                                                                                   |

|--------------|----------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | RXD      | Receive Data                     | CAN bus receive data output pin.                                                                                                             |

| 2            | TXD      | Transmit Data                    | CAN bus transmit data input pin.                                                                                                             |

| 3            | VDD      | Voltage Digital Drain            | 5.0 V regulator output pin. Supply pin for the MCU.                                                                                          |

| 4            | RST      | Reset Output<br>(Active LOW)     | This is the device reset output pin whose main function is to reset the MCU. This pin has an internal -up current source to VDD.             |

| 5            | ĪNT      | Interrupt Output<br>(Active LOW) | This output is asserted LOW when an enabled interrupt condition occurs. The output is a push-pull structure.                                 |

| 6–9<br>20–23 | GND      | Ground                           | These device ground pins are internally connected to the package lead frame to provide a 33742-to-PCB thermal path.                          |

| 10           | V2       | Voltage Source 2                 | Sense input for the V2 regulator using an external series pass transistor. V2 is also the internal supply for the CAN transceiver.           |

| 11           | V2CTRL   | Voltage Source 2 Control         | Output drive source for the V2 regulator connected to the external series pass transistor.                                                   |

| 12           | VSUP     | Voltage Supply                   | Supply input pin for the 33742.                                                                                                              |

| 13           | HS       | High Side Output                 | Output of the internal high side switch. The output current is internally limited to 150 mA.                                                 |

| 14–17        | L0-L3    | Level 0-3 Inputs                 | Inputs from external switches or from logic circuitry.                                                                                       |

| 18           | CANH     | CAN High Output                  | CAN high output pin.                                                                                                                         |

| 19           | CANL     | CAN Low Output                   | CAN low output pin.                                                                                                                          |

| 24           | SCLK     | Serial Data Clock                | Clock input pin for the Serial Peripheral Interface (SPI).                                                                                   |

| 25           | MISO     | Master In Slave Out              | SPI data sent to the MCU by the 33742. When CS is HIGH, the pin is in the high-impedance state.                                              |

| 26           | MOSI     | Master Out Slave In              | SPI data received by the 33742.                                                                                                              |

| 27           | CS       | Chip Select<br>(Active LOW)      | The CS input pin is used with the SPI bus to select the 33742. When the CS is asserted LOW, the 33742 is the selected device of the SPI bus. |

| 28           | WDOG     | Watchdog Output<br>(Active LOW)  | The WDOG output pin is asserted LOW if the software watchdog is not correctly triggered.                                                     |

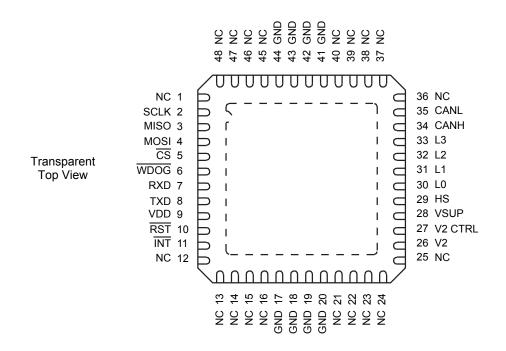

# Table 3. 33742 48-Pin Definitions

A functional description of each pin can be found in the Functional Pin description section beginning on page 22.

| Pin                                    | Pin Name | Formal Name                      | Definition                                                                                                                                   |

|----------------------------------------|----------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 12-16,<br>21-25,<br>36-40,<br>45-48 | NC       | No Connect                       | No connection.                                                                                                                               |

| 2                                      | SCLK     | Serial Data Clock                | Clock input pin for the Serial Peripheral Interface (SPI).                                                                                   |

| 3                                      | MISO     | Master In Slave Out              | SPI data sent to the MCU by the 33742. When CS is HIGH, the pin is in the high-impedance state.                                              |

| 4                                      | MOSI     | Master Out Slave In              | SPI data received by the 33742.                                                                                                              |

| 5                                      | CS       | Chip Select<br>(Active LOW)      | The CS input pin is used with the SPI bus to select the 33742. When the CS is asserted LOW, the 33742 is the selected device of the SPI bus. |

| 6                                      | WDOG     | Watchdog Output<br>(Active LOW)  | The WDOG output pin is asserted LOW if the software watchdog is not correctly triggered.                                                     |

| 7                                      | RXD      | Receive Data                     | CAN bus receive data output pin.                                                                                                             |

| 8                                      | TXD      | Transmit Data                    | CAN bus transmit data input pin.                                                                                                             |

| 9                                      | VDD      | Voltage Digital Drain            | 5.0 V regulator output pin. Supply pin for the MCU.                                                                                          |

| 10                                     | RST      | Reset Output<br>(Active LOW)     | This is the device reset output pin whose main function is to reset the MCU. This pin has an internal pull-up current source to VDD.         |

| 11                                     | INT      | Interrupt Output<br>(Active LOW) | This output is asserted LOW when an enabled interrupt condition occurs. The output is a push-pull structure.                                 |

| 17-20<br>41-44                         | GND      | Ground                           | These device ground pins are internally connected to the package lead frame to provide a 33742-to-PCB thermal path.                          |

# Table 3. 33742 48-Pin Definitions (continued)

A functional description of each pin can be found in the Functional Pin description section beginning on page 22.

| Pin   | Pin Name | Formal Name              | Definition                                                                                                                         |

|-------|----------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 26    | V2       | Voltage Source 2         | Sense input for the V2 regulator using an external series pass transistor. V2 is also the internal supply for the CAN transceiver. |

| 27    | V2CTRL   | Voltage Source 2 Control | Output drive source for the V2 regulator connected to the external series pass transistor.                                         |

| 28    | VSUP     | Voltage Supply           | Supply input pin for the 33742.                                                                                                    |

| 29    | HS       | High Side Output         | Output of the internal high side switch. The output current is internally limited to 150 mA.                                       |

| 30-33 | L0-L3    | Level 0-3 Inputs         | Inputs from external switches or from logic circuitry.                                                                             |

| 34    | CANH     | CAN High Output          | CAN high output pin.                                                                                                               |

| 35    | CANL     | CAN Low Output           | CAN low output pin.                                                                                                                |

# **ELECTRICAL CHARACTERISTICS**

# **MAXIMUM RATINGS**

# Table 4. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                                                                                     | Symbol              | Value                          | Unit |

|----------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------|------|

| ELECTRICAL RATINGS                                                                                                         |                     |                                |      |

| Power Supply Voltage at VSUP                                                                                               | V <sub>SUP</sub>    |                                | V    |

| Continuous (Steady-state)                                                                                                  |                     | -0.3 to 27                     |      |

| Transient Voltage (Load Dump)                                                                                              |                     | -0.3 to 40                     |      |

| Logic Signals (RXD, TXD, MOSI, MISO, $\overline{CS}$ , SCLK, $\overline{RST}$ , $\overline{WDOG}$ , and $\overline{INT}$ ) | V <sub>LOG</sub>    | -0.3 to V <sub>DD</sub> +0.3   | V    |

| Output Voltage at VDD                                                                                                      | V <sub>DD</sub>     | 0.0 to 5.3                     | V    |

| Output Current at VDD                                                                                                      | I <sub>DD</sub>     | Internally Limited             | А    |

| HS                                                                                                                         |                     |                                |      |

| Voltage                                                                                                                    | V <sub>HS</sub>     | -0.3 to V <sub>SUP</sub> + 0.3 | V    |

| Output Current                                                                                                             | I <sub>HS</sub>     | Internally Limited             | А    |

| ESD Capability, Human Body Model <sup>(1)</sup>                                                                            | V <sub>ESD1</sub>   |                                | V    |

| MC33742 in 28-pin SOIC                                                                                                     |                     |                                |      |

| HS, L0, L1, L2, L3, CANH, CANL pins                                                                                        |                     | ±4000                          |      |

| All Other pins                                                                                                             |                     | ±2000                          |      |

| MC33742 in 48-pin QFN                                                                                                      |                     |                                |      |

| All pins                                                                                                                   |                     | ±2000                          |      |

| ESD Capability, Machine Model <sup>(1)</sup>                                                                               | V <sub>ESD2</sub>   | ±200                           | V    |

| Input Voltage/Current at L0, L1, L2, L3                                                                                    |                     |                                |      |

| DC Input Voltage                                                                                                           | V <sub>DCIN</sub>   | -0.3 to 40                     | V    |

| DC Input Current                                                                                                           | IDCIN               | ±2.0                           | mA   |

| Transient Input Voltage attached to external circuitry <sup>(2)</sup>                                                      | V <sub>TRINEC</sub> | ±100                           | V    |

| CANL and CANH                                                                                                              |                     |                                |      |

| Continuous Voltage                                                                                                         | V <sub>CANH/L</sub> | -27 to 40                      | V    |

| Continuous Current                                                                                                         | I <sub>CANH/L</sub> | 200                            | mA   |

| CANH and CANL Transient Voltage (Load Dump) <sup>(3)</sup>                                                                 | V <sub>LDH/L</sub>  | 40                             | V    |

| CANH and CANL Transient Voltage <sup>(3)</sup>                                                                             | V <sub>TRH/L</sub>  | ±40                            | V    |

Notes

1. Testing done in accordance with the Human Body Model ( $C_{ZAP}$ =100 pF,  $R_{ZAP}$ =1500  $\Omega$ ), Machine Model ( $C_{ZAP}$ =200 pF,  $R_{ZAP}$ =0  $\Omega$ ).

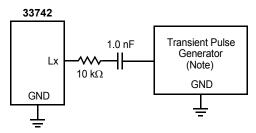

2. Testing done in accordance with ISO 7637-1. See Figure 5.

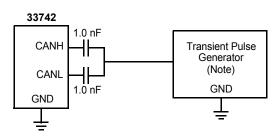

3. Load dump testing done in accordance with ISO 7637-1, Transient test done in accordance with ISO 7637-1. See Figure 6.

# Table 4. Maximum Ratings (continued)

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                                        | Symbol                      | Value      | Unit |

|-------------------------------------------------------------------------------|-----------------------------|------------|------|

| THERMAL RATINGS                                                               |                             |            |      |

| Operating Temperature                                                         |                             |            | °C   |

| Ambient                                                                       | Τ <sub>Α</sub>              | -40 to 125 |      |

| Junction                                                                      | TJ                          | -40 to 150 |      |

| Storage Temperature                                                           | T <sub>STG</sub>            | -55 to 165 | °C   |

| Thermal Resistance                                                            | $R_{	heta JG}$              | 20         | °C/W |

| Thermal Resistance Junction Case (QFN)                                        | $R_{TJC}$ - $R_{\theta JC}$ | TBD        | °C/W |

| Power Dissipation <sup>(4)</sup>                                              | PD                          | 1.0        | W    |

| Peak Package Reflow Temperature During Reflow <sup>(6)</sup> , <sup>(7)</sup> | T <sub>PPRT</sub>           | Note 7     | °C   |

Notes

4. Maximum power dissipation is at 85 °C ambient temperature in free alr and with no heatsink, according to JEDEC JESD51-2 and JESD51-3 specifications.

5. The package is not designed for immersion soldering. The maximum soldering time is 10 seconds at 240 °C on any pin. Exceeding the maximum temperature and time limits may cause permanent damage to the device.

6. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

7. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

Note Waveform per ISO 7637-1. Test Pulses 1, 2, 3a, and 3b. Figure 5. Transient Test Setup for L0:L3 Inputs

Note Waveform per ISO 7637-1. Test Pulses 1, 2, 3a, and 3b. Figure 6. Transient Test Setup for CANH/CANL

# STATIC ELECTRICAL CHARACTERISTICS

# **Table 5. Static Electrical Characteristics**

Characteristics noted under conditions 4.75 V  $\leq$  V2  $\leq$  5.25 V, 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                       | Symbol                    | Min | Тур      | Max | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|----------|-----|------|

| INPUT PIN (VSUP)                                                                                                                                                     |                           |     |          |     |      |

| Supply Voltage                                                                                                                                                       | V <sub>SUP</sub>          |     |          |     | V    |

| Nominal DC Voltage                                                                                                                                                   |                           | 5.5 | _        | 18  |      |

| Extended DC Voltage: Full Functionality <sup>(8)</sup>                                                                                                               |                           | 18  | _        | 27  |      |

| Extended DC Voltage: Reduced Functionality <sup>(9)</sup>                                                                                                            |                           | 4.5 | —        | 5.5 |      |

| Load Dump                                                                                                                                                            |                           | —   | —        | 40  |      |

| Jump Start                                                                                                                                                           |                           | —   | -        | 27  |      |

| Supply Current in Standby Mode <sup>(10)</sup><br>(I <sub>OUT</sub> at VDD = 40 mA, CAN Recessive or Sleep Mode)                                                     | I <sub>SUP(STDBY)</sub>   |     |          |     | mA   |

| $T_A \ge 25 \ ^\circ C$                                                                                                                                              |                           | _   | 42       | 45  |      |

| Supply Current in Normal Mode <sup>(10)</sup><br>(I <sub>OUT</sub> at VDD = 40 mA, CAN Recessive or Sleep mode)                                                      | I <sub>SUP(NORM)</sub>    |     |          |     | mA   |

| $T_A \ge 25 \ ^\circ C$                                                                                                                                              |                           | —   | 42       | 45  |      |

| Supply Current in Sleep Mode <sup>(10)</sup><br>(VDD and V2 OFF, CAN in Sleep Mode with CAN Wake-up Disabled <sup>(11)</sup> )                                       | I <sub>SUP(SLP-WD)</sub>  |     |          |     | μA   |

| V <sub>SUP</sub> < 13.5 V, Oscillator Running <sup>(12)</sup>                                                                                                        |                           | _   | 85       | 105 |      |

| V <sub>SUP</sub> < 13.5 V, Oscillator Not Running <sup>(13)</sup>                                                                                                    |                           | —   | 53       | 80  |      |

| V <sub>SUP</sub> = 18 V, Oscillator Running <sup>(12)</sup>                                                                                                          |                           | _   | 110      | 140 |      |

| Supply Current in Sleep Mode <sup>(10)</sup><br>(V1 and V2 OFF, $V_{SUP}$ < 13.5 V, Oscillator Not Running <sup>(13)</sup> , CAN in Sleep Mode with Wake-up Enabled) | I <sub>SUP(SLP-WE)</sub>  |     |          |     | μΑ   |

| T <sub>A</sub> = −40 °C                                                                                                                                              |                           |     |          |     |      |

| T <sub>A</sub> = 25 °C                                                                                                                                               |                           | —   | 80       | _   |      |

| T <sub>A</sub> = 125 °C                                                                                                                                              |                           | _   | 65<br>55 |     |      |

| Supply Current in Stop Mode <sup>(10)</sup><br>( $I_{OUT}$ at VDD < 2.0 mA, VDD ON, CAN in Sleep Mode with Wake-up Disabled <sup>(11)</sup> )                        | I <sub>SUP(STOP-WD)</sub> |     |          |     | μΑ   |

| VSUP < 13.5 V, Oscillator Running <sup>(12)</sup>                                                                                                                    |                           |     |          | 160 |      |

| VSUP < 13.5 V, Oscillator Not Running <sup>(13)</sup>                                                                                                                |                           | _   | 80       | 160 |      |

| VSUP = 18 V, Oscillator Running <sup>(12)</sup>                                                                                                                      |                           | _   | 100      | 210 |      |

Notes

8. All functions and modes available and operating: Watchdog, HS turn ON/turn OFF, CAN transceiver operating, L0:L3 inputs operating, normal SPI operation. The 33742 may experience an over-temperature fault.

9. At VDD > 4.0 V, RST HIGH if reset 2 selected via SPI. The logic HIGH level will be degraded but the 33742 is functional.

10. Current measured at the VSUP pin.

- 11. If CAN Module is Sleep-enabled for wake-up, an additional current (I<sub>CAN-SLEEP</sub>) must be added to specified value.

- Oscillator running means one of the following function is active: Forced Wake-up *or* Cyclic Sense *or* Software Watchdog in Stop mode.

Oscillator not running means none of the following functions are active: Forced Wake-up *and* Cyclic Sense *and* Software Watchdog in

- Oscillator not running means none of the following functions are active: Forced Wake-up and Cyclic Sense and Software Watchdog in Stop mode.

Characteristics noted under conditions 4.75 V  $\leq$  V2  $\leq$  5.25 V, 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                                              | Symbol                    | Min        | Тур | Max      | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------|-----|----------|------|

| INPUT PIN (VSUP) (CONTINUED)                                                                                                                                                                | 1 1                       |            |     | 1        |      |

| Supply Current in Stop Mode <sup>(14)</sup><br>(I <sub>OUT</sub> at VDD < 2.0 mA, VDD ON, VSUP < 13.5 V, Oscillator Not Running,<br>CAN in Sleep Mode with Wake-up Enabled) <sup>(15)</sup> | I <sub>SUP(STOP-WE)</sub> |            |     |          | μA   |

| T <sub>A</sub> = −40 °C                                                                                                                                                                     |                           | _          | 100 | _        |      |

| T <sub>A</sub> = 25 °C                                                                                                                                                                      |                           | _          | 92  | _        |      |

| T <sub>A</sub> = 125 °C                                                                                                                                                                     |                           | _          | 80  | _        |      |

| BATFAIL Flag Internal Threshold                                                                                                                                                             | V <sub>BF</sub>           | 1.5        | 3.0 | 4.0      | V    |

| BATFAIL Flag Hysteresis <sup>(16)</sup>                                                                                                                                                     | V <sub>BF(HYS)</sub>      | _          | 1.0 | —        | V    |

| Battery Fall Early Warning Threshold<br>In Normal and Standby Modes                                                                                                                         | V <sub>BF(EW)</sub>       | 5.3        | 5.8 | 6.3      | V    |

| Battery Fall Early Warning Hysteresis<br>In Normal and Standby Modes <sup>(16)</sup>                                                                                                        | V <sub>BF(EW-HYST)</sub>  | 0.1        | 0.2 | 0.3      | V    |

| OUTPUT PIN (VDD) <sup>(17)</sup>                                                                                                                                                            |                           |            | •   | l        |      |

| VDD Output Voltage (2.0 mA < I <sub>V1</sub> < 200 mA)<br>5.5 V < VSUP < 27 V<br>4.5 V < VSUP < 5.5 V                                                                                       | V <sub>DDOUT</sub>        | 4.9<br>4.0 | 5.0 | 5.1<br>— | V    |

| Dropout Voltage<br>I <sub>DD</sub> = 200 mA                                                                                                                                                 | V <sub>DDDRP1</sub>       | _          | 0.2 | 0.5      | V    |

| Dropout Voltage, Limited Output Current and Low V <sub>SUP</sub> $I_{DD}$ = 50 mA, 4.5 V < VSUP                                                                                             | V <sub>DDDRP2</sub>       |            | 0.1 | 0.25     | V    |

| Output Current<br>Internally Limited                                                                                                                                                        | I <sub>DD</sub>           | 200        | 285 | 350      | mA   |

| Thermal Shutdown (Junction)<br>Normal or Standby Mode                                                                                                                                       | T <sub>SD</sub>           | 160        | _   | 200      | °C   |

| Over-temperature Pre-warning (Junction)<br>VDDTEMP Bit Set                                                                                                                                  | T <sub>PW</sub>           | 125        | _   | 160      | °C   |

Notes

14. Current measured at the VSUP pin.

15. Oscillator not running means none of the following functions are active: Forced Wake-up *and* Cyclic Sense *and* Software Watchdog in Stop mode.

16. Guaranteed by design; it is not production tested.

I<sub>DD</sub> is the total regulator output current. V1 specification with external capacitor. Stability requirement: Capacitance > 47 μF, ESR < 1.3 Ω (tantalum capacitor). In Reset, Normal Request, Normal and Standby modes. Measures with capacitance = 47 μF tantalum.</li>

Characteristics noted under conditions 4.75 V  $\leq$  V2  $\leq$  5.25 V, 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                      | Symbol                            | Min  | Тур | Max                | Unit |

|-------------------------------------------------------------------------------------|-----------------------------------|------|-----|--------------------|------|

| OUTPUT PIN (VDD) (CONTINUED) <sup>(18)</sup>                                        |                                   |      |     |                    |      |

| Temperature Threshold Difference                                                    | T <sub>SD</sub> - T <sub>PW</sub> | 20   | _   | 40                 | °C   |

| Reset Threshold                                                                     | V <sub>RSTTH</sub>                |      |     |                    | V    |

| Threshold 1, Default Value after Reset, RSTTH Bit Set to Logic [0]                  |                                   | 4.5  | 4.6 | 4.7                |      |

| Threshold 2, RSTTH Bit Set to Logic [1]                                             |                                   | 4.0  | 4.2 | 4.3                |      |

| VDD for Reset Active                                                                | V <sub>DDR</sub>                  | 1.0  | —   | V <sub>RSTTH</sub> | V    |

| Line Regulation (I <sub>DD</sub> = 10 mA, Capacitance = 47 $\mu$ F Tantalum at VDD) | V <sub>DDR</sub>                  |      |     |                    | mV   |

| 9.0 V < V <sub>SUP</sub> < 18 V                                                     |                                   | —    | 5.0 | 25                 |      |

| 5.5 V < V <sub>SUP</sub> < 27 V                                                     |                                   | —    | 10  | 25                 |      |

| Load Regulation (Capacitance = 47 µF Tantalum at V1)                                | V <sub>LD</sub>                   |      |     |                    | mV   |

| 1.0 mA < I <sub>DD</sub> < 200 mA                                                   |                                   | —    | 25  | 75                 |      |

| Thermal Stability                                                                   | V <sub>THERM-S</sub>              |      |     |                    | mV   |

| V <sub>SUP</sub> = 13.5 V, I <sub>DD</sub> = 100 mA <sup>(19)</sup>                 |                                   | —    | 30  | 50                 |      |

| OUTPUT PIN IN STOP MODE (VDD) <sup>(18)</sup>                                       | 1                                 | I    | 1   | 1                  |      |

| VDD Output Voltage                                                                  | V <sub>DDSTOP</sub>               |      |     |                    | V    |

| $I_{DD} \le 2.0 \text{ mA}$                                                         |                                   | 4.75 | 5.0 | 5.25               |      |

| $I_{DD} \le 10 \text{ mA}$                                                          |                                   | 4.75 | 5.0 | 5.25               |      |

| I <sub>DD</sub> Output Current to Wake-up                                           | I <sub>DDS-WU</sub>               | 10   | 17  | 25                 | mA   |

| Reset Threshold <sup>(18)</sup>                                                     | V <sub>RST-STOP</sub>             |      |     |                    | V    |

| Threshold 1, Default Value after Reset, RSTTH Bit Set to Logic [0]                  |                                   | 4.5  | 4.6 | 4.7                |      |

| Threshold 2, RSTTH Bit Set to Logic [1]                                             |                                   | 4.1  | 4.2 | 4.3                |      |

| Line Regulation (Capacitance = 47 $\mu$ F Tantalum at VDD)                          | V <sub>LR-STOP</sub>              |      |     |                    | mV   |

| 5.5 V < V <sub>SUP</sub> < 27 V, I <sub>DD</sub> = 2.0 mA                           |                                   | —    | 5.0 | 25                 |      |

| Load Regulation (Capacitance = 47 µF Tantalum at V1)                                | V <sub>LD-STOP</sub>              |      |     |                    | mV   |

| 1.0 mA < I <sub>DD</sub> < 10 mA                                                    |                                   | —    | 15  | 75                 |      |

Notes

18.  $I_{DD}$  is the total regulator output current. VDD specification with external capacitor. Stability requirement: capacitance > 47  $\mu$ F, ESR < 1.3  $\Omega$  (tantalum capacitor). In Reset, Normal Request, Normal and Standby modes, measures with capacitance = 47  $\mu$ F tantalum.Selectable by RSTTH bit in SPI Register Reset Control Register (RCR).

19. Guaranteed by characterization and design; it is not production tested.

Characteristics noted under conditions 4.75 V  $\leq$  V2  $\leq$  5.25 V, 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                              | Symbol              | Min                  | Тур  | Мах                   | Unit            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|------|-----------------------|-----------------|

| TRACKING VOLTAGE REGULATOR (V2) <sup>(20)</sup>                                                                                                             |                     |                      |      | 1                     | 1               |

| V2 Output Voltage (Capacitance = 10 $\mu F$ Tantalum at V2) 2.0 mA $\leq$ $I_{V2}$ $\leq$ 200 mA, 5.5 V $<$ $V_{SUP}$ $<$ 27 V                              | V <sub>2</sub>      | 0.99                 | 1.0  | 1.01                  | V <sub>DD</sub> |

| I <sub>V2</sub> Output Current (for Information Only)<br>Depending on External Ballast Transistor                                                           | I <sub>V2</sub>     | 200                  |      | _                     | mA              |

| V2 Control Drive Current Capability <sup>(21)</sup><br>Worst Case at $T_J = 125$ °C                                                                         | I <sub>V2CTRL</sub> | 0.0                  | _    | 10                    | mA              |

| V2LOW Flag Threshold                                                                                                                                        | V <sub>2LTH</sub>   | 3.75                 | 4.0  | 4.25                  | V               |

| LOGIC OUTPUT PIN (MISO) <sup>(22)</sup>                                                                                                                     |                     |                      |      | 1                     |                 |

| Low-level Output Voltage<br>I <sub>OUT</sub> = 1.5 mA                                                                                                       | V <sub>OL</sub>     | 0.0                  | _    | 1.0                   | V               |

| High-level Output Voltage<br>I <sub>OUT</sub> = -250 μA                                                                                                     | V <sub>OH</sub>     | V <sub>DD</sub> -0.9 | _    | V <sub>DD</sub>       | V               |

| Tri-stated MISO Leakage Current<br>0 V < V <sub>MISO</sub> < V <sub>DD</sub>                                                                                | I <sub>HZ</sub>     | -2.0                 |      | 2.0                   | μA              |

| LOGIC INPUT PINS (MOSI, SCLK, CS)                                                                                                                           |                     |                      |      |                       |                 |

| High-level Input Voltage                                                                                                                                    | V <sub>IH</sub>     | 0.7 V <sub>DD</sub>  | _    | V <sub>DD</sub> + 0.3 | V               |

| Low-level Input Voltage                                                                                                                                     | V <sub>IL</sub>     | -0.3                 | _    | 0.3 V <sub>DD</sub>   | V               |

| High-level Input Current on $\overline{CS}$<br>V <sub>IN</sub> = 4.0 V                                                                                      | I <sub>IH</sub>     | -100                 | _    | -20                   | μA              |

| Low-level Input Current on $\overline{CS}$<br>V <sub>IN</sub> = 1.0 V                                                                                       | IIL                 | -100                 | _    | -20                   | μA              |

| MOSI and SCLK Input Current<br>0 V < V <sub>IN</sub> < V <sub>DD</sub>                                                                                      | I <sub>IN</sub>     | -10                  | _    | 10                    | μA              |

|                                                                                                                                                             |                     |                      |      |                       |                 |

| High-level Output Current<br>0 V < V <sub>OUT</sub> < 0.7 V <sub>DD</sub>                                                                                   | I <sub>ОН</sub>     | -300                 | -250 | -150                  | μA              |

| Low-level Output Voltage<br>$I_O = 1.5 \text{ mA}, 5.5 \text{ V} < V_{SUP} < 27 \text{ V}$<br>$I_O = 0 \text{ mA}, 1.0 \text{ V} < V_{SUP} < 5.5 \text{ V}$ | V <sub>OL</sub>     | 0.0<br>0.0           | _    | 0.9<br>0.9            | V               |

| RST Pull-down Current<br>V > 0.9 V                                                                                                                          | I <sub>PDW</sub>    | 2.3                  | _    | 5.0                   | mA              |

Notes

20. V2 specification with external capacitor. Stability requirement: capacitance > 42 μF and ESR < 1.3 Ω (tantalum capacitor), external resistor between base and emitter required. Measurement conditions: ballast transistor MJD32C, capacitance > 10 μF tantalum, 2.2 kΩ resistor between base and emitter of ballast transistor.

21. The guaranteed V2CTRL current capability is 10 mA. No active current limiting is used so the actual available current may be higher.

22. Push-pull structure with tri-state condition ( $\overline{CS}$  HIGH).

23. Output pin only. Supply from VDD. Structure switch to ground with pull-up current source.

Characteristics noted under conditions 4.75 V  $\leq$  V2  $\leq$  5.25 V, 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                       | Symbol              | Min                  | Тур | Мах             | Unit |

|--------------------------------------------------------------------------------------|---------------------|----------------------|-----|-----------------|------|

| OUTPUT PIN (WDOG) <sup>(24)</sup>                                                    | I                   | _II                  |     | ı               |      |

| Low-level Output Voltage                                                             | V <sub>OL</sub>     |                      |     |                 | V    |

| I <sub>O</sub> = 1.5 mA, 1.0 V < V <sub>SUP</sub> < 27 V                             |                     | 0.0                  | _   | 0.9             |      |

| High-level Output Voltage                                                            | V <sub>OH</sub>     |                      |     |                 | V    |

| I <sub>O</sub> = -250 μA                                                             |                     | V <sub>DD</sub> -0.9 | —   | V <sub>DD</sub> |      |

| OUTPUT PIN (INT) <sup>(24)</sup>                                                     | ·                   |                      |     |                 | •    |

| Low-level Output Voltage                                                             | V <sub>OL</sub>     |                      |     |                 | V    |

| I <sub>O</sub> = 1.5 mA                                                              |                     | 0.0                  | —   | 0.9             |      |

| High-level Output Voltage                                                            | V <sub>OH</sub>     |                      |     |                 | V    |

| I <sub>O</sub> = -250 μA                                                             |                     | V <sub>DD</sub> -0.9 | —   | $V_{DD}$        |      |

| OUTPUT PIN (HS)                                                                      | ·                   | · ·                  |     | ·               |      |

| Driver Output ON Resistance                                                          | R <sub>DS(ON)</sub> |                      |     |                 | Ω    |

| T <sub>A</sub> = 25 °C, I <sub>OUT</sub> - 150 mA, V <sub>SUP</sub> > 9.0 V          |                     | —                    | 2.0 | 2.5             |      |

| T <sub>A</sub> = 125 °C, I <sub>OUT</sub> - 150 mA, V <sub>SUP</sub> > 9.0 V         |                     | —                    | —   | 4.5             |      |

| T <sub>A</sub> = 125 °C, I <sub>OUT</sub> - 120 mA, 5.5 V < V <sub>SUP</sub> < 9.0 V |                     | —                    | 3.5 | 5.5             |      |

| Output Current Limitation                                                            | I <sub>LIM</sub>    |                      |     |                 | mA   |

| $V_{SUP}$ - $V_{HS}$ > 1.0 V                                                         |                     | 160                  | —   | 500             |      |

| HS Thermal Shutdown                                                                  | T <sub>SD</sub>     | 155                  | _   | 190             | °C   |

| HS Leakage Current                                                                   | I <sub>LEAK</sub>   | —                    | —   | 10              | μA   |

| Output Clamp Voltage                                                                 | V <sub>CL</sub>     |                      |     |                 | V    |

| I <sub>OUT</sub> = -10 mA, No Inductive Load Drive Capability                        |                     | -1.5                 | —   | -0.3            |      |

| NPUT PINS (L0, L1, L2, AND L3)                                                       | I                   | -11                  |     |                 |      |

| Low-voltage Detection Threshold                                                      | V <sub>THL</sub>    |                      |     |                 | V    |

| 5.5 V < V <sub>SUP</sub> < 6.0 V                                                     |                     | 2.0                  | 2.5 | 3.0             |      |

| 6.0 V < V <sub>SUP</sub> < 18 V                                                      |                     | 2.5                  | 3.0 | 3.6             |      |

| 18 V < V <sub>SUP</sub> < 27 V                                                       |                     | 2.7                  | 3.2 | 3.7             |      |

| High-voltage Detection Threshold                                                     | V <sub>THH</sub>    |                      |     |                 | V    |

| 5.5 V < V <sub>SUP</sub> < 6.0 V                                                     |                     | 2.7                  | 3.3 | 3.8             |      |

| 6.0 V < V <sub>SUP</sub> < 18 V                                                      |                     | 3.0                  | 4.0 | 4.6             |      |

| 18 V < V <sub>SUP</sub> < 27 V                                                       |                     | 3.5                  | 4.2 | 4.7             |      |

| Hysteresis                                                                           | V <sub>HYS</sub>    |                      |     |                 | V    |

| 5.5 V < V <sub>SUP</sub> < 27 V                                                      |                     | 0.6                  | _   | 1.3             |      |

| Input Current                                                                        | I <sub>IN</sub>     |                      |     |                 | μA   |

| -0.2 V < V <sub>IN</sub> < 40 V                                                      |                     | -10                  | _   | 10              |      |

Notes

24. Push-pull structure.

Characteristics noted under conditions 4.75 V  $\leq$  V2  $\leq$  5.25 V, 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                        | Symbol                               | Min  | Тур | Max  | Unit |

|-------------------------------------------------------------------------------------------------------|--------------------------------------|------|-----|------|------|

| CAN TRANSCEIVER CURRENT                                                                               |                                      |      |     | 1    |      |

| Supply Current of CAN Module                                                                          |                                      |      |     |      |      |

| CAN in Normal mode, Bus Recessive State                                                               | I <sub>RES</sub>                     | _    | 1.3 | 3.0  | mA   |

| CAN in Normal mode, Bus Dominant State without Bus Load                                               | I <sub>DOM</sub>                     | _    | 1.5 | 3.5  | mA   |

| CAN in Sleep State, Wake-up Enabled, V2 Regulator OFF                                                 | I <sub>CAN-SLEEP</sub>               | _    | 12  | 24   | μA   |

| CAN in Sleep State, Wake-up Disabled, V2 Regulator OFF <sup>(25)</sup>                                | I <sub>DIS</sub>                     | —    | —   | 1.0  | μA   |

| PINS (CANH AND CANL)                                                                                  |                                      |      | •   |      |      |

| Bus Pin Common Mode Voltage                                                                           | V <sub>CM</sub>                      | -27  | —   | 40   | V    |

| Differential Input Voltage (Common Mode Between -3.0 V and 7.0 V)                                     | V <sub>CANH</sub> -V <sub>CANL</sub> |      |     |      | mV   |

| Recessive State at RXD                                                                                |                                      | _    | _   | 500  |      |

| Dominant State at RXD                                                                                 |                                      | 900  | _   | _    |      |

| Differential Input Hysteresis (RXD)                                                                   | V <sub>HYS</sub>                     | 100  | _   | _    | mV   |

| Input Resistance                                                                                      | R <sub>IN</sub>                      |      |     |      | kΩ   |

| 28-pin SOIC                                                                                           |                                      | 5.0  | _   | 100  |      |

| 48-pin QFN                                                                                            |                                      | 5.0  | —   | 50   |      |

| Differential Input Resistance                                                                         | R <sub>IND</sub>                     | 10   | _   | 100  | kΩ   |

| CANH Output Voltage                                                                                   | V <sub>CANH</sub>                    |      |     |      | V    |

| TXD Dominant State                                                                                    |                                      | 2.75 | _   | 4.5  |      |

| TXD Recessive State                                                                                   |                                      | —    | —   | 3.0  |      |

| CANL Output Voltage                                                                                   | V <sub>CANL</sub>                    |      |     |      | V    |

| TXD Dominant State                                                                                    |                                      | 0.5  | —   | 2.25 |      |

| TXD Recessive State                                                                                   |                                      | 2.0  | —   | —    |      |

| Differential Output Voltage                                                                           | Vo <sub>H</sub> -Vo <sub>L</sub>     |      |     |      |      |

| TXD Dominant State                                                                                    |                                      | 1.5  | —   | 3.0  | V    |

| TXD Recessive State                                                                                   |                                      | —    | —   | 100  | mV   |

| Output Current Capability (Dominant State)                                                            |                                      |      |     |      | mA   |

| CANH                                                                                                  | I <sub>CANH</sub>                    | _    | —   | -35  |      |

| CANL                                                                                                  | ICANL                                | 35   | —   | —    |      |

| Over-temperature Shutdown                                                                             | T <sub>SD</sub>                      | 160  | 180 | —    | °C   |

| CANL Over-current Detection <sup>(26)</sup>                                                           |                                      |      |     |      | mA   |

| CANL                                                                                                  | I <sub>CANL/OC</sub>                 | 60   | —   | 200  |      |

| CANH                                                                                                  | I <sub>CANH/OC</sub>                 | -200 | —   | -60  |      |

| CANH and CANL Input Current, Device Supplied<br>(CAN Sleep mode with CAN Wake-up Enabled or Disabled) | I <sub>CAN1</sub>                    |      |     |      | μΑ   |

| V <sub>CANH</sub> , V <sub>CANL</sub> from 0 V to 5.0 V                                               |                                      | _    | 3.0 | 10   |      |

| $V_{CANH}$ , $V_{CANL}$ = -2.0 V                                                                      |                                      | -60  | -50 | _    |      |

| $V_{CANH}$ , $V_{CANL}$ = 7.0 V                                                                       |                                      |      | 60  | 75   |      |

Notes

25. Guaranteed by design; it is not production tested.

26. Reported in CAN register. For a description of the contents of the CAN register, refer to CAN Register (CAN) on page 49

Characteristics noted under conditions 4.75 V  $\leq$  V2  $\leq$  5.25 V, 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                    | Symbol            | Min                   | Тур                    | Max                   | Unit |

|---------------------------------------------------|-------------------|-----------------------|------------------------|-----------------------|------|

| PINS (CANH AND CANL) (CONTINUED)                  |                   | 1                     | 1                      | 1                     |      |

| CANH and CANL Input Current, Device Unsupplied    | I <sub>CAN2</sub> |                       |                        |                       | μA   |

| $V_{CANH}$ , $V_{CANL}$ = 2.5 V                   |                   | _                     | 40                     | 100                   |      |

| $V_{CANH}$ , $V_{CANL}$ = -2.0 V                  |                   | -60                   | -50                    | —                     |      |

| $V_{CANH}$ , $V_{CANL}$ = 7.0 V                   |                   | —                     | 190                    | 240                   |      |

| DIAGNOSTIC INFORMATION (CANH AND CANL)            | ·                 | •                     |                        |                       |      |

| CANL to GND Threshold                             | V <sub>LG</sub>   |                       | 1.75                   |                       | V    |

| CANH to GND Threshold                             | V <sub>HG</sub>   | —                     | 1.75                   | —                     | V    |

| CANL to VSUP Threshold                            | V <sub>LVB</sub>  | —                     | V <sub>SUP</sub> -2.0  | —                     | V    |

| CANH to VSUP Threshold                            | V <sub>HVB</sub>  | —                     | V <sub>SUP</sub> -2.0  | —                     | V    |

| CANL to VDD Threshold                             | V <sub>L5</sub>   | —                     | V <sub>DD</sub> -0.43  | —                     | V    |

| CANH to VDD Threshold                             | V <sub>H5</sub>   | _                     | V <sub>DD</sub> - 0.43 | _                     | V    |

| RXD Weak Pull-down Current Source <sup>(27)</sup> | I <sub>RXDW</sub> |                       |                        |                       | μA   |

| RXD Permanent Dominant Failure Condition          |                   | —                     | 100                    | —                     |      |

| PINS (TXD AND RXD)                                |                   |                       |                        |                       |      |

| TXD Input High-voltage                            | V <sub>IH</sub>   | 0.7 V <sub>DD</sub>   | —                      | V <sub>DD</sub> + 0.4 | V    |

| TXD Input Low-voltage                             | V <sub>IL</sub>   | -0.4                  | —                      | 0.3 V <sub>DD</sub>   | V    |

| TXD High-level Input Current                      | I <sub>IH</sub>   |                       |                        |                       | μA   |

| $V_{TXD} = V_2$                                   |                   | -10                   | —                      | 10                    |      |

| TXD Low-level Input Current                       | I <sub>IL</sub>   |                       |                        |                       | μA   |

| V <sub>TXD</sub> = 0 V                            |                   | -150                  | -100                   | -50                   |      |

| RXD Output High Voltage <sup>(28)</sup>           | V <sub>OH</sub>   |                       |                        |                       | V    |

| I <sub>RXD</sub> = 250 μA                         |                   | V <sub>DD</sub> - 1.0 | —                      | —                     |      |

| RXD Output Low-voltage                            | V <sub>OL</sub>   |                       |                        |                       | V    |

| $I_{RXD}$ = 1.0 mA                                |                   | _                     | —                      | 0.5                   |      |

Notes

27. Guaranteed by design; it is not production tested.

28. RXD is a push-pull structure between the V2 pin and GND.

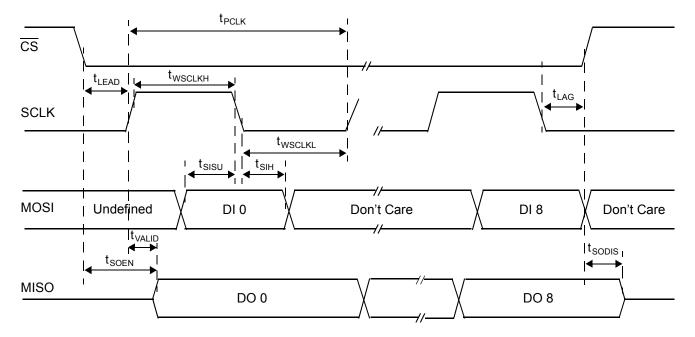

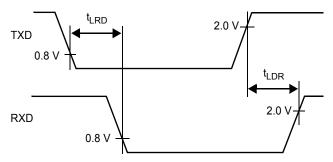

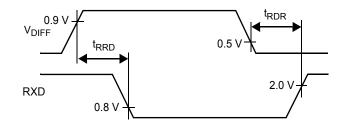

# **DYNAMIC ELECTRICAL CHARACTERISTICS**

#### Table 6. Dynamic Electrical Characteristics

Characteristics noted under conditions 4.75 V  $\leq$  V2  $\leq$  5.25 V, 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                          | Symbol                                  | Min  | Тур | Max      | Unit |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------|------|-----|----------|------|

| DIGITAL INTERFACE TIMING (SCLK, CS, MOSI, MISO) <sup>(29)</sup>                                         |                                         | 1    |     |          |      |

| SPI Operation Frequency                                                                                 | f <sub>REQ</sub>                        | 0.25 | _   | 4.0      | MHz  |

| SCLK Clock Period                                                                                       | t <sub>PCLK</sub>                       | 250  | _   | N/A      | ns   |

| SCLK Clock High Time                                                                                    | t <sub>wsclkh</sub>                     | 125  | _   | N/A      | ns   |

| SCLK Clock Low Time                                                                                     | t <sub>wsclkl</sub>                     | 125  | _   | N/A      | ns   |

| Falling Edge of CS to Rising Edge of SCLK                                                               | t <sub>LEAD</sub>                       | 100  | _   | N/A      | ns   |

| Falling Edge of SCLK to Rising Edge of $\overline{\text{CS}}$                                           | t <sub>LAG</sub>                        | 100  | _   | N/A      | ns   |

| MOSI to Falling Edge of SCLK                                                                            | t <sub>SISU</sub>                       | 40   | _   | N/A      | ns   |

| Falling Edge of SCLK to MOSI                                                                            | t <sub>SIH</sub>                        | 40   | _   | N/A      | ns   |

| MISO Rise Time <sup>(30)</sup><br>$C_L = 220 \text{ pF}$                                                | t <sub>RSO</sub>                        | _    | 25  | 50       | ns   |

| MISO Fall Time <sup>(30)</sup><br>C <sub>L</sub> = 220 pF                                               | t <sub>FSO</sub>                        | _    | 25  | 50       | ns   |

| Time from Falling or Rising Edges of CS<br>MISO Low-impedance<br>MISO High-impedance                    | t <sub>SOEN</sub><br>t <sub>SODIS</sub> |      |     | 50<br>50 | ns   |

| Time from Rising Edge of SCLK to MISO Data Valid 0.2 V_{DD} $\leq$ MISO $\geq$ 0.8 V_{DD}, C_L = 200 pF | t <sub>VALID</sub>                      | _    | _   | 50       | ns   |

# STATE MACHINE TIMING (CS, SCLK, MOSI, MISO, WDOG, INT)

| Delay Between CS LOW-to-HIGH Transition (at End of SPI Stop Command) and Stop mode Activation <sup>(31)</sup> | t <sub>CS-STOP</sub> |     |     |    | μS  |

|---------------------------------------------------------------------------------------------------------------|----------------------|-----|-----|----|-----|

|                                                                                                               |                      | 18  | —   | 34 |     |

| Interrupt Low-level Duration                                                                                  | t <sub>īNT</sub>     |     |     |    | μS  |

| Stop Mode                                                                                                     |                      | 7.0 | 10  | 13 |     |

| Internal Oscillator Frequency <sup>(32)</sup>                                                                 | f <sub>OSC</sub>     | —   | 100 | —  | kHz |

Notes

29. See Figure 7, SPI Timing Diagram, page 20.

30. Not production tested. Guaranteed by design.

31. Not production tested. Guaranteed by design. Detected by V2 OFF.

32. f<sub>OSC</sub> is indirectly measured (1.0 ms reset) and trimmed.

Characteristics noted under conditions 4.75 V  $\leq$  V2  $\leq$  5.25 V, 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                       | Symbol               | Min  | Тур  | Мах   | Unit     |

|------------------------------------------------------|----------------------|------|------|-------|----------|

| STATE MACHINE TIMING (CS, SCLK, MOSI, MISO, WDOG, IN | T) (CONTINUED)       |      |      |       |          |

| Watchdog Period Normal and Standby Modes             | twdog                |      |      |       | ms       |

| 28-pin SOIC                                          |                      |      |      |       |          |

| Period 1                                             |                      | 8.58 | 9.75 | 10.92 |          |

| Period 2                                             |                      | 39.6 | 45   | 50.4  |          |

| Period 3                                             |                      | 88   | 100  | 112   |          |

| Period 4                                             |                      | 308  | 350  | 392   |          |

| 48-pin QFN                                           |                      | 000  | 000  | 002   |          |

| Period 1                                             |                      | 8.3  | 9.75 | 10.92 |          |

| Period 2                                             |                      |      |      | 50.4  |          |

| Period 3                                             |                      | 38.5 | 45   |       |          |

| Period 4                                             |                      | 86   | 100  | 112   |          |

|                                                      |                      | 300  | 350  | 392   |          |

| Normal Request Mode Timeout                          | t <sub>NRTOUT</sub>  |      |      |       | ms       |

| 28-pin SOIC                                          |                      | 308  | 350  | 392   |          |

| 48-pin QFN                                           |                      | 300  | 350  | 392   |          |

| Watchdog Period Stop Mode                            | t <sub>WD-STOP</sub> |      |      |       | ms       |

| Period 1                                             |                      | 6.82 | 9.75 | 12.7  |          |

| Period 2                                             |                      | 31.5 | 45   | 58.5  |          |

| Period 3                                             |                      | 70   | 100  | 130   |          |

| Period 4                                             |                      | 245  | 350  | 455   |          |

| Watchdog Period Accuracy                             | t <sub>ACC</sub>     |      |      |       | %        |

| Normal and Standby Modes                             |                      | -12  | _    | 12    |          |

| Stop Mode                                            |                      | -30  | —    | 30    |          |

| Cyclic Sense/FWU Timing Sleep and Stop Modes         | t <sub>CSFWU</sub>   |      |      |       | ms       |

| Timing 1                                             |                      | 3.22 | 4.6  | 5.98  |          |

| Timing 2                                             |                      | 6.47 | 9.25 | 12    |          |

| Timing 3                                             |                      | 12.9 | 18.5 | 24    |          |

| Timing 4                                             |                      | 25.9 | 37   | 48.1  |          |

| Timing 5                                             |                      | 51.8 | 74   | 96.2  |          |

| Timing 6                                             |                      | 66.8 | 95.5 | 124   |          |

| Timing 7                                             |                      | 134  | 191  | 248   |          |

| Timing 8                                             |                      | 271  | 388  | 504   |          |

|                                                      |                      | 211  | 500  | 504   | <u> </u> |

| Cyclic Sense ON Time                                 | t <sub>ON</sub>      |      |      |       | μS       |

| Sleep and Stop modes.                                |                      | 200  | 350  | 500   |          |

| Cyclic Sense/FWU Timing Accuracy                     | t <sub>ACC</sub>     |      |      |       | %        |

| Sleep and Stop modes                                 |                      | -30  | _    | 30    |          |

Characteristics noted under conditions 4.75 V  $\leq$  V2  $\leq$  5.25 V, 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                               | Symbol               | Min | Тур | Мах | Unit |

|------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|-----|-----|------|

| STATE MACHINE TIMING (CS, SCLK, MOSI, MISO, WDOG, INT) (CONTI                                                                | NUED)                |     | 1   | I   | 1    |

| Delay Between SPI Command and HS Turn ON <sup>(33)</sup><br>Normal or Standby mode, V <sub>SUP</sub> > 9.0 V                 | t <sub>s-HSON</sub>  | _   | —   | 22  | μS   |

| Delay Between SPI Command and HS Turn OFF <sup>(33)</sup><br>Normal or Standby mode, V <sub>SUP</sub> > 9.0 V                | t <sub>S-HSOFF</sub> | _   | —   | 22  | μS   |

| Delay Between SPI and V2 Turn ON <sup>(33)</sup><br>Standby mode                                                             | t <sub>S-V2ON</sub>  | 9.0 | _   | 22  | μs   |

| Delay Between SPI and V2 Turn OFF <sup>(33)</sup><br>Normal mode                                                             | t <sub>S-V2OFF</sub> | 9.0 | _   | 22  | μS   |

| Delay Between Normal Request and Normal mode After Watchdog Trigger Command <sup>(33)</sup>                                  | t <sub>S-NR2N</sub>  |     |     |     | μs   |

| Normal Request mode                                                                                                          |                      | 15  | 35  | 70  |      |

| STATE MACHINE TIMING ( $\overline{CS}$ , SCLK, MOSI, MISO, $\overline{WDOG}$ , $\overline{INT}$ ) (CONTIN                    | IUED)                |     |     |     |      |

| Delay Between SPI and CAN Normal mode <sup>(34)</sup><br>Normal mode <sup>(35)</sup>                                         | t <sub>s-can_n</sub> | _   | _   | 10  | μS   |

| Delay Between SPI and CAN Sleep Mode <sup>(34)</sup><br>Normal mode <sup>(35)</sup>                                          | t <sub>s-can_s</sub> | _   | _   | 10  | μS   |

| Delay Between $\overline{CS}$ Wake-up ( $\overline{CS}$ LOW to HIGH) and Device in Normal Request mode (VDD ON and RST HIGH) | t <sub>₩-ՇS</sub>    |     |     |     | μs   |

| Stop mode                                                                                                                    |                      | 15  | 40  | 90  |      |

| Delay Between CS Wake-up (CS LOW to HIGH) and First Accepted SPI Command                                                     | t <sub>W-SPI</sub>   |     |     |     | μS   |

| Device in Stop mode After Wake-up                                                                                            |                      | 90  | —   | N/A |      |

| Delay Between INT Pulse and First SPI Command Accepted      | t <sub>S-1STSPI</sub> |  |

|-------------------------------------------------------------|-----------------------|--|

| Device in Stop mode After Wake-up                           |                       |  |

| Delay Between Two SPI Messages Addressing the Same Register | t <sub>2SPI</sub>     |  |

#### **OUTPUT PIN (VDD)**