# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### NXP Semiconductors Technical Data

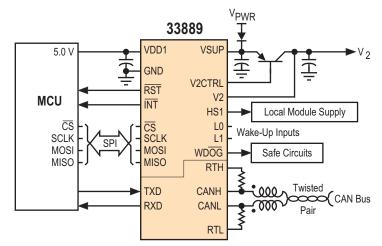

# System basis chip (SBC) with low speed fault tolerant CAN interface

The 33889 is an SBC having a fully protected, fixed 5.0 V low drop-out regulator, with current limit, overtemperature prewarning and reset. An SBC device is a monolithic IC combining many functions repeatedly found in standard microcontroller-based systems, e.g., protection, diagnostics, communication, power, etc.

An output drive with sense input is also provided to implement a second 5.0 V regulator using an external PNP. The 33889 has Normal, Standby, Stop and Sleep modes; an internally switched high-side power supply output with two wake-up inputs; programmable timeout or window watchdog, Interrupt, Reset, serial peripheral interface (SPI) input control, and a low-speed fault tolerant CAN transceiver, compatible with CAN 2.0 A and B protocols for module-to-module communications. The combination is an economical solution for power management, high-speed communication, and control in MCU-based systems. This device is powered by SMARTMOS technology.

#### Features

- VDD1: 5.0 V low drop voltage regulator, current limitation, overtemperature detection, monitoring and reset function with total current capability 200 mA

- V2: tracking function of VDD1 regulator; control circuitry for external bipolar ballast transistor for high flexibility in choice of peripheral voltage and current supply

- · Four operational modes

- · Low standby current consumption in Stop and Sleep modes

- Built-in low speed 125 kbps fault tolerant CAN physical interface.

- External high voltage wake-up input, associated with HS1 V<sub>BAT</sub> switch

150 mA output current capability for HS1 V<sub>BAT</sub> switch allowing drive of

- 150 mA output current capability for HS1 V<sub>BAT</sub> switch allowing drive external switches pull-up resistors or relays

| ORDERING INFORMATION                                          |                                        |           |  |  |  |

|---------------------------------------------------------------|----------------------------------------|-----------|--|--|--|

| <b>Device</b><br>(Add R2 Suffix for<br>Tape and Reel <b>)</b> | Temperature<br>Range (T <sub>A</sub> ) | Package   |  |  |  |

| MC33889BPEG                                                   | -40 to 125 °C                          | 28 SOICW  |  |  |  |

| *MC33889DPEG                                                  | -1010120 0                             | 20 001010 |  |  |  |

\*Recommended for new designs

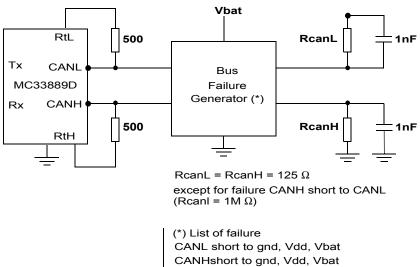

Figure 1. 33889 simplified application diagram

# 1 Device variations

#### Table 1. Device variations between the 33889D and 33889B versions <sup>(1)</sup>

| Devenuetore                                                                                               | Quarter at         | Tuelt | Device pa                        | e part number           |  |

|-----------------------------------------------------------------------------------------------------------|--------------------|-------|----------------------------------|-------------------------|--|

| Parameters                                                                                                | Symbol             | Trait | MC33889B <sup>(2)</sup>          | MC33889D <sup>(2)</sup> |  |

|                                                                                                           |                    | Min.  | 3.2 V                            | 3.5 V                   |  |

| Differential Receiver, Recessive To Dominant Threshold (By Definition, $V_{DIFF} = V_{CANH} - V_{CANL}$ ) | V <sub>DIFF1</sub> | Тур   | 2.6 V                            | 3.0 V                   |  |

| CANE CANE                                                                                                 | - DIFF I           | Max.  | 2.1 V                            | 2.5 V                   |  |

|                                                                                                           |                    | Min.  | 3.2 V                            | 3.5 V                   |  |

| Differential Receiver, Dominant To Recessive Threshold (Bus Failures 1, 2, 5)                             | V <sub>DIFF2</sub> | Тур   | 2.6 V                            | 3.0 V                   |  |

|                                                                                                           | DIFFZ              | Max.  | 2.1 V                            | 2.5 V                   |  |

|                                                                                                           |                    | Min.  | 50 mA                            | 50 mA                   |  |

| CANH Output Current (V <sub>CANH</sub> = 0; TX = 0.0)                                                     | I <sub>CANH</sub>  | Тур   | 75 mA                            | 100 mA                  |  |

|                                                                                                           | CANT               | Max.  | 110 mA                           | 130 mA                  |  |

|                                                                                                           | ICANL              | Min.  | 50 mA                            | 50 mA                   |  |

| CANL Output Current (V <sub>CANL</sub> = 14 V; TX = 0.0)                                                  |                    | Тур   | 90 mA                            | 140 mA                  |  |

|                                                                                                           | CANE               | Max.  | 135 mA                           | 170 mA                  |  |

| Detection threshold for Short circuit to Battery voltage                                                  | Vcanh              | Max.  | Vsup/2 + 5V                      | Vsup/2 + 4.55V          |  |

| oop time Tx to Rx, no bus failure, ISO configuration                                                      | tLOOPRD            | Max.  | N/A                              | 1.5us                   |  |

| loop time Tx to Rx, with bus failure, ISO configuration                                                   | tLOOPRD-F          | Max.  | N/A                              | 1.9us                   |  |

| oop time Tx to Rx, with bus failure and +-1.5V gnd shift,<br>5 node network, ISO configuration            | tLOOPRD/DR-F+GS    |       | N/A                              | 3.6us                   |  |

|                                                                                                           |                    | Min.  | N/A                              | 8                       |  |

| Minimum Dominant time for Wake up on CANL or CANH (Tem Vbat mode)                                         | tWAKE              | typ   | 30                               | 16                      |  |

|                                                                                                           |                    | Max.  | N/A                              | 30                      |  |

| T2SPI timing                                                                                              | T2spi              | Min.  | not specified, 25us spec applied | 25us                    |  |

| Device behavior                                                                                           | 1                  |       | 1                                |                         |  |

| CANH or CANL open wire recovery principle | Reference MC33889B on page 32  | after 4 non consecutive<br>pulses | after 4 consecutive pulses                         |

|-------------------------------------------|--------------------------------|-----------------------------------|----------------------------------------------------|

| Rx behavior in TermVbat mode              | Reference MC333889D on page 32 | Rx recessive, no pulse            | Rx recessive, dominant pulse to signal bus traffic |

Notes

1. This datasheet uses the term 33889 in the inclusive sense, referring to both the D version (33889D) and the B version (33689B).

2. The 33889D and 33889B versions are nearly identical. However, where variations in characteristic occur, these items will be separated onto individual lines.

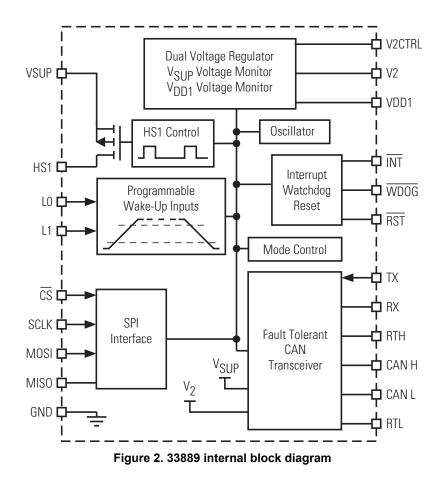

# 2 Internal block diagram

# 3 Pin connections

| RX 📼     | 1 • | 28 |            |

|----------|-----|----|------------|

| TX 📼     | 2   | 27 | □ CS       |

| VDD1 📼   | 3   | 26 | □ – I MOSI |

| RST 📼    | 4   | 25 | 💷 MISO     |

| INT 📼    | 5   | 24 | □ SCLK     |

| GND 📼    | 6   | 23 | 💷 GND      |

| GND 📼    | 7   | 22 | 🖽 GND      |

| GND 📼    | 8   | 21 | 💷 GND      |

| GND 📼    | 9   | 20 | 💷 GND      |

| V2CTRL 📼 | 10  | 19 | 📼 CANL     |

| VSUP 📼   | 11  | 18 | 🖵 CANH     |

| HS1 📼    | 12  | 17 | 💷 RTL      |

| L0 📼     | 13  | 16 | 💷 RTH      |

| L1 📼     | 14  | 15 | □ 1 V2     |

| l        |     |    | 1          |

#### Figure 3. 33889 pin connections

A functional description of each pin can be found in the Functional pin description section page 20.

#### Table 2. Pin definitions

| Pin           | Pin name | Pin function | Formal Name              | Definition                                                                                                                                                                 |

|---------------|----------|--------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | RX       | Output       | Receiver Data            | CAN bus receive data output pin                                                                                                                                            |

| 2             | ΤX       | Input        | Transmitter Data         | CAN bus receive data input pin                                                                                                                                             |

| 3             | VDD1     | Power Output | Voltage Regulator One    | 5.0 V pin is a 2% low drop voltage regulator for to the microcontroller supply.                                                                                            |

| 4             | RST      | Output       | Reset                    | This is the device reset output pin whose main function is to reset the MCU.                                                                                               |

| 5             | INT      | Output       | Interrupt                | This output is asserted LOW when an enabled interrupt condition occurs.                                                                                                    |

| 6 -9, 20 - 23 | GND      | Ground       | Ground                   | These device ground pins are internally connected to the package lead frame to provide a 33889-to-PCB thermal path.                                                        |

| 10            | V2CTRL   | Output       | Voltage Source 2 Control | Output drive source for the V2 regulator connected to the external series pass transistor.                                                                                 |

| 11            | VSUP     | Power Input  | Voltage Supply           | Supply input pin.                                                                                                                                                          |

| 12            | HS1      | Output       | High-Side Output         | Output of the internal high-side switch.                                                                                                                                   |

| 13 - 14       | L0, L1   | Input        | Level 0 - 1 Inputs       | Inputs from external switches or from logic circuitry.                                                                                                                     |

| 15            | V2       | Input        | Voltage Regulator Two    | 5.0 V pin is a low drop voltage regulator dedicated to the peripherals supply.                                                                                             |

| 16            | RTH      | Output       | RTH                      | Pin for connection of the bus termination resistor to CANH.                                                                                                                |

| 17            | RTL      | Output       | RTL                      | Pin for connection of the bus termination resistor to CANL.                                                                                                                |

| 18            | CANH     | Output       | CAN High                 | CAN high output pin.                                                                                                                                                       |

| 19            | CANL     | Output       | CAN Low                  | CAN low output pin.                                                                                                                                                        |

| 24            | SCLK     | Input        | System Clock             | Clock input pin for the Serial Peripheral Interface (SPI).                                                                                                                 |

| 25            | MISO     | Output       | Master In/Slave Out      | SPI data sent to the MCU by the 33889. When $\rm CS_{\rm LOW}$ is HIGH, the pin is in the high impedance state.                                                            |

| 26            | MOSI     | Input        | Master Out/Slave In      | SPI data received by the 33889.                                                                                                                                            |

| 27            | CS       | Input        | Chip Select              | The CS <sub>LOW</sub> input pin is used with the SPI bus to select the 33889. When the CS <sub>LOW</sub> is asserted LOW, the 33889 is the selected device of the SPI bus. |

| 28            | WDOG     | Output       | Watchdog                 | The WDOG output pin is asserted LOW if the software watchdog is not correctly triggered.                                                                                   |

# 4 Electrical characteristics

### 4.1 Maximum ratings

#### Table 3. Maximum ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                                  | Ratings                                                                                                                                                             | Max.                                                | Unit         | Notes   |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------|---------|

| lectrical ratings                                       | 5<br>5                                                                                                                                                              |                                                     |              |         |

| V <sub>SUP</sub>                                        | Supply Voltage at VSUP<br>Continuous voltage<br>Transient voltage (Load dump)                                                                                       | -0.3 to 27<br>40                                    | V            |         |

| V <sub>LOG</sub>                                        | Logic Signals (RX, TX, MOSI, MISO, CS, SCLK, RST, WDOG, INT)                                                                                                        | -0.3 to V <sub>DD1</sub> +0.3                       | V            |         |

| I                                                       | Output current VDD1                                                                                                                                                 | Internally Limited                                  | mA           |         |

| V<br>I                                                  | HS1<br>Voltage<br>Output Current                                                                                                                                    | -0.2 to V <sub>SUP</sub> +0.3<br>Internally Limited | V<br>A       |         |

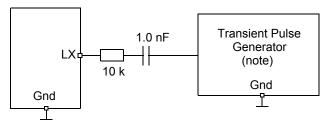

| V <sub>WU</sub><br>I <sub>WU</sub><br>V <sub>TRWU</sub> | L0, L1<br>DC Input voltage<br>DC Input current<br>Transient input voltage (according to ISO7637 specification) and with external<br>component per <u>Figure 4</u> . | -0.3 to 40<br>-2.0 to 2.0<br>+-100                  | V<br>mA<br>V |         |

| V <sub>2INT</sub>                                       | DC voltage at V2 (V2INT)                                                                                                                                            | 0 to 5.25                                           | V            |         |

| V <sub>BUS</sub>                                        | DC Voltage On Pins CANH, CANL                                                                                                                                       | -20 to +27                                          | V            |         |

| V <sub>CANH</sub> /V <sub>CANL</sub>                    | Transient Voltage At Pins CANH, CANL<br>0.0 < V2-INT < 5.5 V; VSUP = 0.0; T < 500 ms                                                                                | -40 to +40                                          | V            |         |

| V <sub>TR</sub>                                         | Transient Voltage On Pins CANH, CANL<br>(Coupled Through 1.0 nF Capacitor)                                                                                          | -150 to +100                                        | V            |         |

| V <sub>RTL</sub> , V <sub>RTH</sub>                     | DC Voltage On Pins RTH, RTL                                                                                                                                         | -0.3 to +27                                         | V            |         |

| V <sub>RTH</sub> /V <sub>RTL</sub>                      | Transient Voltage At Pins RTH, RTL<br>0.0 < V2-INT < 5.5 V; VSUP = 0.0; T < 500 ms                                                                                  | -0.3 to +40                                         | V            |         |

| V <sub>ESDH</sub>                                       | ESD voltage (HBM 100 pF, 1.5 k)<br>CANL, CANH, HS1, L0, L1<br>RTH, RTL<br>All other pins                                                                            | ±4.0<br>±3.0<br>±2.0                                | kV           | (3)     |

| V <sub>ESD-MM</sub>                                     | ESD voltage (Machine Model) All pins, MC33889B                                                                                                                      | ±200                                                | V            | (3) (4) |

| V <sub>ESD-CDM</sub>                                    | ESD voltage (CDM) All pins, MC33889D<br>Pins 1,14,15, & 28<br>All other pins                                                                                        | 750<br>500                                          | V            | (4)     |

| R <sub>T</sub>                                          | RTH, RTL Termination Resistance                                                                                                                                     | 500 to 16000                                        | Ω            |         |

#### Table 3. Maximum ratings (continued)

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol             | Ratings                                               | Max.       | Unit | Notes |

|--------------------|-------------------------------------------------------|------------|------|-------|

| Thermal ratings    |                                                       |            |      |       |

| TJ                 | Junction Temperature                                  | -40 to 150 | °C   |       |

| Τ <sub>S</sub>     | Storage Temperature                                   | -55 to 165 | °C   |       |

| T <sub>A</sub>     | Ambient Temperature (for info only)                   | -40 to 125 | °C   |       |

| R <sub>THJ/P</sub> | Thermal resistance junction to gnd pin <sup>(5)</sup> | 20         | °C/W |       |

Notes:

3. Testing done in accordance with the Human Body Model (CzaP = 100 pF, RzaP = 1500 Ω), Machine Model (CzaP = 200 pF, RzaP = 0 Ω).

4. ESD machine model (MM) is for MC33889B only. MM is now replaced by CDM (Charged Discharged model).

5. Gnd pins 6,7,8,9,20, 21, 22, 23.

Note: Waveform in accordance to ISO7637 part1, test pulses 1, 2, 3a and 3b.

#### Figure 4. Transient test pulse for L0 and L1 inputs

### 4.2 Static electrical characteristics

#### Table 4. Static electrical characteristics

Characteristics noted under conditions -  $V_{SUP}$  From 5.5 V to 18 V and  $T_J$  from -40 to 125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25$  °C under nominal conditions unless otherwise noted.

| Symbol                       | Description                                                                                                      | Min. | Тур. | Max. | Unit | Notes                         |

|------------------------------|------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------------------------------|

| put pin (VSUP)               |                                                                                                                  |      |      | I    | I    |                               |

| V <sub>SUP</sub>             | Nominal DC Voltage range                                                                                         | 5.5  | -    | 18   | V    |                               |

| V <sub>SUP-EX1</sub>         | Extended DC Voltage range 1<br>Reduced functionality                                                             | 4.5  | -    | 5.5  | V    | (6)                           |

| V <sub>SUP-EX2</sub>         | Extended DC Voltage range 2                                                                                      | 18   | -    | 27   | V    | (8)                           |

| V <sub>SUPLD</sub>           | Input Voltage during Load Dump<br>Load dump situation                                                            | -    | -    | 40   | V    |                               |

| V <sub>SUPJS</sub>           | Input Voltage during jump start<br>Jump start situation                                                          | -    | -    | 27   | V    |                               |

| I <sub>SUP</sub><br>(SLEEP1) | Supply Current in Sleep Mode $V_{DD1}$ & V2 off, $V_{SUP} \le$ 12 V, oscillator running                          | -    | 95   | 130  | μA   | (7) (10                       |

| I <sub>SUP</sub><br>(SLEEP2) | Supply Current in Sleep Mode $V_{DD1}$ & V2 off, $V_{SUP} \le 12$ V, oscillator not running                      | -    | 55   | 90   | μΑ   | (7)                           |

| I <sub>SUP</sub><br>(SLEEP3) | Supply current in sleep mode<br>V <sub>DD1</sub> & V2 off, V <sub>SUP</sub> = 18 V, oscillator running           | -    | 170  | 270  | μΑ   | (7) (10                       |

| I <sub>SUP(STDBY)</sub>      | Supply Current in Stand-by Mode $I_{OUT}$ at $V_{DD1}$ = 40 mA, CAN recessive state or disabled                  | -    | 42   | 45   | mA   | (7),(9                        |

| I <sub>SUP(NORM)</sub>       | Supply Current in Normal Mode $I_{OUT}$ at $V_{DD1}$ = 40 mA, CAN recessive state or disabled                    | -    | 42.5 | 45   | mA   | (7)                           |

| I <sub>SUP</sub><br>(STOP1)  | Supply Current in Stop mode $I_{OUT} V_{DD1}$ < 2.0 mA, $V_{DD1}$ on , $V_{SUP} \le$ 12 V, oscillator running    | -    | 120  | 150  | μA   | (7),(9)(<br>(11)              |

| I <sub>SUP</sub><br>(STOP2)  | Supply Current in Stop mode $I_{OUT} V_{DD1}$ < 2.0 mA, $V_{DD1}$ on, $V_{SUP} \le$ 12 V, oscillator not running | -    | 80   | 110  | μA   | (7),(9)(<br>(11)              |

| I <sub>SUP</sub><br>(STOP3)  | Supply Current in Stop mode<br>lout $V_{DD1}$ < 2.0 mA, $V_{DD1}$ on, $V_{SUP}$ = 18 V, oscillator running       | -    | 200  | 285  | μΑ   | (7),(9)( <sup>-</sup><br>(11) |

| V <sub>THRESH</sub>          | Supply Fail Flag internal threshold                                                                              | 1.5  | 3.0  | 4.0  | V    |                               |

| V <sub>DETHYST</sub>         | Supply Fail Flag hysteresis                                                                                      | -    | 1.0  | -    | V    | (12)                          |

| $BF_EW$                      | Battery fall early warning threshold<br>In normal & standby mode                                                 | 5.8  | 6.1  | 6.4  | V    |                               |

| BF <sub>EWH</sub>            | Battery fall early warning hysteresis<br>In normal & standby mode                                                | 0.1  | 0.2  | 0.3  | V    | (12)                          |

Notes

6.  $V_{DD1}$  > 4.0 V, reset high, if  $R_{STTH-2}$  selected and  $I_{OUT}$   $V_{DD1}$  reduced, logic pin high level reduced, device is functional.

7. Current measured at V<sub>SUP</sub> pin.

8. Device is fully functional. All modes available and operating, Watchdog, HS1 turn ON turn OFF, CAN cell operating, L0 and L1 inputs operating, SPI read write operation. Over temperature may occur.

9. Measured in worst case condition with 5.0 V at V2 pin (V2 pin tied to VDD1).

10. Oscillator running means "Forced Wake-up" or "Cyclic Sense" or "Software Watchdog" timer activated. Software Watchdog is available in stop mode only.

11.  $V_{DD1}$  is ON with 2.0 mA typical output current capability.

12. Guaranteed by design

Characteristics noted under conditions -  $V_{SUP}$  From 5.5 V to 18 V and  $T_J$  from -40 to 125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25$  °C under nominal conditions unless otherwise noted.

| Symbol                           | Description                                                                                                                       | Min.       | Тур.     | Max.     | Unit | Notes |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------|----------|----------|------|-------|

| Output pin (VDD                  | 1) (14)                                                                                                                           | L          |          | I        | I    |       |

| V <sub>DD1OUT</sub>              | VDD1 Output Voltage<br>I <sub>DD1</sub> from 2.0 to 200 mA<br>5.5 V < V <sub>SUP</sub> < 27 V<br>4.5 V < V <sub>SUP</sub> < 5.5 V | 4.9<br>4.0 | 5.0<br>- | 5.1<br>- | V    |       |

| V <sub>DD1DROP</sub>             | Drop Voltage V <sub>SUP</sub> > V <sub>DDOUT</sub><br>I <sub>DD1</sub> = 200 mA                                                   | -          | 0.2      | 0.5      | V    |       |

| V <sub>DD1DP2</sub>              | Drop Voltage $V_{SUP} > V_{DDOUT}$ , limited output current<br>I <sub>DD1</sub> = 50 mA<br>4.5 V < V <sub>SUP</sub> < 27 V        | -          | 0.1      | 0.25     | V    |       |

| I <sub>DD1</sub>                 | I <sub>DD1</sub> Output Current<br>Internally limited                                                                             | 200        | 270      | 350      | mA   |       |

| V <sub>DDSTOP</sub>              | VDD1 Output Voltage in stop mode<br>I <sub>OUT</sub> < 2.0 mA                                                                     | 4.75       | 5.00     | 5.25     | V    |       |

| I <sub>DD1S-WU1</sub>            | I <sub>DD1</sub> stop output current to wake-up SBC<br>Default value after reset.                                                 | 2.0        | 3.5      | 6.0      | mA   | (15)  |

| IDD1S-WU2                        | I <sub>DD1</sub> stop output current to wake-up SBC                                                                               | 10         | 14       | 18       | mA   | (15)  |

| I <sub>DD1-DGIT11</sub>          | I <sub>DD1</sub> overcurrent wake deglitcher<br>(with I <sub>DD1S-WU1</sub> selected)                                             | 40         | 55       | 75       | μs   | (13)  |

| I <sub>DD1-DGIT2</sub>           | I <sub>DD1</sub> overcurrent wake deglitcher<br>(with I <sub>DD1S-WU2</sub> selected)                                             | -          | 150      | -        | μs   | (13)  |

| T <sub>SD</sub>                  | Thermal Shutdown<br>Normal or standby mode                                                                                        | 160        | -        | 190      | °C   |       |

| T <sub>PW</sub>                  | Overtemperature prewarning<br>VDDTEMP bit set                                                                                     | 130        | -        | 160      | °C   |       |

| T <sub>SD</sub> -T <sub>PW</sub> | Temperature Threshold difference                                                                                                  | 20         | -        | 40       | °C   |       |

| V <sub>RST-TH1</sub>             | Reset threshold 1<br>Default value after reset. <sup>(15)</sup>                                                                   | 4.5        | 4.6      | 4.7      | V    |       |

| V <sub>RST-TH2</sub>             | Reset threshold 2 <sup>(15)</sup>                                                                                                 | 4.1        | 4.2      | 4.3      | V    |       |

| RESET-DUR                        | Reset duration                                                                                                                    | 0.85       | 1.0      | 2.0      | ms   |       |

| V <sub>DD</sub>                  | VDD1 range for Reset Active                                                                                                       | 1.0        | -        | -        | V    |       |

| t <sub>D</sub>                   | Reset Delay Time<br>Measured at 50% of reset signal. <sup>(13)</sup>                                                              | 5.0        | -        | 20       | μs   |       |

| LR1                              | Line Regulation<br>9.0 V < V <sub>SUP</sub> < 18 V, I <sub>DD</sub> = 10 mA                                                       | -          | 5.0      | 25       | mV   |       |

| LR2                              | Line Regulation<br>5.5 V < V <sub>SUP</sub> < 27 V, I <sub>DD</sub> = 10 mA                                                       | -          | 10       | 25       | mV   |       |

| LD                               | Load Regulation<br>1.0 mA < I <sub>IDD</sub> < 200 mA                                                                             | -          | 25       | 75       | mV   |       |

| THERMS                           | Thermal stability<br>V <sub>SUP</sub> = 13.5 V, I = 100 mA                                                                        | -          | 5.0      | -        | mV   |       |

Notes

13. Guaranteed by design

14.  $I_{DD1}$  is the total regulator output current. VDD specification with external capacitor C  $\ge$  22  $\mu$ F and ESR < 10  $\Omega$ .

15. Selectable by SPI

Characteristics noted under conditions -  $V_{SUP}$  From 5.5 V to 18 V and  $T_J$  from -40 to 125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A$  = 25 °C under nominal conditions unless otherwise noted.

| Symbol                             | Description                                                                                                       | Min.                 | Тур. | Max.                   | Unit             | Notes |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------|------|------------------------|------------------|-------|

| 2 regulator (V2                    | 2) (16)                                                                                                           |                      |      |                        |                  |       |

|                                    | V2 Output Voltage                                                                                                 |                      |      |                        |                  |       |

| V2                                 | I2 from 2.0 to 200 mA, 5.5 V < V <sub>SUP</sub> < 27 V <sup>(17)</sup>                                            | 0.99                 | 1.0  | 1.01                   | V <sub>DD1</sub> |       |

| 12                                 | I2 output current (for information only)<br>Depending on the external ballast transistor                          | 200                  | -    | -                      | mA               |       |

| I2 <sub>CTRL</sub>                 | V2 CTRL sink current capability                                                                                   | 10                   | -    | -                      | mA               |       |

| V2L <sub>TH</sub>                  | V2LOW flag threshold                                                                                              | 3.75                 | 4.0  | 4.25                   | V                |       |

| I <sub>V2RS</sub>                  | Internal V2 Supply Current (CAN and SBC in Normal Mode). TX = 5.0 V, CAN in Recessive State                       | 3.8                  | 5.6  | 6.8                    | mA               |       |

| I <sub>V2DS</sub>                  | Internal V2 Supply Current (CAN and SBC in Normal Mode). TX = 0.0 V, No Load, CAN in Dominant State               | 4.0                  | 5.8  | 7.0                    | mA               |       |

| $I_{V2R}$                          | Internal V2 Supply Current (CAN in Receive Only Mode, SBC in Normal mode). V <sub>SUP</sub> = 12 V                | -                    | 80   | 120                    | μΑ               |       |

| I <sub>V2BT</sub>                  | Internal V2 Supply Current (CAN in Bus TermVbat mode, SBC in normal mode), $\rm V_{SUP}$ = 12 V                   | -                    | 35   | 60                     | μΑ               |       |

| ogic output pi                     | ns (MISO)                                                                                                         |                      |      | -11                    |                  |       |

| V <sub>OL</sub>                    | Low Level Output Voltage<br>I <sub>OUT</sub> = 1.5 mA                                                             | -                    | -    | 1.0                    | V                |       |

| V <sub>OH</sub>                    | High Level Output Voltage $I_{OUT}$ = -250 $\mu$ A                                                                | V <sub>DD1-0.9</sub> | -    | -                      | V                |       |

| I <sub>HZ</sub>                    | Tri-state MISO Leakage Current<br>0.0 V < V <sub>MISO</sub> < V <sub>DD</sub>                                     | -2.0                 | -    | +2.0                   | μA               |       |

| ogic input pins                    | s (MOSI, SCLK, CS)                                                                                                |                      |      |                        |                  |       |

| V <sub>IH</sub>                    | High Level Input Voltage                                                                                          | 0.7V <sub>DD1</sub>  | -    | V <sub>DD1</sub> +0.3V |                  |       |

| V <sub>IL</sub>                    | Low Level Input Voltage                                                                                           | -0.3                 | -    | 0.3 V <sub>DD1</sub>   | V                |       |

| I <sub>IH</sub><br>I <sub>IL</sub> | Input Current on $\overline{CS}$<br>$V_1 = 4.0 V$<br>$V_1 = 1.0 V$                                                | -100                 | -    | -20                    | μΑ               |       |

| I <sub>IL</sub>                    | Low Level Input Current $\overline{CS}$<br>V <sub>1</sub> = 1.0 V                                                 | -100                 | -    | -20                    | μA               |       |

| I <sub>IN</sub>                    | MOSI, SCLK Input Current<br>0.0 < V <sub>IN</sub> < V <sub>DD</sub>                                               | -10                  | -    | 10                     | μΑ               |       |

| eset pin (RST)                     |                                                                                                                   |                      |      |                        |                  |       |

| I <sub>ОН</sub>                    | High Level Output current<br>0.0 < V <sub>OUT</sub> < 0.7 V <sub>DD</sub>                                         | -350                 | -250 | -150                   | μA               |       |

| V <sub>OL</sub>                    | Low Level Output Voltage (I <sub>0</sub> = 1.5 mA)<br>5.5 V < V <sub>SUP</sub> < 27 V<br>1.0 V < V <sub>DD1</sub> | 0.0<br>0.0           | -    | 0.9<br>0.9             | V                |       |

| I <sub>PDW</sub>                   | Reset pull-down current                                                                                           | 2.3                  | -    | 5.0                    | mA               |       |

16. V2 tracking voltage regulator - V2 specification with external capacitor

- option 1:  $C \ge 22 \ \mu F$  and ESR < 10  $\Omega$ . Using a resistor of 2 k $\Omega$  or less between the base and emitter of the external PNP is recommended. - option2: 1.0  $\mu F < C < 22 \ \mu F$  and ESR < 10  $\Omega$ . In this case depending on the ballast transistor gain an additional resistor and capacitor network between emitter and base of PNP ballast transistor might be required. Refer to NXP application information or contact your local technical support. - option 3: 10  $\mu F < C < 22 \ \mu F$  ESR > 0.2  $\Omega$ : a resistor of 2 k $\Omega$  or less is required between the base and emitter of the external PNP.

17. For  $I_{VDD1} > 10 \text{ mA}$

Characteristics noted under conditions -  $V_{SUP}$  From 5.5 V to 18 V and  $T_J$  from -40 to 125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A$  = 25 °C under nominal conditions unless otherwise noted.

| Symbol                | Description                                                                                                    | Min.                  | Тур. | Max.             | Unit | Notes |

|-----------------------|----------------------------------------------------------------------------------------------------------------|-----------------------|------|------------------|------|-------|

| Vatchdog pin (        | (Wdog)                                                                                                         |                       |      | 1                |      | 1     |

|                       | Low Level Output Voltage (I <sub>0</sub> = 1.5 mA)                                                             | 0.0                   |      | 0.0              |      |       |

| V <sub>OL</sub>       | 5.5 V < V <sub>SUP</sub> < 27 V                                                                                | 0.0                   | -    | 0.9              | V    |       |

| V <sub>OH</sub>       | High Level Output Voltage ( $I_0 = -250 \ \mu A$ )                                                             | V <sub>DD1</sub> -0.9 | -    | V <sub>DD1</sub> | V    |       |

| terrupt Pin (IN       | T)                                                                                                             |                       |      |                  |      |       |

| V <sub>OL</sub>       | Low Level Output Voltage (I <sub>0</sub> = 1.5 mA)                                                             | 0.0                   | -    | 0.9              | V    |       |

| V <sub>OH</sub>       | High Level Output Voltage ( $I_0 = -250 \ \mu A$ )                                                             | V <sub>DD1</sub> -0.9 | -    | V <sub>DD1</sub> | V    |       |

| igh-side outpu        | it pin (HS1)                                                                                                   |                       |      |                  |      |       |

| R <sub>DSON25</sub>   | R <sub>DSON</sub> at Tj = 25 °C, and I <sub>OUT</sub> -150 mA<br>V <sub>SUP</sub> > 9.0 V                      | -                     | -    | 2.5              | w    |       |

| R <sub>DSON125</sub>  | R <sub>DSON</sub> at T <sub>J</sub> = 125 °C, and I <sub>OUT</sub> -150 mA<br>V <sub>SUP</sub> > 9.0 V         | -                     | -    | 5.0              | w    |       |

| R <sub>DON125-2</sub> | R <sub>DSON</sub> at T <sub>J</sub> = 125 °C, and I <sub>OUT</sub> -120 mA<br>5.5 V < V <sub>SUP</sub> < 9.0 V | -                     | 4.0  | 5.5              | W    |       |

| I <sub>LIM</sub>      | Output current limitation                                                                                      | 160                   | -    | 500              | mA   |       |

| O <sub>VT</sub>       | Overtemperature Shutdown                                                                                       | 155                   | -    | 190              | °C   |       |

| I <sub>LEAK</sub>     | Leakage current                                                                                                | -                     | -    | 10               | μΑ   |       |

| V <sub>CL</sub>       | Output Clamp Voltage at I <sub>OUT</sub> = -1.0 mA<br>no inductive load drive capability                       | -1.5                  | -    | -0.3             | V    | (18)  |

| put pins (L0 a        | nd L1)                                                                                                         |                       |      |                  | I    |       |

|                       | L0 Negative Switching Threshold                                                                                |                       |      |                  |      |       |

|                       | 5.5 V < V <sub>SUP</sub> < 6.0 V                                                                               | 1.7                   | 2.0  | 3.0              |      |       |

| V <sub>TH0N</sub>     | 6.0 V < V <sub>SUP</sub> < 18 V                                                                                | 2.0                   | 2.4  | 3.0              | V    |       |

|                       | 18 V < V <sub>SUP</sub> < 27 V                                                                                 | 2.0                   | 2.5  | 3.1              |      |       |

|                       | L0 Positive Switching Threshold                                                                                |                       |      |                  |      |       |

|                       | 5.5 V < V <sub>SUP</sub> < 6.0 V                                                                               | 2.2                   | 2.75 | 4.0              |      |       |

| V <sub>TH0P</sub>     | 6.0 V < V <sub>SUP</sub> < 18 V                                                                                | 2.5                   | 3.4  | 4.0              | V    |       |

|                       | 18 V < V <sub>SUP</sub> < 27 V                                                                                 | 2.5                   | 3.5  | 4.1              |      |       |

|                       |                                                                                                                | 2.0                   | 0.0  |                  |      |       |

|                       | L1 Negative Switching Threshold                                                                                |                       |      |                  |      |       |

| V <sub>TH1N</sub>     | 5.5 V < V <sub>SUP</sub> < 6.0 V                                                                               | 2.0                   | 2.5  | 3.0              | V    |       |

| ♥ I H1N               | 6.0 V < V <sub>SUP</sub> < 18 V                                                                                | 2.5                   | 3.0  | 3.7              | v    |       |

|                       | 18 V < V <sub>SUP</sub> < 27 V                                                                                 | 2.7                   | 3.2  | 3.8              |      |       |

|                       | L1 Positive Switching Threshold                                                                                |                       |      |                  |      |       |

|                       | 5.5 V < V <sub>SUP</sub> < 6.0 V                                                                               | 2.7                   | 3.3  | 3.8              |      |       |

| V <sub>TH1P</sub>     | 6.0 V < V <sub>SUP</sub> < 18V                                                                                 | 3.0                   | 4.0  | 4.7              | V    |       |

|                       | 18 V < V <sub>SUP</sub> < 27 V                                                                                 | 3.5                   | 4.2  | 4.8              |      |       |

|                       | Hysteresis                                                                                                     |                       |      |                  |      |       |

| V <sub>HYST</sub>     | 5.5 V < V <sub>SUP</sub> < 27 V                                                                                | 0.6                   | 1.0  | 1.3              | V    |       |

|                       | Input current                                                                                                  |                       |      | 40               |      | 1     |

| I <sub>IN</sub>       | -0.2 V < V <sub>IN</sub> < 40 V                                                                                | -10                   | -    | 10               | μA   | 1     |

Notes

18. Refer to HS1 negative maximum rating voltage limitation of -0.2 V.

Characteristics noted under conditions -  $V_{SUP}$  From 5.5 V to 18 V and  $T_J$  from -40 to 125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25$  °C under nominal conditions unless otherwise noted.

| Symbol                               | Description                                                                                                                                                      | Min.                     | Тур.         | Max.                         | Unit | Notes |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------|------------------------------|------|-------|

| CAN module spe                       | cification (TX, RX, CANH, CANL, RTH, and RTL)                                                                                                                    | <u> </u>                 |              |                              |      | 1     |

| V <sub>LOGIC</sub>                   | DC Voltage On Pins TX, RX                                                                                                                                        | -0.3                     |              | V <sub>DD1</sub> + 0.3       | V    |       |

| V2 <sub>INT</sub>                    | DC voltage at V2 (V2INT)                                                                                                                                         | 0.0                      |              | 5.25                         | V    |       |

| V <sub>BUS</sub>                     | DC Voltage On Pins CANH, CANL                                                                                                                                    | -20                      |              | +27                          | V    | 1     |

| V <sub>CANH</sub> /V <sub>CANL</sub> | Transient Voltage At Pins CANH, CANL 0.0 < V <sub>2-INT</sub> < 5.5 V; V <sub>SUP</sub> $\geq$ 0.0; T < 500 ms                                                   | -40                      | -            | 40                           | V    |       |

| V <sub>TR</sub>                      | Transient Voltage On Pins CANH, CANL (Coupled Through 1.0 nF Capacitor)                                                                                          | -150                     | -            | 100                          | V    |       |

| V <sub>CANH</sub>                    | Detection Threshold For Short-circuit To Battery Voltage (Term VBAT Mode) MC33889B                                                                               | V <sub>SUP</sub> /2+3    | -            | V <sub>SUP</sub> /2+5        | V    |       |

| V <sub>CANH</sub>                    | Detection Threshold For Short-circuit To Battery Voltage (Term VBAT Mode) MC33889D                                                                               | V <sub>SUP</sub> /2+3    | -            | V <sub>SUP</sub> /<br>2+4.55 | V    |       |

| V <sub>RTL</sub> , V <sub>RTH</sub>  | DC Voltage On Pins RTH, RTL                                                                                                                                      | -0.3                     | -            | +27                          | V    |       |

| V <sub>RTH</sub> /V <sub>RTL</sub>   | Transient Voltage At Pins RTH, RTL 0.0 < V <sub>2-INT</sub> < 5.5 V; V <sub>SUP</sub> $\ge$ 0.0; T < 500 ms                                                      | -0.3                     | -            | 40                           | V    |       |

| ransmitter Data                      | Pin (TX)                                                                                                                                                         | II                       |              | 11                           |      |       |

| V <sub>IH</sub>                      | High Level Input Voltage                                                                                                                                         | 0.7*V <sub>2</sub>       | -            | V <sub>2</sub> +0.3V         | V    | Τ     |

| V <sub>IL</sub>                      | Low Level Input Voltage                                                                                                                                          | -0.3                     | -            | 0.3 * V <sub>2</sub>         | V    |       |

| I <sub>TXH</sub>                     | TX High Level Input Current (V <sub>I</sub> = 4.0 V)                                                                                                             | -100                     | -50          | -25                          | μA   |       |

| I <sub>TXL</sub>                     | TX Low Level Input Current (V <sub>1</sub> = 1.0 V)                                                                                                              | -100                     | -50          | -25                          | μA   |       |

| Receive data pin                     | (rX)                                                                                                                                                             |                          |              |                              |      |       |

| V <sub>OH</sub>                      | High Level Output Voltage RX ( $I_0 = -250 \mu A$ )                                                                                                              | V <sub>2-INT</sub> - 0.9 | -            | V <sub>2-INT</sub>           | V    |       |

| V <sub>OL</sub>                      | Low Level Output Voltage (I <sub>0</sub> = 1.5 mA)                                                                                                               | 0.0                      | -            | 0.9                          | V    |       |

| CAN high and ca                      | n low pins (CANH, CANL)                                                                                                                                          | L L                      |              |                              |      |       |

| V <sub>DIFF1</sub>                   | Differential Receiver, Recessive To Dominant Threshold<br>(By Definition, V <sub>DIFF</sub> = V <sub>CANH</sub> -V <sub>CANL</sub> )<br>For 33889D<br>For 33889B | -3.5<br>-3.2             | -3.0<br>-2.6 | -2.5<br>-2.1                 | V    |       |

| V <sub>DIFF2</sub>                   | Differential Receiver, Dominant To Recessive Threshold (Bus Failures<br>1, 2, 5)<br>For 33889D<br>For 33889B                                                     | -3.5<br>-3.2             | -3.0<br>-2.6 | -2.5<br>-2.1                 | V    |       |

| V <sub>CANH</sub>                    | CANH Recessive Output Voltage<br>TX = 5.0 V; R <sub>(RTH)</sub> < 4.0 k                                                                                          | -                        | -            | 0.2                          | V    |       |

| V <sub>CANL</sub>                    | CANL Recessive Output Voltage<br>TX = 5.0 V; R <sub>(RTL)</sub> < 4.0 k                                                                                          | V <sub>2-INT</sub> - 0.2 | -            | -                            | V    |       |

Characteristics noted under conditions -  $V_{SUP}$  From 5.5 V to 18 V and  $T_J$  from -40 to 125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A$  = 25 °C under nominal conditions unless otherwise noted.

| Symbol                                 | Description                                                                                                        | Min.                 | Тур.      | Max.            | Unit | Notes |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------|-----------|-----------------|------|-------|

| V <sub>CANH</sub>                      | CANH Output Voltage, Dominant<br>TX = 0.0 V; I <sub>CANH</sub> = -40 mA; Normal Operating Mode                     | V <sub>2</sub> - 1.4 | -         | -               | V    | (19)  |

| V <sub>CANL</sub>                      | CANL Output Voltage, Dominant<br>TX = 0.0 V; I <sub>CANL</sub> = 40 mA; Normal Operating Mode                      | -                    | -         | 1.4             | V    | (19)  |

| I <sub>CANH</sub>                      | CANH Output Current (V <sub>CANH</sub> = 0; TX = 0.0)<br>For 33889D<br>For 33889B                                  | 50<br>50             | 100<br>75 | 130<br>110      | mA   |       |

| I <sub>CANL</sub>                      | CANL Output Current (V <sub>CANL</sub> = 14 V; TX = 0.0)<br>For 33889D<br>For 33889B                               | 50<br>50             | 140<br>90 | 170<br>135      | mA   |       |

| $V_{CANH}, V_{CANL}$                   | Detection Threshold For Short-circuit To Battery Voltage (Normal Mode)                                             | 7.3                  | 7.9       | 8.9             | V    |       |

| VcanH                                  | Detection Threshold For Short-circuit To Battery Voltage (Term VBAT Mode), MC33889B                                | Vsup/2+3             | -         | Vsup/2+5        | V    |       |

| VcanH                                  | Detection Threshold For Short-circuit To Battery Voltage (Term VBAT Mode), MC33889D                                | Vsup/2+3             | -         | Vsup/<br>2+4.55 | V    |       |

| I <sub>CANH</sub>                      | CANH Output Current (Term V <sub>BAT</sub> Mode; V <sub>CANH</sub> = 12 V, Failure3)                               | -                    | 5.0       | 10              | μA   |       |

| ICANL                                  | CANL Output Current (Term V <sub>BAT</sub> Mode; V <sub>CANL</sub> = 0.0 V;<br>V <sub>BAT</sub> = 12 V, Failure 4) | -                    | 0.0       | 2.0             | μΑ   |       |

| V <sub>WAKE,L</sub>                    | CANL Wake-up Voltage Threshold                                                                                     | 2.5                  | 3.0       | 3.9             | V    |       |

| V <sub>WAKE,H</sub>                    | CANH Wake-up Voltage Threshold                                                                                     | 1.2                  | 2.0       | 2.7             | V    |       |

| V <sub>WAKEL</sub> -V <sub>WAKEH</sub> | Wake-up Threshold Difference (Hysteresis)                                                                          | 0.2                  | -         | -               | V    |       |

| V <sub>SE, CANH</sub>                  | CANH Single Ended Receiver Threshold (Failures 4, 6, 7)                                                            | 1.5                  | 1.85      | 2.15            | V    |       |

| $V_{SE, CANL}$                         | CANL Single Ended Receiver Threshold (Failures 3, 8)                                                               | 2.8                  | 3.05      | 3.4             | V    |       |

| I <sub>CANL,PU</sub>                   | CANL Pull-up Current (Normal Mode)                                                                                 | 45                   | 75        | 90              | μA   |       |

| I <sub>CANH,PD</sub>                   | CANH Pull-down Current (Normal Mode)                                                                               | 45                   | 75        | 90              | μA   |       |

| R <sub>DIFF</sub>                      | Receiver Differential Input Impedance CANH / CANL                                                                  | 100                  | -         | 300             | kΩ   |       |

| V <sub>COM</sub>                       | Differential Receiver Common Mode Voltage Range                                                                    | -10                  | -         | 10              | V    | (20)  |

| C <sub>CANH</sub>                      | CANH To Ground Capacitance                                                                                         | -                    | -         | 50              | pF   |       |

| C <sub>CANL</sub>                      | CANL To Ground Capacitance                                                                                         | -                    | -         | 50              | pF   |       |

| DC <sub>CAN</sub>                      | C <sub>CANL</sub> to C <sub>CANH</sub> Capacitor Difference                                                        | -                    | -         | 10              | pF   |       |

| t <sub>CSD</sub>                       | CAN Driver Thermal Shutdown                                                                                        | 150                  | 160       | -               | °C   |       |

| R <sub>RTL</sub> | RTL to V2 Switch On Resistance<br>(I <sub>OUT</sub> < -10 mA; Normal Operating Mode)    | 10  | 30   | 90 | W  |  |

|------------------|-----------------------------------------------------------------------------------------|-----|------|----|----|--|

| R <sub>RTL</sub> | RTL to BAT Switch Series Resistance (term V <sub>BAT</sub> Mode)                        | 8.0 | 12.5 | 20 | kΩ |  |

| R <sub>RTH</sub> | RTH To Ground Switch On Resistance (I <sub>OUT</sub> < 10 mA; Normal<br>Operating Mode) | 10  | 30   | 90 | W  |  |

Notes

19. For MC33889B, after 128 pulses on TX and no bus failure.

20. Guaranteed by design

### 4.3 Dynamic electrical characteristics

#### Table 5. Dynamic electrical characteristics

$V_{SUP}$  From 5.5 V to 18 V, V2INT from 4.75 to 5.25 V and  $T_J$  from -40 to 150 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions, unless otherwise noted.

| Symbol                                  | Conditions                                                                                                                                    | Min. | Тур. | Max.     | Unit | Notes |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|-------|

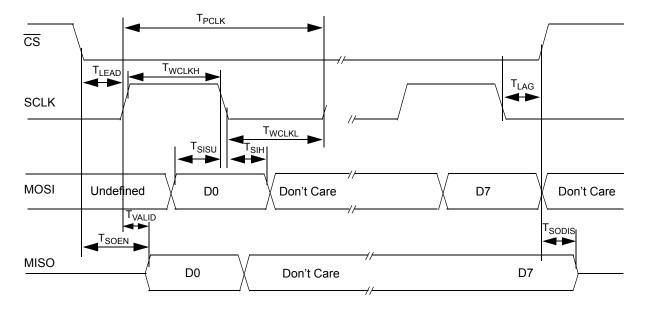

| gital interface t                       | timing (SCLK, CS, MOSI, MISO)                                                                                                                 |      |      |          |      |       |

| FREQ                                    | SPI operation frequency                                                                                                                       | -    | -    | 4.0      | MHz  |       |

| t <sub>PCLK</sub>                       | SCLK Clock Period                                                                                                                             | 250  | -    | -        | ns   |       |

| t <sub>WSCLKH</sub>                     | SCLK Clock High Time                                                                                                                          | 125  | -    | -        | ns   |       |

| t <sub>WSCLKL</sub>                     | SCLK Clock Low Time                                                                                                                           | 125  | -    | -        | ns   |       |

| t <sub>ILEAD</sub>                      | Falling Edge of CS to Rising Edge of SCLK                                                                                                     | 100  | 50   | -        | ns   |       |

| t <sub>LAG</sub>                        | Falling Edge of SCLK to Rising Edge of CS                                                                                                     | 100  | 50   | -        | ns   |       |

| t <sub>SISU</sub>                       | MOSI to Falling Edge of SCLK                                                                                                                  | 40   | 25   | -        | ns   |       |

| t <sub>SIH</sub>                        | Falling Edge of SCLK to MOSI                                                                                                                  | 40   | 25   | -        | ns   |       |

| t <sub>RSO</sub>                        | MISO Rise Time (CL = 220 pF)                                                                                                                  | -    | 25   | 50       | ns   |       |

| t <sub>fSO</sub>                        | MISO Fall Time (CL = 220 pF)                                                                                                                  | -    | 25   | 50       | ns   |       |

| t <sub>SOEN</sub><br>t <sub>SODIS</sub> | Time from Falling or Rising Edges of CS to:<br>- MISO Low-impedance<br>- MISO High-impedance                                                  | -    | -    | 50<br>50 | ns   |       |

| t <sub>VALID</sub>                      | Time from Rising Edge of SCLK to MISO Data Valid 0.2 V1 $\leq$ SO $\geq$ 0.8 V1, C <sub>L</sub> = 200 pF                                      | -    | -    | 50       | ns   |       |

| T <sub>CS-STOP</sub>                    | Delay between $\overline{\text{CS}}$ low to high transition (at end of SPI stop command) and Stop or sleep mode activation detected by V2 off | 18   | -    | 34       | μs   | (21)  |

| T <sub>INT</sub>                        | Interrupt low level duration<br>SBC in stop mode                                                                                              | 7.0  | 10   | 13       | μs   |       |

| O <sub>SC-F1</sub>                      | Internal oscillator frequency<br>All modes except Sleep and Stop                                                                              | -    | 100  | -        | kHz  | (21)  |

| O <sub>SC-F2</sub>                      | Internal low power oscillator frequency<br>Sleep and Stop modes                                                                               | -    | 100  | -        | kHz  | (21)  |

| W <sub>D1</sub>                         | Watchdog period 1<br>Normal and standby modes                                                                                                 | 8.58 | 9.75 | 10.92    | ms   |       |

| W <sub>D2</sub>                         | Watchdog period 2<br>Normal and standby modes                                                                                                 | 39.6 | 45   | 50.4     | ms   |       |

| W <sub>D3</sub>                         | Watchdog period 3<br>Normal and standby modes                                                                                                 | 88   | 100  | 112      | ms   |       |

| W <sub>D4</sub>                         | Watchdog period 4<br>Normal and standby modes                                                                                                 | 308  | 350  | 392      | ms   |       |

| F1 <sub>ACC</sub>                       | Watchdog period accuracy<br>Normal and standby modes                                                                                          | -12  | -    | 12       | %    |       |

| NR <sub>TOUT</sub>                      | Normal request mode timeout<br>Normal request mode                                                                                            | 308  | 350  | 392      | ms   |       |

| WD1 <sub>STOP</sub>                     | Watchdog period 1 - stop<br>Stop mode                                                                                                         | 6.82 | 9.75 | 12.7     | ms   |       |

| WD2 <sub>STOP</sub>                     | Watchdog period 2- stop                                                                                                                       |      |      |          | ms   |       |

Notes

21. Guaranteed by design

$V_{SUP}$  From 5.5 V to 18 V, V2INT from 4.75 to 5.25 V and  $T_J$  from -40 to 150 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25$ °C under nominal conditions, unless otherwise noted.

| Symbol               | Conditions                                                                                        | Min. | Тур. | Max. | Unit | Notes |

|----------------------|---------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| WD3 <sub>STOP</sub>  | Watchdog period 3 - stop<br>Stop mode                                                             | 70   | 100  | 130  | ms   |       |

| WD4 <sub>STOP</sub>  | Watchdog period 4 - stop<br>Stop mode                                                             | 245  | 350  | 455  | ms   |       |

| F2 <sub>ACC</sub>    | Stop mode watchdog period accuracy<br>Stop mode                                                   | -30  | -    | 30   | %    |       |

| CSFWU1               | Cyclic sense/FWU timing 1<br>Sleep and Stop modes                                                 | 3.22 | 4.6  | 5.98 | ms   |       |

| CSFWU2               | Cyclic sense/FWU timing 2<br>Sleep and Stop modes                                                 | 6.47 | 9.25 | 12   | ms   |       |

| CSFWU3               | Cyclic sense/FWU timing 3<br>Sleep and Stop modes                                                 | 12.9 | 18.5 | 24   | ms   |       |

| CSFWU4               | Cyclic sense/FWU timing 4<br>Sleep and Stop modes                                                 | 25.9 | 37   | 48.1 | ms   |       |

| CSFWU5               | Cyclic sense/FWU timing 5<br>Sleep and Stop modes                                                 | 51.8 | 74   | 96.2 | ms   |       |

| CSFWU6               | Cyclic sense/FWU timing 6<br>Sleep and Stop modes                                                 | 66.8 | 95.5 | 124  | ms   |       |

| CSFWU7               | Cyclic sense/FWU timing 7<br>Sleep and Stop modes                                                 | 134  | 191  | 248  | ms   |       |

| CSFWU8               | Cyclic sense/FWU timing 8<br>Sleep and Stop modes                                                 | 271  | 388  | 504  | ms   |       |

| t <sub>ON</sub>      | Cyclic sense On time<br>Sleep and Stop modes                                                      | 200  | 300  | 400  | μs   |       |

| t <sub>ACC</sub>     | Cyclic sense/FWU timing accuracy<br>Sleep and Stop mode                                           | -30  | -    | +30  | %    |       |

| t <sub>S-HSON</sub>  | Delay between SPI command and HS1 turn on<br>Normal or Standby mode, V <sub>SUP</sub> > 9.0 V     | -    | -    | 22   | μs   | (22)  |

| t <sub>S-HSOFF</sub> | Delay between SPI command and HS1 turn off<br>Normal or Standby mode, V <sub>SUP</sub> > 9.0 V    | -    | -    | 22   | μs   | (22)  |

| t <sub>S-V2ON</sub>  | Delay between SPI and V2 turn on<br>Standby mode                                                  | 9.0  | -    | 25   | μs   | (22)  |

| t <sub>S-V2OFF</sub> | Delay between SPI and V2 turn off<br>Normal modes                                                 | 9.0  | -    | 25   | μs   | (22)  |

| t <sub>S-NR2N</sub>  | Delay between Normal Request and Normal mode, after<br>W/D trigger command<br>Normal request mode | 15   | 35   | 70   | μs   |       |

Notes

22. State Machine Timing - Delay starts at rising edge of CS (end of SPI command) and start of Turn on or Turn off of HS1 or V2.

$V_{SUP}$  From 5.5 V to 18 V, V2INT from 4.75 to 5.25 V and  $T_J$  from -40 to 150 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions, unless otherwise noted.

| Symbol                | Conditions                                                                                                                                           | Min.       | Тур.       | Max.       | Unit | Notes |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|------|-------|

| t <sub>S-CANN</sub>   | Delay between SPI and "CAN normal mode"<br>SBC Normal mode                                                                                           | -          | -          | 10         | μs   | (23)  |

| t <sub>S-CANS</sub>   | Delay between SPI and "CAN sleep mode"<br>SBC Normal mode                                                                                            | -          | -          | 10         | μs   | (23)  |

| t <sub>₩-</sub> cs    | Delay between $\overline{CS}$ wake-up ( $\overline{CS}$ low to high) and SBC normal request mode (V <sub>DD1</sub> on & reset high) SBC in Stop mode | 15         | 40         | 90         | μs   |       |

| t <sub>W-SPI</sub>    | Delay between CS wake-up (CS low to high) and first accepted SPI command SBC in Stop mode                                                            | 90         | -          | -          | μs   |       |

| t <sub>S-1STSPI</sub> | Delay between INT pulse and 1st SPI command accepted<br>In Stop mode after wake-up                                                                   | 20         | -          | -          | μs   |       |

| t2 <sub>SPI</sub>     | Delay between two SPI messages addressing the same register<br>For 33889D only                                                                       | 25         | -          | -          | μs   |       |

| Input pins (L0 a      | nd L1)                                                                                                                                               |            |            | •          | •    | •     |

| t <sub>WUF</sub>      | Wake-up Filter Time (enable/disable option on L0 input)<br>(If filter enabled)                                                                       | 8.0        | 20         | 38         | μs   |       |

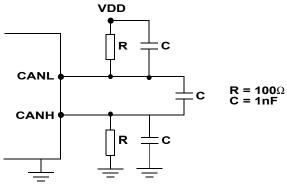

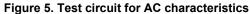

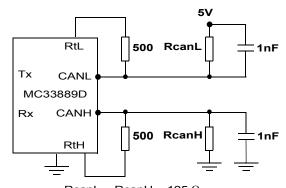

| Pin AC characte       | ristics (canh, canl, rx, tx)                                                                                                                         |            |            | •          | •    | -     |

| t <sub>SLDR</sub>     | CANL and CANH Slew Rates (25% to 75% CAN signal).<br>Recessive to Dominant state<br>Dominant to Recessive state                                      | 2.0<br>2.0 | -          | 8.0<br>9.0 | V/µs | (24)  |

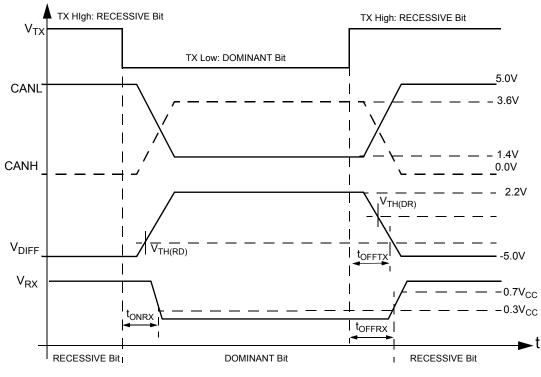

| t <sub>onrx</sub>     | Propagation Delay<br>TX to RX Low40 < T $\leq$ 25°C.<br>TX to RX Low. 25 < T < 125°C.                                                                | -          | 1.2<br>1.1 | 1.6<br>1.8 | μs   | (25)  |

| t <sub>OFFRX</sub>    | Propagation Delay TX to RX High.                                                                                                                     | -          | 1.8        | 2.2        | μs   | (25)  |

Notes

23. Guaranteed by design

24. Dominant to recessive slew rate is dependant upon the bus load characteristics.

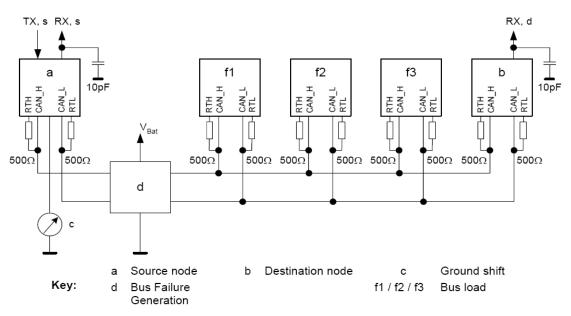

25. AC Characteristics measured according to schematic Figure 5

$V_{SUP}$  From 5.5 V to 18 V, V2INT from 4.75 to 5.25 V and  $T_J$  from -40 to 150 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions, unless otherwise noted.

| Symbol                      | Conditions                                                                                                                    | Min.     | Тур.     | Max.    | Unit | Notes |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------|----------|---------|------|-------|