# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

10 A H-bridge, SPI programmable brushed DC motor driverRev. 6.0 — 9 August 2018Data sheet: advance information

# **1** General description

The MC33HB2000 is a SMARTMOS monolithic H-Bridge Power IC, enhanced with SPI configurability and diagnostic capabilities. It is designed primarily for DC motor or servo motor control applications within the specified current and voltage limits.

The MC33HB2000 is able to control inductive loads with peak currents greater than 10 A. The nominal continuous average load current is 3.0 A. A current mirror output provides an analog feedback signal proportional to the load current.

This part is designed to specifically address the ISO 26262 safety requirements. It meets the stringent requirements of automotive applications and is fully AEC-Q100 grade 1 qualified.

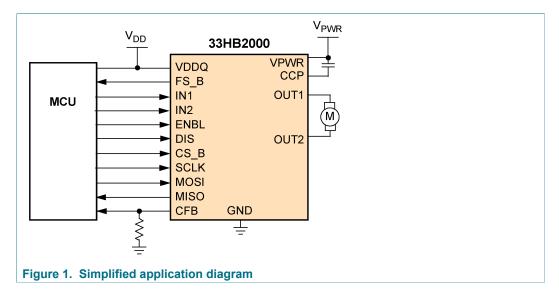

# 2 Simplified application diagram

# 3 Features and benefits

- Advanced diagnostic reporting via a serial peripheral interface (SPI): charge pump undervoltage, overvoltage, and undervoltage on VPWR, short to ground and short to VPWR for each output, open load, temperature warning and overtemperature shutdown

- Thermal management: Excellent thermal resistance of <1.0 °C/W between junction and case (exposed pad)

- Eight selectable slew rates via the SPI: 0.25 V/ $\!\mu s$  to more than 16 V/ $\!\mu s$  for EMI and thermal performance optimization

#### 10 A H-bridge, SPI programmable brushed DC motor driver

- Four selectable current limits via the SPI: 5.4/7.0/8.8/10.7 A covering a wide range of applications

- Three package sizes available in SOIC, PQFN and HVQFN to meet footprint and application requirement

- Can be operated without SPI with default slew rate of 2.0 V/ $\!\mu s$  and a 7.0 A current limit threshold

- Highly accurate real-time current feedback through a current mirror output signal with less than 5.0 % error

- Drives inductive loads in a full H-bridge or Half-bridge configuration

- Overvoltage protection places the load in high-side recirculation (braking) mode with notification in H-bridge mode

- Wide operating range: 5.0 V to 28 V operation

- Low  $R_{DS(on)}$  integrated MOSFETs: Maximum of 235 m $\Omega$  (T\_J = 150 °C) for each MOSFET

- Internal protection for overtemperature, undervoltage, and short-circuit by signaling the error condition and disabling the outputs

- I/O pins can withstand up to 36 V

- AEC-Q100 grade 1 qualified

### 4 Applications

- Electronic throttle control

- Exhaust gas recirculation control (EGR)

- · Turbo, swirl and whirl and waste flap control

- · Electric pumps, motor control and auxiliaries

### 5 Ordering information

This section describes the part numbers available to be purchased along with their differences.

#### Table 1. Orderable parts

| Part number <sup>[1]</sup> | Operating temperature                                                                                         | Package                  |

|----------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------|

| MC33HB2000EK               | T 40.00 / 405.00                                                                                              | 32-pin SOICW exposed pad |

| MC33HB2000FK               | MC33HB2000FK $T_A = -40 \text{ °C to } 125 \text{ °C}$ PC33HB2000ES $T_J = -40 \text{ °C to } 150 \text{ °C}$ | 32-pin PQFN exposed pad  |

| PC33HB2000ES               |                                                                                                               | 28-pin QFN exposed pad   |

[1] To order parts in tape and reel, add the R2 suffix to the part number.

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to <u>http://www.nxp.com</u> and perform a part number search.

# MC33HB2000

10 A H-bridge, SPI programmable brushed DC motor driver

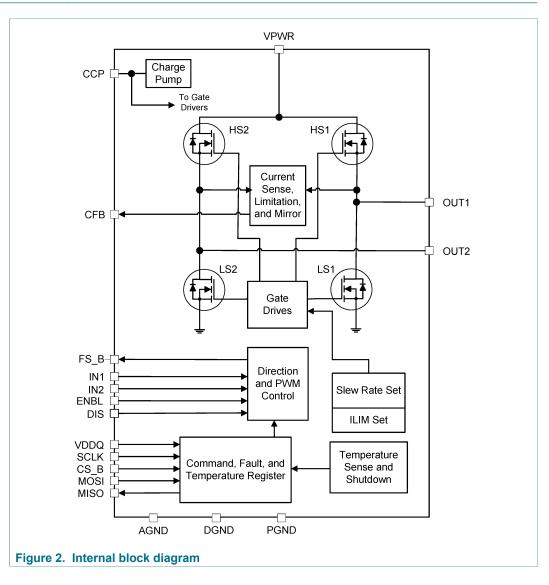

# 6 Internal block diagram

Data sheet: advance information

10 A H-bridge, SPI programmable brushed DC motor driver

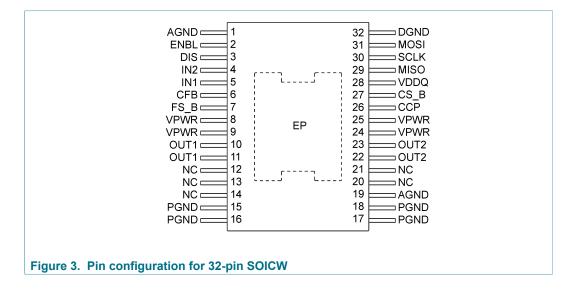

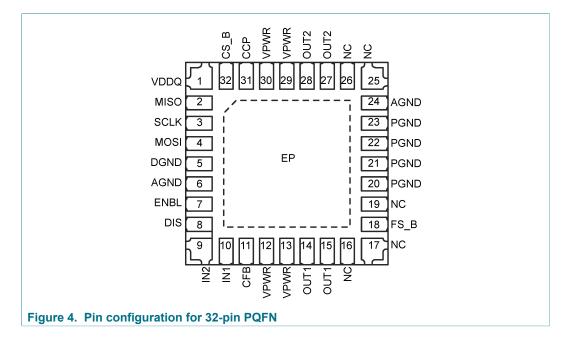

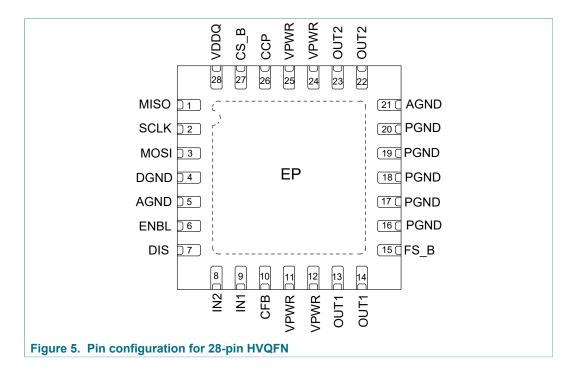

### 7 Pinning information

### 7.1 Pinning

MC33HB2000

© NXP B.V. 2018. All rights reserved.

10 A H-bridge, SPI programmable brushed DC motor driver

### 7.2 Pin description

For functional description of each pin see <u>Section 7.3 "Functional pin description"</u>.

|        | n description         |                       |                 |                 |                                                                                                                                                                     |

|--------|-----------------------|-----------------------|-----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol | 32-pin<br>SOICW       | 32-pin PQFN           | 28-pin<br>HVQFN | Pin<br>function | Definition                                                                                                                                                          |

| AGND   | 1, 19                 | 6, 24                 | 5               | GND             | Ground for analog <sup>[1]</sup>                                                                                                                                    |

| ENBL   | 2                     | 7                     | 6               | D_ln            | When ENBL is logic HIGH, the H-bridge is operational. When ENBL is logic LOW, the H-bridge outputs are tri-stated and placed in Sleep mode.                         |

| DIS    | 3                     | 8                     | 7               | D_ln            | When DIS is logic HIGH, both OUT1 and OUT2 are tri-stated                                                                                                           |

| IN2    | 4                     | 9                     | 8               | D_ln            | Logic input control of OUT2                                                                                                                                         |

| IN1    | 5                     | 10                    | 9               | D_ln            | Logic input control of OUT1                                                                                                                                         |

| CFB    | 6                     | 11                    | 10              | A_Out           | The load current feedback output provides ground referenced 0.25 % of the high-side output current.                                                                 |

| FS_B   | 7                     | 18                    | 15              | D_Out           | Open drain active LOW status flag output                                                                                                                            |

| VPWR   | 8, 9, 24, 25          | 12, 13, 29, 30        | 11, 12, 24, 25  | Supply          | These pins must be connected together physically<br>as close as possible and directly soldered down<br>to a wide, thick, low resistance supply plane on<br>the PCB. |

| OUT1   | 10, 11                | 14, 15                | 13, 14          | A_Out           | Source of HS1 and drain of LS1                                                                                                                                      |

|        | 12, 13, 14, 20,<br>21 | 16, 17, 19, 25,<br>26 | —               | NC              | No connection to die or substrate                                                                                                                                   |

#### Table 2. Pin description

мсззнв2000 Data sheet: advance information

# MC33HB2000

| Symbol | 32-pin<br>SOICW | 32-pin PQFN    | 28-pin<br>HVQFN       | Pin<br>function | Definition                                                                              |

|--------|-----------------|----------------|-----------------------|-----------------|-----------------------------------------------------------------------------------------|

| PGND   | 15, 16, 17, 18  | 20, 21, 22, 23 | 16, 17, 18, 19,<br>20 | GND             | Power ground for OUT1 and OUT2 <sup>[1]</sup>                                           |

| OUT2   | 22, 23          | 27, 28         | 22, 23                | A_Out           | Source of HS2 and drain of LS2                                                          |

| CCP    | 26              | 31             | 26                    | A_Out           | External reservoir capacitor connection for the internal charge pump; connected to VPWR |

| CS_B   | 27              | 32             | 27                    | D_In            | SPI control chip select bar input pin                                                   |

| VDDQ   | 28              | 1              | 28                    | Supply          | Logic level bias                                                                        |

| MISO   | 29              | 2              | 1                     | D_Out           | Provides digital data from HB2000 to the MCU                                            |

| SCLK   | 30              | 3              | 2                     | D_ln            | SPI control clock input pin                                                             |

| MOSI   | 31              | 4              | 3                     | D_ln            | SPI control data input pin from MCU                                                     |

| DGND   | 32              | 5              | 4                     | GND             | Ground for logic <sup>[1]</sup>                                                         |

| EP     | EP              | EP             | EP                    | GND             | Thermal exposed pad – connected to substrate <sup>[1]</sup>                             |

#### 10 A H-bridge, SPI programmable brushed DC motor driver

[1] All PGND, AGND, DGND and EP pins must be connected together with very low-impedance on the PCB.

### 7.3 Functional pin description

#### 7.3.1 Logic bias input (VDDQ)

VDDQ supplies a level shifted bias voltage for the logic level outputs designed to be read by the microprocessor/microcontroller. This pin applies the logic supply voltage to MISO making the output logic levels compliant to logic systems from 3.3 V to 5.0 V. See <u>Section 10.3 "VDDQ digital output supply voltage"</u> for more details.

#### 7.3.2 Supply voltage (VPWR)

VPWR is the power supply input for the H-bridge. The input voltage range with full performance is from 8.0 V to 28 V. In either case, the maximum allowable transient voltage during the event such as load dump is 40 V. Exceeding this limit could result in an avalanche breakdown, as discussed in <u>Section 11.3 "Output avalanche protection"</u>. A Zener clamp and/or an appropriately valued capacitor are common methods of limiting the transient. This pin must be externally protected against application of a reverse voltage through an external inverted N-channel MOSFET, diode or switched relay.

#### 7.3.3 Outputs (OUT1 and OUT2)

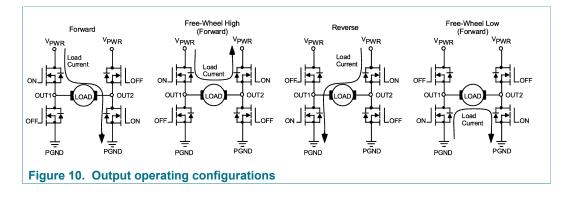

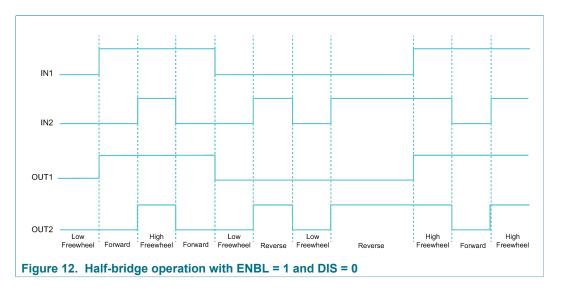

The OUT1 and OUT2 outputs drive the bi-directional DC motor. Each output has two internal N-channel MOSFETs connected in a Half-bridge configuration between VPWR and ground. Only one internal MOSFET is ON at one time for each output. The turn ON/ OFF slew times are determined by the selected SPI slew time register contents.

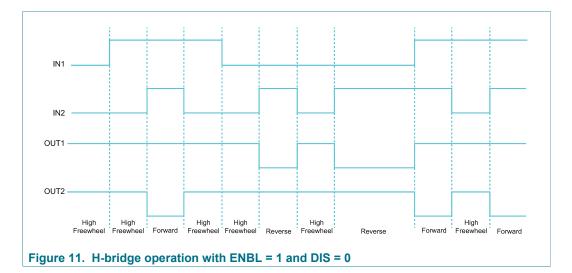

#### 7.3.4 Inputs (IN1 and IN2)

The IN1 and IN2 inputs determine the direction of current flow in the H-Bridge by directing the PWM input to one of the low-side MOSFETs (see <u>Table 21</u>). When a change in the current direction is commanded via the microprocessor/microcontroller, the PWM switches from one low-side MOSFET to the other without shoot-through current

#### 10 A H-bridge, SPI programmable brushed DC motor driver

in the H-Bridge. Both MOSFETs cannot be turned ON simultaneously in the same Halfbridge.

#### 7.3.5 Enable inputs (ENBL)

The ENBL pin at logic [0] disables all four of the output drivers (outputs tri-stated) and the part goes into Sleep mode. The ENBL pin at logic [1] enables the part functionality.

#### 7.3.6 Disable inputs (DIS)

The DIS pin at logic [1] disables all four of the output drivers (outputs tri-stated) and the part goes into Standby mode. However, it does not put the part in Sleep mode. The DIS pin is at logic [0] does not inhibit the output.

#### 7.3.7 Current recopy (CFB)

High-side FETs have a current recopy feature through an internal current-mirror which supplies 1/400th of the load current. The current recopy has better than 5.0 % accuracy for load currents between 2.0 A and 10 A. An external resistor may be connected to the CFB pin ( $R_{CFB}$ ), which sets current to voltage gain. The circuit operates properly in the presence of high-frequency noise. An external capacitor is used to provide filtering. Tie to GND through a resistor if not used.

$$V_{CFB} = \frac{I_{OUT}}{400} \times R_{CFB}$$

#### 7.3.8 Charge pump capacitor (CCP)

This pin is the charge pump output pin for connecting the external charge pump reservoir capacitor. A typical value is 100 nF. The capacitor must be connected from the CCP pin to the VPWR pin. The part does not operate properly without the external reservoir capacitor.

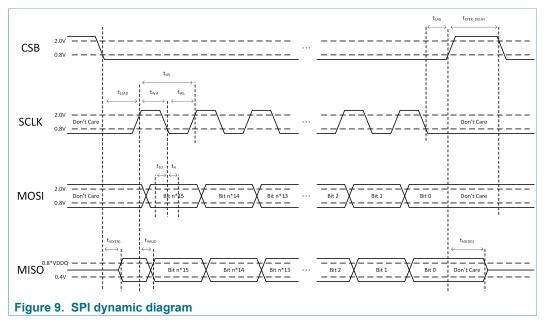

#### 7.3.9 Serial peripheral interface (SPI)

The MC33HB2000 has a serial peripheral interface consisting of Chip Select (CS\_B), Serial Clock (SCLK), Master IN Slave Out (MISO), and Master Out Slave In (MOSI). This device is configured as a SPI slave and is daisy-chainable (single CS\_B for multiple SPI slaves). See <u>Section 9.6 "16-bit SPI interface"</u> for detailed information on the SPI.

#### 7.3.9.1 Serial clock (SCLK)

The SCLK input is the clock signal input for synchronization of serial data transfer. This pin has TTL/CMOS level compatible input voltages, which allows proper operation with microprocessors using a 3.3 V to 5.0 V supply. When CS\_B is asserted low, the MOSI data reads on the SCLK falling edge and the MISO data is updated on the SCLK rising edge.

#### 7.3.9.2 Serial data output (MISO)

The MISO is the SPI data out pin. When CS\_B is asserted (low), the MSB is the first bit of the word transmitted on MISO and the LSB is the last bit of the word transmitted on

#### 10 A H-bridge, SPI programmable brushed DC motor driver

MISO. After all 16 bits of the fault register are transmitted, the MISO output sequentially transmits the digital data received on the MOSI pin. This allows the microprocessor to distinguish a shorted MOSI pin condition. The MISO output continues to transmit the input data from the MOSI input until CS\_B eventually transitions from a logic [0] to a logic [1]. The MISO output pin is in a high-impedance condition unless CS\_B is low. When active, the output is "rail to rail", depending on the voltage at the VDDQ pin.

#### 7.3.9.3 Serial data input (MOSI)

The MOSI input takes data from the microprocessor while CS\_B is asserted (low). The MSB is the first bit of each word received on MOSI and the LSB is the last bit of each word received on MOSI. The MC33HB2000 serially wraps around the MOSI input bits to the MISO output after the MISO output transmits its fault flag bits. This pin has TTL/ CMOS level compatible input voltages, allowing proper operation with microprocessors using a 3.3 V to 5.0 V supply.

#### 7.3.9.4 Chip select (CS\_B)

The CS\_B input selects this device for serial transfers. The SPI applies the contents of the I/O register when CS\_B rises. When CS\_B falls, the I/O register is loaded with the contents of the previously addressed register. This pin has TTL/CMOS level compatible input voltages, which allows proper operation with microprocessors using a 3.3 V to 5.0 V supply.

#### 7.3.10 Status fault (FS\_B)

This pin is the device fault status output which signals the MCU of any fault. The fault status pin goes low to report system status according to the bits selected in the Fault Status Mask register as explained in <u>Table 15</u>. This output is active LOW open drain structure, which requires a pull-up resistor to VDD. For more details on this pin, see <u>Table 21</u>.

## 8 General product characteristics

#### 8.1 Maximum ratings

#### Table 3. Maximum ratings

All voltages are with respect to ground, unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol            | Description (Rating)      | Min. | Max.                  | Unit |

|-------------------|---------------------------|------|-----------------------|------|

| SUPPLY            |                           |      | 1                     |      |

| V <sub>PWR</sub>  | Supply voltage (VPWR)     | -0.3 | 40                    | V    |

| V <sub>DDQ</sub>  | Logic bias input (VDDQ)   | -0.3 | 36                    | V    |

| V <sub>AGND</sub> | Analog ground (AGND)      | -0.3 | 0.3                   | V    |

| V <sub>DGND</sub> | Digital ground (DGND)     | -0.3 | 0.3                   | V    |

| V <sub>PGND</sub> | Power ground (PGND)       | -0.3 | 0.3                   | V    |

| CHARGE I          | PUMP                      |      |                       |      |

| V <sub>CCP</sub>  | Charge pump (CCP) voltage | -0.3 | V <sub>PWR</sub> + 12 | V    |

| DIGITAL I/        | 0                         |      |                       |      |

| V <sub>IN1</sub>  | Input 1 (IN1) voltage     | -0.3 | 36                    | V    |

# MC33HB2000

### 10 A H-bridge, SPI programmable brushed DC motor driver

| Symbol                                     | Description (Rating)                                                                                                   | Min.        | Max.                   | Unit |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------|------------------------|------|

| V <sub>IN2</sub>                           | Input 2 (IN2) voltage                                                                                                  | -0.3        | 36                     | V    |

| V <sub>DIS</sub>                           | Disable (DIS) voltage                                                                                                  | -0.3        | 36                     | V    |

| V <sub>ENBL</sub>                          | Enable (ENBL) voltage                                                                                                  | -0.3        | 36                     | V    |

| V <sub>FS_B</sub>                          | Status flag (FS_B) voltage                                                                                             | -0.3        | 36                     | V    |

| SPI                                        |                                                                                                                        |             |                        |      |

| V <sub>MISO</sub>                          | Serial data output (MISO) voltage                                                                                      | -0.3        | V <sub>DDQ</sub> + 0.3 | V    |

| V <sub>MOSI</sub>                          | Serial data input (MOSI) voltage                                                                                       | -0.3        | 36                     | V    |

| V <sub>CSB</sub>                           | Chip select (CS_B) voltage                                                                                             | -0.3        | 36                     | V    |

| V <sub>SCLK</sub>                          | Serial clock (SCLK)                                                                                                    | -0.3        | 36                     | V    |

| OUTPUTS                                    |                                                                                                                        | I           |                        |      |

| V <sub>OUTX</sub>                          | OUT1 and OUT2 voltage                                                                                                  | -0.3        | V <sub>PWR</sub> + 2.0 | V    |

| V <sub>CFB</sub>                           | Current recopy (CFB)                                                                                                   | -0.3        | 30                     | V    |

| CURRENT                                    | S                                                                                                                      |             | I                      |      |

| I <sub>POUTX</sub>                         | OUTx peak current<br>Transient current (< 5.0 ms) T <sub>J</sub> ≤ 150 °C                                              | _           | 16                     | A    |

| I <sub>CLAMP</sub>                         | Digital pin current in clamping mode<br>ENBL, DIS, MOSI, CS_B, SCLK, IN1, IN2                                          | -3.0        | 3.0                    | mA   |

| ESD PRO                                    | TECTION                                                                                                                |             |                        |      |

| V <sub>ESD_A1</sub><br>V <sub>ESD_G1</sub> | ESD Voltage<br>Human Body Model (HBM)<br>Local pins, all pins except VPWR, OUT1, OUT2<br>Global pins: VPWR, OUT1, OUT2 | [1] [2]<br> | ±2000<br>±4000         | V    |

|                                            | Charge Device Model (CDM)                                                                                              |             |                        |      |

| V <sub>ESD_A2</sub>                        | All pins                                                                                                               | <u> </u>    | ±500                   |      |

| V <sub>ESD_C2</sub>                        | Corners pins                                                                                                           |             | ±750                   |      |

| V <sub>ESD_C2</sub>                        | Machine Model                                                                                                          |             |                        |      |

|                                            | All pins                                                                                                               | —           | ±200                   |      |

Human body model: AEC-Q100

Charged Device model and Machine model: AEC-Q100 Rev H

### 8.2 Thermal characteristics

| Symbol            | Description (Rating)                                             |         | Min. | Max. | Unit |

|-------------------|------------------------------------------------------------------|---------|------|------|------|

| THERMAL           | RATINGS                                                          |         | 1    | l    |      |

|                   | Operational junction temperature                                 |         |      |      |      |

| TJ                | Continuous                                                       |         | -40  | 150  | °C   |

|                   | Transient                                                        |         | -40  | 195  |      |

| T <sub>A</sub>    | Operational ambient temperature                                  | [1]     | -40  | 125  | °C   |

| T <sub>STG</sub>  | Storage temperature                                              |         | -65  | 150  | °C   |

| T <sub>PPRT</sub> | Peak package reflow temperature during reflow                    | [2] [3] | —    | —    | °C   |

| мсззнв20          | 000EK THERMAL RESISTANCE AND PACKAGE DISSIPATION RATIN           | IGS     |      |      |      |

| R <sub>OJA</sub>  | Junction to ambient natural convection - single layer board (1s) | [4] [5] | _    | 75.7 | °C/W |

| R <sub>ØJA</sub>  | Junction to ambient natural convection – four layer board (2s2p) | [4] [5] | _    | 23.9 | °C/W |

Data sheet: advance information

# MC33HB2000

#### 10 A H-bridge, SPI programmable brushed DC motor driver

| Symbol                 | Description (Rating)                                             |         | Min. | Max.  | Unit |

|------------------------|------------------------------------------------------------------|---------|------|-------|------|

| R <sub>OJB</sub>       | Junction to board                                                | [6]     | —    | 7.1   | °C/W |

| R <sub>ØJCBOTTOM</sub> | Junction to case (bottom)                                        | [7]     | —    | 0.66  | °C/W |

| $\Psi_{JT}$            | Junction to package top – natural convection                     | [8]     | —    | 2.97  | °C/W |

| MC33HB2000             | DES THERMAL RESISTANCE AND PACKAGE DISSIPATION RAT               | INGS    | 1    |       |      |

| R <sub>OJA</sub>       | Junction to ambient natural convection – single layer board (1s) | [4] [5] | _    | 88.9  | °C/W |

| R <sub>OJA</sub>       | Junction to ambient natural convection – four layer board (2s2p) | [4] [5] | —    | 31.9  | °C/W |

| R <sub>OJMA</sub>      | Junction to ambient (@200 ft/min) – single layer board (1s)      | [4] [9] | —    | 73.1  | °C/W |

| R <sub>OJMA</sub>      | Junction to ambient (@200 ft/min) – four layer board (2s2p)      | [4] [9] | —    | 26.2  | °C/W |

| R <sub>OJB</sub>       | Junction to board                                                | [6]     | —    | 11.9  | °C/W |

| R <sub>ØJCBOTTOM</sub> | Junction to case (bottom)                                        | [7]     | —    | 1.07  | °C/W |

| $\Psi_{JT}$            | Junction to package top – natural convection                     | [8]     | —    | 1.45  | °C/W |

| MC33HB2000             | OFK THERMAL RESISTANCE AND PACKAGE DISSIPATION RAT               | INGS    |      | I     | I    |

| R <sub>OJA</sub>       | Junction to ambient natural convection – single layer board (1s) | [4] [5] | —    | 63.4  | °C/W |

| R <sub>OJA</sub>       | Junction to ambient natural convection – four layer board (2s2p) | [4] [5] | —    | 21.55 | °C/W |

| R <sub>OJB</sub>       | Junction to board                                                | [6]     | —    | 6.41  | °C/W |

| R <sub>ØJCBOTTOM</sub> | Junction to case (bottom)                                        | [7]     | —    | 0.61  | °C/W |

| $\Psi_{JT}$            | Junction to package top – natural convection                     | [8]     | —    | 2.6   | °C/W |

[1] The circuit specification describes IC operation within the parametric operating range defined in the electrical characteristic table.

[2] Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

[3] NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), go to nxp.com, search by part number. Remove prefixes/suffixes and enter the core ID to view all orderable parts (for MC33xxxD enter 33xxx), and review parametrics.

[4] Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

[5] Per JEDEC JESD51-2 with natural convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

[6] Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

[7] Thermal resistance between the die and the solder pad on the bottom of the package. Interface resistance is ignored.

[8] Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters (Ψ) are not available, the thermal characterization parameter is written as Psi-JT.

[9] Per JEDEC JESD51-6 with forced convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

### 8.3 Operating conditions

This section describes the operating conditions of the device. Conditions apply to the following data, unless otherwise noted.

#### Table 5. Nominal operation

Within the range of functionality, all functionalities have to be guaranteed. All voltages refer to GND. Currents are positive into and negative out of the specified pin.  $T_J = -40$  °C to 150 °C, unless otherwise specified.

| Symbol           | Description (Rating)                           | Min. | Max. | Unit |  |

|------------------|------------------------------------------------|------|------|------|--|

| SUPPLY VOLTAGE   |                                                |      |      |      |  |

| V <sub>PWR</sub> | Functional operating supply voltage range—VPWR | 5.0  | 28   | V    |  |

| SPI              |                                                |      |      |      |  |

| f <sub>SPI</sub> | SPI frequency range                            | 0.5  | 10   | MHz  |  |

#### 10 A H-bridge, SPI programmable brushed DC motor driver

#### Table 6. Supply current consumption

$V_{PWR}$  = 5.0 V to 28 V,  $T_{J}$  = -40 °C to 150 °C, unless otherwise specified.

| Symbol                   | Description (Rating)                                                                                    |     | Min.    | Max. | Unit |

|--------------------------|---------------------------------------------------------------------------------------------------------|-----|---------|------|------|

| VPWR SUPP                | LY CURRENT CONSUMPTIONS                                                                                 |     |         |      |      |

| I <sub>VPWR</sub>        | Operating mode—V <sub>PWR</sub>                                                                         | [1] | —       | 20   | mA   |

| I <sub>VPWR(SLEEP)</sub> | Sleep mode, measured at V <sub>PWR</sub> = 12 V                                                         | [2] | —       | 50   | μA   |

| LEAKAGE C                | URRENTS FOR THE FUNCTIONS CONNECTED TO VPWR                                                             |     |         |      |      |

| I <sub>OUTLEAK</sub>     | Output leakage current, outputs off, VPWR = 28 V<br>V <sub>OUTx</sub> = VPWR<br>V <sub>OUTx</sub> = GND |     | <br>-60 | 100  | μΑ   |

[1]

ENBL = Logic [1], I<sub>OUT</sub> = 0 A ENBL = Logic[0], DIS = Logic[1] and I<sub>OUT</sub> = 0 A [2]

#### 8.3.1 Reverse battery

To protect against a reverse battery condition, a dedicated device to block reverse current must be populated in the application, as shown in Figure 22 (with a diode).

Some applications require operation at very low battery voltages (start-stop applications), and many systems have multiple H-bridges in parallel, which require high current reverse battery protection with very low voltage drops during the operation. In such applications, an external, reverse-polarity, FET may be used instead of the reverse protection diode, to lower the voltage drop from battery to VPWR pins. The CCP pin can be used to bias the gate of an N-channel FET, provided the bias current requirement is less than 20 µA. In Figure 23, the NPN transistor is used for fast response of the N-Channel FET during turnoff.

#### 8.3.2 Digital I/Os characteristics

#### Table 7. Digital I/Os characteristics

$V_{PWR}$  = 5.0 V to 28 V,  $T_J$  = -40 °C to 150 °C, unless otherwise specified.

| Symbol               | Parameter                                             | Min.                 | Max. | Unit |

|----------------------|-------------------------------------------------------|----------------------|------|------|

| DIGITAL IN           | IPUTS                                                 | l.                   |      |      |

| V <sub>IH_X</sub>    | Input high-voltage                                    | 2.0                  | —    | V    |

| V <sub>IL_X</sub>    | Input low-voltage                                     |                      | 0.8  | V    |

| V <sub>HYS_X</sub>   | Input voltage threshold hysteresis                    | 100                  | —    | mV   |

| R <sub>PD_X</sub>    | Input pull-down resistance—MOSI, SCLK, ENBL, IN1, IN2 | 40                   | 175  | kΩ   |

| R <sub>PU_X</sub>    | DIS, CS_B Input pull-up resistance to 5.0 V           | 40                   | 175  | kΩ   |

| C <sub>IN</sub>      | Input capacitance                                     | —                    | 12   | pF   |

| DIGITAL O            | UTPUTS                                                |                      |      |      |

| V <sub>OH_X</sub>    | MISO output high-voltage, with -1.0 mA                | $0.8 \times V_{DDQ}$ | _    | V    |

| V <sub>OL_X</sub>    | MISO output low-voltage, with 1.0 mA                  | —                    | 0.4  | V    |

| I <sub>MISO_LK</sub> | MISO tri-state leakage current                        | -10                  | 10   | μA   |

| V <sub>OL_FS_B</sub> | FS_B low-voltage, with 1.0 mA                         | —                    | 0.4  | V    |

| R <sub>PU_FS_B</sub> | FS_B output pull-up resistance to 5.0 V               | 100                  | 500  | kΩ   |

10 A H-bridge, SPI programmable brushed DC motor driver

# 9 General IC functional description and application information

### 9.1 Introduction

The MC33HB2000 is a programmable H-bridge, power integrated circuit (IC) designed to drive DC motors or bi-directional solenoid controlled actuators, such as throttle control or exhaust gas recirculation actuators. It is particularly well suited for the harsh environment found in automotive power train systems. The MC33HB2000 is designed to specifically address the ISO 26262 safety standard requirements. The key characteristic of this versatile driver is configurability. The selectable slew rate permits the customer to choose the slew rate needed for performance and noise suppression. The Serial Peripheral Interface (SPI) allows the system microprocessor to clear the fault register, select a programmable current limit, and select the slew rate.

The MC33HB2000 is designed to drive a bi-directional DC motor using pulse-width modulation (PWM) for speed and torque control. A current mirror output provides an analog feedback signal proportional to the load current. SPI diagnostic reporting includes, open load, short-to-battery, short-to-ground, die temperature range, overvoltage, and undervoltage.

### 9.2 Features

- Advanced diagnostic reporting via the serial peripheral interface (SPI)

- Charge pump undervoltage

- Overvoltage and undervoltage on VPWR

- Short to ground as well as short to VPWR for each output

- Open load

- Temperature warning

- Overtemperature shutdown

- Excellent thermal resistance of <1.0 °C/W between junction and case (exposed pad)

- Eight selectable slew rates via the SPI from 0.25 V/µs to more than 16 V/µs, giving the user flexibility to perform trade-offs between low EMI and better thermal performance

- Active current limiting with four selectable current limits via the SPI: 5.4/7.0/8.8/10.7 A covering a wide range of applications

- Can be operated without SPI with default slew rate of 2.0 V/µs and a 7.0 A current limit threshold. See <u>Figure 22</u> for operation without SPI.

- Efficient thermal management scheme by reducing the switching losses to ensure continuous operation and availability of the part under harsh operating conditions

- Accurate real-time current feedback through a current mirror output signal with less than 5.0 % error

- Configurable for full H-bridge or Half-bridge operation through the SPI

- Overvoltage protection places the load in high-side recirculation (braking) mode and signal the error condition in H-bridge mode

- Wide operating range: 5.0 V to 28 V operation

- Low R<sub>DS(on)</sub> integrated MOSFETs: Maximum 235 m $\Omega$  (T<sub>J</sub> = 150 °C) for each MOSFET

- Internal protection for short-circuit, overtemperature, and undervoltage by signaling the error condition and disabling the outputs

- I/O pins can withstand up to 36 V

#### 10 A H-bridge, SPI programmable brushed DC motor driver

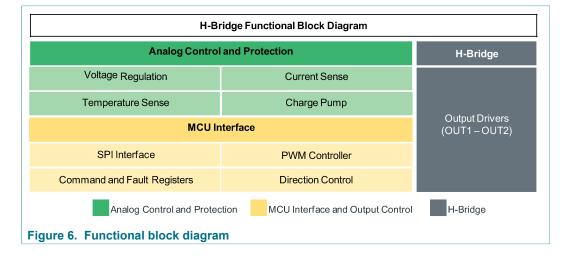

### 9.3 Functional block diagram

### 9.4 Functional description

#### 9.4.1 H-bridge output drivers (OUT1 and OUT2)

The MC33HB2000 power IC provides the means to efficiently drive a DC motor in both forward and reverse shaft rotation via a monolithic H-bridge comprising low  $R_{DS(on)}$  N-channel MOSFETs and integrated control circuitry. The switching action of the H-bridge can be pulse-width modulated to obtain both torque and speed control, with slew rates selectable from 0.25 V/µs to 16 V/µs in eight steps, giving the user flexibility to perform trade offs between meeting the EMI requirements and minimize switching losses. The outputs comprise four power MOSFETs configured as a standard H-bridge, controlled by the IN1 and IN2 inputs.

#### 9.4.2 Analog control, protection, and diagnostics

The MC33HB2000 has integrated voltage regulators supplying the logic and protection functions internally. This reduces the requirements for external supplies and insures the device is safely controlled at all times when battery voltage is applied. An integrated charge pump provides the required bias levels to insure the output MOSFETs turn fully ON when commanded. Each MOSFET provides feedback to the protection circuitry by way of a current sensor. Each sense signal is compared with programmable overcurrent levels and produces an immediate shutdown in case of a high current short-circuit. The high-side current sense is also used for producing a current limiting PWM to reduce overload conditions as determined by the programmable limits. The high-side current sense is available to the MCU as an analog current proportional to the load current.

Each MOSFET has overtemperature protection circuitry disabling the device. A thermal warning sets a flag in the SPI register when the device is approaching a protection limit. A thermal management scheme decreases the current limiting PWM frequency, while keeping the average current at the selected limit.

The MC33HB2000 consists of advanced diagnostics and protection features such as open load detection, overvoltage sense and protection, undervoltage protection, or charge pump undervoltage detection.

MC33HB2000

© NXP B.V. 2018. All rights reserved.

#### 10 A H-bridge, SPI programmable brushed DC motor driver

#### 9.4.3 MCU interface and output control

The SPI and control logic signals are compatible with both 5.0 V and 3.3 V logic systems. The SPI provides an easy to configure interface for the MCU through programmable control of output slew rates, current limits, enabling/disabling of outputs, SPI equivalent of inputs (VIN1 and VIN2), and mode of operation (H-bridge/half-bridge). The status register makes detailed diagnostics available for protective and warning functions. The output drivers are controlled by the input signals ENBL, DIS, IN1, and IN2 using the parallel inputs and VIN1, VIN2, as well as EN using the SPI control.

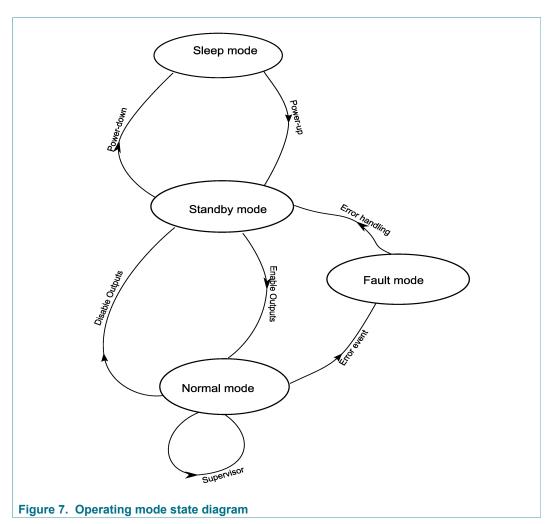

### 9.5 Modes of operation

#### 9.5.1 Description

The operating modes are:

Sleep mode

All MC33HB2000 functions are disabled. The current consumption does not exceed the sleep-state current specification.

Standby mode

All MC33HB2000 logic are fully operational with the outputs in a high-impedance state.

Normal mode

All MC33HB2000 functions are fully operational. Any detected faults transition the device to Fault mode.

• Fault mode

Certain of functions are forced off and FS\_B signal is latched to logic [0] indicating a fault.

10 A H-bridge, SPI programmable brushed DC motor driver

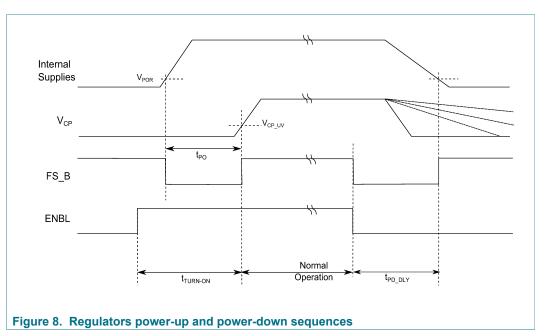

The MC33HB2000 wakes up by EN going to a logic high state. If a valid wake-up event occurs while the  $V_{PWR}$  voltage level is above the specified threshold, the regulators power-up sequence is initiated as illustrated in Figure 8.

Data sheet: advance information

# MC33HB2000

10 A H-bridge, SPI programmable brushed DC motor driver

On Power-up, Fault Status (FS\_B) activates after the internal supplies reach their operating threshold. All regulators acquire their steady-state by the turn-on delay time ( $t_{TURN-ON}$ ). On power-up, FS\_B is active for at least  $t_{PO}$ , and then deactivates after  $V_{CP}$  is greater than the undervoltage threshold ( $V_{CP\_UV}$ ) and all faults are clear. When ENBL transitions to logic LOW, the outputs turn off (high-impedance state) and FS\_B goes low. Power-down starts  $t_{PD\_DLY}$  after ENBL goes low. DIS must also be low for FS\_B to deactivate. On Power-down, FS B is activated until the internal supplies are disabled.

#### 9.5.2 Electrical characteristics

#### Table 8. Electrical characteristics

$V_{PWR}$  = 5.0 V to 28 V,  $T_J$  = -40 °C to 150 °C, unless otherwise specified.

| Symbol               | Characteristic                                                                      | Min. | Тур. | Max. | Unit |

|----------------------|-------------------------------------------------------------------------------------|------|------|------|------|

| Wake-up              |                                                                                     |      |      |      |      |

| t <sub>TURN-ON</sub> | Turn-on delay time. Time from ENBL going high to FS_B <sup>[1]</sup> returning high |      | —    | 1.0  | ms   |

| t <sub>PO</sub>      | Turn-on Status time. Minimum pulse width on FS_B during power up                    | 1.0  | —    | 2.0  | μs   |

| t <sub>PD_DLY</sub>  | Turn-off delay time. ENBL going low until FS_B is allowed to go high                | 8.0  | —    | 11   | μs   |

[1] ENBL is a digital input and has the characteristics defined in <u>Table 7</u>.

Data sheet: advance information

10 A H-bridge, SPI programmable brushed DC motor driver

### 9.6 16-bit SPI interface

#### 9.6.1 Description

The Serial Peripheral Interface (SPI) has the following features:

- Full duplex, 4-wire synchronous communication

- · Slave mode operation only

- · Fixed SCLK polarity and phase requirements

- Fixed 16-bit command word

- SCLK operation up to 10 MHz

The SPI communication works as follows:

SPI communication is "MSB first" and is composed of 16 SCLK cycles. The MOSI data is read on SCLK falling edge and the MISO data is updated on SCLK rising edge. The daisy-chain feature passes data in excess of 16 bits to the next device in line. If the number of clock pulses within CS\_B low is not more than 0 and an integer multiple of 16, the current SPI communication is ignored and a framing error is recorded in the status register. Both the serial input and the serial output data are valid on the SCLK falling edge, and transitions on the rising edge of SCLK.

The content reported by the MC33HB2000 is the previous selected register address at the time CS\_B goes low. On the first SPI communication after enable goes high, the first register sent on the MISO line is the status register. When addressing a READ register, the content bits are ignored. See <u>Table 9</u> for detail on timing parameters.

#### Note:

It is recommended to use good programming practices incorporating writes to SPI registers, immediately verified by reads to the registers. This ensures a reliable communication between MCU and the device. MCU is responsible for detecting any malfunction in the communication that may come up due to hardware or software failure.

#### 10 A H-bridge, SPI programmable brushed DC motor driver

#### 9.6.2 Electrical characteristics

#### Table 9. Electrical characteristics

$V_{DDQ}$  = 3.13 V to 5.25 V,  $T_J$  = -40 °C to 150 °C, unless otherwise specified.

| Symbol                  | Characteristic                                                                                          | Min. | Тур.                | Max. | Unit |

|-------------------------|---------------------------------------------------------------------------------------------------------|------|---------------------|------|------|

| SPI INTERFA             | ACE TIMING                                                                                              |      |                     |      |      |

| f <sub>SPI</sub>        | Recommended frequency of SPI operation, $t_{SPI} = 1/f_{SPI}$                                           | 0.5  | —                   | 10   | MHz  |

| t <sub>LEAD</sub>       | Falling edge of CS_B to rising edge of SCLK (required setup time)                                       | 30   | —                   | —    | ns   |

| t <sub>LAG</sub>        | Falling edge of SCLK to rising edge of CS_B (required setup time)                                       | 30   |                     |      | ns   |

| t <sub>XFER_DELAY</sub> | No data time between SPI commands                                                                       | 300  | _                   |      | ns   |

| t <sub>WH</sub>         | High time of SCLK                                                                                       | 45   | t <sub>SPI/</sub> 2 | _    | ns   |

| t <sub>WL</sub>         | Low time of SCLK                                                                                        | 45   | t <sub>SPI/</sub> 2 | _    | ns   |

| t <sub>SU</sub>         | MOSI to SCLK falling edge (required setup time)                                                         | 15   | _                   | —    | ns   |

| t <sub>SO(EN)</sub>     | Time from falling edge of CS_B to MISO low-impedance                                                    | —    | _                   | 30   | ns   |

| t <sub>SO(DIS)</sub>    | Time from rising edge of CS_B to MISO high-impedance                                                    | —    | _                   | 30   | ns   |

| t <sub>VALID</sub>      | Time from rising edge of SCLK to MISO data valid, $V_{DDQ}$ = 5.0 V, 1.0 V ≤ MISO ≤ 4.0 V, CL = 50 pF   | _    | —                   | 30   | ns   |

| t <sub>VALID</sub>      | Time from rising edge of SCLK to MISO data valid, $V_{DDQ}$ = 3.3 V, 0.66 V ≤ MISO ≤ 2.64 V, CL = 50 pF |      |                     | 45   | ns   |

| t <sub>H</sub>          | SCLK falling edge to MOSI (required hold time)                                                          | 30   | _                   |      | ns   |

#### 9.6.3 SPI fault reporting

The MC33HB2000 has an advanced SPI fault reporting and error detection feature. The fault status register latches a fault at the time a fault is detected.

#### 9.6.3.1 Clearing the fault status

The fault status is cleared when the fault is no longer present and one of three events occurs, this is referred to as "clr\_flt" throughout this document.

| Symbol                | Characteristic                                                                                                                   | Min. | Тур. | Max. | Unit |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>DIS_MIN</sub>  | The falling edge of a logic signal on DIS clears non-<br>active faults. Minimum pulse width to ensure the faults<br>are cleared. | _    | —    | 1.0  | μs   |

| t <sub>ENBL_MIN</sub> | The rising edge of a logic signal on ENBL clears non-<br>active faults. Minimum pulse width to ensure the faults<br>are cleared. | -    | —    | 1.0  | μs   |

|                       | A write to the status register selectively clears fault status with a '1' in this bit location.                                  |      |      |      |      |

#### 9.6.3.2 SPI framing error detection

A SPI Framing error is recorded if either of the following two conditions are met:

#### 10 A H-bridge, SPI programmable brushed DC motor driver

- The number of clock pulses within CS\_B low is not more than 0 and an integer multiple of 16

- Register 00 is addressed for a Write operation

#### 9.6.4 SPI mapping

Bit 15 is 1 for a Write operation and 0 for a Read operation. A write to the status register selectively clears the fault status with a '1' in this bit location, unless the fault is still present.

#### Table 11. SPI register selection

| 14 | 13 | Register                         |

|----|----|----------------------------------|

| 0  | 0  | Device Identification (Reserved) |

| 0  | 1  | Status                           |

| 1  | 0  | Fault Status Mask                |

| 1  | 1  | Configuration and Control        |

#### Table 12. Device identification (Reserved)

| Bit  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|------|----|----|----|----|----|----|---|---|---|---|---|---|-----|-----|-----|-----|

| Read | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 1 | RV3 | RV2 | RV1 | RV0 |

RV0-RV3 reserved bits. Bit 4 is the device identifier.

#### Table 13. Status

| Bit                 | 15 | 14 | 13 | 12 | 11  | 10   | 9  | 8  | 7    | 6    | 5    | 4    | 3  | 2  | 1  | 0  |

|---------------------|----|----|----|----|-----|------|----|----|------|------|------|------|----|----|----|----|

| Name                | —  | _  | _  | —  | FRM | CP_U | UV | OV | SCP2 | SCP1 | SCG2 | SCG1 | OL | OC | TW | OT |

| Read <sup>[1]</sup> | 0  | 0  | 1  | 0  | 0   | 0    | 0  | 0  | 0    | 0    | 0    | 0    | 0  | 0  | 0  | 0  |

| Write               | 1  | 0  | 1  | 0  | Х   | Х    | Х  | Х  | Х    | Х    | Х    | Х    | Х  | х  | х  | Х  |

[1] The default value for all bits (bit 0 to bit 11) in status register is 0 if no fault is detected in the device.

#### Table 14. Status bits description

| Bit | Bit name | Description                      |

|-----|----------|----------------------------------|

| 15  |          | —                                |

| 14  |          | -                                |

| 13  | —        | -                                |

| 12  |          | -                                |

| 11  | FRM      | SPI framing error                |

| 10  | CP_U     | Charge pump undervoltage         |

| 9   | UV       | VPWR undervoltage                |

| 8   | OV       | VPWR overvoltage                 |

| 7   | SCP2     | Short-circuit to power output 2  |

| 6   | SCP1     | Short-circuit to power output 1  |

| 5   | SCG2     | Short-circuit to ground output 2 |

MC33HB2000

© NXP B.V. 2018. All rights reserved.

# MC33HB2000

#### 10 A H-bridge, SPI programmable brushed DC motor driver

| Bit | Bit name | Description                                    |

|-----|----------|------------------------------------------------|

| 4   | SCG1     | Short-circuit to ground output 1               |

| 3   | OL       | Open load                                      |

| 2   | OC       | Overcurrent - current limit has been activated |

| 1   | TW       | Thermal warning                                |

| 0   | ОТ       | Overtemperature shutdown                       |

#### Table 15. Fault status mask

| Bit                 | 15 | 14 | 13 | 12  | 11  | 10   | 9  | 8  | 7    | 6    | 5    | 4    | 3  | 2  | 1  | 0  |

|---------------------|----|----|----|-----|-----|------|----|----|------|------|------|------|----|----|----|----|

| Name                | _  | _  | —  | DOV | FRM | CP_U | UV | ov | SCP2 | SCP1 | SCG2 | SCG1 | OL | OC | τw | ОТ |

| Read <sup>[1]</sup> | 0  | 1  | 0  | 0   | 0   | 1    | 1  | 0  | 1    | 1    | 1    | 1    | 0  | 0  | 0  | 1  |

| Write               | 1  | 1  | 0  | 0   | Х   | Х    | Х  | Х  | Х    | Х    | Х    | Х    | Х  | Х  | Х  | Х  |

[1] The SPI bits in "Read" section show the default values.

The mask bits are in the same order as the Status bits. A '1' causes the FS\_B to become active when this fault is active.

Bit 12 (DOV - Disable overvoltage) configures the response to an overvoltage condition:

- 1 = Disable overvoltage protection (OV bit is warning only)

- 0 = Enable overvoltage protection in Full Bridge mode

#### Table 16. Configuration and control

| Bit                 | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8    | 7   | 6   | 5   | 4  | 3    | 2     | 1    | 0    |

|---------------------|----|----|----|----|----|----|------|------|-----|-----|-----|----|------|-------|------|------|

| Name                | —  | —  | —  | CL | тм | AL | ILM1 | ILM0 | SR2 | SR1 | SR0 | EN | MODE | INPUT | VIN2 | VIN1 |

| Read <sup>[1]</sup> | 0  | 1  | 1  | 0  | 1  | 1  | 0    | 1    | 1   | 0   | 0   | 1  | 1    | 0     | 0    | 0    |

| Write               | 1  | 1  | 1  | Х  | Х  | Х  | Х    | Х    | Х   | Х   | Х   | Х  | Х    | Х     | Х    | Х    |

[1] The SPI bits in "Read" section show the default values.

#### Table 17. Configuration and control bits description

| Bit | Bit name | Description                                                                                                                                                                                                                                                                         |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | —        | —                                                                                                                                                                                                                                                                                   |

| 14  | —        | —                                                                                                                                                                                                                                                                                   |

| 13  | —        | _                                                                                                                                                                                                                                                                                   |

| 12  | CL       | <ul> <li>Check for open load (in Full Bridge Standby mode)</li> <li>1 = Enabled on transition from Standby to Normal mode. Execute test in Standby on transition to 1</li> <li>0 = Disable test</li> </ul>                                                                          |

| 11  | ТМ       | <ul> <li>Thermal Management mode</li> <li>1 = Enable change of current limit frequency by control of t<sub>B</sub> when OT<sub>W</sub> state</li> <li>0 = Disable change of current limit frequency by OT<sub>W</sub>, t<sub>B</sub> shall be set to the slowest setting</li> </ul> |

# MC33HB2000

#### 10 A H-bridge, SPI programmable brushed DC motor driver

| Bit | Bit name | Description                                                                                                                                                                                                                                                       |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | AL       | <ul> <li>Active Current Limit mode</li> <li>1 = Enable active current limit when overcurrent ILIM threshold has been exceeded</li> <li>0 = Disable active current limit. Exceeding overcurrent ILIM threshold set OC flag but does not control outputs</li> </ul> |

| 9   | ILIM1    | ILIM Bit 1                                                                                                                                                                                                                                                        |

| 8   | ILIM0    | ILIM Bit 0                                                                                                                                                                                                                                                        |

| 7   | SR2      | Slew Rate Bit 2                                                                                                                                                                                                                                                   |

| 6   | SR1      | Slew Rate Bit 1                                                                                                                                                                                                                                                   |

| 5   | SR0      | Slew Rate Bit 0                                                                                                                                                                                                                                                   |

| 4   | EN       | <ul> <li>Disable Outputs</li> <li>1 = ENABLE output control when ENBL pin is high and DIS pin is low</li> <li>0 = DISABLE output control and tri-state outputs</li> </ul>                                                                                         |

| 3   | MODE     | Input Control mode <sup>[1]</sup> <ul> <li>1 = H-bridge control mode</li> <li>0 = Half-bridge control mode</li> </ul>                                                                                                                                             |

| 2   | INPUT    | <ul> <li>Active INPUT Control mode</li> <li>1 = SPI control of outputs by way of VIN1 and VIN2, IN1 pin and IN2 pin are disabled</li> <li>0 = Parallel control of outputs by way of IN1 pin and IN2 pin, VIN1 and VIN2 are disabled</li> </ul>                    |

| 1   | VIN2     | <ul> <li>Virtual Input 2 (SPI equivalent of IN2)</li> <li>1 = ON equivalent to IN2 pin at logic high in parallel mode</li> <li>0 = OFF equivalent to IN2 pin at logic low in parallel mode</li> </ul>                                                             |

| 0   | VIN1     | <ul> <li>Virtual Input 1 (SPI equivalent of IN1)</li> <li>1 = ON equivalent to IN1 pin at logic high in parallel mode</li> <li>0 = OFF equivalent to IN1 pin at logic low in parallel mode</li> </ul>                                                             |

[1] When MODE=0 (Half-bridge mode): Active Current Limit mode is disabled, OV is a warning only, SC acts independent on each output, open load is disabled.

### 9.7 Protection and supervision

The MC33HB2000 includes supervision features which enable advanced diagnostics by monitoring the  $V_{PWR}$  undervoltage,  $V_{PWR}$  overvoltage and die temperature.

#### 9.7.1 V<sub>PWR</sub> undervoltage detection

#### 9.7.1.1 Description

When VPWR is less than V<sub>PWR\_FUV</sub> longer than t<sub>VPWR</sub> all output transistors turn off and remain off until VPWR increases above the V<sub>PWR\_FUV</sub> threshold by V<sub>PWR\_UVHYS</sub>. While ramping up the voltage on VPWR, when VPWR increases to a voltage greater than V<sub>PWR\_FUV</sub> + V<sub>PWR\_UVHYS</sub> for at least t<sub>VPWR</sub>, the MC33HB2000 starts unrestricted operation.

Data sheet: advance information

#### 10 A H-bridge, SPI programmable brushed DC motor driver

#### 9.7.1.2 Electrical characteristics

#### Table 18. V<sub>PWR\_UV</sub> electrical characterization

$T_J = -40$  °C to 150 °C, unless otherwise specified.

| Symbol                 | Characteristic                                           | Min.   | Тур. | Max. | Unit |

|------------------------|----------------------------------------------------------|--------|------|------|------|

| V <sub>PWR</sub> UNDER | VOLTAGE                                                  | ,<br>, | Ì    | Ċ    |      |

| V <sub>PWR_FUV</sub>   | Undervoltage threshold to disable outputs (falling edge) | 3.55   | —    | 4.0  | V    |

| V <sub>PWR_UVHYS</sub> | Undervoltage hysteresis                                  | 250    | —    | 450  | mV   |

| t <sub>VPWR</sub>      | Undervoltage detection filter time                       | _      | —    | 10   | μs   |

| V <sub>PWR_POR</sub>   | Power On Reset with VPWR falling                         | 2.3    | —    | 3.1  | V    |

#### 9.7.2 V<sub>PWR</sub> overvoltage detection

If VPWR voltage is higher than  $OV_{HSD}$  threshold longer than  $t_{OV_{HSD}}$ , the OV status bit is set and the device is in an overvoltage condition. When the device is in an overvoltage condition and is also in H-bridge mode (MODE bit =1), both OUT1 and OUT2 low-side switches controlling the load is turned off and both OUT1 and OUT2 high-side switches are turned on to drain the energy in the load.

When VPWR voltage drops by more than  $OV_{HYS}$  below the  $OV_{HSD}$  threshold, the outputs are restored to operation without an overvoltage condition. The OV status bit is not reset until clr\_flt conditions are satisfied.

#### 9.7.2.1 Electrical characteristics

#### Table 19. V<sub>PWR\_OV</sub> electrical characterization

$T_J = -40$  °C to 150 °C, unless otherwise specified.

| Symbol                  | Characteristic                        | Min. | Тур. | Max. | Unit |  |

|-------------------------|---------------------------------------|------|------|------|------|--|

| OVERVOLTAGE DETECTION   |                                       |      |      |      |      |  |

| V <sub>PWR_OV_HSD</sub> | Overvoltage detection threshold       | 33   | 35   | 37   | V    |  |

| V <sub>PWR_OV_HYS</sub> | Overvoltage detection hysteresis      | 2.3  | 2.45 | 2.5  | V    |  |

| t <sub>OV_HSD</sub>     | Overvoltage detection filter time [1] | —    | —    | 3.0  | μs   |  |

[1] Measured in H-bridge mode, 1.0 A resistive load, SR = 000, measured from FS\_B low to both V<sub>OUT</sub> ≥ 10 % V<sub>PWR</sub>

#### 9.7.3 Die temperature

#### 9.7.3.1 Description

The MC33HB2000 has temperature sensors near the center of each power device.

The threshold of the overtemperature warning  $(OT_W)$  is approximately 150 °C on any power device. Temperature warning condition is defined as exceeding  $OT_W$ . When a temperature warning occurs, outputs are not shutdown. However, the SPI status bit shows the actual status at accessing time. This is a non-latching condition and the status clears when the temperature falls below the hysteresis threshold. Further action is taken on temperature warning as described in <u>Section 9.6.4 "SPI mapping"</u> and <u>Section 10.4.1.4 "Active current limit regulation"</u>.

When the temperature is above the overtemperature threshold (OT) for the defined filter time ( $t_{OT}$ ), the driver latches off, the SPI OT fault bit is set. This is a latching fault and

#### 10 A H-bridge, SPI programmable brushed DC motor driver

requires performing clr\_flt, as described in <u>Section 9.6.3.1 "Clearing the fault status"</u>, after the temperature reduces  $T_{HYS}$  below the threshold.

#### 9.7.3.2 Electrical characteristics

#### Table 20. OT electrical characterization

$V_{PWR}$  = 5.0 V to 28 V, unless otherwise specified.

| Symbol                              | Characteristic                              |     | Min. | Тур. | Max. | Unit |  |

|-------------------------------------|---------------------------------------------|-----|------|------|------|------|--|

| OVERTEMPERATURE/TEMPERATURE WARNING |                                             |     |      |      |      |      |  |

| OT <sub>W</sub>                     | Overtemperature warning detection threshold | [1] | 140  | 150  | 165  | °C   |  |

| ОТ                                  | Overtemperature shutdown threshold          | [1] | 165  | 175  | 190  | °C   |  |

| T <sub>HYS</sub>                    | Overtemperature hysteresis                  | [1] | —    | 12   | —    | °C   |  |

| t <sub>OT</sub>                     | Temperature warning detection filter time   |     | _    | —    | 11   | μs   |  |

[1] Guaranteed by characterization.

#### 9.7.4 Truth table

The following truth table summarizes the output response to input states. The tri-state conditions and the status flag are reset using DIS, ENBL, or SPI. The truth table uses the following notations: L = LOW, H = HIGH, X = HIGH or LOW, Xb is inverse of X, and Z = High-impedance.

Data sheet: advance information

# MC33HB2000

#### 10 A H-bridge, SPI programmable brushed DC motor driver

#### Table 21. Truth table

| Device state                        | Input conditions |                    |                    |                    | Status              | Outputs |      |

|-------------------------------------|------------------|--------------------|--------------------|--------------------|---------------------|---------|------|

|                                     | ENBL             | DIS <sup>[1]</sup> | IN1 <sup>[2]</sup> | IN2 <sup>[2]</sup> | FS_B <sup>[3]</sup> | OUT1    | OUT2 |

| HALF-BRIDGE CONTROL MODE            |                  |                    |                    |                    |                     |         |      |

| Forward                             | Н                | L                  | Н                  | L                  | Н                   | Н       | L    |

| Reverse                             | н                | L                  | L                  | Н                  | Н                   | L       | Н    |

| Freewheeling Low                    | Н                | L                  | L                  | L                  | Н                   | L       | L    |

| Freewheeling High                   | Н                | L                  | Н                  | Н                  | Н                   | Н       | Н    |

| IN1 Disconnected                    | Н                | L                  | Z                  | Х                  | Н                   | L       | Х    |

| IN2 Disconnected                    | Н                | L                  | Х                  | Z                  | Н                   | Х       | L    |

| H-BRIDGE CONTROL MODE               |                  |                    |                    |                    |                     |         | ,    |

| Forward                             | Н                | L                  | Н                  | Н                  | Н                   | Н       | L    |

| Reverse                             | Н                | L                  | L                  | Н                  | Н                   | L       | Н    |

| Freewheel High                      | Н                | L                  | Х                  | L                  | Н                   | Н       | Н    |

| IN1 Disconnected – Reverse          | н                | L                  | Z                  | Х                  | Н                   | Xb      | Н    |

| IN2 Disconnected – Freewheel High   | Н                | L                  | Х                  | Z                  | Н                   | Н       | н    |

| PROTECTION                          |                  |                    |                    |                    |                     |         |      |

| Disable (DIS)                       | Н                | Н                  | Х                  | Х                  | L                   | Z       | Z    |

| DIS Disconnected                    | Н                | Z                  | Х                  | Х                  | L                   | Z       | Z    |

| Undervoltage Lockout <sup>[4]</sup> | н                | Х                  | Х                  | Х                  | L                   | Z       | Z    |

| Overvoltage <sup>[5]</sup>          | Н                | Х                  | Х                  | Х                  | L                   | Н       | Н    |

| Overtemperature <sup>[6]</sup>      | Н                | Х                  | Х                  | Х                  | L                   | Z       | Z    |

| Short-circuit <sup>[7]</sup>        | Н                | Х                  | Х                  | Х                  | L                   | Z       | Z    |

| Sleep mode ENBL                     | L                | Х                  | Х                  | Х                  | Н                   | Z       | Z    |

| ENBL Disconnected                   | Z                | Х                  | Х                  | Х                  | Н                   | Z       | Z    |

SPI bit EN=1 AND DIS=L for table entry DIS=L [1]

When the SPI bit INPUT = 1, the SPI bit VIN1 behaves the same as IN1 and SPI bit VIN2 behaves the same as IN2.

[2] [3] [4] Default response for FS\_B, SPI programming may change the default behavior. In the event of an undervoltage condition, the outputs tri-state and status flag is SET logic LOW. Upon undervoltage recovery the outputs are restored to

their original operating condition, FS\_B remains low until clr\_flt clears the status register. In the event of an overvoltage condition, the outputs go to freewheeling high configuration, independent of the input signals, and the status flag is latched to a logic LOW. Upon overvoltage recovery, the outputs are restored to following the input signals but FS\_B remains low until clr\_flt clears the status [5] register. In Half-bridge mode an overvoltage event does not change the output state.

When a short-circuit or overtemperature condition is detected, the power outputs are tri-state latched-OFF, independent of the input signals, and the [6] status flag is latched to a logic LOW. To reset from this condition requires the togging of either DIS, ENBL, or V<sub>PWR</sub> or flt\_clr from the SPI. When in H-bridge control mode, short-circuit controls both OUT1 and OUT2. However, in Half-bridge mode, short-circuit only controls the output which

[7] detects the short-circuit.

# MC33HB2000

10 A H-bridge, SPI programmable brushed DC motor driver

### 9.8 Error handling

#### Table 22. Error handling

| Type of error              | <b>Detection condition</b>                          | Action              | Clear SPI flag                                       | <b>Restart condition</b>                        |  |  |  |  |

|----------------------------|-----------------------------------------------------|---------------------|------------------------------------------------------|-------------------------------------------------|--|--|--|--|

| SUPERVISION                |                                                     |                     |                                                      |                                                 |  |  |  |  |

| Overtemperature shutdown   | Normal mode                                         | See <u>Table 21</u> | Write Clear Fault SPI<br>bit OT                      | Latching fault requires<br>clr_flt              |  |  |  |  |

| Die temperature<br>warning | All except Sleep mode                               | SPI flag only (TW)  | Non-latching auto<br>clears when condition<br>clears | Non-latching fault clears when condition clears |  |  |  |  |

| Overcurrent                | Normal mode                                         | SPI flag only (OC)  | Write Clear Fault SPI<br>bit OC                      | Latching fault requires<br>clr_flt              |  |  |  |  |

| Open load                  | Transition to Normal<br>mode or request from<br>MCU | SPI flag only (OL)  | Write Clear Fault SPI bit OL                         | Information only, no restart required           |  |  |  |  |

MC33HB2000 Data sheet: advance information