# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### 8-Channel LED Driver with Differential Interface

The 34848 is a high efficiency, 8-channel LED driver for use in LCD backlighting applications. It is designed to support up to 160 mA / channels in scan backlight mode, or 80 mA/channels in local dimming mode. Current reference is set using a single resistor to GND and LED current tolerance is accurate to  $\pm$ 1% channel-to-channel and IC-to-IC. The current can be programmed in both local dimming and scan modes.

Each channel has independent PWM control with 10-bit resolution, programmed with high speed differential interface. The frequency between ICs is synchronized and derived from Controller (LED Driver Controller) signals. When the SCAN pin is pulled high, it enables the Scan mode. In this mode, each of 8 channels is on for nominally 3/8 of the frame.

The integrated boost controller is used to generate the minimum output voltage required to keep all LEDs illuminated with the selected current, providing the highest efficiency possible. The integrated boost clock can be programmed from 200 kHz to 1.2 MHz.

#### Features

- Drives 8 LED channels: ±1% current tolerance

- Local dimming mode, scan mode (2/8, 3/8, 4/8, 5/8), test mode

- · Output voltage up to 45 V supporting up to 12 LEDs

- Auto drive voltage (V<sub>OUT</sub>) selection: Minimum feedback voltage 500 mV for low power

- Differential Interface: Initial setup (LED current, f<sub>PWM</sub>, OVP, etc.), PWM data in normal operation

- Integrated PLL for synchronization: 177 to 200 Hz in 1.0 Hz steps

- 10-bit PWM control per channel: Dimming ratio: >1000:1, turn-on time: <200 ns

- · Pb-free packaging designated by suffix code EP"

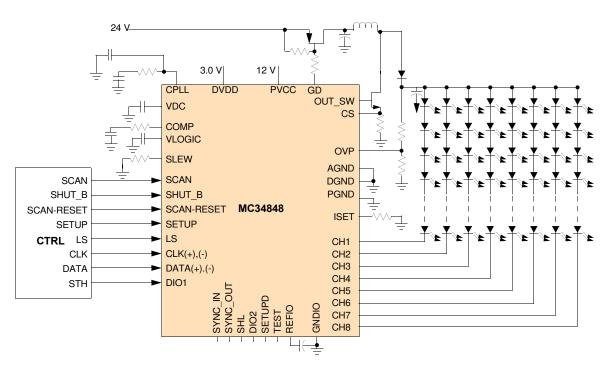

Figure 1. 34848 Simplified Application Diagram

\* This document contains certain information on a new product.

Specifications and information herein are subject to change without notice.

© Freescale Semiconductor, Inc., 2010. All rights reserved.

MC34848

#### POWER MANAGEMENT IC

| ORDERING INFORMATION                          |               |           |  |  |

|-----------------------------------------------|---------------|-----------|--|--|

| Device Temperature<br>Range (T <sub>A</sub> ) |               | Package   |  |  |

| MC34848EP                                     | -40°C to 85°C | 48 QFN EP |  |  |

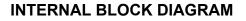

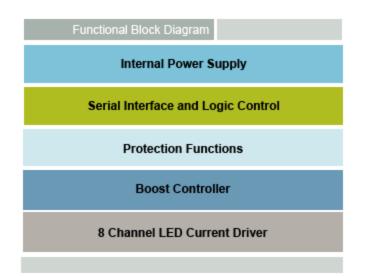

Figure 2. 34848 Simplified Internal Block Diagram

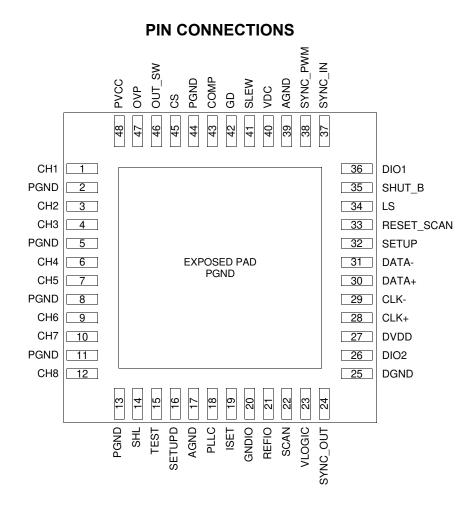

#### Figure 3. 34848 Pin Connections

#### Table 1. 34848 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section.

| Pin Number             | Pin Name | Pin Function | Formal Name | Definition                                                                                                  |

|------------------------|----------|--------------|-------------|-------------------------------------------------------------------------------------------------------------|

| 1                      | CH1      |              |             | LED connection - channel 1                                                                                  |

| 2, 5, 8, 11,<br>13, 44 | PGND     |              |             | Power ground                                                                                                |

| 3                      | CH2      |              |             | LED connection - channel 2                                                                                  |

| 4                      | CH3      |              |             | LED connection - channel 3                                                                                  |

| 6                      | CH4      |              |             | LED connection - channel 4                                                                                  |

| 7                      | CH5      |              |             | LED connection - channel 5                                                                                  |

| 9                      | CH6      |              |             | LED connection - channel 6                                                                                  |

| 10                     | CH7      |              |             | LED connection - channel 7                                                                                  |

| 12                     | CH8      |              |             | LED connection - channel 8                                                                                  |

| 14                     | SHL      |              |             | Shift register direction ('H' - DIO1 input, CH1 - CH8, DIO2 output, 'L' DIO2 input, CH8 - CH1, DIO1 output) |

| 15                     | TEST     |              |             | Enable test mode                                                                                            |

| 16                     | SETUPD   |              |             | Setup default value select                                                                                  |

#### Table 1. 34848 Pin Definitions (continued)

A functional description of each pin can be found in the Functional Pin Description section.

| Pin Number  | Pin Name   | Pin Function | Formal Name | Definition                                                |

|-------------|------------|--------------|-------------|-----------------------------------------------------------|

| 17, 39      | AGND       | Ground       |             | Analog ground                                             |

| 18          | PLLC       |              |             | PLL compensation network connection                       |

| 19          | ISET       |              |             | Current reference setting                                 |

| 20          | GNDIO      |              |             | Ground reference REFIO supply                             |

| 21          | REFIO      |              |             | Reference voltage supply                                  |

| 22          | SCAN       |              |             | Enable scan made ('H' enabled, 'L' disabled)              |

| 23          | VLOGIC     |              |             | Decouple for internally generated 2.5 V rail              |

| 24          | SYNC-OUT   |              |             | Boost clock output                                        |

| 25          | DGND       |              |             | Digital ground                                            |

| 26          | DIO2       |              |             | Data shift register I/O2                                  |

| 27          | DVDD       |              |             | Logic supply voltage                                      |

| 28          | CLK+       |              |             | Differential interface clock+                             |

| 29          | CLK-       |              |             | Differential interface clock -                            |

| 30          | DATA+      |              |             | Data+                                                     |

| 31          | DATA-      |              |             | Data-                                                     |

| 32          | SETUP      | Input        |             | SETUP input. Setup mode and clear data register when high |

| 33          | RESET_SCAN | Input        |             | RESET_SCAN input. Reset internal counter                  |

| 34          | LS         |              |             | Data Latch                                                |

| 35          | SHUT_B     |              |             | Shutdown pin, active low                                  |

| 36          | DIO1       |              |             | Data shift register I/O1                                  |

| 37          | SYNC_IN    | Input        |             | Boost clock input                                         |

| 38          | SYNC_PWM   | Input        |             | PWM sync input                                            |

| 40          | VDC        |              |             | Decouple for internal gate driver voltage                 |

| 41          | SLEW       |              |             | Boost driver slew rate control                            |

| 42          | GD         |              |             | Control to power switch for input voltage $V_{IN}$        |

| 43          | COMP       |              |             | Boost compensation pin                                    |

| 45          | CS         | Input        |             | Current sense input pin                                   |

| 46          | OUT-SW     | Output       |             | FET driver output                                         |

| 47          | OVP        |              |             | Over-voltage protection sense pin                         |

| 48          | PVCC       |              |             | Switch driver power supply                                |

| Exposed Pad | PGND       | Ground       |             | Power ground                                              |

#### **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

#### Table 2. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                             | Symbol               | Value      | Unit |

|---------------------------------------------------------------------|----------------------|------------|------|

|                                                                     |                      |            |      |

| Maximum Pin Voltage                                                 | V <sub>MAX</sub>     |            | V    |

| CH1 - CH8                                                           |                      | 45         |      |

| GD                                                                  |                      | 28         |      |

| PVCC                                                                |                      | 14         |      |

| VDC, OUT_SW                                                         |                      | 6.2        |      |

| PLLC, ISET, REFIO, VLOGIC, OVP, CS, COMP, SLEW, SYNC_PWM, CLK, DATA |                      | 2.6        |      |

| All other pins                                                      |                      | 3.6        |      |

| VIN Input Voltage Range                                             | V <sub>IN</sub>      | 12 to 28   | V    |

| PVCC Input Voltage Range                                            | P <sub>VCC</sub>     | 6.0 to 14  | V    |

| DVDD Input Voltage Range                                            | D <sub>VDD</sub>     | 2.6 to 3.6 | V    |

| Maximum LED Current - Local Dimming Mode                            | I <sub>LED_LDM</sub> | 82         | mA   |

| Maximum LED Current - Scan Mode                                     | I <sub>LED_SM</sub>  | 164        | mA   |

| ESD Voltage <sup>(1)</sup>                                          | V <sub>ESD</sub>     |            | V    |

| Human Body Model (HBM)                                              |                      | ±2000      |      |

| Machine Model (MM)                                                  |                      | ±200       |      |

| Ambient Temperature Range                                     | T <sub>A</sub>     | -40 to 85 | °C   |

|---------------------------------------------------------------|--------------------|-----------|------|

| Storage Temperature                                           | T <sub>STO</sub>   | -40 to150 | °C   |

| Peak Package Reflow Temperature During Reflow <sup>(2),</sup> | T <sub>PPRT</sub>  | Note 2    | °C   |

| Maximum Junction Temperature                                  | T <sub>J_MAX</sub> | 150       | °C   |

| Thermal Resistance, Junction to Ambient <sup>(3)</sup>        | R <sub>θJ-A</sub>  | 28        | °C/W |

| Thermal Resistance, Junction to Case <sup>(4)</sup>           | R <sub>θJ-C</sub>  | 2.0       | °C/W |

Notes

1. ESD testing is performed in accordance with the Human Body Model (HBM) (AEC-Q100-2), and the Machine Model (MM) (AEC-Q100-003),  $R_{ZAP} = 0 \Omega$ ).

Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL),Go to <u>www.freescale.com</u>, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

3. Thermal resistance measured in accordance with EIA/JESD51-2.

4. Theoretical thermal resistance from the die junction to the exposed pad.

#### STATIC ELECTRICAL CHARACTERISTICS

#### **Table 3. Static Electrical Characteristics**

Characteristics noted under conditions  $V_{IN} = 24 \text{ V}$ ,  $V_{PVCC} = 12 \text{ V}$ ,  $V_{DVDD} = 3.3 \text{ V}$ ,  $I_{LED} = 70 \text{ mA}$  (Local Dimming Mode); 140 mA (Scan Mode),  $f_S = 700 \text{ kHz}$ ,  $f_{PWM} = 660 \text{ Hz}$ , GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}\text{C}$  under nominal conditions, unless otherwise noted.

| Characteristic                                                                     | Symbol                          | Min | Тур  | Max  | Unit |

|------------------------------------------------------------------------------------|---------------------------------|-----|------|------|------|

| SUPPLY                                                                             |                                 |     | 1    |      |      |

| Supply Voltage at PVCC                                                             | V <sub>PVCC</sub>               | 6.0 | 12   | 14   | V    |

| Supply Current at PVCC, Device Enabled<br>SHUT_B = High, V <sub>PVCC</sub> = 14 V  | IPVCC                           | -   | 18.5 | 22   | mA   |

| Supply Current at PVCC, Device Disabled<br>SHUT_B = Low, V <sub>PVCC</sub> = 14 V  | I <sub>PVCC-DIS</sub>           | -   | 14.5 | 18   | mA   |

| PVCC Under-voltage Lockout<br>V <sub>PVCC</sub> Falling                            | V <sub>PVCC_UVLO</sub>          | -   | -    | 5.5  | V    |

| PVCC Under-voltage Lockout Hysteresis<br>V <sub>PVCC</sub> Rising                  | V <sub>PVCC_UVLO_HY</sub><br>ST | -   | 0.24 | -    | V    |

| Supply Voltage at DVDD                                                             | V <sub>DVDD</sub>               | 2.6 | 3.3  | 3.6  | V    |

| Supply Current at DVDD, Device Enabled<br>SHUT_B = High, V <sub>DVDD</sub> = 3.6 V | IDVDD                           | -   | 7.5  | 12   | mA   |

| Supply Current, Device Disabled<br>SHUT_B = Low, V <sub>DVDD</sub> = 3.6 V         | I <sub>DVDD-DIS</sub>           | -   | 7.5  | 12   | mA   |

| DVDD Under-voltage Lockout<br>V <sub>DVDD</sub> Falling                            | V <sub>DVDD_UVLO</sub>          | 2.3 | 2.4  | 2.55 | V    |

| DVDD Under-voltage Lockout Hysteresis<br>V <sub>PVCC</sub> Rising                  | V <sub>DVDD_UVLO_HY</sub><br>ST | -   | 0.15 | -    | V    |

| VDC Output Voltage <sup>(5)</sup><br>$C_{VDC} = 2.2 \ \mu F$                       | V <sub>DC</sub>                 | 5.8 | 6.0  | 6.2  | V    |

| $V_{LOGIC}$ Output Voltage <sup>(5)</sup><br>$C_{VLOGIC} = 2.2 \mu\text{F}$        | V <sub>LOGIC</sub>              | 2.4 | 2.5  | 2.6  | V    |

Notes

5. This pin is for internal use only, and not to be used for other purposes.

#### Table 3. Static Electrical Characteristics (continued)

Characteristics noted under conditions  $V_{IN} = 24 \text{ V}$ ,  $V_{PVCC} = 12 \text{ V}$ ,  $V_{DVDD} = 3.3 \text{ V}$ ,  $I_{LED} = 70 \text{ mA}$  (Local Dimming Mode); 140 mA (Scan Mode),  $f_S = 700 \text{ kHz}$ ,  $f_{PWM} = 660 \text{ Hz}$ , GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}\text{C}$  under nominal conditions, unless otherwise noted.

| Characteristic                                               | Symbol                            | Min   | Тур      | Max   | Unit |

|--------------------------------------------------------------|-----------------------------------|-------|----------|-------|------|

| BOOST CONVERTER                                              |                                   |       | 1        |       |      |

| SW Output Voltage                                            | V <sub>SW</sub>                   | 5.8   | 6.0      | 6.2   | V    |

| CS Sense Voltage                                             | V <sub>CS</sub>                   |       |          |       | V    |

| $R_{CS}$ = 50 mΩ, $I_{LIMIT}$ Threshold = 3.5 A              |                                   | -     | 0.175    | -     |      |

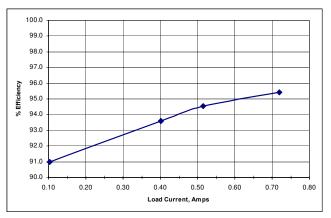

| Boost Efficiency <sup>(6)</sup>                              | EFF <sub>BOOST</sub>              |       |          |       | %    |

| I <sub>LOAD</sub> = 0.5 A                                    |                                   | -     | 94       | -     |      |

| Boost Line Regulation                                        | I <sub>OUT</sub> /V <sub>IN</sub> |       |          |       | %/V  |

| $(V_{IN} = 24 \text{ V} \pm 15\%, I_{LOAD} = 0.5 \text{ A})$ |                                   | -     | 0.1      | -     |      |

| Current Sense Amplifier Gain                                 | A <sub>CSA</sub>                  | -     | 4.5      | -     |      |

| Slope Compensation Voltage Ramp                              | V <sub>SLOPE</sub>                | -     | 0.34     | -     | V    |

| ED CURRENT DRIVER                                            |                                   |       | 4        |       | ļ    |

| Maximum sink current                                         | ۱ <sub>S</sub>                    |       |          |       | mA   |

| Local Dimming Mode                                           |                                   | -     | -        | 82    |      |

| Scan Mode                                                    |                                   | -     | -        | 164   |      |

| Regulated Minimum voltage across drivers                     | V <sub>MIN</sub>                  | 400   | 500      | 600   | mV   |

| Off-state Leakage Current, all channels                      | I <sub>CH_LEAK</sub>              |       |          |       | μA   |

| (V <sub>CH</sub> = 45 V)                                     |                                   | -     | -        | 10    |      |

| LED Current Tolerance                                        | ITOLERANCE                        |       |          |       | %    |

| Channel-to-Channel/ Chip-to-Chip                             |                                   | -1    | -        | +1    |      |

| ISET pin voltage                                             | V <sub>SET</sub>                  | 1.252 | 1.265    | 1.277 | V    |

| Local Dimming Mode Drive Current                             | I <sub>LDM</sub>                  |       |          |       | mA   |

| IL = 000                                                     |                                   | 61.8  | 62.5     | 63.2  |      |

| IL = 111                                                     |                                   | 79.2  | 80       | 80.8  |      |

| Scan Mode Drive Current                                      | I <sub>SCAN</sub>                 |       |          |       | mA   |

| IS = 00000                                                   |                                   | 120.0 | 121.2    | 122.4 |      |

| IS = 11111                                                   |                                   | 158.4 | 160      | 161.6 |      |

| AULT PROTECTION                                              |                                   |       |          |       |      |

| Over-temperature Threshold                                   | O <sub>TT</sub>                   | 140   | 150      | 160   | °C   |

| Short Failure Detection Voltage                              | S <sub>FDV</sub>                  |       |          |       | V    |

| C = 00                                                       |                                   | -     | Disabled | -     |      |

| L | <br> | <br> |  |

|---|------|------|--|

|   |      |      |  |

|   | ι.   |      |  |

|   |      |      |  |

C = 01

C = 10

C = 11

6. Boost efficiency test is performed under the following conditions: f<sub>SW</sub> = 700 kHz, V<sub>IN</sub> = 24 V, T<sub>A</sub> = 25°C, V<sub>PVCC</sub> = 12 V, V<sub>DVDD</sub> = 3.3 V, and R<sub>L</sub> = 70 Ω. The following external components are used: FDS3692 (Boost FET), FDS4675 (Q-FET), L = 22 μH (DCR = 54 mΩ), C<sub>TOUT</sub> = 30 μF, SS36-E3 (Schottky diode). The measurement does not include Q-FET losses. Note: Freescale does not assume liability, endorse, or warrant components from external manufacturers that are referenced in circuit drawings or tables. While Freescale offers component recommendations in this configuration, it is the customer's responsibility to validate their application.

2.7

3.6

4.5

3.0

4.0

5.0

3.3

4.4

5.5

#### Table 3. Static Electrical Characteristics (continued)

Characteristics noted under conditions  $V_{IN} = 24 \text{ V}$ ,  $V_{PVCC} = 12 \text{ V}$ ,  $V_{DVDD} = 3.3 \text{ V}$ ,  $I_{LED} = 70 \text{ mA}$  (Local Dimming Mode); 140 mA (Scan Mode),  $f_S = 700 \text{ kHz}$ ,  $f_{PWM} = 660 \text{ Hz}$ , GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}\text{C}$  under nominal conditions, unless otherwise noted.

| Characteristic               | Symbol          | Min  | Тур | Мах  | Unit |

|------------------------------|-----------------|------|-----|------|------|

| OVP Threshold <sup>(7)</sup> | O <sub>VP</sub> |      |     |      | V    |

| V = 000                      |                 | 27.9 | 31  | 34.1 |      |

| V = 001                      |                 | 29.7 | 33  | 36.3 |      |

| V = 010                      |                 | 31.5 | 35  | 38.5 |      |

| V = 011                      |                 | 33.3 | 37  | 40.7 |      |

| V = 100                      |                 | 35.1 | 38  | 42.9 |      |

| V = 101                      |                 | 36.9 | 41  | 45.1 |      |

| V = 110                      |                 | 38.7 | 43  | 47.3 |      |

| V = 111                      |                 | 40.5 | 45  | 49.5 |      |

#### LOGIC INPUTS (SHUT\_B, DIO1, DIO2, RESET, LS, SHL)

| Input Threshold Low                                          | V <sub>IL</sub>          | -   | - | 0.8 | V  |

|--------------------------------------------------------------|--------------------------|-----|---|-----|----|

| Input Threshold High                                         | V <sub>IH</sub>          | 2.0 | - | -   | V  |

| SHUT_B Input Leakage Current<br>V <sub>SHUT_B</sub> = 1.0 V  | I <sub>SHUT_B_LEAK</sub> | -   | - | 10  | μA |

| DIO1, DIO2 Input Leakage Current<br>V <sub>DIO</sub> = 1.0 V | I <sub>DIO_LEAK</sub>    | -   | - | 10  | μΑ |

| SETUP, RESET_SCAN Input Leakage Current<br>V = 1.0 V         | I <sub>LEAK</sub>        | -   | - | 10  | μA |

| LS Input Leakage Current<br>V <sub>LS</sub> = 1.0 V          | ILS_LEAK                 | -   | - | 10  | μA |

| SHL Input Leakage Current<br>V <sub>SHL</sub> = 1.0 V        | I <sub>SHL_LEAK</sub>    | -   | - | 10  | μΑ |

Notes

7. Measurements performed using a resistor divider network with a ratio of 23.71.

#### DYNAMIC ELECTRICAL CHARACTERISTICS

#### Table 4. Dynamic Electrical Characteristics

Characteristics noted under conditions  $V_{IN} = 24 \text{ V}$ ,  $V_{PVCC} = 12 \text{ V}$ ,  $V_{DVDD} = 3.3 \text{ V}$ ,  $I_{LED} = 70 \text{ mA}$  (Local Dimming Mode); 140 mA (Scan Mode),  $f_S = 700 \text{ kHz}$ ,  $f_{PWM} = 660 \text{ Hz}$ , GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}\text{C}$  under nominal conditions unless otherwise noted.

| Characteristic                                                                                      | Symbol           | Min | Тур  | Max  | Unit |

|-----------------------------------------------------------------------------------------------------|------------------|-----|------|------|------|

| BOOST CONVERTER                                                                                     | 1                | 1   |      | 1    |      |

| Minimum duty cycle                                                                                  | D <sub>MIN</sub> | 25  | -    | 75   | ns   |

| Maximum duty cycle                                                                                  | D <sub>MAX</sub> | -   | -    | 98   | %    |

| Switching Frequency                                                                                 | f <sub>S</sub>   |     |      |      | kHz  |

| F = 000                                                                                             | -                | 160 | 200  | 240  |      |

| F = 001                                                                                             |                  | 240 | 300  | 360  |      |

| F = 010                                                                                             |                  | 320 | 400  | 480  |      |

| F = 011                                                                                             |                  | 400 | 500  | 600  |      |

| F = 100                                                                                             |                  | 480 | 600  | 720  |      |

| F = 101                                                                                             |                  | 560 | 700  | 840  |      |

| F = 110                                                                                             |                  | 720 | 900  | 1080 |      |

| F = 111                                                                                             |                  | 960 | 1200 | 1440 |      |

| Soft Start Period                                                                                   | t <sub>SS</sub>  | -   | 20   | -    | ms   |

| SW Drive                                                                                            | SW <sub>DR</sub> | Ī   |      |      | ns   |

| Rise time (10% to 90%), C <sub>LOAD</sub> = 1.2 nF, VSW = 6.0 V, R <sub>SLEW</sub> = 4.7 k $\Omega$ |                  | -   | 12.5 | -    |      |

| Fall time (90% to 10%), $C_{\text{LOAD}}$ = 1.2 nF, VSW = 6.0 V, $R_{\text{SLEW}}$ = 4.7 $k\Omega$  |                  | -   | 16.5 | -    |      |

#### **PWM GENERATOR**

| RESET_SCAN Frequency                         | F <sub>RESET_SCAN</sub> | 80   | 120  | 180  | Hz  |

|----------------------------------------------|-------------------------|------|------|------|-----|

| PWM frequency <sup>(8)</sup>                 | f <sub>PWM</sub>        |      |      |      | Hz  |

| P = 0000000000                               |                         |      |      |      |     |

| F <sub>RESET_SCAN</sub> = 80 Hz              |                         | 112  | 118  | 124  |     |

| F <sub>RESET_SCAN</sub> = 120 Hz             |                         | 168  | 177  | 186  |     |

| F <sub>RESET_SCAN</sub> = 180 Hz             |                         | 253  | 266  | 279  |     |

| P = 1111111111                               |                         |      |      |      |     |

| F <sub>RESET_SCAN</sub> = 80 Hz              |                         | 760  | 800  | 840  |     |

| F <sub>RESET_SCAN</sub> = 120 Hz             |                         | 1140 | 1200 | 1260 |     |

| F <sub>RESET_SCAN</sub> = 180 Hz             |                         | 1710 | 1800 | 1890 |     |

| PWM Synchronization Frequency <sup>(8)</sup> | f <sub>SYNC_PWM</sub>   |      |      |      | kHz |

| f <sub>PWM</sub> = 177 Hz                    |                         | 172  | 181  | 190  |     |

| f <sub>PWM</sub> = 1200 Hz                   |                         | 1166 | 1228 | 1289 |     |

| LED CURRENT | DRIVER |

|-------------|--------|

|-------------|--------|

| Channel Rise Time - 10% to 90%, I <sub>LED_PEAK</sub> = 70 mA | t <sub>R</sub> | - | - | 200 | ns |

|---------------------------------------------------------------|----------------|---|---|-----|----|

| Channel Fall Time - 90% to 10%, I <sub>LED_PEAK</sub> = 70 mA | t <sub>F</sub> | - | - | 200 | ns |

Notes

8. For Slave mode, the IC to IC matching is under  $\pm 1\%$

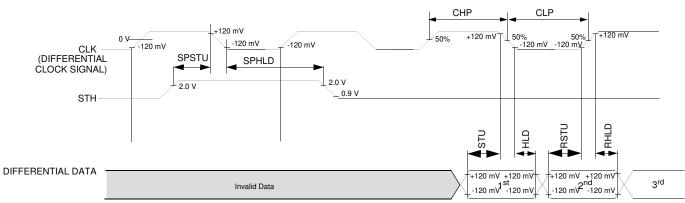

#### TIMING DIAGRAMS

The differential interface for data and clock control is specified as below.

#### NOTE: Max CLK Frequency - 85 MHz

#### Figure 4. Timing Specifications 1

#### Table 5. Timing Specification 1

| Symbol | Parameter                                        | Conditions                                                 | Min   | Тур. | Max | Unit |

|--------|--------------------------------------------------|------------------------------------------------------------|-------|------|-----|------|

| CHP    | Clock (CLK) High Period                          | f = 85 MHz                                                 | -     | 5.7  | -   | ns   |

| CLP    | Clock (CLK) Low Period                           | f = 85 MHz                                                 | -     | 5.8  | -   | ns   |

| STU    | (R.G.B.) Setup to falling or rising edge of CLK  | f = 85 MHz                                                 | 1.875 | -    | -   | ns   |

| HLD    | (R.G.B.) Hold from falling or rising edge of CLK | I <sub>PI</sub> = 100 μA, f = 85 MHz                       | 0.225 | -    | -   | ns   |

| SPSTU  | STH rising to CLK falling                        | $R_T = 100 \ \Omega, \ C_T = 5.0 \ pF, \ f = 85 \ MHz$     | 3.0   | -    | -   | ns   |

| SPHLD  | STH falling to CLK falling                       | $R_{T} = 100 \ \Omega, \ C_{T} = 5.0 \ pF, \ f = 85 \ MHz$ | 1.5   | -    | -   | ns   |

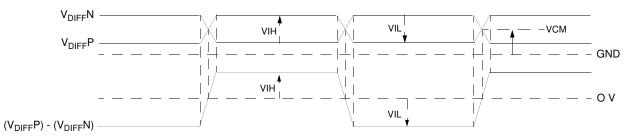

#### Figure 5. CLK and Data input Specification

#### Table 6. Timing Specification 1

| Symbol          | Parameter                       | Conditions                                         | Min | Тур. | Max | Unit |

|-----------------|---------------------------------|----------------------------------------------------|-----|------|-----|------|

| V <sub>IH</sub> | High Input Voltage              | $V_{CM} = +1.2 V^{(9)}$                            | 70  | 200  | -   | mV   |

| V <sub>IL</sub> | Low Input Voltage               | $V_{CM} = +1.2 V^{(9)}$                            | -   | -200 | -70 |      |

| V <sub>CM</sub> | Common Mode Input Voltage Range | $V_{IH} = +70 \text{ mV}, V_{IL} = -70 \text{ mV}$ | 0.9 | 1.2  | 1.4 | V    |

| I <sub>DL</sub> | Input Leakage Current           | DxxP, DxxN, CLKP, CLKN                             | -10 | -    | 10  | μA   |

Notes:

#### 9. VCM = (VCLKP+VCLKN)/2 or VCM = (VDxxP+VDxxN)/2

The positive sign means that DxxP (or CLKP) is higher than ground DxxN (or CLKN) The negative sign means that DxxP (or CLKP) is lower than ground DxxN (or CLKN)

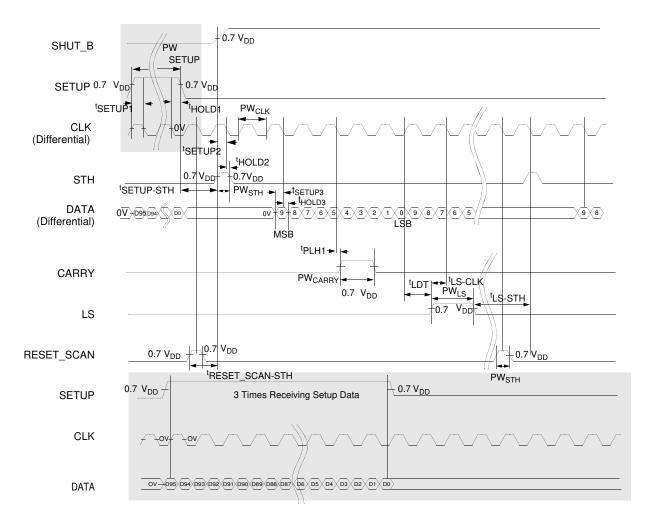

#### Figure 6. Total Interface Detailed Timing

#### Table 7. Interface Timing Specifications

| Symbol                 | Min  | Тур | Max | Unit |

|------------------------|------|-----|-----|------|

| tshut_dvdd             | 200  | -   | -   | ms   |

| tsetup-dvdd            | 1.0  | -   | -   | ms   |

| t <sub>SETUP1</sub>    | 2.0  | -   | -   | ns   |

| t <sub>HOLD1</sub>     | 2.0  | -   | -   | ns   |

| PW <sub>SETUP</sub>    | 48   | -   | -   | CLK  |

| t <sub>SETUP-STH</sub> | 2.0  | -   | -   | CLK  |

| PW <sub>CLK</sub>      | 11.7 | -   | 333 | ns   |

| t <sub>SETUP2</sub>    | 2.0  | -   | -   | ns   |

| t <sub>HOLD2</sub>     | 2.0  | -   | -   | ns   |

| tls-clk                | 4.0  | -   | -   |      |

| PW <sub>STH</sub>      | 1.0  | -   | 2.0 | CLK  |

| t <sub>SETUP3</sub>    | 2.0  | -   | -   | ns   |

| t <sub>HOLD3</sub>     | 2.0  | -   | -   | ns   |

#### Table 7. Interface Timing Specifications

| Symbol                         | Min | Тур | Мах  | Unit |

|--------------------------------|-----|-----|------|------|

| PW <sub>CARRY</sub>            | -   | -   | 1.0  | CLK  |

| t <sub>PLH1</sub> (CL = 15 pf) | 1.0 | -   | 10.7 | ns   |

| t <sub>LDT</sub>               | 1.0 | -   | -    | CLK  |

| tls-sth                        | 2.0 | -   | -    | CLK  |

| treset_scan-sth                | 1.0 | -   | -    | CLK  |

| PW <sub>LS</sub>               | 5.0 | -   | -    | CLK  |

#### CONFIGURATION

When the SETUPD pin is high, the configuration registers are set to the default values in <u>Table 8</u>. When the SETUPD pin is low, the configuration registers can be programmed via the differential interface.

When the SETUPD and SHUT\_B pins are low and SETUP is high, data can be written to the set-up register through the differential interface. Once the register has been

programmed, the data is locked and the register cannot be

reprogrammed again until a complete POR (Power-on-reset) is applied. Although the setup register is only 32 bits, the 34848 requires the data to be written 3 times (i.e. 96 bits). When SETUP is taken low, the 3 sets of data are compared. If 2 or more sets match, then that data is used. Otherwise, the default values are used. This interface programs the LED current, boost frequency, PWM frequency, OVP voltage, and LED short detection voltage.

| Table 8. | Setup | Interface | Registers |

|----------|-------|-----------|-----------|

|----------|-------|-----------|-----------|

| D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|

| IL2 | IL1 | IL0 | IS4 | IS3 | IS2 | IS1 | IS0 | P9 | P8 | P7 | P6 | P5 | P4 | P3 | P2 |

| P1  | P0  | F2  | F1  | F0  | V2  | V1  | V0  | S1 | S0 | C1 | C0 | R3 | R2 | R1 | R0 |

- IL[2:0] = Local dimming mode current control ('000' = 62.5 mA, '111' = 80 mA). Default = '011' = 70 mA

- IS[4:0] = Scan mode current control ('00000' = 121.25 mA, '11111' = 160 mA) Default = '01111' = 140 mA

- P[9:0] = PWM frequency ('0000000000' = 177 Hz, '1111111111' = 1200 Hz). Default = '0111100011' = 660 Hz

- F[2:0] = Boost switching frequency (000 = 200 kHz, 001 = 300 kHz, 010 = 400 kHz, 011 = 500 kHz, 100 = 600 kHz, 101 = 700 kHz, 110 = 900 kHz, 111 = 1.2 MHz). Default = '101' = 700 kHz

- V[2:0] = Over-voltage protection threshold ('000' = 31 V, '111' = 45 V). Default = '111' = 45 V

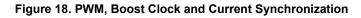

- S[1:0] = Scan mode row count ('00' = 2/8 row, '01' = 3/8 row, '10' = 4/8 row, '11' = 5/8 row). Default = '01' 3/8

- C[1:0] = LED short detection voltage ('00' = disabled, '01' = 3.0 V, '10' = 4.0 V, '11' = 5.0 V). Default = '10' = 4.0 V

- R[3:0] = reserved

#### TEST MODE

The TEST input can be used to place the 34848 into test mode. In this mode, the device is placed in to a predetermined mode of operation as follows:

- · Control register loaded with default values

- All PWM drivers set to 95% duty cycle

- No input data and clock (no CLK, no LS)

- Master device needs to use an on-chip oscillator to serve as the reference frequency to PLL

#### ELECTRICAL PERFORMANCE CURVES

#### TYPICAL PERFORMANCE CURVES (T<sub>A</sub>=25°C)

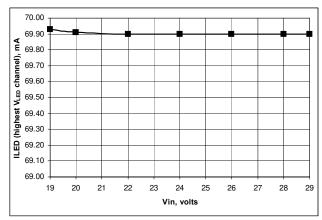

Figure 7. Line Regulation, V<sub>IN</sub> Changing

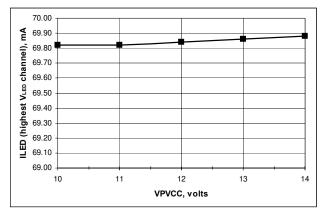

Figure 8. Line Regulation, V<sub>PVCC</sub> Changing

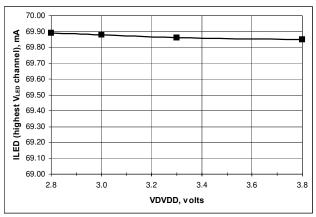

Figure 9. Line Regulation, V<sub>DVDD</sub> Changing

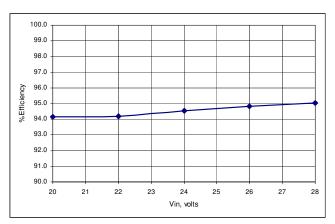

Figure 10. Boost Efficiency vs Input Voltage

Figure 11. Boost Efficiency vs Load Current

Note: Typical Performance Curves were performed under the following conditions:  $f_{SW}$  = 700 kHz,  $V_{IN}$  = 24 V,  $V_{PVCC}$  = 12 V,  $V_{DVDD}$  = 3.3 V, and  $R_L$  = 70  $\Omega$ . The following external components are used: FDS3692 (Boost FET), FDS4675 (Q-FET), L = 22  $\mu$ H (DCR = 54 m $\Omega$ ),  $C_{TOUT}$  = 30  $\mu$ F, SS36-E3 (Schottky diode). The efficiency measurements do not include Q-FET losses.

### FUNCTIONAL DESCRIPTION

#### **INTRODUCTION**

The 34848 is a high efficiency, 8-channel LED driver for use in LCD backlighting applications. The 34848 is designed to support up to 160 mA per channel in scan backlight mode. or 80 mA per channel in local dimming mode. The current reference is set using a single resistor to GND, and LED current tolerance is accurate to ±1% channel-to-channel and IC-to-IC. The current can be programmed in both local dimming and scan modes independently.

Each channel has independent PWM control with 10-bit resolution, programmed via the high speed differential

#### FUNCTIONAL PIN DESCRIPTION

#### **LED CONNECTION (CH1 - CH8)**

LED current driver inputs, with maximum sink current capabilities in local dimming mode of 80 mA, and in scan mode of 160 mA.

#### **POWER GROUND (PGND)**

Power ground of the IC. Internal LED drivers and regulators are referenced to this pin.

#### SHIFT REGISTER DIRECTION (SHL)

The direction of the internal shift register is set by this pin.

#### **TEST MODE (TEST)**

This pin is used to enable the test mode.

#### **SETUP DATA (SETUPD)**

When this pin is high, the configuration registers are set to the default values. When this pin is low, the configuration registers can be programmed via the differential interface.

#### ANALOG GROUND (AGND)

Analog ground of the IC. Internal analog signals are referenced to this pin.

#### PLL NETWORK (PLLC)

PLL compensation network connection.

#### CURRENT REFERENCE SETTING (ISET)

The LED current is set with a 2.0 k resistor connected from this pin to ground. The precision of the resistor is recommended to be no higher than 0.1%.

#### **REFERENCE VOTALGE SUPPLY (REFIO)**

This voltage supply pin is used as a reference for achieving high current matching ratios when two or more ICs are connected together.

interface. The frequency between ICs is synchronized and derived from Controller signals. When the SCAN pin is pulled high, it enables the scan mode. In this mode, each of 8 channels is on for nominally 3/8 (programmable from 2/8 to 5/ 8) of the frame.

The integrated boost controller is used to generate the minimum output voltage required to keep all LEDs illuminated with the selected current, providing the highest efficiency possible. The integrated boost clock can be programmed from 200 kHz and 1.2 MHz using the control interface.

#### **GROUND FOR REFIO SUPPLY (GNDIO)**

Ground reference for the REFIO pin.

#### **ENABLE SCAN MODE (SCAN)**

If this pin is taken high, the IC enters in scan mode from the local dimming mode.

#### **DECOUPLED LOGIC INTERNAL VOLTAGE** (VLOGIC)

This pin is for internal use only, and not to be used for other purposes. A capacitor of 2.2 µF is connected between this pin and ground for decoupling purposes.

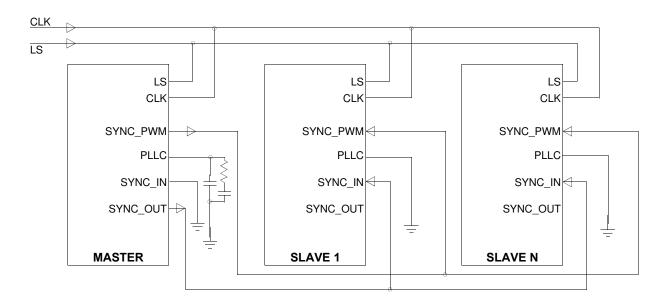

#### BOOST CLOCK OUTPUT (SYNC OUT)

Boost converter frequency is the output on this pin.

#### **DIGITAL GROUND (DGND)**

Digital ground of the IC. Internal digital signals are referenced to this pin.

#### DATA SHIFT REGISTER INPUT/OUTPUT (DIO1/ DIO2)

These pins are used as inputs and outputs to the shift register depending on the status of SHL.

#### LOGIC SUPPLY VOLTAGE (DVDD)

Input voltage pin which ranges from 2.6 to 3.6 V, and used to power the internal logic circuits.

#### CLOCK SIGNALS (CLK+,CLK-)

Differential data clock signals.

#### DATA SIGNALS (DATA+, DATA-)

Differential data signals.

14

#### **SETUP INPUT (SETUP)**

When this pin is taken high, the differential interface programs the data registers and the device is in the setup mode.

#### **RESET\_SCAN INPUT (RESET\_SCAN)**

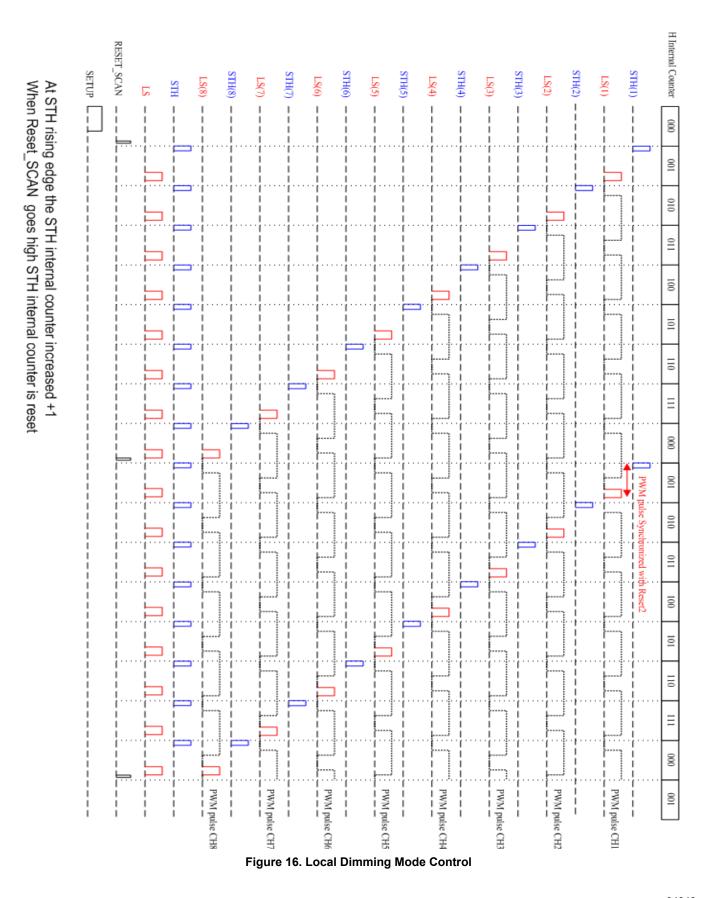

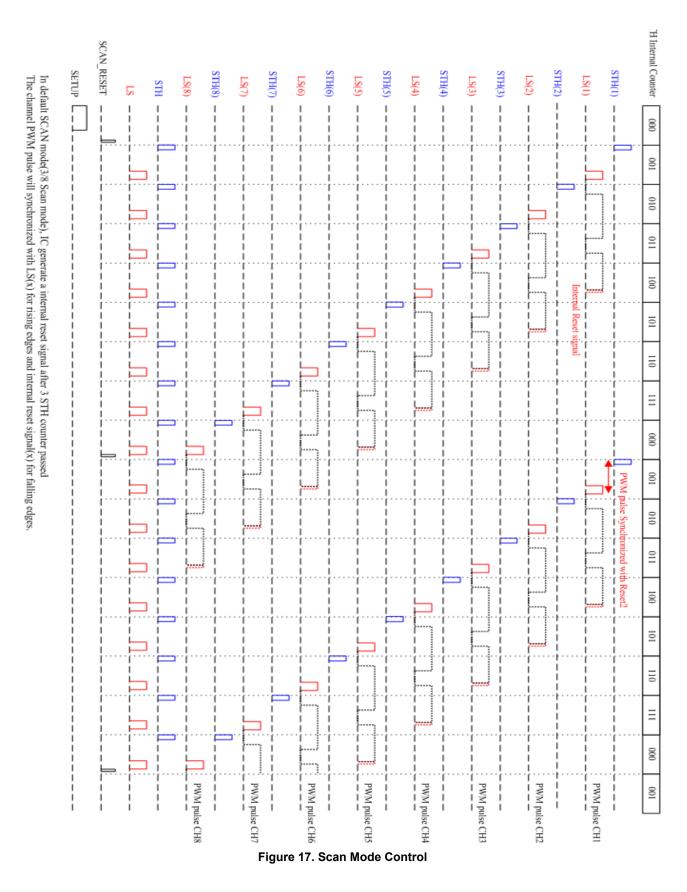

This pin is taken high at the start of each frame to reset the internal counter.

#### DATA LATCH (LS)

When this pin is pulsed, the PWM data in each of the Sample and Hold blocks is transferred to the corresponding PWM controller to start the PWM for the LED driver, and increase the internal counter by 1 in each LED driver device.

#### SHUT\_B

When this pin is high, the boost and LED drivers are enabled.

#### BOOST CLOCK INPUT (SYNC\_IN)

The Boost converter frequency can be synchronized to an external signal if provided at this pin. If this pin is connected to ground, an On-Chip oscillator is used to generate the boost frequency.

#### **PWM SYNC CONNECTIONS (SYNC\_PWM)**

When the IC is operated as a Master, the resulting clock for PWM pulse generation is output on this pin. For Slave chips, this pin acts as an input for the reference clock for the PWM generator.

### DECOUPLED INTERNAL GATE DRIVER VOLTAGE (VDC)

This pin is for internal use only, and not to be used for other purposes. A capacitor of 2.2  $\mu$ F is connected between this pin and ground for decoupling purposes.

#### **BOOST DRIVER SLEW RATE CONTROL (SLEW)**

This pin is used to control the slew rate on the OUT\_SW pin for different application needs. The slew rate can be adjusted by connecting a resistor with a value of 4.7 k, 14 k, or 24 k, from this pin to GND.

#### Q-FET CONTROL (GD)

This pin is used to control the ON/OFF operation of the Q-FET.

#### **BOOST COMPENSATION (COMP)**

Boost converter compensation network connects to this pin.

#### POWER MOSFET DRIVER OUTPUT (OUT\_SW)

Boost converter power MOSFET driver output.

#### **CURRENT SENSE (CS)**

Boost power MOSFET current is sensed across a resistor connected to this pin and ground, as well as for over-current protection (OCP) and current sensing for current mode control.

#### USER PRGRAMABLE OVER-VOLTAGE PROTECTION (OVP)

Over-voltage protection sense pin.

#### SWITCH DRIVER POWER SUPPLY (PVCC)

Input voltage pin that can range from 6.0 to 14 V and used to power the LED drivers and gate drive for the boost controller.

#### FUNCTIONAL INTERNAL BLOCK DESCRIPTION

#### INTERNAL POWER SUPPLY

The internal circuitry of the 34848 uses two separate power supplies. The first is a high voltage input at PVCC that can range from 6.0 to 14 V, and is used to power the LED drivers and gate drive for the boost controller. The external Boost low side FET gate drive is equal to the input voltage at VDC. The second supply is DVDD, which ranges from 2.6 to 3.6 V, and is used to power the internal logic circuits.

Internally there are two regulators, which both have external decoupling capacitors. VDC is used to regulate the PVCC input to produce a constant drive voltage for the internal LED drivers, and is decoupled on the VDC pin. VLOGIC is used to produce 2.5 V for internal logic from the DVDD supply and is decoupled using a capacitor on the VLOGIC pin. If the input voltage at either supply falls below their respective UVLO threshold, the device automatically enters the power down mode. Likewise, operation of the device is only possible when the two input voltages are above the UVLO threshold levels.

In addition to the above, PVCC voltage is also monitored for UVLO.

The SHUT\_B pin can be used to enable/disable the Boost Controller and LED drivers.

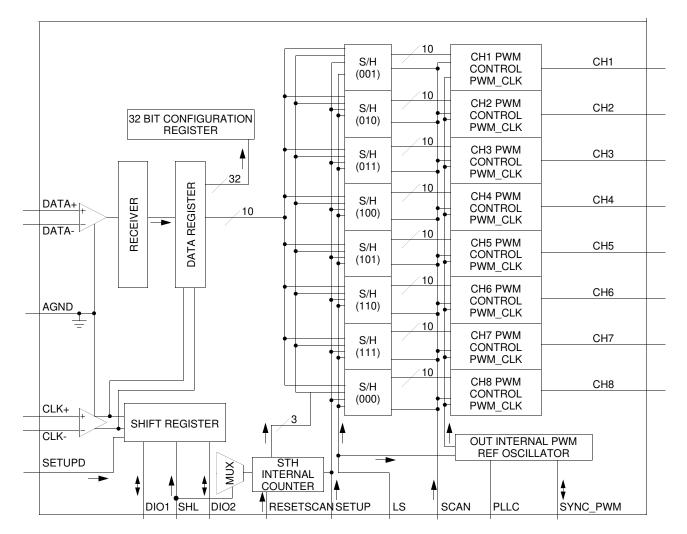

### DIFFERENTIAL INTERFACE AND CONTROL LOGIC

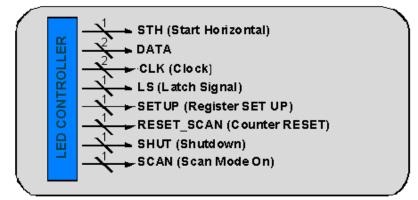

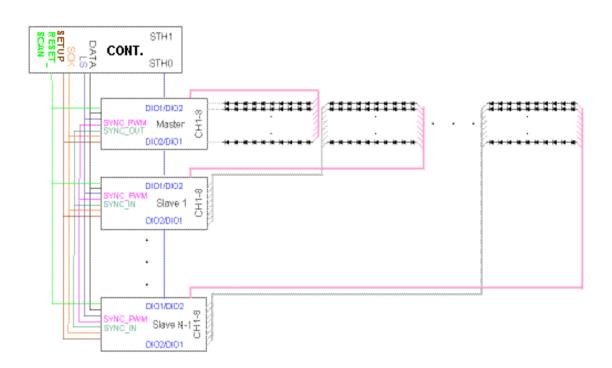

The 34848 uses a differential interface. The clock rate supported is up to 85 MHz. In addition, 6 logic pins are also used as part of the interface.

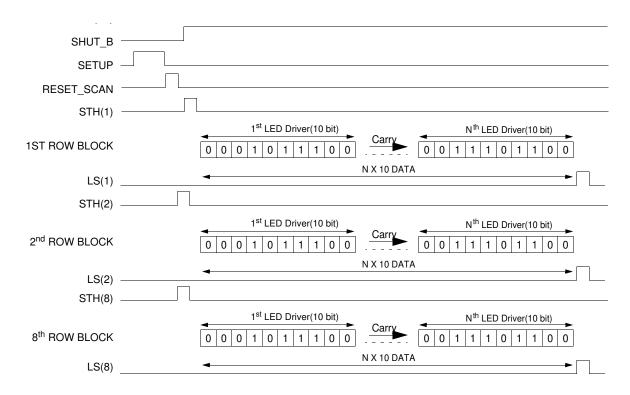

#### Figure 12. Control Interface

When SETUP is taken high the interface programs data registers which are in setting mode. An integrated 10-bit shift register selects which bit is being written. After the pulsing from SETUP and RESET\_SCAN, the STH triggers the PWM

data in from the differential interface. An internal counter (SIC) selects which channel is being written. The 10-bit shift register in multiple devices are connected to generate a long

16

chain of bit selects through all of the LED driver ICs in a system  $(10 \times N \text{ bits. N} = \# \text{ of LED Driver IC}).$

RESET\_SCAN is taken high at the start of each frame to reset the internal counter. Following the STH pulsing the input to the 10-bit register, the Controller is set to 1, which ripples through the connected shift registers with each data write. Once 10-bit data for this LED Driver has been written, the DIO1 (or DIO2) pin is taken high. This latches the data in the Sample and Hold (S/H) of the corresponding PWM channel (selected by SIC counter) for this LED Driver device. The DIO1 (or DIO2) pulsing from this LED Driver is input to the next LED Driver, as its STH signal at DIO2 (or DIO1) pin. Then the next 10-bit data can be written to the S/H of the selected PWM channel for this LED Driver device. This process continues until all the 10-bit data is written to the S/

Hs in all LED Driver ICs, respectively. When LS is pulsed, the 10-bit PWM data is transferred from S/H to the PWM controller to start the PWM for LED driver, and the SIC counter increases by 1 in each LED Driver device.

For multiple devices, another  $10 \times N$  bits are then written for the next selected PWM channels in each LED Drivers using the same procedure. This continues and repeats for the N = 8 PWM channels in each LED Driver device.

The direction of the internal shift register is set using the SHL input. The DIO1 and DIO2 pins are used as inputs and output to the shift register depending on the status of SHL.

The differential interface control also features a default configuration mode for device setup. This is enabled by taking the SETUPD pin high.

Figure 13. Control Register Block Diagram

#### FUNCTIONAL DESCRIPTION FUNCTIONAL INTERNAL BLOCK DESCRIPTION

Analog Integrated Circuit Device Data Freescale Semiconductor

19

#### FUNCTIONAL DESCRIPTION FUNCTIONAL INTERNAL BLOCK DESCRIPTION

34848

#### **PROTECTION FUNCTIONS**

The 34848 monitors the backlighting application from several fault conditions to protect itself and the LED strings. See Protection and Diagnostic Features for a detailed description.

#### **BOOST CONTROLLER**

The integrated boost controller operates in nonsynchronous mode and uses an external boost low side FET. Current is sensed across the sense resistor between the low side FET and ground, and is used for over-current protection (OCP) and current sensing for current mode control.

#### **8 CHANNEL LED CURRENT DRIVER**

The programmable current driver matches the current in up to 8 LED strings to within  $\pm$ 1%. The current can be programmed independently for scan and local dimming modes. In scan mode, the current can be programmed from 121.25 to 160 mA in 32 steps. In local dimming mode, the current range is from 62.5 to 80 mA in 8 steps. To provide this high matching ratio between ICs, the voltage references used in the ICs are connected between each chip using the REFIO and GNDIO pins.

The current driver circuits are also used to disable current flow in the LEDs when the LEDs are in the Off state, or when PWM is off. This enhances the performance of the PWM dimming function by maintaining a constant current through the LEDs when illuminated.

#### FUNCTIONAL DEVICE OPERATION

#### BOOST

An integrated sense circuit is used to sense the voltage at the LED current driver inputs and automatically sets the output voltage to the minimum voltage needed to keep all LEDs biased with the required current. Care has been taken to ensure that the minimum required output voltage (also the minimum VF of the LEDs) is used in order to minimize onchip power dissipation. The boost frequency is programmed in the setup routine (see 'Configuration' below) from 200 kHz to 1.2 MHz, or can be synchronized to an input signal if provided at the SYNC\_IN pin. If SYNC\_IN is connected to GND, an on-chip oscillator is used to generate the boost frequency and the boost frequency is output on the SYNC\_OUT pin. The boost converter also features Over-current Protection (OCP). The OCP operates on a cycle by cycle basis. However, if the OCP condition remains for more than 60 ms then the boost regulator is latched off and GD asserts high to shutoff the Q-FET. The device can only be restarted by recycling the power supply.

The SLEW pin is used to limit the slew on the OUT\_SW pin to reduce noise and avoid EMI problems. If the slew rate is reduced too much, the efficiency of the device will reduce. The slew rate can be changed by tying a resistor from the SLEW pin to GND.

The Boost converter has been designed to operate over a wide range of switching frequencies. <u>Table 9</u> shows the recommended external components to ensure stable operation under all operating conditions.

| Switching Frequency [kHz] | L [µH] | С <sub>О</sub> [µF] | R <sub>COMP</sub> [kΩ] | C <sub>COMP1</sub> [nF] | C <sub>COMP2</sub> [pF] |

|---------------------------|--------|---------------------|------------------------|-------------------------|-------------------------|

| 200                       | 100    | 150                 | 130                    | 1.5                     | 59                      |

| 300                       | 68     | 100                 | 130                    | 1.0                     | 39                      |

| 400                       | 47     | 68                  | 130                    | 0.7                     | 29                      |

| 500                       | 33     | 47                  | 130                    | 0.6                     | 24                      |

| 600                       | 33     | 47                  | 130                    | 0.5                     | 20                      |

| 700                       | 22     | 33                  | 130                    | 0.4                     | -                       |

| 900                       | 22     | 33                  | 130                    | 0.3                     | -                       |

| 1200                      | 15     | 22                  | 130                    | 0.2                     | -                       |

Table 9. Recommended External Components (V<sub>IN</sub> = 24 V ±10%)

The output capacitor  $C_O$  should be a low ESR type, preferably a MLCC. If an electrolytic capacitor is used, a small value ceramic capacitor should be connected in parallel to  $C_O$  to reduce the ESR, thus reducing the output ripple voltage of the converter.

#### **PWM DIMMING**

Each channel has an independently programmable 10-bit PWM generator. The data for the PWM generator is programmed using the differential interface in standard operating mode. If the channel is programmed with 0 duty cycle, that channel is programmed off, and is ignored for automatic output voltage control and for LED failure detection (see Protection and Diagnostic Features).

The PWM generator frequency can be programmed from 177 to 1200 Hz in 1.0 Hz step using a register in the start-up

control registers, and is generated by a PLL using RESET-SCAN as the frequency reference. To operate in Master mode, the SYNC\_IN pin is connected to GND. The resulting clock for PWM pulse generation is output on the SYNC\_PWM pin. A compensation network is connected between the PLLC pin and GND. For Slave mode, the SYNC\_PWM pin acts as an input for the reference clock for the PWM generator. In this manner, one device can be used as the master IC, SYNC\_IN tied to GND, (compensation network on PLLC, and SYNC\_PWM as output) and the remainder as slaves (PLLC grounded, SYNC\_PWM as input) just by connecting the SYNC\_PWM pins together.

The default Frame Frequency is 120 Hz. However, the RESET-SCAN frequency input range can be between 80 and 180 Hz. Therefore, the resulting PWM frequency is given by ( $F_{RESET-SCAN}/120$ ) x  $F_{PWM}$ .

#### SCAN

When the SCAN pin is set high, the 34848 enters scan mode. In this mode, the LED current is set as determined in the IS register. The number of banks illuminated at any one time is set using the configuration register. (See Figure 19) When the scan pin is set low, the 34848 device goes into local dimming mode.

#### **PWM FREQUENCY**

For master mode the PWM frequency is set by the internal register while for slave mode it is synchronized to SYNC\_PWM.

Figure 19. Scan Mode Operation

#### **PROTECTION AND DIAGNOSTIC FEATURES**

#### **OVER-CURRENT PROTECTION**

The boost converter features Over-current Protection (OCP). The OCP operates on a cycle by cycle basis. However, if the OCP condition remains for more than 60 ms then the boost regulator is latched off and GD asserts high to shutoff the Q FET. The device can only be restarted by cycling the power supply.

#### **OVER-VOLTAGE PROTECTION**

The 34848 features user programmable Over-voltage Protection (OVP). The OVP level can be programmed between 31 and 45 V in 2.0 V steps. When OVP is reached, the  $V_{OUT}$  voltage is clamped at the OVP level, and the 50 ms timer is started. If the  $V_{OUT}$  is clamped at the OVP level for more than 50 ms, the  $V_{OUT}$  voltage is lowered by 4.0 V, the DHC is turned off, and another 150 ms timer starts After the 150 ms timer has elapsed, the DHC is turned on again.

If  $V_{OUT}$  drops below the OVP before the 50 ms timer expires, normal operation continues. However, if OVP is still reached after the 50 ms timer expires, the device will repeat the OVP sequence two more times. If the OVP fault condition is still present after the third sequence, the Q-FET, LED drivers, and boost are turned off.

The 34848 uses an internal ADC to measure the voltage level at the OVP pin and compares it with the configured OVP level. A resistor divider network needs to be added between  $V_{OUT}$  and ground, with the center tap connected to OVP. The typical value for the upper divider resistor  $R_{UPPER}$  is 243 k (1%) and 10.7 k (1%) for the lower resistor  $R_{LOWER}$ .

This results in a divider ratio of 23.71 ( $R_{UPPER} + R_{LOWER} / R_{LOWER}$ ), which sets the max OVP value.

The OVP voltage can be programmed from 31 to 45 V.

#### LED OPEN PROTECTION

The 34848 monitors the LED status at all 8 channels. The output voltage is continuously maintained at the minimum voltage possible to drive all LEDs, i.e. the maximum forward voltage of the 8 strings plus the minimum threshold needed (0.5 V, typ) for the current sense circuit and the current driver to regulate.

If an LED fails open, the voltage at the CHx pin for the effected LED string falls close to ground, and therefore the correspondent LED channel will be disabled.

#### LED SHORT PROTECTION

The 34848 also protects against LED short failures. If delta  $V_{FB}$ ,  $|V_{FB\_MAX} - V_{FB\_MIN}|$ , is higher than SFDV and PWM duty of each channels are more than 0%, then this  $V_{FB\_MAX}$  channel is disabled.

#### **OVER-TEMPERATURE PROTECTION**

The 34848 has an on-chip temperature sensor that measures die temperature. If the IC temperature exceeds the OTP threshold, the IC will turn off. While off, the GD pin is set to high-impedance to turn off the Q-FET. The device turns back on after recycling the power.