Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## escale Semiconductor Technical Data

# Configurable Motor Driver IC with Power Supplies

The 34921 power IC integrates multiple motor drivers, multiple power regulators, and most other analog functions a small consumer motion-enabled product needs. The 34921's circuitry is fully protected with current limiting, short-circuit shutdown, over-temperature, over-voltage, and under-voltage detection. Supervisory functions can be read and programmed through a 8-MHz Serial Interface.

A 5.0 V dual-mode (linear or switching) voltage regulator, 3.3 V switching buck regulator, and a voltage-selectable (1.5 V, 1.8 V, 2.5 V) linear regulator provide power management. Two H-Bridges and a configurable motor driver are provided for controlling two dc motors and one unipolar stepper motor.

The highly integrated 34921 brings together sensing, communication, power management, system protection, and motor control in one device.

#### **Features**

- Two Functionally Identical Pulse-Width Modulated (PWM) DC Motor Drivers

- One Switching, One Linear, and One Dual-Mode Regulator

- Dual Mode Switching/Linear 5.0 V Regulator

- Supervisory Functions (Power-ON Reset and Error Reset Circuitry)

- 8-Channel, 8-Bit Analog-to-Digital Converter (ADC)

- · Charge Pump for High-Side MOSFET Drive

- Complete Support for

- · Analog Quadrature Encoder

- · Pb-Free package is designated by suffix AE

## 34921

### H-BRIDGE MOTOR DRIVER AND POWER SUPPLY

| ORDERING INFORMATION |                                        |            |  |  |  |

|----------------------|----------------------------------------|------------|--|--|--|

| Device               | Temperature<br>Range (T <sub>A</sub> ) | Package    |  |  |  |

| MC34921AE/R2         | 0°C to 70°C                            | 64 LQFP-EP |  |  |  |

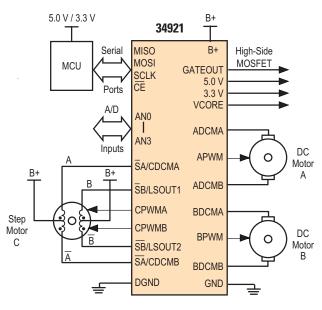

Figure 1. 34921 Simplified Application Diagram

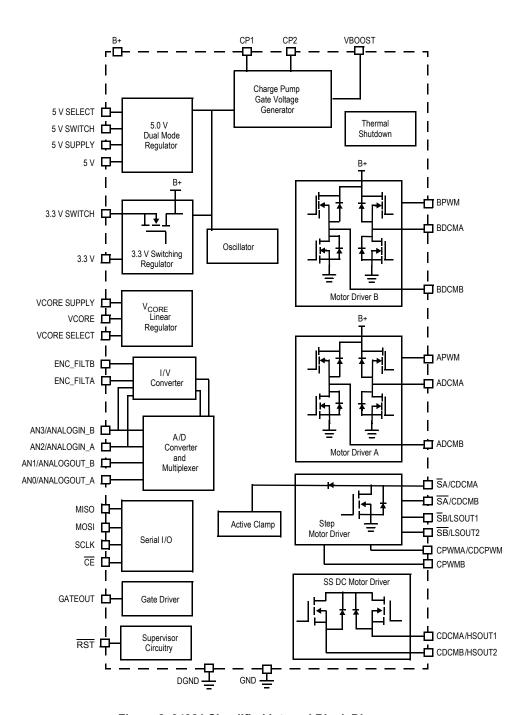

## INTERNAL BLOCK DIAGRAM

Figure 2. 34921 Simplified Internal Block Diagram

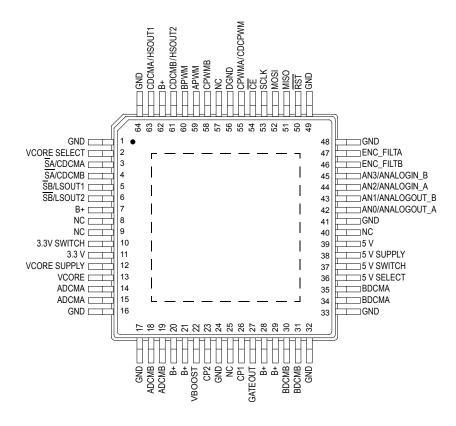

## **TERMINAL CONNECTIONS**

Figure 3. Terminal Function Description

**Table 1. Terminal Function Description**

A functional description of each terminal can be found in the Functional Terminal Description section beginning on page 18

| Terminal                                    | Terminal Name | Formal Name                             | Definition                                    |

|---------------------------------------------|---------------|-----------------------------------------|-----------------------------------------------|

| 1, 16, 17, 24,<br>32, 33, 41,<br>48, 49, 64 | GND           | Ground                                  | Ground.                                       |

| 2                                           | VCORE SELECT  | Core Voltage Output<br>Select           | Core voltage regulator output voltage select. |

| 3                                           | SA/CDCMA      | Unipolar Step A/<br>DC Motor C Output A | Step Motor Output A or DC Motor C Output A.   |

| 4                                           | SA/CDCMB      | Unipolar Step A/ DC Motor C Output B    | Step Motor Output A or DC Motor C Output B.   |

| 5                                           | SB/LSOUT1     | Unipolar Step B/<br>Low-Side 1          | Step Motor Output B or Low-Side Output 1.     |

| 6                                           | SB/LSOUT2     | Unipolar Step B/<br>Low-Side 2          | Step Motor Output B or Low-Side Output 2.     |

| 7, 20, 21, 28,<br>29, 62                    | B+            | Power Supply Input                      | Motor and regulator input voltage.            |

| 8, 9, 25,<br>40, 57                         | NC            | No Connect                              | No internal connection to this terminal.      |

## **Table 1. Terminal Function Description (continued)**

A functional description of each terminal can be found in the Functional Terminal Description section beginning on page 18

| Terminal | Terminal Name   | Formal Name                                   | Definition                                                                 |

|----------|-----------------|-----------------------------------------------|----------------------------------------------------------------------------|

| 10       | 3.3 V SWITCH    | 3.3 V Switching<br>Regulator Switch<br>Output | 3.3 V regulator switching output.                                          |

| 11       | 3.3 V           | 3.3 V Regulator<br>Feedback                   | Feedback terminal for 3.3 V switching regulator and internal logic supply. |

| 12       | VCORE SUPPLY    | Core Voltage<br>Regulator Input               | Core regulator input supply.                                               |

| 13       | VCORE           | Core Voltage<br>Regulator Output              | Core regulator output voltage.                                             |

| 14, 15   | ADCMA           | DC Motor A Output A                           | DC motor driver A output A.                                                |

| 18, 19   | ADCMB           | DC Motor A Output B                           | DC motor driver A output B.                                                |

| 22       | VBOOST          | Boost Voltage                                 | Boost voltage storage node.                                                |

| 23       | CP2             | Switching Capacitor 2                         | Charge pump capacitor connection 2.                                        |

| 26       | CP1             | Switching Capacitor 1                         | Charge pump capacitor connection 1.                                        |

| 27       | GATEOUT         | High-Side MOSFET<br>Gate Driver               | Gate driver for external N-channel switch.                                 |

| 30, 31   | BDCMB           | DC Motor B Output B                           | DC motor driver B output B.                                                |

| 34, 35   | BDCMA           | DC Motor B Output A                           | DC motor driver B output A.                                                |

| 36       | 5 V SELECT      | 5.0 V Regulator Mode<br>Select                | 5.0 V regulator operating mode select.                                     |

| 37       | 5 V SWITCH      | 5.0 V Switching<br>Regulator Switch<br>Output | 5.0 V switching regulator switching output.                                |

| 38       | 5 V SUPPLY      | 5.0 V Regulator Input<br>Supply               | 5.0 V regulator input voltage.                                             |

| 39       | 5 V             | 5.0 V Regulator<br>Feedback                   | 5.0 V regulator feedback.                                                  |

| 42       | AN0/ANALOGOUT_A | AN0/Analogout_A                               | A/D input 0 or analog encoder output A.                                    |

| 43       | AN1/ANALOGOUT_B | AN1/Analogout_B                               | A/D input 1 or analog encoder output B.                                    |

| 44       | AN2/ANALOGIN_A  | AN2/Analogin_A                                | A/D input 2 or analog encoder input A.                                     |

| 45       | AN3/ANALOGIN_B  | AN3/Analogin_B                                | A/D input 3 or analog encoder input B.                                     |

| 46       | ENC_FILTB       | Analog Encoder<br>Channel B Filter            | I/V amplifier channel B filter.                                            |

| 47       | ENC_FILTA       | Analog Encoder<br>Channel A Filter            | I/V amplifier channel A filter.                                            |

| 50       | RST             | Reset                                         | Reset input and output.                                                    |

| 51       | MISO            | Master In Slave Out                           | Serial data out to MCU.                                                    |

| 52       | MOSI            | Master Out Slave In                           | Serial data in from MCU.                                                   |

|          | SCLK            | Serial Clock                                  | Serial data clock.                                                         |

## **Table 1. Terminal Function Description (continued)**

A functional description of each terminal can be found in the Functional Terminal Description section beginning on page 18

| Terminal | Terminal Name | Formal Name                                                 | Definition                                            |

|----------|---------------|-------------------------------------------------------------|-------------------------------------------------------|

| 54       | CE            | Chip Enable                                                 | Serial data strobe.                                   |

| 55       | CPWMA/CDCPWM  | Motor Driver C PWM<br>Input A                               | Step motor driver Phase A PWM or DC motor driver PWM. |

| 56       | DGND          | Digital Ground                                              | Digital ground.                                       |

| 58       | СРШМВ         | Motor Driver C PWM<br>Input B                               | Step motor driver Phase B PWM.                        |

| 59       | APWM          | Motor Driver A PWM<br>Input                                 | PWM input for DC motor driver A.                      |

| 60       | BPWM          | Motor Driver B PWM<br>Input                                 | PWM input for DC motor driver B.                      |

| 61       | CDCMB/HSOUT2  | Motor Driver C DC<br>Motor Output or High-<br>Side Output 2 | Step motor driver C output or high-side output 2.     |

| 63       | CDCMA/HSOUT1  | Motor Driver C DC<br>Motor Output or High-<br>Side Output 1 | Step motor driver C output or high-side output 1.     |

## **MAXIMUM RATINGS**

## **Table 2. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                                                    | Symbol               | Max                           | Unit    |

|-------------------------------------------------------------------------------------------|----------------------|-------------------------------|---------|

| ELECTRICAL Ratings                                                                        |                      |                               |         |

| Input Power Supply Voltage                                                                | B+                   |                               | V       |

| I <sub>B+</sub> = 0.0 A                                                                   |                      | -0.3 to 38                    |         |

| Logic Input Voltage                                                                       | V <sub>IN</sub>      | -0.3 to V <sub>5.0</sub> +0.3 | V       |

| Boost Supply Voltage                                                                      | V <sub>BOOST</sub>   | B <sup>+</sup> +15            | V       |

| Input Power Supply Ripple Voltage                                                         | V <sub>RIPPLEB</sub> |                               | $mV_PP$ |

| Ripple Voltage Measured at < 20 MHz                                                       |                      | 400                           |         |

| Motor Drivers A & B Maximum Output Voltage                                                | V <sub>OUTMAX</sub>  | 40                            | V       |

| 5.0 V Linear Regulator Maximum Output Voltage                                             | V <sub>5.0</sub>     |                               | V       |

| Startup                                                                                   |                      | 5.4                           |         |

| 5.0 V Switching Regulator Maximum Output Voltage                                          | V <sub>5.0</sub>     |                               | V       |

| Startup                                                                                   |                      | 5.4                           |         |

| 3.3 V Switching Regulator Maximum Output Voltage                                          | V <sub>3.3</sub>     |                               | V       |

| Startup                                                                                   |                      | 3.6                           |         |

| VCORE Linear Regulator Maximum Output Voltage                                             | V <sub>CORE</sub>    |                               | V       |

| $I_{CORE} = 0.0 A$                                                                        |                      | V <sub>CORE_NOM</sub> +10%    |         |

| Motor Drivers A, B, and C (Motor Driver C Configured as Step Motor Driver) <sup>(1)</sup> |                      |                               | А       |

| Motor Driver A Sink or Source Current                                                     | I <sub>PWM</sub> (A) | ±4.5                          |         |

| Motor Driver B Sink or Source Current                                                     | I <sub>PWM</sub> (B) | ±4.5                          |         |

| Motor Driver C Sink or Source Current                                                     | I <sub>PWM</sub> (C) | ±1.5                          |         |

| Motor Driver C in Step Mode Step Motor Output Current                                     | I <sub>STEP</sub>    |                               | Α       |

| Output x or $\overline{x}$ On                                                             |                      | 2.0                           |         |

| Motor Driver C in Step Mode Standoff Voltage                                              | V <sub>BVDS</sub>    |                               | V       |

| Output Off, I <sub>DSS</sub> = 10 mA                                                      |                      | 60                            |         |

| ESD Voltage <sup>(2)</sup>                                                                | V <sub>ESD</sub>     |                               | V       |

| Non-Operating, Unbiased, Human Body Model                                                 |                      | ±2000                         |         |

| Machine Model                                                                             |                      | ±200                          |         |

| Charge Device Model                                                                       |                      | ±250                          |         |

## Notes

- 1. B+ = 34 V, Motor Stalled and Saturated

- 2. ESD testing is performed in accordance with the Human Body Model ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ), the Machine Model ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ), and the Charge Device Model.

## Table 2. Maximum Ratings(continued)

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                                | Symbol              | Max        | Unit |

|-----------------------------------------------------------------------|---------------------|------------|------|

| THERMAL RATINGS                                                       |                     |            | 1    |

| Operating Temperature                                                 |                     |            | °C   |

| Ambient                                                               | T <sub>A</sub>      | 0.0 to 70  |      |

| Junction                                                              | TJ                  | 150        |      |

| Storage Temperature                                                   | T <sub>STG</sub>    | -55 to 150 | °C   |

| Thermal Resistance                                                    |                     |            | °C/W |

| Junction to Ambient <sup>(3)</sup>                                    | $R_{	heta JA}$      | 40         |      |

| Junction to Board <sup>(4)</sup>                                      | $R_{	heta JB}$      | 14         |      |

| Junction to Case                                                      | $R_{	heta JC}$      | <1.0       |      |

| Peak Package Reflow Temperature During Solder Mounting <sup>(5)</sup> | T <sub>SOLDER</sub> | 245        | °C   |

| THERMAL RESISTANCE AND PACKAGE DISSIPATION RATINGS                    | <u> </u>            |            | •    |

| Power Dissipation (T <sub>A</sub> = 25° C) <sup>(6)</sup>             | P <sub>D</sub>      | 2.0        | W    |

#### Notes

- 3. 1s PCB test board JESD51-2 and SEMI G38-87.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured at the package center lead foot. 2s2p test board, exposed pad soldered to PCB.

- 5. Terminal soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 6. Maximum power dissipation at indicated ambient temperature in free air with no heatsink used.

## STATIC ELECTRICAL CHARACTERISTICS

## **Table 3. Static Electrical Characteristics**

Characteristics noted under conditions 16 V  $\leq$  B+  $\leq$  34 V, 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C, and 0°C  $\leq$  T<sub>J</sub>  $\leq$  100°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                | Symbol                  | Min                   | Тур                        | Max              | Unit |

|-----------------------------------------------------------------------------------------------|-------------------------|-----------------------|----------------------------|------------------|------|

| Serial Interfaces (MISO, MOSI, SCLK, CE)                                                      |                         | ı                     | L                          | L                |      |

| Input Low Voltage from MCU                                                                    | V <sub>IL</sub>         |                       |                            |                  | V    |

| $V_{5.0}$ = 5.0 V, $V_{3.3}$ = 3.3 V, $I_{IN}$ $\leq$ 200 $\mu$ A, $V_{IN}$ Falling           |                         | 1.1                   | 1.35                       | 2.2              |      |

| Input High Voltage                                                                            | V <sub>IH</sub>         |                       |                            |                  | ٧    |

| $\rm V_{5.0}$ = 5.0 V, $\rm V_{3.3}$ = 3.3 V, $\rm I_{IN}{\leq}200~\mu A,  \rm V_{IN}$ Rising |                         | 1.1                   | 2.00                       | 2.2              |      |

| Input Hysteresis                                                                              | V <sub>HYS</sub>        |                       |                            |                  | V    |

| $V_{5.0} = 5.0 \text{ V}, V_{3.3} = 3.3 \text{ V}$                                            |                         | 0.4                   | 0.6                        | 1.5              |      |

| Output High-Level, MISO ( $V_{5.0} = 5.0 \text{ V}$ , $V_{3.3} = 3.3 \text{ V}$ )             | V <sub>OH</sub> (MISO)  |                       |                            |                  | V    |

| I <sub>OUT</sub> = 150 μA                                                                     |                         | 2.4                   | V <sub>3.3</sub> -25<br>mV | V <sub>3.3</sub> |      |

| $I_{OUT} = 20 \mu A$                                                                          |                         | V <sub>3.3</sub> -0.1 | V <sub>3.3</sub> -10<br>mV | V <sub>3.3</sub> |      |

| Output Low-Level, MISO ( $V_{5.0} = 5.0 \text{ V}, V_{3.3} = 3.3 \text{ V}$ )                 | V <sub>OL</sub> (MISO)  |                       |                            |                  | mV   |

| I <sub>OUT</sub> ≤ 20 μA                                                                      |                         | 0.0                   | 10                         | 100              |      |

| I <sub>OUT</sub> ≤ 150 μA                                                                     |                         | 0.0                   | 25                         | 400              |      |

| Input Pulldown Current                                                                        | I <sub>PULLDOWN</sub>   |                       |                            |                  | μΑ   |

| $V_{5.0}$ = 5.0 V, $V_{3.3}$ = 3.3 V, $V_{IN}$ = 5.0 V, Includes $\overline{RST}$             |                         | 50                    | 120                        | 175              |      |

| MISO High-Impedance Current                                                                   | I <sub>HI-Z</sub>       |                       |                            |                  | μΑ   |

| MISO = 3.3 V or GND                                                                           |                         | -100                  | 0.1                        | 100              |      |

| 5.0 V Linear Regulator                                                                        |                         |                       |                            |                  |      |

| Logic Supply Voltage                                                                          | V <sub>5.0</sub>        |                       |                            |                  | V    |

| $I_{V5.0}$ = 10 mA to 50 mA, 16 V $\leq$ B+ $\leq$ 20 V, $R_{EXT}$ = 140 $\Omega$             |                         | 4.8                   | 5.0                        | 5.2              |      |

| Load Regulation                                                                               | V <sub>ILOAD</sub>      |                       |                            |                  | mV   |

| $I_{LOAD}$ = 10 mA to 50 mA                                                                   |                         |                       |                            |                  |      |

|                                                                                               |                         | -                     | -                          | ±100             |      |

| Current Limit Threshold                                                                       | I <sub>LIMIT</sub>      | _                     | 4.5                        |                  | mA   |

| $R_{EXT} = 0 \Omega$                                                                          |                         | 75                    | 135                        | 600              |      |

| V <sub>5.0</sub> to Turn On/Off V <sub>3.3</sub> Regulator <sup>(7)</sup>                     | V <sub>5_3.3t</sub>     | _                     | 2.2                        | _                | V    |

| Hysteresis for V <sub>5_3.3t</sub> <sup>(7)</sup>                                             | V <sub>5_3.3t_hys</sub> | _                     | 175                        | -                | mV   |

#### Notes

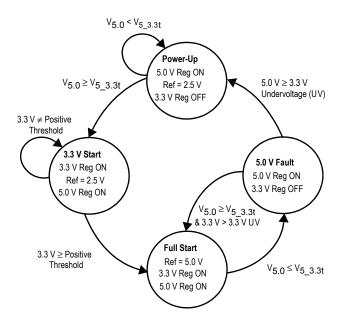

7. See Figure 10, Power-Up Sequencing, page 22.

Characteristics noted under conditions 16 V  $\leq$  B+  $\leq$  34 V, 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C, and 0°C  $\leq$  T<sub>J</sub>  $\leq$  100°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                            | Symbol                  | Min   | Тур  | Max   | Unit |

|---------------------------------------------------------------------------|-------------------------|-------|------|-------|------|

| 5.0 V Switching Regulator                                                 | ,                       |       | •    | •     | •    |

| Vreg Threshold                                                            | V <sub>5.0</sub>        | 4.8   | 5.0  | 5.2   | V    |

| Cycle-by-Cycle Current Limit Threshold                                    | I <sub>LIMIT</sub>      |       |      |       | Α    |

| $V_{5.0} = 2.0 \text{ V to Max}$                                          |                         | 0.75  | 1.2  | 2.25  |      |

| $V_{5.0} \le 1.0 \text{ V}$                                               |                         | -     | 1.0  | _     |      |

| V <sub>5.0</sub> to Turn On/Off V <sub>3.3</sub> Regulator <sup>(8)</sup> | V <sub>5_3.3t</sub>     | _     | 2.2  | _     | V    |

| Hysteresis for V <sub>5_3.3t</sub> <sup>(8)</sup>                         | V <sub>5_3.3t_hys</sub> | _     | 175  | _     | mV   |

| 3.3 V Switching Regulator                                                 |                         | •     | •    | 1     | •    |

| Vreg Threshold                                                            | V <sub>3.3</sub>        | 3.15  | 3.28 | 3.45  | V    |

| Cycle-by-Cycle Current Limit Threshold                                    | I <sub>LIMIT</sub>      |       |      |       | Α    |

| $V_{3.3} = 2.0 \text{ V to Max}$                                          |                         | 2.75  | 3.6  | 5.5   |      |

| $V_{3.3} \le 1.0 \text{ V}$                                               |                         | -     | 3.5  | -     |      |

| VCORE 3.3V Linear Regulator                                               | 1                       | l     |      | 1     |      |

| Voltage Tolerance                                                         | V <sub>CORE_TOL</sub>   |       |      |       | V    |

| $I_{CORE} = 0.02 \text{ A to } 0.3 \text{ A}, V_{NOM} = 2.5 \text{ V}$    | _                       | 2.35  | 2.49 | 2.66  |      |

| $I_{CORE} = 0.02 \text{ A to } 0.3 \text{ A, } V_{NOM} = 1.8 \text{ V}$   |                         | 1.675 | 1.78 | 1.925 |      |

| $I_{CORE} 0 0.02 A to 0.3 A, V_{NOM} = 1.5 V$                             |                         | 1.4   | 1.49 | 1.6   |      |

| Load Regulation                                                           | V <sub>ILOAD</sub>      |       |      |       | mV   |

| $I_{LOAD}$ = 20 mA to 300 mA                                              |                         | _     | ±10  | ±100  |      |

| Current Limit Threshold                                                   | I <sub>LIMIT</sub>      | 400   | 750  | 1200  | mA   |

| Motor Drivers in DC Mode                                                  | 1                       |       |      | I     |      |

| Motor Driver A High- or Low-Side Switch Voltage Drop                      | V <sub>DROP</sub> (A)   |       |      |       | V    |

| I <sub>PWM</sub> = 1.7 A, GND or B+ to Output                             |                         | _     | .65  | 1.5   |      |

| Motor Driver A Output Current Limit                                       | I <sub>LIMIT</sub> (A)  | 3.6   | 4.9  | 7.2   | Α    |

| Motor Driver B High- or Low-Side Switch Voltage Drop                      | V <sub>DROP</sub> (B)   |       |      |       | V    |

| I <sub>PWM</sub> = 2.0 A, GND or B+ to Output                             |                         | _     | .70  | 1.4   |      |

| Motor Driver B Output Current Limit                                       | I <sub>LIMIT</sub> (B)  | 2.8   | 4.9  | 7.2   | Α    |

| Motor Driver C High- or Low-Side Switch Voltage Drop                      | V <sub>DROP</sub> (C)   |       |      |       | V    |

| I <sub>PWM</sub> = 0.375 A, GND or B+ to Output                           |                         | -     | .75  | 1.5   |      |

| Motor Driver C Current Limit—Top Side                                     | I <sub>LIMIT1</sub> (C) | 0.75  | 1.2  | 1.5   | Α    |

| Motor Driver C Current Limit—Bottom Side                                  | I <sub>LIMIT2</sub> (C) | 1.0   | 1.65 | 2.0   | Α    |

#### Notes

8. See Figure 10, Power-Up Sequencing, page 22.

Characteristics noted under conditions 16 V  $\leq$  B+  $\leq$  34 V, 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C, and 0°C  $\leq$  T<sub>J</sub>  $\leq$  100°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                         | Symbol                   | Min                                        | Тур                                      | Max                | Unit |

|--------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------|------------------------------------------|--------------------|------|

| Motor Drivers in DC Mode (cont)                                                                        |                          |                                            |                                          |                    | I    |

| Output MOSFET Leakage Current $V_{GS} = 0.0 \text{ V}, V_{O} = 0.0 \text{ V} \text{ or } 20 \text{ V}$ | I <sub>DSS</sub>         | -                                          | 0.1                                      | ±40                | μА   |

| Current Limit Maximum Duty Cycle <sup>(9)</sup>                                                        | IDC <sub>LIMIT</sub>     | 1.0                                        | 2.0                                      | 4.0                | %    |

| Current Limit Pulse Width <sup>(9)</sup>                                                               | I <sub>LIMITPW</sub>     | 0.5                                        | 1.5                                      | 6.0                | μs   |

| Motor Driver C in Step Mode                                                                            |                          |                                            |                                          |                    |      |

| Switch Voltage Drop, Output to Ground  I <sub>STEP</sub> = 0.375 A, GND to Output                      | V <sub>SDROP</sub>       | -                                          | _                                        | 1.5                | V    |

| Step Motor Current Limit B+ = 20 V                                                                     | I <sub>STEP(LIMIT)</sub> | 1.0                                        | _                                        | 2.0                | А    |

| Voltage at Which Internal Clamp Activates I <sub>DSS</sub> = 1.0 mA, B+ = 20 V                         | V <sub>CLAMP</sub>       | 44                                         | 51                                       | 59                 | V    |

| Tested Maximum High-Voltage Leakage Current $V_S = V_{CLAMP} + 4.0$                                    | I <sub>BREAKDOWN</sub>   | -                                          | 0.5                                      | 40                 | μА   |

| Any Step Driver Output Leakage Current to Ground B+ = 20 V, V <sub>S</sub> = 20 V                      | I <sub>LEAKAGE</sub>     | _                                          | 0.1                                      | 40                 | μΑ   |

| Current Limit Maximum Duty Cycle                                                                       | td <sub>ILIMIT</sub>     | 5.0                                        | 11                                       | 15                 | %    |

| Current Limit Pulse Width                                                                              | I <sub>LIMITPW</sub>     | 5                                          | 10                                       | 20                 | μs   |

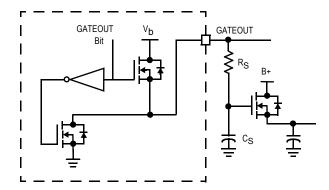

| V <sub>b</sub> Charge Pump                                                                             | <u>.</u>                 |                                            |                                          |                    |      |

| Boost Voltage<br>I <sub>B</sub> = 0.5 mA                                                               | V <sub>b</sub>           | B++10                                      | B <sup>+</sup> +11.5                     | B <sup>+</sup> +15 | V    |

| External N-FET Gate Drive Output                                                                       |                          |                                            |                                          |                    |      |

| GATEOUT High Output $I_{OH}$ = 4.0 mA $I_{OH}$ = 200 $\mu$ A                                           | V <sub>OH2</sub>         | V <sub>b</sub> -6.0<br>V <sub>b</sub> -0.3 | V <sub>b</sub> - 2.5<br>V <sub>b</sub> 1 | V <sub>b</sub>     | V    |

| GATEOUT Low Output<br>I <sub>OL</sub> = -200 μA                                                        | V <sub>OL</sub>          | _                                          | 0.1                                      | 0.3                | V    |

## Notes

9. Motor driver A, B, C Top Side only. For C Bottom Side, see Motor Driver C in Step Mode: Current Limit Maximum Duty Cycle and Current Limit Pulse Width

Characteristics noted under conditions 16 V  $\leq$  B+  $\leq$  34 V, 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C, and 0°C  $\leq$  T<sub>J</sub>  $\leq$  100°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                     | Symbol                   | Min                | Тур   | Max                | Unit                 |

|----------------------------------------------------------------------------------------------------|--------------------------|--------------------|-------|--------------------|----------------------|

| Supervisor Circuitry                                                                               | -                        |                    |       | 1                  | 1                    |

| Minimum Function B+ for Charge Pump, Oscillator Up                                                 | B+                       |                    |       |                    | V                    |

| Reset/Fault Registers Valid (10)                                                                   |                          | 9.0                | -     | _                  |                      |

| Minimum Function V <sub>5.0</sub> for $\overline{\text{RST}}$ Operational                          | V <sub>5.0</sub> RST     |                    |       |                    | V                    |

| $\overline{\text{RST}} \text{ V}_{\text{OL}} \le 0.05 \text{ V} \text{ @ } 1.0 \text{ mA} ^{(10)}$ |                          | 2.0                | _     | _                  |                      |

| Minimum Function V <sub>3.3</sub> for RST Operational                                              | V <sub>3.3</sub> RST     |                    |       |                    | V                    |

| $\overline{RST} \text{ V}_{OL} \le 0.05 \text{ V} \textcircled{@} 1.0 \text{ mA} ^{(10)}$          |                          | 2.0                | -     | _                  |                      |

| RST Low Voltage (11)                                                                               | V <sub>OL</sub>          |                    |       |                    | V                    |

| I <sub>RST</sub> ≤ 5.0 mA                                                                          |                          | _                  | 0.1   | 0.25               |                      |

| RST V <sub>5.0</sub> Threshold                                                                     |                          |                    |       |                    | V                    |

| V <sub>5.0</sub> Rising                                                                            | V <sub>5.0 t+</sub>      | _                  | 4.65  | 4.75               |                      |

| V <sub>5.0</sub> Falling                                                                           | V <sub>5.0 t</sub> –     | 4.5                | 4.6   | 4.70               |                      |

| RST Hysteresis for V <sub>5.0</sub>                                                                | V <sub>HYSV5.0</sub>     | 10                 | 50    | _                  | mV                   |

| RST V <sub>3.3</sub> Threshold                                                                     |                          |                    |       |                    | V                    |

| V <sub>3.3</sub> Rising                                                                            | V <sub>3.3t+</sub>       | -                  | 2.9   | 3.15               |                      |

| V <sub>3.3</sub> Falling                                                                           | V <sub>3.3t</sub> –      | 2.8                | 2.9   | 3.0                |                      |

| RST Hysteresis for V <sub>3.3</sub>                                                                | V <sub>HYS_3.3</sub>     | 10                 | 15    | _                  | mV                   |

| RST V <sub>CORE</sub> Threshold                                                                    |                          |                    |       |                    | %V <sub>CORE</sub> _ |

| V <sub>CORE</sub> Falling                                                                          | V <sub>CORE</sub>        | 85                 | 86    | 90                 | NOM                  |

| RST Hysteresis for V <sub>CORE</sub>                                                               | V <sub>HYS</sub> CORE    | _                  | 10    | _                  | mV                   |

| Overtemperature Junction Temperature <sup>(12)</sup>                                               | T <sub>J(OVER)</sub>     |                    |       |                    | °C                   |

| T <sub>J</sub> Rising                                                                              |                          | 140                | -     | _                  |                      |

| Overtemperature Hysteresis <sup>(12)</sup>                                                         | T <sub>J(HYS)</sub>      |                    |       |                    | °C                   |

| $T_J$ Falling                                                                                      |                          | 10                 | -     | 30                 |                      |

| Thermal Warning <sup>(12)</sup>                                                                    | T <sub>W</sub>           | T <sub>J</sub> -30 | -     | T <sub>J</sub> -20 | °C                   |

| B+ Undervoltage Threshold to Assert RST                                                            | B+ <sub>(FAULT)</sub>    |                    |       |                    | V                    |

| V <sub>5.0</sub> = +5.0 V, B+ Falling                                                              |                          | 12                 | 12.75 | 13.5               |                      |

| B+ Undervoltage Threshold Hysteresis <sup>(13)</sup>                                               | B+ <sub>FAULT(HYS)</sub> | 1.0                | 1.5   | 2.0                | V                    |

| Minimum B+ Necessary to Clear B+ Fault                                                             | B+ <sub>RECOVERY</sub>   |                    |       |                    | V                    |

| $V_{5.0}$ = +5.0 V, B+ Rising                                                                      |                          | _                  | _     | 15.25              |                      |

## Notes

- 10. If any of these conditions for this not is true, then RST is activated until all operating conditions are met.

- 11. The RST terminal uses an external pull-up, which may be to 5.0 V or 3.3 V.

- 12. Guaranteed by design.

- 13. Alternately, the minimum B+ fault threshold voltage must not be lower than 12 V, and the B+ fault clear voltage must not be higher than 15.25 V. The hysteresis may be greater than 2.0 V if this requirement is met.

Characteristics noted under conditions 16 V  $\leq$  B+  $\leq$  34 V, 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C, and 0°C  $\leq$  T<sub>J</sub>  $\leq$  100°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                                                                              | Symbol                  | Min  | Тур  | Max      | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|------|----------|------|

| Analog Encoder Interface Current-to-Voltage Conversion Sta                                                                                                                                  | age                     |      |      |          |      |

| Minimum Offset Current                                                                                                                                                                      | I <sub>OFFSET_MIN</sub> | -6.0 | -8.0 | -10      | μΑ   |

| Midpoint Offset Current                                                                                                                                                                     | I <sub>OFFSET_MID</sub> | -0.5 | 0.0  | 0.5      | μΑ   |

| Maximum Offset Current                                                                                                                                                                      | I <sub>OFFSET_MAX</sub> | 6.0  | 8.0  | 10       | μΑ   |

| Offset Step Size (1 LSB)                                                                                                                                                                    | I <sub>OFFSTEP</sub>    | 0.25 | 0.5  | 0.75     | μΑ   |

| Analog-to-Digital Converter                                                                                                                                                                 |                         |      |      |          |      |

| Resolution, No Missing Codes                                                                                                                                                                | ADC                     | _    | -    | 8.0      | Bits |

| Measurement Range for Correct Conversion                                                                                                                                                    | IMR                     | 0.0  | _    | 5.0      | V    |

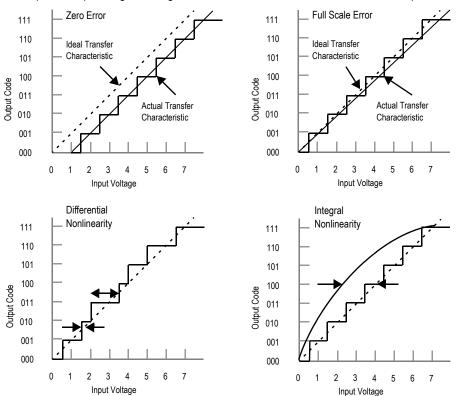

| Linearity Error $^{(16)}$<br>Over Input Voltage Range of 4% to 96% Ideal Measurement Range (IMR) max. Over Time and Temperature $^{(14)}$ , $^{(15)}$<br>$V_{IN}$ = -0.5 to 5.5 V $^{(17)}$ | I <sub>NL</sub>         | -    | 0.4  | ±1.0 LSB | -    |

| Input Leakage Current (ANx) $V_{5.0} = 5.0 \text{ V, T}_{J} = 25^{\circ}\text{C, V}_{ANx} = 5.0 \text{ V, ANALOG\_TEST MODE} = 0, \\ \text{Channel Not Selected}$                           | ILEAKAGE                | -    | 0.1  | 10       | μΑ   |

#### Notes

- 14. Errors include effects of multiplexer and sample and hold circuitry, including droop.

- 15. The Linearity Error is the worst case error caused by the differential and integral nonlinearity.

- 16. An LSB (least significant bit) is defined as follows:

$$LSB = \frac{IMR}{2^{\#BITS}-1} Volts$$

#### Where:

- IMR is the Ideal Measurement Range.

- #BITS is the resolution of the ADC.

- 17. The ADC will read full scale at  $V_{IN}$  = 5.0 V. If  $V_{IN}$  on one input exceeds this value, the value of other inputs may become unreadable.

Characteristics noted under conditions 16 V  $\leq$  B+  $\leq$  34 V, 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C, and 0°C  $\leq$  T<sub>J</sub>  $\leq$  100°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                               | Symbol          | Min | Тур  | Max  | Unit                |

|----------------------------------------------|-----------------|-----|------|------|---------------------|

| Analog-to-Digital Converter (cont)           |                 |     |      |      |                     |

| Zero Error <sup>(18), (19)</sup>             | E <sub>Z</sub>  | _   | ±1.0 | ±8.0 | LSB <sup>(20)</sup> |

| Zero Error Drift                             | E <sub>ZD</sub> |     |      |      | LSB                 |

| Over Time and Temperature <sup>(18)</sup>    |                 | _   | ±4.0 | -    |                     |

| Full Scale Error <sup>(18), (19), (21)</sup> | E <sub>FS</sub> | -   | ±2.0 | ±8.0 | LSB                 |

#### Notes

- 18. Errors include effects of multiplexer and sample and hold circuitry, including droop.

- 19. The Zero Error is defined as the number of LSB values away from the ideal value of 1/2 LSB that the ADC output count will transition from 0 to 1 when the input is swept through the range of interest. The transition must occur within the specified range.

20. An LSB is defined as follows:

LSB =

$$\frac{IMR}{2^{\#BITS}-1}$$

Volts

#### Where:

- IMR is the Ideal Measurement Range.

- #BITS is the resolution of the ADC.

- 21. The Full Scale Error is defined as the number of LSB values away from the ideal value of -1/2 LSB from Full Scale that the ADC output count actually transitions from -1 LSB count to Full Scale count when the input voltage is swept through the voltage range of interest. The transition must occur within the specified range.

### **DYNAMIC ELECTRICAL CHARACTERISTICS**

## **Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions 16 V  $\leq$  B+  $\leq$  34 V, 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C, and 0°C  $\leq$  T<sub>J</sub>  $\leq$  100°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                        | Symbol                          | Min | Тур      | Max      | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----|----------|----------|------|

| Serial Interface Timing <sup>(22)</sup>                                                                                               |                                 |     | l        | l        |      |

| Setup Time for $\overline{\text{CE}}$ to rising edge of SCLK (C <sub>L</sub> = 50 pF)                                                 | t <sub>setup(CE)</sub>          | 15  | _        | _        | ns   |

| Hold Time for $\overline{CE}$ after rising edge of SCLK (C <sub>L</sub> = 50 pF)                                                      | t <sub>hold(Œ)</sub>            | 15  | -        | -        | ns   |

| Setup Time for MOSI to rising edge of SCLK (C <sub>L</sub> = 50 pF)                                                                   | t <sub>setup(MOSI)</sub>        | 15  | -        | -        | ns   |

| Hold Time for MOSI after rising edge of SCLK (C <sub>L</sub> = 50 pF)                                                                 | t <sub>hold(MOSI)</sub>         | 15  | -        | -        | ns   |

| Delay for MISO valid after rising edge of SCLK (C <sub>L</sub> = 50 pF)                                                               | t <sub>delay(MISO)</sub>        | _   | 35       | 55       | ns   |

| Period for SCLK (C <sub>L</sub> = 50 pF)                                                                                              | t <sub>period(SCLK)</sub>       | 125 | _        | 750      | ns   |

| Duty Cycle of SCLK                                                                                                                    | t <sub>duty (SCLK)</sub>        | 45  | _        | 55       | %    |

| 5.0 V Switching Regulator                                                                                                             | ·                               |     | <u>I</u> | <u>I</u> |      |

| Switching Rise and Fall Time Load Resistance = 100 $\Omega$ , B+ = 18 V                                                               | t <sub>r</sub> , t <sub>f</sub> | 10  | 30       | 50       | ns   |

| 3.3 V Switching Regulator                                                                                                             |                                 |     | I.       | l        |      |

| Switching Rise and Fall Time Load Resistance = 100 $\Omega$ , B+ = 18 V                                                               | t <sub>r</sub> , t <sub>f</sub> | 10  | 16       | 50       | ns   |

| Motor Drivers                                                                                                                         |                                 |     | l        | l        |      |

| Motor Drivers A and B Output Waveform Rise Time<br>R = 7.0 $\Omega$ , V <sub>DCX</sub> = (5.0 V) to (0.90 x B+), B+ = 18 V            | t <sub>r</sub>                  | 100 | 175      | 300      | ns   |

| Motor Driver C Output Waveform Rise Time<br>R = 25 $\Omega$ , V <sub>DCX</sub> = (5.0 V) to (0.90 x B+), B+ = 18 V                    | t <sub>r</sub>                  | 100 | 175      | 300      | ns   |

| Output Waveform Fall Time $V_{DCX}$ = (0.90 x B+) to 5.0 V, R = 7.0 $\Omega$ , B+ = 18 V                                              | t <sub>f</sub>                  | 100 | -        | 300      | ns   |

| Crossover Dead Time (23)                                                                                                              | t <sub>dead</sub>               | 15  | 600      | 2000     | ns   |

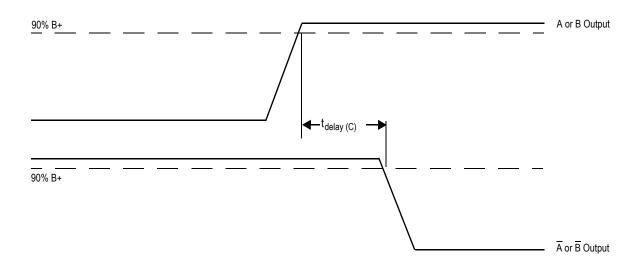

| Motor Driver C in Step Mode                                                                                                           |                                 |     | ı        | ı        | l    |

| Output Rise Time $V_{\text{XPHASE}} = 5.0 \text{ V to } 0.90 \text{ x B+, R}_{\text{W}} = 20 \Omega, \text{ B+} = 18 \text{ V}$       | t <sub>r</sub>                  | 100 | 175      | 350      | ns   |

| Output Fall Time $V_{XPHASE} = 0.90 \text{ x B+ to } 5.0 \text{ V}, R_{W} = 20 \Omega, B+ = 18 \text{ V}$                             | t <sub>f</sub>                  | 100 | 155      | 350      | ns   |

| Delay from Phase Turn-Off to Counterphase Turn-On $R_{W} = 20~\Omega,  0.90~x~B+~Rising \ to \ 0.90~x~B+~Falling,  B+~=~18~V~Falling$ | t <sub>delay</sub> (C)          | 0.0 | 300      | 400      | ns   |

#### Notes

- 22. See Figure 4, Serial Interface Timing, page 16.

- 23. This parameter is guaranteed by design but not production tested.

Characteristics noted under conditions 16 V  $\leq$  B+  $\leq$  34 V,  $0^{\circ}$ C  $\leq$   $T_{A} \leq$  70 $^{\circ}$ C, and  $0^{\circ}$ C  $\leq$   $T_{J} \leq$  100 $^{\circ}$ C unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_{A}$  = 25 $^{\circ}$ C under nominal conditions unless otherwise noted.

| Characteristic                                                                               | Symbol                   | Min                                       | Тур  | Max | Unit              |

|----------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------|------|-----|-------------------|

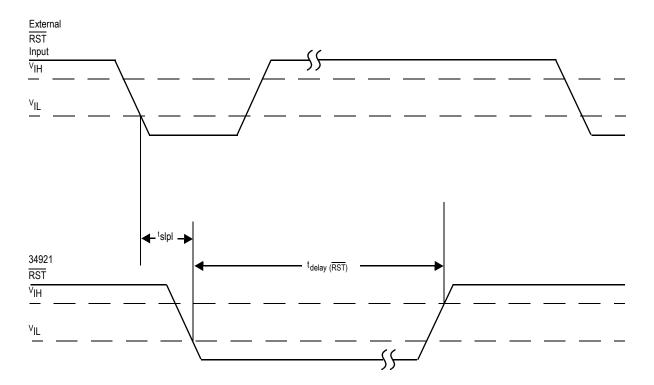

| Supervisor Circuitry                                                                         | <u> </u>                 |                                           | 1    |     |                   |

| RST Delay                                                                                    | t <sub>delay (RST)</sub> |                                           |      |     | t <sub>SCLK</sub> |

| $V_{5.0} = \ge +4.9 \text{ V}^{(24)}$                                                        | ,                        | 128                                       | -    | 128 |                   |

| RST Filter Time                                                                              | t <sub>filter</sub>      |                                           |      |     | μs                |

| $V_{5.0} = 5.0 \text{ V}$                                                                    |                          | -                                         | 3.25 | _   |                   |

| RST Fall Time                                                                                | t <sub>f</sub>           |                                           |      |     | ns                |

| $V_{5.0}$ = 5.0 V, $C_L$ = 100 pF, $I_{PULLUP}$ = 0.75 mA(external), 90% to 10% of $V_{5.0}$ |                          | -                                         | 7.0  | 20  |                   |

| External Input Low to RST Pulled Low                                                         | t <sub>slpl</sub>        |                                           |      |     | ns                |

| $V_{5.0} = 5.0 \text{ V}^{(25)}$                                                             | ·                        | -                                         | 26   | 60  |                   |

| Analog Encoder Interface Variable Gain Stage                                                 | 1                        |                                           | 1    |     | ·I                |

| Adjustable Gain (Ideal)                                                                      | G (Ideal)                |                                           |      |     |                   |

| Settings S = 0 to 15, Default 0                                                              |                          | (1.0+0.1 * S)<br>(1.0+0.1 * [S-16])/0.375 |      |     |                   |

| Settings S = 16 to 31, Default 0                                                             |                          |                                           | ( [  |     |                   |

| Gain                                                                                         | G                        |                                           |      |     | V/V               |

| Setting = 0                                                                                  |                          | 0.8                                       | 1.0  | 1.2 |                   |

| Setting = 31                                                                                 |                          | 6.0                                       | 6.6  | 7.2 |                   |

| Gain Step Factor Tolerance                                                                   | GSF                      |                                           |      |     | V/V               |

| Gain Step Size $Gs/G(s_{-1})$ S = 1 to 31                                                    |                          | 1.01                                      | 1.02 | 1.2 |                   |

| Analog Encoder Interface Digital Signal Conversion Stage                                     |                          |                                           |      |     |                   |

| Operating Frequency                                                                          | f <sub>OP(MAX)</sub>     | 0                                         | -    | 15  | kHz               |

| Comparator Filter Time <sup>(24)</sup>                                                       | t <sub>filter</sub>      |                                           |      |     | SCL               |

| Filter Configuration Bit Set to 0                                                            |                          | 3.0                                       | _    | 4.0 | Cycle             |

| Filter Configuration Bit Set to 1                                                            |                          | 6.0                                       | _    | 7.0 |                   |

| ADC                                                                                          |                          |                                           |      |     |                   |

| Sample and Hold Acquisition Time                                                             | t <sub>sh</sub>          |                                           |      |     | t <sub>SCLF</sub> |

| A/D Speed Bit = 0                                                                            |                          | 15                                        | _    | 16  |                   |

| A/D Speed Bit = 1                                                                            |                          | 31                                        | _    | 32  |                   |

| Conversion Time (Return Word Clocked Out Immediately Following t <sub>c</sub> )              | t <sub>c</sub>           |                                           |      |     | t <sub>SCLK</sub> |

| A/D Speed Bit = 0                                                                            |                          | _                                         | _    | 48  | 1                 |

| A/D Speed Bit = 1                                                                            |                          | -                                         | _    | 96  |                   |

| Master Oscillator                                                                            |                          |                                           |      |     |                   |

| Operating Frequency                                                                          | f <sub>OP</sub>          |                                           |      |     | kHz               |

| D : 4014                                                                                     |                          |                                           |      |     | 1                 |

150

200

250

### Notes

$B+ \ge 12 V$

- 24. Guaranteed by design.

- 25. See Figure 6, RST Timing, page 17.

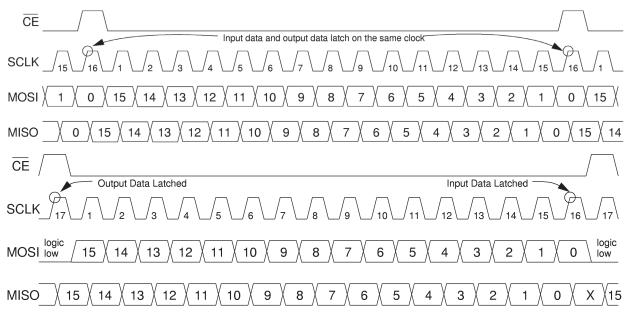

## **TIMING DIAGRAMS**

Figure 4. Serial Interface Timing

Figure 5. Step Motor Crossover Delay Timing

Figure 6. RST Timing

## **FUNCTIONAL DESCRIPTION**

#### INTRODUCTION

The serial interface of the MC34921 is a three input, one output interface similar to a Serial Peripheral Interface (SPI) port in general form, but different in specific clocking requirements due to the fact that an A/D converter cannot reliably run without a continuous clock. The 34921 serial interface communicates to a microcontroller unit (MCU) at up to 16 MHz. The serial signals are SCLK,  $\overline{\text{CE}}$ , MOSI, and MISO. The SCLK signal pin requires a free-running clock (up to 16 MHz) which is provided by the MCU. This signal is required to ensure proper operation of both the ADC and the reset timer circuitry. The serial data transfers between the

MCU and the 34921 via the MOSI and MISO terminals. The serial data from the MCU is handled in the MC34921 via two input registers -- the NORMAL input register contains bits controlling the motor drivers as well as the A/D converter, and the CONFIG register contains bits relating to the general configuration setup of the device. The MC34921 also has two output registers -- the NORMAL output register reports A/D conversion data as well as digital encoder data, and the IREQ output register reports under voltage, temperature, and other device status data.

## **FUNCTIONAL TERMINAL DESCRIPTION**

### **GROUND (GND)**

Main ground. It is used for the B+ filters and motor filter grounds, as well as the ground return for external components which are used with the linear and switching regulators.

## COVER VOLTAGE OUTPUT SELECT (VCORE SELECT)

This terminal is used to select the output voltage provided by the VCORE linear regulator. The VCORE Select potential is latched in during the MC34921's power-on sequence. The MC34921 will not respond to changes in VCORE Select after power up.

## UNIPOLAR STEP A/DC MOTOR C OUTPUT A (SA/CDCMA)

A low-side driver output is configurable for either stepper motor control  $(\overline{S}A)$  or C DC motor (as CDCMA, which requires an external hardwire to pin 63) via the serial I/O. The driver is PWM controlled via the CPWMA/CDCPWM pin, and direction controlled via the Serial I/O. It includes an active voltage clamp, current limit, and thermal shutdown protection.

## UNIPOLAR STEP A/DC MOTOR C OUTPUT B (SA/CDCMB)

A low-side driver output is configurable for either stepper motor control  $(\overline{SA})$  or C DC motor (as CDCMB, it requires external hardwire to pin 61) via the serial I/O. The driver is PWM controlled via the CPWMA/CDCPWM pin, and direction controlled via the Serial I/O. It includes active voltage clamp, current limit, and thermal shutdown protection.

## UNIPOLAR STEP B/LOW-SIDE 1 (SB/LSOUT1)

A low-side driver output is configurable for either stepper motor control (SB) or as a general purpose low-side driver (LSOUT1) via the serial I/O. The SB is PWM controlled via

the CPWMB pin. The direction and LSOUT1 are controlled via the serial I/O. It includes active voltage clamp, current limit and thermal shutdown protection.

## UNIPOLAR STEP B/LOW-SIDE 2 (SB/LSOUT2)

A low-side <u>driver</u> output is configurable for either stepper motor control (SB) or as a general <u>purpose</u> low-side driver (LSOUT2) via the serial I/O. The SB is PWM controlled via the CPWMB pin. The direction and LSOUT2 are controlled via the serial I/O. It includes active voltage clamp, current limit and thermal shutdown protection.

## POWER SUPPLY INPUT (B+)

This is the main power supply input for the regulators and DC motor drivers.

## 3.3 V SWITCHING REGULATOR SWITCH OUTPUT (3.3 V SWITCH)

The high-side driver output is used for the 3.3v switching regulator. It uses the internal 200KHZ clock.

## 3.3 V REGULATOR FEEDBACK (3.3 V)

This terminal is the error amp feedback for the 3.3v switching regulator. It is also the output point for the 3.3v switching supply.

## CORE VOLTAGE REGULATOR INPUT (VCORE SUPPLY)

The input voltage terminal for the VCORE linear supply, which is usually provided by externally hardwiring the 3.3v switching regulator output.

### CORE VOLTAGE REGULATOR OUTPUT (VCORE)

The output terminal of the VCORE linear regulator. Voltage options of 1.5v, 1.8v, or 2.5v are set by the potential of the VCORE Select pin at power up. It features current limit

and thermal shutdown protection. It is typically used to supply a micro processor core or embedded DRAM.

## DC MOTOR A OUTPUT A (ADCMA)

A high-side and low-side driver output terminal, which when combined with ADCMB forms the A H-bridge DC motor driver. The driver is PWM controlled via the APWM input, and direction controlled via the Serial I/O. It features current limit and thermal shutdown protection.

## DC MOTOR A OUTPUT B (ADCMB)

A high-side and low-side driver output terminal, which when combined with ADCMA forms the A H-bridge DC motor driver. The driver is PWM controlled via the APWM input and direction controlled via the Serial I/O. It features current limit and thermal shutdown protection.

### **BOOST VOLTAGE (VBOOST)**

This is the boost voltage storage node for the charge pump circuit. It provides the gate drive voltage for the high-side FETS in the DC motor drivers, switch mode controllers, and Gateout pin.

### **SWTICHING CAPACITOR (CP1 AND CP2)**

These are the connections for the charge pump flying capacitor.

## **HIGH-SIDE MOSFET GATE DRIVER (GATEOUT)**

The output terminal for an external N-channel high-side driver. Enabled via the Serial I/O, it provides gate drive control for an external N-channel MOSFET high-side switch.

## DC MOTOR B OUTPUT B (BDCMB)

A high-side and low-side driver output terminal, which when combined with BDCMB, forms the B H-bridge DC motor driver. The drivers are PWM controlled via the BPWM input, and direction controlled via the Serial I/O. It features current limit and thermal shutdown protection.

### DC MOTOR B OUTPUT A (BDCMA)

A high-side and low-side driver output terminal, which when combined with BDCMA, forms the B H-bridge DC motor driver. The drivers are PWM controlled via the BPWM input, and direction controlled via the Serial I/O. It features current limit and thermal shutdown protection.

## 5.0 V REGULATOR MODE SELECT (5 V SELECT)

This terminal is used to set the 5v regulator to operate in either linear or switching mode. Ground this terminal to operate in switching mode, or float to operate in linear mode.

## 5.0 V REGULATOR SWITCH OUTPUT (5 V SWITCH)

This terminal is the high-side driver output used for the 5v switching regulator. It uses the internal 200KHZ clock.

### **5.0 V REGULATOR INPUT SUPPLY (5 V SUPPLY)**

The input voltage terminal for the 5v regulator. Limit it to 20v in linear mode. An additional series resistor is recommended to dissipate power off-chip.

## 5.0 V REGULATOR FEEDBACK (5 V)

This is the 5v feedback input terminal and output voltage point for the 5v regulator when in the switch configuration, and the output pin when tied to 5v SWITCH in linear configuration. It is also the power supply terminal for the MC34921AE on board logic.

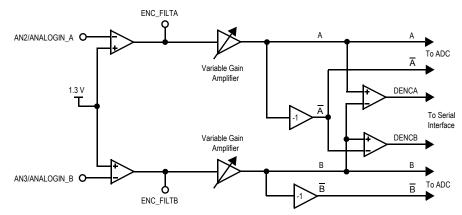

## ANO/ANALOGOUT\_A (ANO/ANALOGOUT\_A)

Mux input 0 for the A/D converter, which is also available in Freescale test mode as an output for the AN2 I/V converter.

## AN1/ANALOGOUT\_B (AN1/ANALOGOUT\_B)

Mux input 1 for the A/D converter, which is also available in Freescale test mode as an output for the AN3 I/V converter.

## AN2/ANALOGIN\_A (AN2/ANALOGIN\_A)

Mux input 2 for the A/D converter incorporating an I/V converter with offset and gain calibration via the Serial I/O.

### AN3/ANALOGIN\_B (AN3/ANALOGIN\_B)

Mux input 3 for the A/D converter incorporating an I/V converter with offset and gain calibration via the Serial I/O.

## ANALOG ENCODER CHANNEL B FILTER (ENC\_FILTB)

Input to the AN3 I/V converter stage for feedback components used with the I/V converter op amp.

## ANALOG ENCODER CHANNEL A FILTER (ENC\_FILTA)

Input to the AN2 I/V converter stage for feedback components used with the I/V converter op amp.

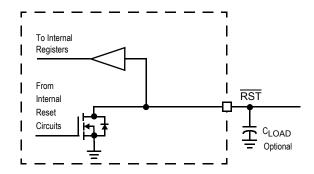

## RESET (RST)

Supervisory function I/O, incorporating a comparator input and an open drain output, and typically connected to the RST of a microprocessor. As an input, RST resets internal registers to default states, turns step motor outputs off, forces DC motor drive low-side drives on, and sets MISO to a high Z state. As an output, RST is set during B+ UVLO, all regulators UVLO, current limit, and thermal shutdown events.

### **MASTER IN SLAVE OUT (MISO)**

This is the master-in-slave-out terminal; the serial output port of the Serial I/O, which typically connects to the MISO of a microprocessor. MISO reports two data frames: NORMAL

- A/D conversion and analog encoder signals, and INFO - Fault data and analog encoder signals.

The output data is loaded into the output shift register on each rising edge of SCLK, while  $\overline{CE}$  is held in a logic high state. This means the MISO pin shows the status of the most significant bit (bit 15) of the output frame until the first rising edge of SCLK after the  $\overline{CE}$  pin is taken to a logic low state. The shift register will then shift data out on the MISO pin on each subsequent rising edge of SCLK while  $\overline{CE}$  is held in the logic low state. During transfers, the most significant bit (MSB) is transferred first. After all 16 bits have been transferred, if any additional clocks are given while  $\overline{CE}$  is in a logic low state, the data is undefined and should be ignored.

### **MASTER OUT SLAVE IN (MOSI)**

This is the master-out-slave-in terminal; the serial input port of the Serial I/O, which typically connects to the MOSI of a microprocessor. It has two frames of operation - NORMAL and CONFIG, which are set by a bit in the NORMAL frame. The MOSI pin is used for serial instruction data input. MOSI information is clocked into the input shift register on the rising edge of SCLK. A logic high state present on MOSI will program a register bit on. The specific bit will turn on with the 16th rising edge of SCLK after placing the  $\overline{\text{CE}}$  pin in a logic low state. Conversely, a logic low state present on the MOSI pin will program the register bit off. The specific bit will turn off with the 16th rising edge of SCLK after placing the CE pin in a logic low state. For each rising edge of the SCLK while CE is logic low, a data bit instruction (on or off) is loaded into the shift register per the data bit MOSI state. The last bit clocked in (bit 0) is the CONFIG bit. If this bit is in a logic high state at the 16th rising edge of SCLK after lowering the CE pin, the bits in the shift register will be loaded into the CONFIG register. If the bit is in a low logic state, the bits will be loaded into the NORMAL register. Care should be taken to keep the MOSI pin in a logic low state when it is not being used for transfers to avoid erroneous data. During transfers, the most significant bit (MSB) is clocked in first.

## **SERIAL CLOCK (SCLK)**

As the serial clock terminal, the SCLK pin clocks the internal shift registers of the MC34921. The serial data input (MOSI) pin data is latched into the input shift register on the rising edge of the 16th clock after the falling edge of the chip select (CE) pin. The serial data output (MISO) pin shifts data out of the shift register on the rising edge of the SCLK signal. False clocking of the shift register must be avoided to ensure validity of data. It is essential that one rising edge of SCLK occur while CE is in a logic high state to ensure the correct output data is latched into the output shift register. Clocking the SCLK pin for more than one clock period while CE is in a logic high state is not recommended and may have undesired effects. For this reason, it is recommended that the SCLK pin be clocked only once while  $\overline{CE}$  is in a logic high state. The MC34921 is designed such that SCLK should be a continuous clock. This ensures that A/D sample rates are held as constant as possible.

## CHIP ENABLE (CE)

The chip enable port of the Serial I/O, typically connects to the  $\overline{\text{CE}}$  of a microprocessor. The logic state of the  $\overline{\text{CE}}$  pin activates clocking in and shifting out of data in and out of the MC34921. While the  $\overline{\text{CE}}$  pin is in the logic high state, the output data in the NORMAL registers and the INFO registers are latched (depending on the state of the IREQ bit in the previous communication frame) in on each rising edge of the clock such that the state of the MSB (bit 15) is readable on the serial data output (MISO) pin. When  $\overline{\text{CE}}$  is in a low logic state both the input shift register and output shift register shift data at the rising edge of SCLK.

## MOTOR DRIVER C PWM INPUT A (CPWMA / CDCPWM)

This is the PWM logic input for the SA/SA/CDCM motor drivers. The motor driver outputs follow this signal.

## MOTOR DRIVER C PWM INPUT B (CPWMB)

This is the PWM logic input for the  $\overline{SB}/\overline{SB}$  motor drivers. The motor driver outputs follow this signal.

### **DIGITAL GROUND (DGND)**

This terminal is used for the Serial I/O and A/D converter logic grounds, and should be kept isolated from the Analog ground on the application PCB.

## MOTOR DRIVER A PWM INPUT (APWM)

The PWM logic input terminal for the ADCM motor drivers. The motor driver outputs follow this signal.

## **MOTOR DRIVER B PWM INPUT (BPWM)**

The PWM logic input terminal for the BDCM motor drivers. The motor driver outputs follow this signal.

## MOTOR DRIVER C STEP MOTOR OUTPUT OR HIGH-SIDE OUTPUT 2 (CDCMB / HSOUT2)

The high-side driver output is configurable for either C DC motor control (as CDCMB, it requires external hardwire to pin 4), or as a general purpose high-side driver (HSOUT2) via the serial I/O. The CDCMB is PWM controlled via the CPWMA/CDCPWM pin. The direction and HSOUT2 are controlled via the serial I/O. It includes current limit and thermal shutdown protection.

## MOTOR DRIVER C STEP MOTOR OUTPUT OR HIGH-SIDE OUTPUT 1 (CDCMA / HSOUT1)

The high-side driver output is configurable for either C DC motor control (as CDCMA, it requires external hardwire to pin 4), or as a general purpose high-side driver (HSOUT1) via the serial I/O. The CDCMA is PWM controlled via the CPWMA/CDCPWM pin. The direction and HSOUT1 are controlled via the serial I/O. It includes current limit and thermal shutdown protection.

#### Supervisorv 3.3 V Regulator DC Motor RST Function Switching Drivers 5.0 V Regulator Step A/D Switching and

Linear

V Core

inear Regulator

Motor Driver

Charge

Pump

Convertor

Timing

Logic

## FUNCTIONAL INTERNAL BLOCK DESCRIPTION

Figure 7. Internal Block Diagram

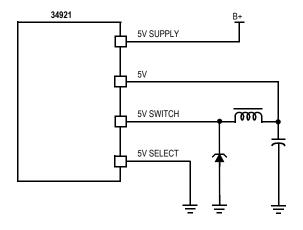

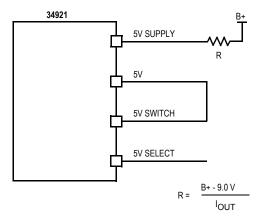

### 5.0 V AND 3.3 V REGULATORS

The 34921 5.0 V regulators have two operating modes switching and linear—that share a dedicated input terminal, as illustrated in Figure 8 and Figure 9. The 5.0 V switching regulator operates off B+ directly. The 5.0 V linear regulator is only used when B+ < 20 V, and the dedicated input terminal is connected to B+ through an external power resistor to dissipate some power off-chip. The regulator that is used depends on the power requirement and B+<sub>NOM</sub> of the application. The designer is able to trade off power versus overall system cost for each particular application. The linear regulator mode is a low-current mode and has much less external component cost.

Figure 8. 5.0 V Switching Regulator Mode

Figure 9. 5.0 V Linear Regulator Mode

The 5V SELECT terminal must be tied to ground for switching regulator mode. An internal pull-up is incorporated in the 34921 sufficient to avoid any problems owing to switching noise on this terminal.

The 5.0 V switching and linear regulators may supply external logic components of the overall assembly, depending on the application. For the 5.0 V linear regulator, an external capacitor on the output should be used for filterina.

### 5.0 V AND 3.3 V SWITCHING REGULATORS