# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Fully integrated octal valve controller system on chip

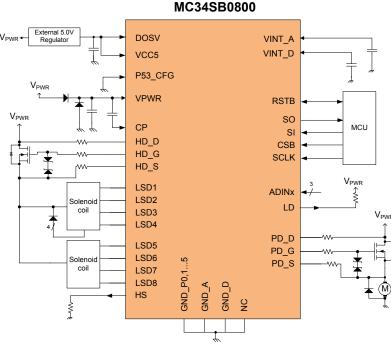

The SB0800 device is a valves and pump controller system designed for use in harsh industrial environments.

It has eight high-current low-side drivers for use with solenoid valves, and highside gate drivers for use with controlling two external N-channel MOSFETs, for DC motor and a master relay for solenoid coils. Alongside this, the SB0800 has three analog to digital converters, plus a low-side driver allowing drive resistive charges. The SB0800 boosts an internal charge pump, permitting the high-side drivers to use inexpensive N-channel MOSFETs. The digital I/O pins can be configured for both 5.0 V and 3.3 V levels for easy connection to any microprocessor. The SB0800 uses standard SPI protocol communication.

The SB0800 is a perfect solution for hydraulic and pneumatic applications. This device is powered by SMARTMOS technology.

#### Features

- Operating voltage 6.0 V to 36 V

- · Eight valves control

- · Four current regulated valves up to 2.25 A (5.0 kHz)

- Four PWMed valves up to 5.0 A (5.0 kHz)

- · High-side predriver for valves protection

- · Pump motor predriver up to 500 Hz PWM

- 16-bit SPI interface with watchdog

- Three 10-bit ADC channels

- High-side driver for general purpose (R\_{DS(on)} 1.0  $\Omega)$

- Low-side driver for resistive charge ( $R_{DS(on)}$  14.0  $\Omega$ )

- Die temperature warning

- Supervision

### Applications

Industrial Controller

- Spot Welding

- Fluid Coating

- Temperature Control

- Brake Pressure

- Laser Cutting

- Bottle Moulding

- Filling Pressure

- 3D Printer

- Oxygen Concentrator

- · Medical test equipment

- · Dialysis machines

- Blood pressure

- Soda dispensers

- Heavy equipment and construction machinery

- Fork lifts

- Water control system for irrigation (connected to farm tractor)

- Food control in animal farm

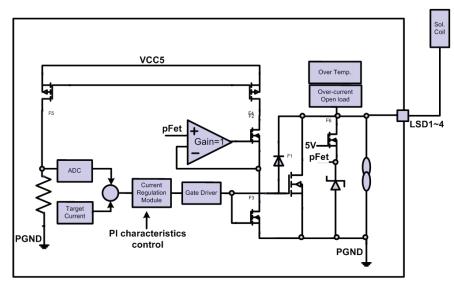

Figure 1. SB0800 simplified 5.0 V application diagram

\* This document contains certain information on a new product.

Specifications and information herein are subject to change without notice.

© 2016 NXP B.V.

# 1 Orderable parts

This section describes the part numbers available to be purchased along with their differences. Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to <a href="http://www.nxp.com">http://www.nxp.com</a> and perform a part number search for the following device numbers.

#### Table 1. Orderable part variations

| Part number                    | Temperature (T <sub>A</sub> ) | Package             | Description                                                                                                                                                                                                                                           | Notes |

|--------------------------------|-------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 34SB0800 octal valves and pump | o controller system on chip   | o for industrial    | l                                                                                                                                                                                                                                                     |       |

| MC34SB0800AE                   | -40 °C to 125 °C              | 10 x 10, 64 LQFP-EP | <ul> <li>Four PWMed valve controls and four current regulated valve controls</li> <li>Safe switch control</li> <li>Pump motor control up to 500 Hz</li> <li>High-side driver for general purpose</li> <li>Low-side FET for resistive loads</li> </ul> | (1)   |

Notes

1. To order parts in Tape & Reel, add the R2 suffix to the part number.

# **Table of Contents**

| 1 | Orderable parts                        | 2  |

|---|----------------------------------------|----|

| 2 | Internal block diagram                 | 4  |

| 3 | Pin connections                        | 5  |

|   | 3.1 Pinout diagram                     | 5  |

|   | 3.2 Pin definitions                    | 6  |

| 4 | General product characteristics        | 8  |

|   | 4.1 Maximum ratings                    | 8  |

|   | 4.2 Operating conditions               | 9  |

|   | 4.3 Supply currents                    | 10 |

|   | 4.4 Thermal ratings                    | 10 |

|   | 4.5 Logical inputs and outputs         | 11 |

| 5 | General description                    | 12 |

|   | 5.1 Block diagram                      | 12 |

|   | 5.2 Functional description             | 12 |

|   | 5.3 Features                           | 12 |

| 6 | Functional block description           | 14 |

|   | 6.1 Error handling                     | 14 |

|   | 6.2 High-side driver                   | 16 |

|   | 6.3 Pump motor pre-driver              | 17 |

|   | 6.4 Low-side driver                    | 19 |

|   | 6.5 Low-side driver for resistive load | 24 |

|   | 6.6 Analog to digital converter (x3ch) | 26 |

|   | 6.7 High-side                          | 27 |

|   | 6.8 Monitoring module                  | 29 |

|   | 6.9 Supervision                        | 31 |

|   | 6.10 SPI and data register             | 37 |

| 7 | Typical applications                   | 32 |

|   | 7.1 Application diagrams               | ô2 |

| 8 | Packaging                              | 33 |

|   | 8.1 Package mechanical dimensions      | 63 |

| 9 | Revision history                       | 37 |

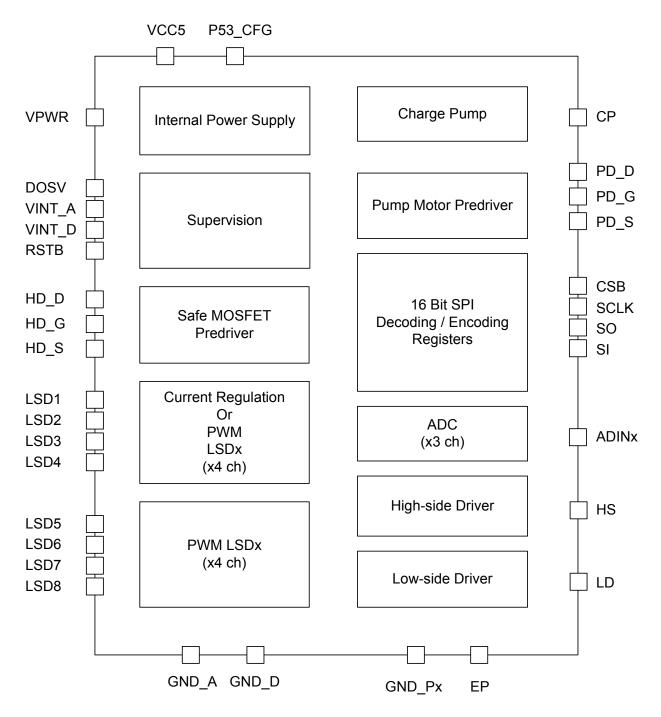

# 2 Internal block diagram

Figure 2. SB0800 simplified internal block diagram

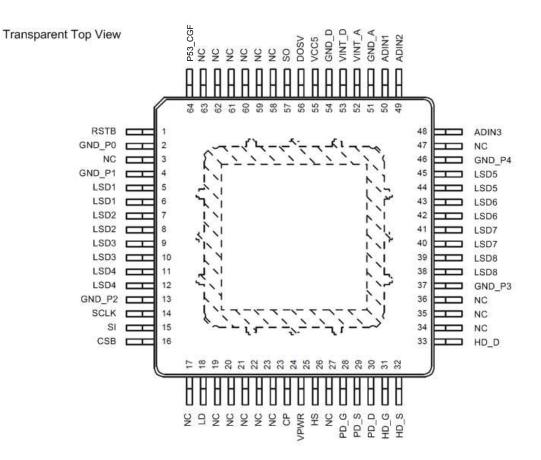

# 3 Pin connections

# 3.1 Pinout diagram

Figure 3. SB0800 64-pin LQFP-EP pinout diagram

# 3.2 Pin definitions

### Table 2. SB0800 pin definitions

| Pin<br>number         | Pin name | Pin function                                         | Definition                                                                            | DOSV =<br>5.0 V | DOSV =<br>3.3 V | Notes |

|-----------------------|----------|------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------|-----------------|-------|

| 1                     | RSTB     | Reset                                                | Reset PIN                                                                             | external        | pull-up         |       |

| 2                     | GND_P0   | Supply                                               | Power Ground 0 <sup>(4)</sup>                                                         | no              | no              |       |

| 4                     | GND_P1   | Supply                                               | Power Ground 1                                                                        | no              | no              | (4)   |

| 5, 6                  | LSD1     | Low-side Driver for Current Regulated & PWMed Valves | Open Drain Output for Low-side Driver 1                                               | no              | no              | (2)   |

| 7, 8                  | LSD2     | Low-side Driver for Current Regulated & PWMed Valves | Open Drain Output for Low-side Driver 2                                               | no              | no              | (2)   |

| 9, 10                 | LSD3     | Low-side Driver for Current Regulated & PWMed Valves | Open Drain Output for Low-side Driver 3                                               | no              | no              | (2)   |

| 11, 12                | LSD4     | Low-side Driver for Current Regulated & PWMed Valves | Open Drain Output for Low-side Driver 4                                               | no              | no              | (2)   |

| 13                    | GND_P2   | Supply                                               | Power Ground 2                                                                        | no              | no              | (4)   |

| 14                    | SCLK     | SPI                                                  | SPI Interface Clock Input                                                             | no              | no              |       |

| 15                    | SI       | SPI                                                  | SPI Interface Digital Input                                                           | no              | no              |       |

| 16                    | CSB      | SPI                                                  | SPI Interface Chip Interface                                                          | no              | no              |       |

| 18                    | LD       | Low-side Driver                                      | Open Drain Output for Low-side                                                        | no              | no              |       |

| 24                    | CP       | Charge Pump                                          | Charge Pump Output. For internal use, connect a storage capacitor of > 68 nF to VPWR. | no              | no              |       |

| 25                    | VPWR     | Supply                                               | Supply PIN connect to battery through reverse diode                                   | no              | no              |       |

| 26                    | HS       | High-side Driver for General Purpose (optional)      | High-side driver for general purpose                                                  | no              | no              |       |

| 28                    | PD_G     | Motor Pump Driver                                    | Gate Output to Control Pump Motor FET<br>Connect to gate of external pump motor FET   | no              | no              |       |

| 29                    | PD_S     | Motor Pump Driver                                    | Source Feedback Pump Motor FET<br>Connect to source of external pump motor FET        | no              | no              |       |

| 30                    | PD_D     | Motor Pump Driver                                    | Drain Feedback Pump Motor FET<br>Connect to drain of external pump motor FET          | no              | no              |       |

| 31                    | HD_G     | High-side Driver for Valve's Fail-safe<br>FET        | Gate Output to Control High-side FET<br>Connect to gate of external pump motor FET    | no              | no              |       |

| 32                    | HD_S     | High-side Driver for Valve's Fail-safe<br>FET        | Source Feedback High-side FET<br>Connect to source of external High-side FET          | no              | no              |       |

| 33                    | HD_D     | High-side Driver for Valve's Fail-safe<br>FET        | Drain Feedback High-side FET<br>Connect to drain of external High-side FET            | no              | no              |       |

| 37                    | GND_P3   | Supply                                               | Power Ground 3                                                                        | no              | no              | (4)   |

| 38, 39 <sup>(2)</sup> | LSD8     | Low-side Driver for PWMed Valves                     | Open Drain Output for Low-side Driver 8                                               | no              | no              |       |

| 40, 41 <sup>(2)</sup> | LSD7     | Low-side Driver for PWMed Valves                     | Open Drain Output for Low-side Driver 7                                               | no no           |                 |       |

| 42, 43 <sup>(2)</sup> | LSD6     | Low-side Driver for PWMed Valves                     | Open Drain Output for Low-side Driver 6                                               | no no           |                 |       |

| 44, 45 <sup>(2)</sup> | LSD5     | Low-side Driver for PWMed Valves                     | Open Drain Output for Low-side Driver 5                                               | no              | no              |       |

| 46                    | GND P4   | Supply                                               | Power Ground 4                                                                        | no no           |                 | (4)   |

| 48                    | ADIN3    | ADC                                                  | Analog to Digital Input 3                                                             | no              | no              | . ,   |

### Table 2. SB0800 pin definitions (continued)

| Pin<br>number                            | Pin name | Pin function      | Definition                                               | DOSV =<br>5.0 V | DOSV =<br>3.3 V | Notes |

|------------------------------------------|----------|-------------------|----------------------------------------------------------|-----------------|-----------------|-------|

| 49                                       | ADIN2    | ADC               | Analog to Digital Input 2                                | no              | no              |       |

| 50                                       | ADIN1    | ADC               | Analog to Digital Input 1                                | no              | no              |       |

| 51                                       | GND_A    | Supply            | Analog Ground                                            | no              | no              |       |

| 52                                       | VINT_A   | Internal Function | 2.5 V internal supply for analog                         | no              | no              | (2)   |

| 53                                       | VINT_D   | Internal Function | 2.5 V internal supply for digital                        | no              | no              | (2)   |

| 54                                       | GND_D    | Supply            | Digital Ground                                           | no              | no              |       |

| 55                                       | VCC5     | Supply            | 5.0 V Supply PIN                                         | 5V              | 5V              |       |

| 56                                       | DOSV     | Supply            | Digital Output Voltage Supply, DOSV under voltage reset  | 5V              | 3.3V            |       |

| 57                                       | SO       | SPI               | SPI Interface Digital Output                             | DOS             | / bias          |       |

| 64                                       | P53_CFG  | Supply            | Input to select output voltage at DOSV (5.0 V/<br>3.3 V) | no              | no              |       |

| 20, 21, 22,<br>23, 58, 59,<br>60, 61, 62 | NC       | Not connected     | Pin used for production tests and must not be no no      |                 | no              |       |

| 3, 17, 19,<br>27, 34, 35,<br>36, 47, 63  | NC       | Not connected     | Pin used for production tests and must be grounded       | e no no         |                 |       |

| Exposed<br>pad                           | GND_P5   | Supply            | Power Ground 5                                           | no              | no              | (4)   |

Notes

2. Pins must be shorted together

3. 220 nF/10 V capacitor needed

4. All GND\_Px pins must be shorted together at the PCB level.

# 4 General product characteristics

### 4.1 Maximum ratings

### Table 3. Maximum ratings

Voltage parameters are absolute voltages referenced to GND\_A, GND\_D and flag (tied together internally). Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol               | Description (rating)                        | Min.                             | Max.                           | Unit | Notes |

|----------------------|---------------------------------------------|----------------------------------|--------------------------------|------|-------|

| Supply               |                                             |                                  | 1                              |      |       |

| V <sub>VPWR</sub>    | Analog Power supply voltage                 | -0.3                             | 40                             | V    |       |

| V <sub>DOSV</sub>    | Digital Output Supply Voltage               | -0.3                             | 7.0                            | V    |       |

| V <sub>P53_CFG</sub> | Selection of 5.0 V or 3.3 V for the digital | -0.3                             | 7.0                            | V    |       |

| V <sub>VCC5</sub>    | Digital power supply voltage                | -0.3                             | 7.0                            | V    |       |

| $V_{GND_A}$          | Ground analog                               | -0.3                             | 0.3                            | V    |       |

| $V_{GND_D}$          | Ground digital                              | -0.3                             | 0.3                            | V    |       |

| $V_{GND_P}$          | Ground exposed pad                          | -0.3                             | 0.3                            | V    |       |

| nternal functior     | 1                                           |                                  | 1                              |      |       |

| V <sub>VINT_A</sub>  | Internal regulator analog power supply      | -0.3                             | 3.0                            | V    |       |

| V <sub>VINT_D</sub>  | Internal regulator digital power supply     | -0.3                             | 3.0                            | V    |       |

| Charge pump          |                                             |                                  |                                |      |       |

| V <sub>CP</sub>      | Internal charge pump                        | -0.3 or<br>V <sub>PWR</sub> -0.3 | V <sub>PWR</sub> +15           | V    |       |

| ligh-side driver     | for general purpose                         |                                  | 1                              |      |       |

| V <sub>HS</sub>      | High-side driver                            | -0.3                             | 40 or V <sub>PWR</sub><br>+0.3 | V    |       |

| ligh-side driver     | for valve's fail-safe FET                   |                                  |                                |      |       |

| $V_{HD_G}$           | Gate of the high-side predriver             | -20                              | 55                             | V    |       |

| $V_{HD_S}$           | Source of the high-side predriver           | -0.3                             | 40                             | V    |       |

| $V_{HD_D}$           | Drain of the high-side predriver            | -0.3                             | 40                             | V    |       |

| Notor pump driv      | /er                                         |                                  |                                |      |       |

| V <sub>PD_G</sub>    | Gate of the Motor Pump predriver            | -0.3                             | 55                             | V    |       |

| V <sub>PD_S</sub>    | Source of the Motor Pump predriver          | -0.3                             | 40                             | V    |       |

| V <sub>PD_D</sub>    | Drain of the Motor Pump predriver           | -0.3                             | 40                             | V    |       |

| Reset                |                                             | I                                |                                |      |       |

| V <sub>RSTB</sub>    | Reset pin                                   | -0.3                             | 7.0                            | V    |       |

| A to D converte      | ſ                                           | L                                |                                |      |       |

| V <sub>ADINx</sub>   | Input analog to digital                     | -0.3                             | 7.0                            | V    |       |

|                      |                                             |                                  | 1                              |      | -     |

### Table 3. Maximum ratings (continued)

Voltage parameters are absolute voltages referenced to GND\_A, GND\_D and flag (tied together internally). Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                 | Description (rating)                                                  | Min.    | Max.         | Unit | Notes |

|------------------------|-----------------------------------------------------------------------|---------|--------------|------|-------|

| SPI                    |                                                                       | ·       |              |      | •     |

| V <sub>SO</sub>        | Serial peripheral interface slave output                              | -0.3    | DOSV +0.3    | V    |       |

| V <sub>SI</sub>        | Serial peripheral interface slave input                               | -0.3    | 7.0          | V    |       |

| V <sub>CSB</sub>       | Serial peripheral interface chip select                               | -0.3    | 7.0          | V    |       |

| V <sub>SCLK</sub>      | Serial peripheral interface clock                                     | -0.3    | 7.0          | V    |       |

| Low-side driver        | for valves (LSD1-8)                                                   |         |              |      |       |

| V <sub>LSDx</sub>      | Low-side driver for valves                                            | Table_  | active clamp |      |       |

| Low-side driver        |                                                                       | •       |              |      | 1     |

| $V_{LD}$               | Low-side driver                                                       | -100 mA | 40           | V    |       |

| Energy capabilit       | y .                                                                   | •       |              |      | 1     |

| E <sub>LSD1-4</sub>    | Energy capability (EAR) at 125 °C<br>• LSD1—4, with 20 mH load        | _       | 30           | mJ   |       |

| E <sub>LSD5—8</sub>    | Energy capability (EAR) at 125 °C<br>• LSD5—8, with 20 mH load        | _       | 40           | mJ   |       |

| E <sub>HS</sub>        | Energy capability (EAR) at 125 °C<br>• HS, with 20 mH load            | _       | 13           | mJ   |       |

| Currents               |                                                                       |         |              |      | •     |

| I <sub>LSDX(POS)</sub> | Drain continuous current; during on state <ul> <li>LSDx</li> </ul>    | _       | 5.0          | А    |       |

| I <sub>LSDX(NEG)</sub> | Maximum negative current for 5.0 ms without being destroyed<br>• LSDx | -6.0    | _            | А    |       |

| I <sub>DIG</sub>       | Input current<br>• P53_CFG, SI, CSB, SCLK, RSTB                       | -20     | 20           | mA   |       |

### 4.2 Operating conditions

This section describes the operating conditions and the current consumptions. Conditions apply to all the following data, unless otherwise noted.

### Table 4. Operating conditions

Voltage parameters are absolute voltages referenced to GND. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol            | Description (rating)                                                                                                   | Min. | Тур. | Max. | Unit | Notes |

|-------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| V <sub>PWR</sub>  | <ul><li>Functional operating supply voltage. Device is fully functional.</li><li>All features are operating</li></ul>  | 6.0  | _    | 36   | V    |       |

| V <sub>CC5</sub>  | <ul><li>Functional operating supply voltage. Device is fully functional.</li><li>All features are operating.</li></ul> | 4.75 | _    | 5.25 | V    |       |

| V <sub>DOSV</sub> | <ul><li>Functional operating supply voltage. Device is fully functional.</li><li>All features are operating.</li></ul> | 3.13 | _    | 5.25 | V    |       |

#### **Supply currents** 4.3

This section describes the operating conditions and the current consumptions. Conditions apply to all the following data, unless otherwise noted.

#### Table 5. Supply currents

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, 4.75 V  $\leq$  V<sub>CC5</sub>  $\leq$  5.25 V, 3.13 V  $\leq$  V<sub>DOSV</sub>  $\leq$  5.25 V, -40 °C  $\leq$  T<sub>J</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                    | Description (rating)                                            | Min. | Тур.     | Max.     | Unit | Notes |

|---------------------------|-----------------------------------------------------------------|------|----------|----------|------|-------|

| VPWR current consumptions |                                                                 | 1    | <u>.</u> | <u>.</u> |      | +     |

| I <sub>QVPWR</sub>        | Quiescent current of VPWR measured at 36 V, $V_{CC5}$ = 0 V     | —    | —        | 30       | μA   |       |

| I <sub>VPWR</sub>         | Current of VPWR in operating mode, $V_{CC5}$ = 5.0 V            | —    | 20       | —        | mA   |       |

| VCC5 current co           | nsumptions                                                      |      |          |          |      |       |

| I <sub>VCC5</sub>         | Current of VCC5 pin in operating mode (SPI frequency at 10 MHz) | —    | 10       | —        | mA   |       |

| DOSV current co           | DOSV current consumptions                                       |      |          |          |      |       |

| I <sub>DOSV</sub>         | Current of DOSV pin in operating mode (SPI frequency at 10 MHz) | —    | —        | 10       | mA   |       |

#### **Thermal ratings** 4.4

#### Table 6. Thermal data

| Symbol            | Description (rating)                                                                    | Min. | Тур. | Max.   | Unit | Notes  |

|-------------------|-----------------------------------------------------------------------------------------|------|------|--------|------|--------|

| TJ                | Operational junction Temperature                                                        | -40  | _    | 150    | °C   |        |

| T <sub>STG</sub>  | Storage Temperature                                                                     | -65  | _    | 150    | °C   |        |

| R <sub>θJC</sub>  | $R\theta JC,$ Thermal Resistance, Junction to Case (Package exposed pad) - Steady state | _    | _    | 2.0    | °C/W |        |

| T <sub>PPRT</sub> | Peak Package Reflow Temperature During Reflow                                           | _    | _    | Note 7 | °C   | (5)(6) |

Notes

Lead soldering temperature limit is for 10 seconds maximum duration. Lead soldering can be done twice. Device must be delivered in dry pack. 5.

NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and 6. Moisture Sensitivity Levels (MSL), Go to www.nxp.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

## 4.5 Logical inputs and outputs

### Table 7. Logical inputs/outputs

$V_{PWR}$  = 6.0 to 36 V, VCC5 = 4.75 to 5.25 V, DOSV = 3.13 to 5.25 V, T<sub>J</sub> = -40 to 125 °C, unless otherwise specified.

| Symbol            | Description (rating)                                                      | Min.       | Max. | Unit | Notes |

|-------------------|---------------------------------------------------------------------------|------------|------|------|-------|

| Logical inputs    |                                                                           |            |      | L    |       |

| V <sub>IH_X</sub> | Input High-voltage<br>• P53_CFG, RSTB, SI, CSB, SCLK, ADIN1, ADIN2, ADIN3 | _          | 2.0  | V    |       |

| V <sub>IL_X</sub> | Input Low-voltage<br>• P53_CFG, RSTB, SI, CSB, SCLK, ADIN1, ADIN2, ADIN3  | 0.8        | _    | v    |       |

| Logical outputs   |                                                                           |            |      |      |       |

| V <sub>OH_X</sub> | Input High-voltage, with 1.0 mA • SO                                      | 0.8 x DOSV | _    | V    |       |

| V <sub>OL_X</sub> | Input Low-voltage, with 1.0 mA<br>• SO                                    | _          | 0.4  | V    |       |

| VOL_RSTB          | RSTB Low-voltage, with 1.0 mA<br>• RSTB                                   | _          | 0.4  | V    |       |

# 5 General description

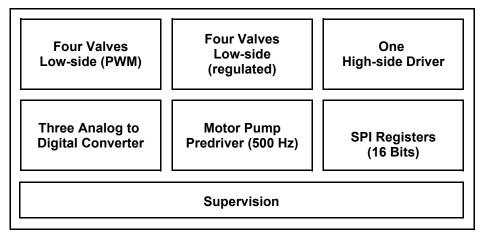

### 5.1 Block diagram

Figure 4. SB0800 functional block diagram

### 5.2 Functional description

The SB0800 device is a valves and pump controller, designed for use in harsh industrial environments, requiring few external components. The SB0800 eight high-current low-side drivers for use with solenoid valves, and high-side gate drivers for controlling two external N-channel MOSFETs for use with a pump motor and master relay for a solenoid coil. In conjunction with this primary functionality, the SB0800 has one low-side driver to control a resistive load. The SB0800 boosts an internal charge-pump, allowing the high-side drivers to use inexpensive N-channel MOSFETs. The digital I/O pins can be configured for both 5.0 V and 3.3 V levels for easy connection to any microprocessor. Also, the device integrated three Analog to Digital converters. The SB0800 uses standard SPI protocol for communication.

### 5.3 Features

This section presents the detailed features of SB0800.

### Table 8. Device features set

| Function                             | Description                                                                                                                                                                                                                |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-side Driver for Fail-safe FET   | <ul> <li>High-side Fail-safe FET driver</li> <li>Overcurrent shutdown</li> <li>Load leakage detection</li> </ul>                                                                                                           |

| High-side Driver for general purpose | <ul> <li>High-side switch connected to VPWR (1.0 Ω max Rds(on) at 125 °C)</li> <li>Open load detection</li> <li>V<sub>DS</sub> state monitoring</li> <li>Overcurrent shutdown</li> <li>Overtemperature shutdown</li> </ul> |

| Pump Driver                          | <ul> <li>Pump motor driver up to 500 Hz PWM frequency controllable through SPI command or a digital signal</li> <li>Overcurrent shutdown between external FET drain and source</li> </ul>                                  |

### Table 8. Device features set (continued)

| Function                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low-side solenoid driver (x4)    | <ul> <li>Solenoid driver (300 mΩ max. R<sub>DS(on)</sub> at 125 °C) works either as current regulator or as PWM</li> <li>Current regulation deviation: ±2.0%</li> <li>Configurable PWM frequency from 3.0 kHz to 5.0 kHz</li> <li>PWM duty cycle 10-bit resolution</li> <li>Open load detection</li> <li>V<sub>DS</sub> state monitoring</li> <li>Overcurrent shutdown</li> <li>Overtemperature shutdown</li> <li>Send current regulation error flag (only for current regulation modules)</li> </ul> |

| Low-side solenoid driver (x4)    | <ul> <li>Solenoid driver (225 mΩ max R<sub>DS(ON)</sub> at 125 °C) are PWM low-side driver</li> <li>Configurable PWM frequency from 3.0 kHz to 5.0 kHz</li> <li>PWM duty cycle resolution 0.39%</li> <li>Open load detection</li> <li>V<sub>DS</sub> state monitoring</li> <li>Overcurrent shutdown</li> <li>Overtemperature shutdown</li> <li>Max switch-off energy 40 mJ</li> </ul>                                                                                                                 |

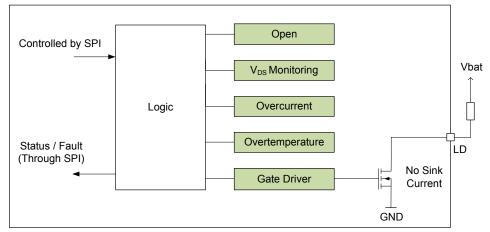

| Low-side resistive Driver        | <ul> <li>Low-side driver (20 mA max, R<sub>DS(on)</sub> 8.0 Ω)</li> <li>Open load detection</li> <li>V<sub>DS</sub> state monitoring</li> <li>Overcurrent shutdown</li> <li>Overtemperature shutdown</li> </ul>                                                                                                                                                                                                                                                                                       |

| Low-side Driver                  | <ul> <li>Low-side driver (350 mA max, R<sub>DS(on)</sub> 1.0 Ω)</li> <li>Open load detection</li> <li>V<sub>DS</sub> state monitoring</li> <li>Overcurrent shutdown</li> <li>Overtemperature shutdown</li> </ul>                                                                                                                                                                                                                                                                                      |

| Analog to Digital Converter (x3) | <ul> <li>10-bit ADC</li> <li>External ADINx pins</li> <li>Internal voltages and temperature information</li> <li>Allow to control the pump by a MCU</li> <li>Allow to control the low-side resistive driver by a MCU</li> </ul>                                                                                                                                                                                                                                                                       |

| Supervision                      | <ul> <li>VINT_x undervoltage (internal regulator)</li> <li>VCC5 &amp; DOSV undervoltage (supply voltage from external)</li> <li>Watchdog fault</li> <li>ALU check counter overflow</li> <li>External reset fault</li> <li>VPWR undervoltage and overvoltage detections</li> <li>Mismatch MAIN-AUX OSC CLK</li> <li>Temperature warning</li> <li>SPI failure</li> <li>Charge pump issue</li> <li>GND supervision</li> </ul>                                                                            |

# 6 Functional block description

## 6.1 Error handling

### Table 9. Error handling

| Type of error                                     | Detection condition              | Action                                                      | Clear SPI flag                                         | Restart condition                                                                              | Notes |

|---------------------------------------------------|----------------------------------|-------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------|-------|

| High-side driver                                  |                                  | 1                                                           |                                                        | 1                                                                                              | 1     |

| Overcurrent between external FET Drain and Source | ON                               | HD_G Off + SPI fault flag (HD_oc)                           | Write 1 to HD_clr_flt 1                                | Write 1 to HD_clr_fit and then<br>turn on by SPI command<br>(hd_on)                            |       |

| Load leakage                                      | hd_on rise-<br>edge (SPI<br>bit) | Ignore hd_on rise-edge command<br>+ SPI fault flag (HD lkg) | Write 1 to HD_clr_flt                                  | Write 1 to HD_clr_flt and then<br>turn on by SPI command<br>(hd_on)                            |       |

| Pump motor PWM driver                             |                                  |                                                             |                                                        |                                                                                                |       |

| Overcurrent between external FET Drain and Source | ON                               | PD_G Off+ SPI fault flag (PD_oc)                            | Write 1 to PD_clr_flt                                  | Write 1 to PD_clr_flt and then<br>turn-on by SPI command (pd<br>on)                            |       |

| LSDx                                              |                                  | ·                                                           |                                                        |                                                                                                |       |

| Open Load                                         | OFF                              | SPI flag only (LSDx_op)                                     | Read diagnosis                                         | No                                                                                             |       |

| V <sub>DS</sub> state monitoring                  | ON/OFF                           | Read V <sub>DS</sub> state by SPI (vds_LSDx)                | update with min filter time<br>(T1) rise and fall edge | No                                                                                             |       |

| Overcurrent                                       | ON                               | OFF fault FET only + SPI fault flag<br>(LSDx_oc)            | Write 1 to LSD_clr_flt                                 | Write 1 to LSD_clr_flt and turn<br>on by SPI command (LSDx<br>duty cycle or current set point) |       |

| Overtemperature                                   | ON                               | OFF fault FET only + SPI fault flag<br>(LSDx_ot)            | Write 1 to LSD_clr_flt                                 | Write 1 to LSD_clr_flt and turn<br>on by SPI command (LSDx<br>duty cycle or current set point) |       |

| Current regulation error<br>(only for LSD1-4)     | ON                               | Read SPI flag only (LSDx_crer)                              | Read diagnosis                                         | No                                                                                             |       |

| LDx                                               |                                  |                                                             |                                                        |                                                                                                |       |

| Open Load                                         | OFF                              | SPI flag only (LDx_op)                                      | Read diagnosis                                         | No                                                                                             |       |

| $V_{\text{DS}}$ state monitoring                  | ON/OFF                           | Send $V_{DS}$ state by SPI ( $V_{DS_{LD}}$ )                | update with min filter time<br>(T1) rise and fall edge | No                                                                                             |       |

| Overcurrent                                       | ON                               | OFF fault FET only + SPI fault flag<br>(LD_oc)              | Write 1 to LD_clr_flt                                  | Write 1 to LD_clr_flt and turn<br>on by SPI command (LD_on)                                    |       |

| Overtemperature                                   | ON                               | OFF fault FET only + SPI fault flag<br>(LD_ot)              | Write 1 to LD_clr_flt                                  | Write 1 to LD_clr_flt and turn<br>on by SPI command (LD_on)                                    |       |

| HS                                                |                                  |                                                             |                                                        |                                                                                                |       |

| Open Load                                         | OFF                              | SPI flag only (HS_ op)                                      | Read diagnosis                                         | No                                                                                             |       |

| $V_{DS}$ state monitoring                         | ON/OFF                           | Send V <sub>DS</sub> state by<br>SPI (V <sub>DS_HS</sub> )  | update with min filter time                            | No                                                                                             |       |

| Overcurrent                                       | ON                               | OFF fault FET only + SPI fault flag<br>(HS_oc)              | Write 1 to HS_clr_fit                                  | Write 1 to HS_clr_flt and then<br>turn on by SPI command<br>(HS_ on)                           |       |

### Table 9. Error handling (continued)

| Type of error   | Detection condition | Action                                         | Clear SPI flag        | Restart condition                                                   | Notes |

|-----------------|---------------------|------------------------------------------------|-----------------------|---------------------------------------------------------------------|-------|

| Overtemperature | ON                  | OFF fault FET only + SPI fault flag<br>(HS_ot) | Write 1 to HS_clr_flt | Write 1 to HS_clr_flt and then<br>turn on by SPI command<br>(HS_on) |       |

#### Supervision

| VINT_x Undervoltage                                   | All except<br>Sleep mode        | SPI register reset & Vint_uv go to<br>High                                                                            | Read Vint_uv bit                                                                  | No                                                                                            |     |

|-------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----|

| VCC5 & DOSV Undervoltage                              | All except<br>Sleep mode        | SPI register reset except VCC5_uv<br>go to High                                                                       | Wait undervoltage reset filter<br>time T1<br>(see <u>Table 19</u> )               | See <u>Table 19,</u>                                                                          |     |

| External reset fault                                  | No internal<br>RSTB<br>pulldown | SPI registers go to initial state                                                                                     | Read the Message 0 of SPI<br>register<br>(see <u>Table 19</u> )                   | See <u>Table 19,</u>                                                                          |     |

| VPWR Undervoltage                                     | RSTB is high<br>state           | All LSDx Off (Clear all LSDx duty<br>cycle registers or current set point)<br>+ SPI fault flag (V <sub>PWR_UV</sub> ) | <ol> <li>Normal condition</li> <li>Read diagnosis (V<sub>PWR_UV</sub>)</li> </ol> | 1. Normal condition<br>2. Turn on by SPI command<br>(LSDx duty cycle or current set<br>point) |     |

| VPWR Overvoltage                                      | RSTB is in<br>high state        | All LSDx Off (Clear all LSDx duty<br>cycle registers or current set point)<br>+ SPI fault flag (V <sub>PWR_OV</sub> ) | 1. Normal condition<br>2. Read diagnosis<br>(V <sub>PWR_OV</sub> )                | 1. Normal condition<br>2. Turn on by SPI command<br>(LSDx duty cycle or current set<br>point) |     |

| Mismatch SB0800 MAIN-AUX<br>OSC CLK                   | RSTB is in<br>high state        | SPI registers goes to initial state<br>low except, see <u>Table 27</u>                                                | Read RST_clk bit                                                                  | No                                                                                            |     |

| Temperature Warning                                   | RSTB is in<br>high state        | SPI flag                                                                                                              | <ol> <li>Normal condition</li> <li>Read diagnosis</li> </ol>                      | No                                                                                            |     |

| SPI Failure                                           | RSTB is in<br>high state        | SPI flag (Fmsg)                                                                                                       | Read diagnosis                                                                    | No                                                                                            |     |

| V <sub>PRE</sub> 10 Monitoring                        | RSTB is in<br>high state        | Send by SPI (ADC)                                                                                                     | No                                                                                | No                                                                                            | (9) |

| V <sub>PRE</sub> 12 Monitoring                        | RSTB is in<br>high state        | Send by SPI (ADC)                                                                                                     | No                                                                                | No                                                                                            | (9) |

| VINT_x Monitoring                                     | RSTB is in<br>high state        | Send by SPI (ADC)                                                                                                     | No                                                                                | No                                                                                            | (9) |

| V <sub>cp_vpwr</sub> Monitoring                       | RSTB is in<br>high state        | Send by SPI (ADC)                                                                                                     | No                                                                                | No                                                                                            |     |

| Temperature Monitoring                                | RSTB is in<br>high state        | Send by SPI (ADC)                                                                                                     | No                                                                                | No                                                                                            | (9) |

| GND_D Supervision                                     | RSTB is in<br>high state        | SPI flag only (FGND)                                                                                                  | No                                                                                | No                                                                                            |     |

| GND_A Supervision; indirect detection by VCC5 or DOSV | RSTB is in<br>high state        | SPI flag only (VCC5_UV or<br>DOSV_UV)                                                                                 | No                                                                                | No                                                                                            |     |

Notes

7. If xxx\_clr\_flt is written "1" by SPI, all SPI flags are set "0", so SW engineer has to read the SPI flag first and then write xxx\_clr\_flt to default value "0".

SW engineering can monitor internal supply voltage in real time with ADC reading, and can use fail-safe function. If these ADC results are not in a certain range, uC can reset the SB0800 (see ADC section).

9. Fail-safe switch off until power is off

### 6.2 High-side driver

### 6.2.1 Function description

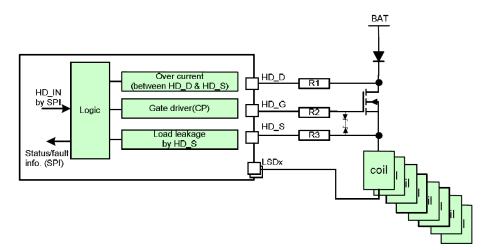

The high-side driver is intended to control the fail-safe switch for the overall solenoid path, and HD\_G is controlled by the SPI command.

Figure 5. High-side driver

### 6.2.2 High-side driver and fault protection

### 6.2.2.1 Overcurrent

High-side driver protects the external n-channel power FET on HD\_G in overcurrent conditions. The drain-source voltage of the FET on HD\_G is checked if the high-side driver is switched on. If the measured drain-source voltage exceeds the overcurrent voltage threshold, the output of the overcurrent comparator is enabled. If the output of the comparator is active longer than the defined filter time, the output HD\_G is switched off. Overcurrent detection logic has a masking time from hd\_on turn-on against malfunctions on transient time. After switching off the power FET on HD\_G by an overcurrent condition, the power FET can be turned back to a "normal state" by a SPI write 1 to the "HD\_clr\_fit" register, and then turned on by a SPI command.

### 6.2.2.2 Load leakage detection

Each time HD\_G is turned on, the ILCdet current is sourced out of the HD\_S pin for the time  $t_{HD_LC}$ , to check the external leakage current on the node in the application. The high-side switch on HD\_G is turned on if the measured voltage is over the detection threshold. If this test fails, HD\_G does not turn-on and the fault flag is set to high. The power FET can be turned back to a "normal state" only by a SPI write 1 to the "HD\_clr\_flt" register, and then turned on by a SPI command. When the power FET is switched off, the gate capacitance of the FET is discharged by a constant current, which is controlled fast and slow by a SPI command (HPD\_sr).

### 6.2.2.3 External components of high-side driver

For protection, external resistors  $R_{HD_D}$ ,  $R_{HD_G}$ , and  $R_{HD_S}$  are required (for example:  $R_{HD_D} = 100 \Omega$ ,  $R_{HD_G} = 100 \Omega$ ,  $R_{HD_S} = 100 \Omega$ ). The zener clamping is necessary to protect the gate and source. The zener chains are used for avalanche clamping and protection against transients.

### Table 10. High-side driver electrical characteristics

$V_{PWR}$  = 6.0 to 36 V, VCC5 = 4.75 to 5.25 V, DOSV = 3.13 to 5.25 V, T<sub>J</sub> = -40 to +125 °C, unless otherwise specified.

| Symbol                   | Characteristic                                                                                                                                                                                                                                                                                                    | Min. | Тур. | Max.                                                                                          | Unit | Notes |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------------------------------------------------------------------------------------------|------|-------|

| HD_G                     |                                                                                                                                                                                                                                                                                                                   |      |      |                                                                                               |      |       |

| V <sub>HD_ON</sub>       | $\begin{array}{l} \text{HD}\_G \text{ switch-on voltage - with pd\_on: PWMat 500 Hz, 50\% duty cycle} \\ \text{through the SPI} \\ \bullet 5.5 \ V \leq V_{PWR} < 6.0 \ V \\ \bullet 6.0 \ V \leq V_{PWR} < 7.0 \ V \\ \bullet 7.0 \ V \leq V_{PWR} < 10 \ V \\ \bullet 10 \ V \leq V_{PWR} < 36 \ V \end{array}$ |      | <br> | V <sub>PWR</sub> + 15<br>V <sub>PWR</sub> +15<br>V <sub>PWR</sub> +15<br>V <sub>PWR</sub> +15 | V    |       |

| V <sub>HD_OFF</sub>      | HD_G switch-off voltage                                                                                                                                                                                                                                                                                           |      | _    | 1                                                                                             | V    |       |

| t <sub>HD_ON</sub>       | Turn-on time - After t <sub>HD_LC</sub>                                                                                                                                                                                                                                                                           | _    | _    | 1.4                                                                                           | ms   |       |

| I <sub>HD_OFF_SLOW</sub> | Turn-off current slow - $V_{HD_G}$ > 2.0 V. HPD_sr = 0                                                                                                                                                                                                                                                            | 70   | 100  | 200                                                                                           | μA   |       |

| I <sub>HD_OFF_FAST</sub> | Turn-off current fast - V <sub>HD_G</sub> > 2.0 V, HPD_sr = 1                                                                                                                                                                                                                                                     | 1.0  | 2.0  | 4.5                                                                                           | mA   |       |

| HD_S                     | •                                                                                                                                                                                                                                                                                                                 |      |      | 1 1                                                                                           |      |       |

| ILEAK_HD_SRC             | Leakage current - 0 $\leq$ V <sub>HD_S</sub> $\leq$ 36 V, 6.0 $\leq$ VPWR $\leq$ 36 V                                                                                                                                                                                                                             | _    | _    | 50                                                                                            | μA   |       |

| HD_D                     |                                                                                                                                                                                                                                                                                                                   |      |      |                                                                                               |      |       |

| L <sub>LEAK_HD_DRN</sub> | Leakage current - VCC5 = DOSV = 0 V,<br>HD_D = PD_D = V <sub>PWR</sub> = 36 V                                                                                                                                                                                                                                     | _    | _    | 10                                                                                            | μA   |       |

| Overcurrent dete         | ction                                                                                                                                                                                                                                                                                                             |      |      |                                                                                               |      |       |

| V <sub>HD_OC</sub>       | Overcurrent detection threshold - $V_{HD_D}$ - $V_{HD_S}$ , $R_{DRN}$ , $R_{SRC}$ = 100 $\Omega$                                                                                                                                                                                                                  | -15% | 1.0  | +15%                                                                                          | V    |       |

| Load leakage cur         | rent detection                                                                                                                                                                                                                                                                                                    |      |      |                                                                                               |      |       |

| I <sub>HD LC</sub>       | HD_S source current                                                                                                                                                                                                                                                                                               | _    | 1.5  | _                                                                                             | mA   |       |

### 6.3 Pump motor pre-driver

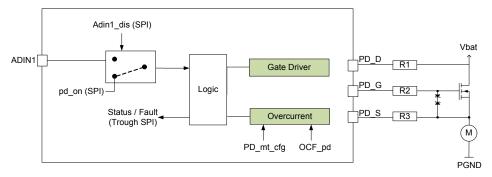

### 6.3.1 Function description

This module is designed for pump motor predrivers, a maximum of 500 Hz PWM is possible. The pump motor pre-driver can be driven by a SPI command (pd\_on) or through the ADIN1 pin by selecting Adin1\_dis bit at "1".

Figure 6. Pump motor predriver

### 6.3.2 Fault Detection

### 6.3.2.1 Overcurrent

The pump pre-driver protects the external n-channel power FET on PD\_G in overcurrent conditions. The drain-source voltage of the FET on PD\_G is checked if the high-side predriver is switched on. If the measured drain-source voltage exceeds the overcurrent voltage threshold, the output of the overcurrent comparator is enabled. If the output of the comparator is active longer than the defined filter time, the output PD\_G is switched off. Overcurrent detection logic has a masking time from pd\_on turn-on against malfunctions in transient time. The masking time and filter time of the pump predriver is controllable by the SPI bit (See SPI and data register). After switching off the power FET on PD\_G by an overcurrent condition, the power FET can be turned back to a "normal state" by a SPI write 1 to the "PD\_cIr\_fit" register, and then turned on by a SPI command.

When the power FET is switched off, the gate capacitance of the FET is discharged by a constant current, which is controlled fast and slow by a SPI command (HPD\_sr).

### 6.3.2.2 External components of pump predriver

Protection of the resistors  $R_{PD_D}$ ,  $R_{PD_G}$ , and  $R_{PD_S}$  is required (for example:  $R_{PD_D} = 2.0 \text{ k}\Omega$ ,  $R_{PD_G} = 100 \Omega$ ,  $R_{PD_S} = 2.0 \text{ k}\Omega$ ). Zener clamping is necessary to protect the gate and source. The zener chains are used for avalanche clamping and protection against transients.

### Table 11. Pump motor predriver electrical characteristics

V<sub>PWR</sub> = 6.0 to 36 V, VCC5 = 4.75 to 5.25 V, DOSV = 3.13 to 5.25 V, T<sub>J</sub> = -40 to +125 °C, unless otherwise specified.

| Symbol                   | Parameter                                                                                                                           | Min.                 | Тур. | Max.                  | Unit | Note |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|-----------------------|------|------|

| D_G                      |                                                                                                                                     | 1                    |      |                       |      |      |

|                          | PD_G switch-on voltage - with pd_on: PWM at 500 Hz, 50% duty cycle through the SPI, 16 nF between PD_G & GND. pd_on = 1 without PWM |                      |      |                       |      |      |

| V <sub>PD_ON</sub>       | <ul> <li>5.5 V ≤ VPWR &lt; 6.0 V</li> </ul>                                                                                         | V <sub>PWR</sub> +4  | _    | V <sub>PWR</sub> + 15 | V    |      |

| . 5_0.1                  | <ul> <li>6.0 V ≤ VPWR &lt; 7.0V</li> </ul>                                                                                          | V <sub>PWR</sub> +5  | —    | V <sub>PWR</sub> +15  |      |      |

|                          | <ul> <li>7.0 V ≤ VPWR &lt; 10 V</li> </ul>                                                                                          | V <sub>PWR</sub> +7  | —    | V <sub>PWR</sub> +15  |      |      |

|                          | • 10 V ≤ VPWR < 36 V                                                                                                                | V <sub>PWR</sub> +10 | —    | V <sub>PWR</sub> +15  |      |      |

| V <sub>PD_OFF</sub>      | PD_G switch-off voltage - pull-up current < 20 μA                                                                                   | —                    | —    | 1                     | V    |      |

| t <sub>PD_ON</sub>       | Turn-on time                                                                                                                        | _                    | 0.5  | _                     | ms   |      |

| I <sub>PD_OFF_SLOW</sub> | Turn-off current slow - PD_G > 2.0 V. HPD_sr = 0                                                                                    | 70                   | 100  | 200                   | μA   |      |

| I <sub>PD_OFF_FAST</sub> | Turn-off current fast - PD_G >2.0 V, HPD_sr = 1                                                                                     | 1.0                  | 2.0  | 4.5                   | nA   |      |

| D_S                      |                                                                                                                                     |                      |      |                       |      | •    |

| ILEAK_PD_SRC             | Leakage current - $0 \le VPD\_src \le 36 V$ , $6.0 \le VPWR \le 36 V$                                                               |                      |      | 10                    | μA   |      |

| D_D                      |                                                                                                                                     | 1                    |      |                       |      |      |

| I <sub>LEAK_PD_DRN</sub> | Leakage current - VCC5 = DOSV = 0 V,<br>HD_D = PD_D = VPWR = 36 V                                                                   | _                    | _    | 10                    | μA   |      |

| vercurrent dete          | ction                                                                                                                               | 1 1                  |      |                       |      |      |

| V <sub>PD_OC</sub>       | Overcurrent detection threshold - V <sub>PD_D</sub> - V <sub>PD_SRC</sub> , R <sub>DRN</sub> ,<br>R <sub>SRC</sub> = 2.0 k $\Omega$ |                      | 1.0  | +15%                  | V    |      |

| t <sub>PD_OC1</sub>      | Overcurrent detection filter time - OCF_pd = 0                                                                                      | —                    | T2   | —                     | μs   |      |

| t <sub>PD_OC2</sub>      | Overcurrent detection filter time - OCF_pd = 1                                                                                      | _                    | 4*T1 | _                     | μs   |      |

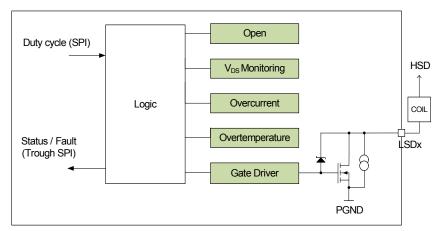

### 6.4 Low-side driver

### 6.4.1 Functional description

The SB0800 is designed to drive inductive loads in low-side configuration. All four channels are monitored by logic and faults are individually reported by the SPI. All external wiring to the loads and supply pins of the device are controlled. The device is self-protected against short-circuit and overtemperature at the outputs.

Figure 7. PWM low-side driver

Channel 1 to 4 can work either as current regulator or as PWM. When Channels 1 to 4 work as a current regulator, freewheeling diodes must be connected. Each channel comprises an output transistor, a predriver circuit, a diagnostic circuitry, and a current regulator. The SPI register defines the target output current. The output current is controlled through the output PWM of the power stage. The LSD1-4 current slopes are controlled by a SPI command to reduce switching loss.

The four power outputs consist of DMOS-power transistors with open drain outputs. The output transistor is equipped with an active clamp to limit the voltage at its output during turn-off with inductive loads. When the external fly-back diode is connected, the current re-circulation executes via the diode to the battery. When the diode is not connected, the PWM driver is equivalent to a digital driver. In those conditions, the inductive load forces the output voltage to increase until the voltage at the output is such that the output transistor turns on again. This lasts until the inductor current becomes zero. At that moment, the output transistor turns off. The predriver is in charge of applying the necessary voltage on the output transistor gate to minimize the On-resistance of the output switch.

The duty cycle of PWM low-side drivers is programmed via an 8-bit SPI message. The duty cycle between 0% and 100% can be selected and the LSB of the 8 bits is weighted with an 0.39% duty. Each channel has an 8-bit SPI register of PWM duty cycle.

The PWM low-side driver uses each channel as a digital low-side switch.

PWMx duty cycle = 1111 1111 - Digital low-side switch ON (conducting)

PWMx duty cycle = 0000 0000 - Digital low-side switch OFF

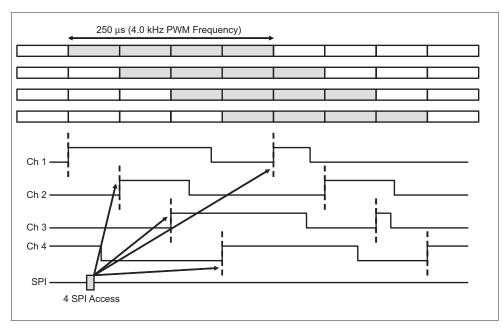

The SB0800 provides interleaved phase shift switching to minimize switching noise of the solenoid coil. Each LSD1 to 4 have this cycle.

Figure 8. PWM valve control interleave

### Table 12. Low-side driver electrical characteristics

$V_{PWR}$  = 6.0 to 36 V, DOSV = 3.13 to 5.25 V,  $T_{J}$  = -40 to 125 °C, unless otherwise specified.

| Symbol                                        | Characteristic                                                                                                                              | Min.        | Тур.        | Max.       | Unit | Notes    |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|------------|------|----------|

| ower output                                   | •                                                                                                                                           |             | l .         | ł          |      | <u> </u> |

| R <sub>ON_LSD14</sub>                         | On Resistance Channel 1 to 4: CR<br>• $T_J$ = 125 °C; 9.0 V $\leq$ V <sub>PWR</sub> $\leq$ 36 V; I <sub>LOAD</sub> = 2.0 A                  | _           | _           | 0.255      | Ω    |          |

| R <sub>ON_LSD14_E</sub>                       | On Resistance Channel 1 to 4: CR (extended mode)<br>• $T_J$ = 125 °C; 5.5 V $\leq$ V <sub>PWR</sub> $\leq$ 9.0 V; I <sub>LOAD</sub> = 2.0 A |             | _           | 0.33       | Ω    |          |

| I <sub>LEAK_LSD</sub>                         | Drain Leakage Current<br>• LSD = 36 V                                                                                                       |             | _           | 10         | μA   |          |

| V <sub>CL_LSD</sub>                           | Active Clamp Voltage                                                                                                                        | _           | 38          | 45         | V    |          |

| ïmings                                        |                                                                                                                                             |             |             |            |      | •        |

| t <sub>R_CR1</sub><br>t <sub>F_CR1</sub>      | Rise Time/Fall Time<br>• 10% to 90%, I <sub>LOAD</sub> = 1.0 A, V <sub>PWR</sub> =24 V; no capacitor didt = 0<br>(SPI bit)                  | 1.0<br>0.1  | 1.7<br>1.35 | 3.0<br>3.0 | μs   |          |

| t <sub>R_CR2</sub><br>t <sub>F_CR2</sub>      | Rise Time/Fall Time<br>• 10% to 90%, I <sub>LOAD</sub> = 1.0 A, V <sub>PWR</sub> = 24 V; no capacitor didt = 1<br>(SPI bit)                 | 0.05<br>0.1 | 0.5<br>1.0  | 1.0<br>3.0 | μs   |          |

| t <sub>D</sub> on CR<br>t <sub>D</sub> off CR | Turn on/off Delay Time<br>• Digital 1 to 10% or 90%, I <sub>LOAD</sub> = 1.0 A, V <sub>PWR</sub> = 24 V, no<br>capacitor                    | 0.0         | _           | 3.0        | μs   | (10)     |

#### Table 12. Low-side driver electrical characteristics (continued)

| Symbol                                               | Characteristic                                                                                                                                                                                                                                            | Min. | Тур.                                                 | Max. | Unit | Notes |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------|------|------|-------|

| imings                                               |                                                                                                                                                                                                                                                           |      |                                                      | 1    | 1    |       |

| LF_PWM                                               | Output PWM frequency for LSD1-4         • LF_PWM xx = 111         • LF_PWM xx = 110         • LF_PWM xx = 101         • LF_PWM xx = 100         • LF_PWM xx = 000 (default)         • LF_PWM xx = 011         • LF_PWM xx = 001         • LF_PWM xx = 010 | -20% | 3.0<br>3.2<br>3.4<br>3.6<br>3.9<br>4.2<br>4.5<br>5.0 | 20%  | kHz  |       |

| 0000 0000<br>0000 0001<br><br>1111 1110<br>1111 1111 | <ul><li>PWM Duty Cycle Programming (8-bits)</li><li>Can be used for digital low-side driver</li></ul>                                                                                                                                                     |      | OFF<br>0.39<br>—<br>99.61<br>ON                      |      | %    |       |

Notes

10. Digital: internal digital signal delivered by interleave synchronization block. See Figure 8.

### 6.4.2 LSD1 to LSD4 current regulation driver

Figure 9. PWM low-side driver (current regulated)

The load current is sensed by an internal low-side sense FET and digitized by an internal A/D converter. The target value of the current is given SPI messages. A digital current regulation circuitry compares the actual load current with the target current value and steers the duty cycle of the low-side power switch. The PI regulator characteristic can be adjusted via the SPI.

### 6.4.2.1 Target current

...

Each current regulator channel has its own 10-bit target current register. The LSB of the 10 bits is weighted with 2.2 mA. A zero value disables the power stage of the respective channel. A new target current is instantaneously passed to the settling time, which is the settling of the new current value.

PWMx target current value = 00 0000 0000  $\rightarrow$  0 mA PWMx target current value = 00 0000 0001  $\rightarrow$  2.2 mA

PWMx target current value = 11 1111 1110  $\rightarrow$  2.248 A PWMx target current value = 11 1111 1111  $\rightarrow$  2.250 A

| CR_DIS12/34 | CR_fb | Mode               | LSD1-4 duty cycle (8-bit) or current read (10-bit)  |

|-------------|-------|--------------------|-----------------------------------------------------|

| 0           | 0     | current regulation | Read current target (to check SPI write)            |

| 0           | 1     | current regulation | Read output duty cycle value for gate driver.       |

| 1           | 0     | PWM                | Read programmed PWM duty cycle (to check SPI write) |

| 1           | 1     | PWM                | Read hardware ADC current value                     |

### 6.4.2.2 Current measurement

The output current is measured during the "ON' phase of the low-side driver. A fraction of the output current is diverted and (using a "current mirror" circuit) generates across an internal resistance a voltage relative to ground, this being proportional to the output current.

### 6.4.3 PI characteristics

Digital PI-regulator with the Transfer function is programmed via the SPI register.

Transfer function:

$$\frac{KI}{z-1} + KP$$