# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 56F8347/56F8147

Data Sheet

Preliminary Technical Data

56F8300 16-bit Digital Signal Controllers

MC56F8347 Rev.11 01/2007

freescale.com

| Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Fixed typos in Section 1.1.3, Replace any reference to Flash Interface Unit with Flash Modul corrected pin number for D14 in Table 2-2, added note to Vcap pin in Table 2-2, corrected thermal numbers for 160 LQFP in Table 10-4, removed unneccessary notes in Table 10-13; corrected temperature range in Table 10-14; added ADC calibration information to Table 10-and new graphs in Figure 10-22.                                                                               |  |  |  |

| Clarification to <b>Table 10-23</b> , corrected Digital Input Current Low (pull-up enabled) numbers in <b>Table 10-5</b> . Removed text and Table 10-2; replaced with note to <b>Table 10-1</b> .                                                                                                                                                                                                                                                                                     |  |  |  |

| Added 56F8147 information; edited to indicate differences in 56F8347 and 56F8147.<br>Reformatted for Freescale look and feel. Updated Temperature Sensor and ADC tables, then<br>updaated balance of electrical tables for consistency throughout the family. Clarified I/O power<br>description in Table 2-2, added note to Table 10-7 and clarified Section 12.3.                                                                                                                   |  |  |  |

| Correcting Figure 4-1 Boot Flash Start = \$02_0000                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Added output voltage maximum value and note to clarify in <b>Table 10-1</b> ; also removed overall life expectancy note, since life expectancy is dependent on customer usage and must be determined by reliability engineering. Clarified value and unit measure for Maximum allowed P <sub>D</sub> in <b>Table 10-3</b> . Corrected note about average value for Flash Data Retention in <b>Table 10-4</b> . Added new RoHS-compliant orderable part numbers in <b>Table 13-1</b> . |  |  |  |

| Added 160MAPBGA information, TA equation updated in <b>Table 10-4</b> and additional minor edits throughout data sheet                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Updated Table 10-24 to reflect new value for maximum Uncalibrated Gain Error                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Deleted formula for Max Ambient Operating Temperature (Automotive) and Max Ambient<br>Operating Temperature (Industrial) and corrected Flash Endurance to 10,000 in <b>Table 10-4</b> .<br>Added RoHS-compliance and "pb-free" language to back cover.                                                                                                                                                                                                                                |  |  |  |

| Corrected Section 6.4 title (from Operation Mode Register to Operating Mode Register).<br>Updated JTAG ID in Section 6.5.4. Added information/corrected state during reset in Table 2-2.<br>Clarified external reference crystal frequency for PLL in Table 10-14 by increasing maximum value to 8.4MHz.                                                                                                                                                                              |  |  |  |

| Replaced "Tri-stated" with an explanation in State During Reset column in Table 2-2.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| <ul> <li>Added the following note to the description of the TMS signal in Table 2-2:<br/>Note: Always tie the TMS pin to V<sub>DD</sub> through a 2.2K resistor.</li> <li>Added the following note to the description of the TRST signal in Table 2-2:<br/>Note: For normal operation, connect TRST directly to V<sub>SS</sub>. If the design is to be used in a debugging</li> </ul>                                                                                                 |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

### **Document Revision History**

Please see http://www.freescale.com for the most current data sheet revision.

# 56F8347/56F8147 General Description

Note: Features in italics are NOT available in the 56F8147 device.

- Up to 60 MIPS at 60MHz core frequency

- DSP and MCU functionality in a unified, C-efficient architecture

- Access up to 4MB of off-chip program and 32MB of data memory

- Chip Select Logic for glueless interface to ROM and SRAM

- 128KB of Program Flash

- 4KB of Program RAM

- 8KB of Data Flash

- 8KB of Data RAM

- 8KB of Boot Flash

- Up to two 6-channel PWM modules

- Four 4-channel, 12-bit ADCs

- Temperature Sensor

- Up to two Quadrature Decoders

- FlexCAN module

- Two Serial Communication Interfaces (SCIs)

- Up to two Serial Peripheral Interfaces (SPIs)

- Up to four general-purpose Quad Timers

- Computer Operating Properly (COP) / Watchdog

- JTAG/Enhanced On-Chip Emulation (OnCE™) for unobtrusive, real-time debugging

- Up to 76 GPIO lines

- 160-pin LQFP Package and 160MAPBGA

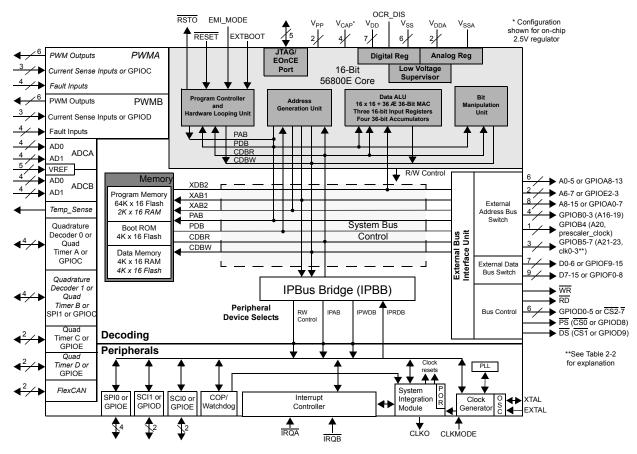

56F8347/56F8147 Block Diagram

# **Table of Contents**

| Part 1: Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                | 5  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----|

| 1.1. 56F8347/56F8147 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 5                                                                                                            |    |

| 1.2. Device Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 7                                                                                                            |    |

| 1.3. Award-Winning Development Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 9                                                                                                            |    |

| 1.4. Architecture Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10                                                                                                             |    |

| 1.5. Product Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |    |

| 1.6. Data Sheet Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |    |

| Part 2: Signal/Connection Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | '                                                                                                              | 15 |

| 2.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |    |

| 2.2. Signal Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |    |

| Part 3: On-Chip Clock Synthesis (OCCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ). 3                                                                                                           | 38 |

| 3.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |    |

| 3.2. External Clock Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |    |

| 3.3. Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |    |

| Part 4: Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                                                                              | 40 |

| 4.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |    |

| 4.2. Program Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |    |

| 4.3. Interrupt Vector Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |    |

| 4.4. Data Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |    |

| 4.5. Flash Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |    |

| 4.6. EOnCE Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |    |

| 4.7. Peripheral Memory Mapped Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |    |

| 4.8. Factory Programmed Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73                                                                                                             |    |

| Part 5: Interrupt Controller (ITCN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73                                                                                                             | 74 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73                                                                                                             | 74 |

| Part 5: Interrupt Controller (ITCN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73<br>7<br>74                                                                                                  | 74 |

| Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73<br>7<br>74<br>74                                                                                            | 74 |

| Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73<br>74<br>74<br>74<br>74                                                                                     | 74 |

| Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                             | 73<br>74<br>74<br>74<br>74<br>76<br>76                                                                         | 74 |

| Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73<br>74<br>74<br>74<br>74<br>76<br>76                                                                         | 74 |

| Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                             | 73<br>74<br>74<br>74<br>76<br>76<br>77                                                                         | 74 |

| Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes<br>5.6. Register Descriptions<br>5.7. Resets                                                                                                                                                                                                                                                                                                                                                                                | 73<br>74<br>74<br>76<br>76<br>76<br>77<br>102                                                                  |    |

| Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes<br>5.6. Register Descriptions<br>5.7. Resets<br>Part 6: System Integration Module (SIM)                                                                                                                                                                                                                                                                                                                                     | 73<br>74<br>74<br>76<br>76<br>76<br>77<br>102                                                                  |    |

| Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets    Part 6: System Integration Module (SIM) 6.1. Overview                                                                                                                                                                                                                                                                                    | 73<br>74<br>74<br>76<br>76<br>76<br>77<br>102<br>. <b>1</b> (<br>103                                           |    |

| Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Overview         6.2. Features                                                                                                                                                                                                                                                 | 73<br>74<br>74<br>76<br>76<br>77<br>102<br>. 10<br>103<br>103                                                  |    |

| Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Overview         6.2. Features         6.3. Operating Modes                                                                                                                                                                                                                    | 73<br>74<br>74<br>76<br>76<br>77<br>102<br>. 10<br>103<br>103<br>104                                           |    |

| Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Overview         6.2. Features         6.3. Operating Modes         6.4. Operating Mode Register                                                                                                                                                                               | 73<br>74<br>74<br>76<br>76<br>76<br>77<br>102<br>. 10<br>103<br>103<br>104<br>104                              |    |

| Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Overview         6.3. Operating Modes         6.4. Operating Modes         6.5. Register Descriptions                                                                                                                                                                          | 73<br>74<br>74<br>74<br>76<br>76<br>77<br>102<br>. 10<br>103<br>103<br>104<br>104<br>105                       |    |

| Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Overview         6.3. Operating Modes         6.4. Operating Modes         6.5. Register Descriptions         6.6. Clock Generation Overview.                                                                                                                                  | 73<br>74<br>74<br>76<br>76<br>76<br>77<br>102<br>. 10<br>103<br>103<br>104<br>104                              |    |

| Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Overview         6.2. Features         6.3. Operating Modes         6.4. Operating Modes         6.5. Register Descriptions         6.6. Clock Generation Overview.         6.7. Power-Down Modes Overview                                                                     | 73<br>74<br>74<br>76<br>76<br>77<br>102<br>. 10<br>103<br>103<br>104<br>104<br>105<br>118<br>118               |    |

| Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Overview         6.2. Features         6.3. Operating Modes         6.4. Operating Modes         6.5. Register Descriptions         6.6. Clock Generation Overview.         6.7. Power-Down Modes Overview         6.8. Stop and Wait Mode Disable Function                    | 73<br>74<br>74<br>76<br>76<br>77<br>102<br>. 10<br>103<br>103<br>103<br>104<br>104<br>105<br>118<br>118<br>118 |    |

| Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Overview         6.2. Features         6.3. Operating Modes         6.4. Operating Modes         6.5. Register Descriptions         6.6. Clock Generation Overview         6.7. Power-Down Modes Overview                                                                      | 73<br>74<br>74<br>76<br>76<br>77<br>102<br>. 10<br>103<br>103<br>103<br>104<br>104<br>105<br>118<br>118<br>118 |    |

| Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Overview         6.2. Features         6.3. Operating Modes         6.4. Operating Modes         6.5. Register Descriptions         6.6. Clock Generation Overview         6.7. Power-Down Modes Overview         6.8. Stop and Wait Mode Disable Function         6.9. Resets | 73<br>74<br>74<br>76<br>76<br>77<br>102<br>. 10<br>103<br>103<br>104<br>104<br>105<br>118<br>118<br>119<br>119 | 03 |

| Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Overview         6.2. Features         6.3. Operating Modes         6.4. Operating Modes         6.5. Register Descriptions         6.6. Clock Generation Overview         6.7. Power-Down Modes Overview         6.8. Stop and Wait Mode Disable Function         6.9. Resets | 73<br>74<br>74<br>76<br>76<br>77<br>102<br>. 10<br>103<br>103<br>104<br>105<br>118<br>118<br>119<br>119<br>12  | 03 |

| Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Overview         6.2. Features         6.3. Operating Modes         6.4. Operating Modes         6.5. Register Descriptions         6.6. Clock Generation Overview         6.7. Power-Down Modes Overview         6.8. Stop and Wait Mode Disable Function         6.9. Resets | 73<br>74<br>74<br>74<br>76<br>77<br>102<br>. 10<br>103<br>104<br>105<br>118<br>118<br>119<br>12<br>120         | 03 |

| Part 8: General Purpose Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (GPIO)       123         8.1. Introduction       123         8.2. Memory Maps       123         8.3. Configuration       123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Part 9: Joint Test Action Group (JTAG). 1289.1. JTAG Information128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Part 10: Specifications.       128         10.1. General Characteristics       128         10.2. DC Electrical Characteristics       132         10.3. AC Electrical Characteristics       136         10.4. Flash Memory Characteristics       136         10.5. External Clock Operation Timing       137         10.6. Phase Locked Loop Timing.       137         10.7. Crystal Oscillator Timing       138         10.8. External Memory Interface Timing       138         10.9. Reset, Stop, Wait, Mode Select,       141         10.10. Serial Peripheral Interface (SPI) Timing       143         10.11. Quad Timer Timing       147         10.12. Quadrature Decoder Timing       147         10.13. Serial Communication Interface       (SCI) Timing         (SCI) Timing       148         10.14. Controller Area Network (CAN) Timing       149         10.15. JTAG Timing       149         10.16. Analog-to-Digital Converter       (ADC) Parameter       151         10.17. Equivalent Circuit for ADC Inputs       154 |

| Part 11: Packaging         156           11.1. 56F8347 Package and Pin-Out         156           11.2. 56F8147 Package and Pin-Out         156           11.2. 56F8147 Package and Pin-Out         163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Part 12: Design Considerations       167         12.1. Thermal Design Considerations       167         12.2. Electrical Design Considerations       168         12.3. Power Distribution and I/O Ring       169                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Part 13: Ordering Information ..... 170

# Part 1 Overview

# 1.1 56F8347/56F8147 Features

## 1.1.1 Core

- Efficient 16-bit 56800E family controller engine with dual Harvard architecture

- Up to 60 Million Instructions Per Second (MIPS) at 60 MHz core frequency

- Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

- Four 36-bit accumulators, including extension bits

- Arithmetic and logic multi-bit shifter

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Three internal address buses

- Four internal data buses

- Instruction set supports both DSP and controller functions

- Controller-style addressing modes and instructions for compact code

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- JTAG/EOnCE debug programming interface

## 1.1.2 Differences Between Devices

Table 1-1 outlines the key differences between the 56F8347 and 56F8147 devices.

| Feature            | 56F8347       | 56F8147       |

|--------------------|---------------|---------------|

| Guaranteed Speed   | 60MHz/60 MIPS | 40MHZ/40MIPS  |

| Program RAM        | 4KB           | Not Available |

| Data Flash         | 8KB           | Not Available |

| PWM                | 2 x 6         | 1 x 6         |

| CAN                | 1             | Not Available |

| Quad Timer         | 4             | 2             |

| Quadrature Decoder | 2 x 4         | 1 x 4         |

| Temperature Sensor | 1             | Not Available |

| Dedicated GPIO     | _             | 7             |

#### **Table 1-1 Device Differences**

## 1.1.3 Memory

Note: Features in italics are NOT available in the 56F8147 device.

- Harvard architecture permits as many as three simultaneous accesses to program and data memory

- Flash security protection feature

- On-chip memory, including a low-cost, high-volume Flash solution

- 128KB of Program Flash

- 4KB of Program RAM

- 8KB of Data Flash

- 8KB of Data RAM

- 8KB of Boot Flash

- Off-chip memory expansion capabilities provide a simple method for interfacing additional external memory and/or peripheral devices

- Access up to 4MB of external program memory or 32MB of external data memory

- External accesses supported at up to 60MHz (zero wait states)

- EEPROM emulation capability

# 1.1.4 Peripheral Circuits

Note: Features in italics are NOT available in the 56F8147 device.

- Pulse Width Modulator:

- In the 56F8347, two Pulse Width Modulator modules, each with six PWM outputs, three Current Sense inputs, and three Fault inputs; fault-tolerant design with dead time insertion; supports both center-aligned and edge-aligned modes

- In the 56F8147, one Pulse Width Modulator module, with six PWM outputs, three Current Sense inputs, and three Fault inputs; fault-tolerant design with dead time insertion; supports both center-aligned and edge-aligned modes

- Four 12-bit, Analog-to-Digital Converters (ADCs), which support four simultaneous conversions with quad, 4-pin multiplexed inputs; ADC and PWM modules can be synchronized through Timer C, channels 2 and 3

- Quadrature Decoder:

- In the 56F8347, two four-input Quadrature Decoders or two additional Quad Timers

- In the 56F8147, one four-input Quadrature Decoder, which works in conjunction with Quad Timer A

- Temperature Sensor diode can be connected, on the board, to any of the ADC inputs to monitor the on-chip temperature

- Quad Timer:

- In the 56F8347, four dedicated general-purpose Quad Timers totaling six dedicated pins: Timer C with two pins and Timer D with four pins

- In the 56F8147, two general-purpose Quad Timers; Timer A works in conjunction with Quadrature Decoder 0 or GPIO and Timer C works in conjunction with GPIO

- FlexCAN (CAN Version 2.0 B-compliant ) module with 2-pin port for transmit and receive

- Two Serial Communication Interfaces (SCIs), each with two pins (or four additional GPIO lines)

- Up to two Serial Peripheral Interfaces (SPIs), both with configurable 4-pin port (or eight additional GPIO lines)

- In the 56F8347, SPI1 can also be used as Quadrature Decoder 1 or Quad Timer B

- In the 56F8147, SPI1 can alternately be used only as GPIO

- Computer Operating Properly (COP) / Watchdog timer

- Two dedicated external interrupt pins

- Up to 76 General Purpose I/O (GPIO) pins

- External reset input pin for hardware reset

- External reset output pin for system reset

- JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, processor speed-independent, real-time debugging

- Software-programmable, Phase Lock Loop (PLL)-based frequency synthesizer for the core clock

#### 1.1.5 Energy Information

- Fabricated in high-density CMOS with 5V-tolerant, TTL-compatible digital inputs

- On-board 3.3V down to 2.6V voltage regulator for powering internal logic and memories; can be disabled

- On-chip regulators for digital and analog circuitry to lower cost and reduce noise

- Wait and Stop modes available

- ADC smart power management

- Each peripheral can be individually disabled to save power

# **1.2 Device Description**

The 56F8347 and 56F8147 are members of the 56800E core-based family of controllers. Each combines, on a single chip, the processing power of a Digital Signal Processor (DSP) and the functionality of a microcontroller with a flexible set of peripherals to create an extremely cost-effective solution. Because of its low cost, configuration flexibility, and compact program code, the 56F8347 and 56F8147 are well-suited for many applications. The device includes many peripherals that are especially useful for motion control, smart appliances, steppers, encoders, tachometers, limit switches, power supply and control, *automotive* control (56F8347 only), engine management, noise suppression, remote utility metering, industrial control for power, lighting, and automation applications.

The 56800E core is based on a Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The MCU-style programming model and optimized instruction set allow straightforward generation of efficient, compact DSP and control code. The instruction set is also highly efficient for C/C++ Compilers to enable rapid development of optimized control applications.

The 56F8347 and 56F8147 support program execution from internal or external memories. Two data operands can be accessed from the on-chip data RAM per instruction cycle. These devices also provide two external dedicated interrupt lines and up to 76 General Purpose Input/Output (GPIO) lines, depending on peripheral configuration.

# 1.2.1 56F8347 Features

The 56F8347 controller includes 128KB of Program Flash and 8KB of Data Flash (each programmable through the JTAG port) with 4KB of Program RAM and 8KB of Data RAM. It also supports program execution from external memory.

A total of 8KB of Boot Flash is incorporated for easy customer inclusion of field-programmable software routines that can be used to program the main Program and Data Flash memory areas. Both Program and Data Flash memories can be independently bulk erased or erased in pages. Program Flash page erase size is 1KB. Boot and Data Flash page erase size is 512 bytes. The Boot Flash memory can also be either bulk or page erased.

A key application-specific feature of the 56F8347 is the inclusion of two Pulse Width Modulator (PWM) modules. These modules each incorporate three complementary, individually programmable PWM signal output pairs (each module is also capable of supporting six independent PWM functions, for a total of 12 PWM outputs) to enhance motor control functionality. Complementary operation permits programmable dead time insertion, distortion correction via current sensing by software, and separate top and bottom output polarity control. The up-counter value is programmable to support a continuously variable PWM frequency. Edge-aligned and center-aligned synchronous pulse width control (0% to 100% modulation) is supported. The device is capable of controlling most motor types: ACIM (AC Induction Motors); both BDC and BLDC (Brush and Brushless DC motors); SRM and VRM (Switched and Variable Reluctance Motors); and stepper motors. The PWMs incorporate fault protection and cycle-by-cycle current limiting with sufficient output drive capability to directly drive standard optoisolators. A "smoke-inhibit", write-once protection feature for key parameters is also included. A patented PWM waveform distortion correction circuit is also provided. Each PWM is double-buffered and includes interrupt controls to permit integral reload rates to be programmable from 1 to 16. The PWM modules provide reference outputs to synchronize the Analog-to-Digital Converters through two channels of Quad Timer C.

The 56F8347 incorporates two Quadrature Decoders capable of capturing all four transitions on the two-phase inputs, permitting generation of a number proportional to actual position. Speed computation capabilities accommodate both fast- and slow-moving shafts. An integrated watchdog timer in the Quadrature Decoder can be programmed with a time-out value to alert when no shaft motion is detected. Each input is filtered to ensure only true transitions are recorded.

This controller also provides a full set of standard programmable peripherals that include two Serial Communications Interfaces (SCIs); two Serial Peripheral Interfaces (SPIs); and four Quad Timers. Any of these interfaces can be used as General Purpose Input/Outputs (GPIOs) if that function is not required. A Flex Controller Area Network (FlexCAN) interface (CAN Version 2.0 B-compliant) and an internal interrupt controller are a part of the 56F8347.

# 1.2.2 56F8147 Features

The 56F8147 controller includes 128KB of Program Flash, programmable through the JTAG port, with 8KB of Data RAM. It also supports program execution from external memory.

A total of 8KB of Boot Flash is incorporated for easy customer inclusion of field-programmable software routines that can be used to program the main Program Flash memory area, which can be independently

bulk erased or erased in pages. Program Flash page erase size is 1KB. Boot Flash page erase size is 512 bytes and the Boot Flash memory can also be either bulk or page erased.

A key application-specific feature of the 56F8147 is the inclusion of one Pulse Width Modulator (PWM) module. This module incorporates three complementary, individually programmable PWM signal output pairs and can also support six independent PWM functions to enhance motor control functionality. Complementary operation permits programmable dead time insertion, distortion correction via current sensing by software, and separate top and bottom output polarity control. The up-counter value is programmable to support a continuously variable PWM frequency. Edge-aligned and center-aligned synchronous pulse width control (0% to 100% modulation) is supported. The device is capable of controlling most motor types: ACIM (AC Induction Motors); both BDC and BLDC (Brush and Brushless DC motors); SRM and VRM (Switched and Variable Reluctance Motors); and stepper motors. The PWM incorporates fault protection and cycle-by-cycle current limiting with sufficient output drive capability to directly drive standard optoisolators. A "smoke-inhibit", write-once protection feature for key parameters is also included. A patented PWM waveform distortion correction circuit is also provided. Each PWM is double-buffered and includes interrupt controls to permit integral reload rates to be programmable from 1 to 16. The PWM module provides reference outputs to synchronize the Analog-to-Digital Converters through two channels of Quad Timer C.

The 56F8147 incorporates a Quadrature Decoder capable of capturing all four transitions on the two-phase inputs, permitting generation of a number proportional to actual position. Speed computation capabilities accommodate both fast- and slow-moving shafts. An integrated watchdog timer in the Quadrature Decoder can be programmed with a time-out value to alert when no shaft motion is detected. Each input is filtered to ensure only true transitions are recorded.

This controller also provides a full set of standard programmable peripherals that include two Serial Communications Interfaces (SCIs); two Serial Peripheral Interfaces (SPIs); and two Quad Timers. Any of these interfaces can be used as General Purpose Input/Outputs (GPIOs) if that function is not required. An internal interrupt controller is also a part of the 56F8147.

# **1.3 Award-Winning Development Environment**

Processor Expert<sup>TM</sup> (PE) provides a Rapid Application Design (RAD) tool that combines easy-to-use component-based software application creation with an expert knowledge system.

The CodeWarrior Integrated Development Environment is a sophisticated tool for code navigation, compiling, and debugging. A complete set of evaluation modules (EVMs) and development system cards will support concurrent engineering. Together, PE, CodeWarrior and EVMs create a complete, scalable tools solution for easy, fast, and efficient development.

# **1.4 Architecture Block Diagram**

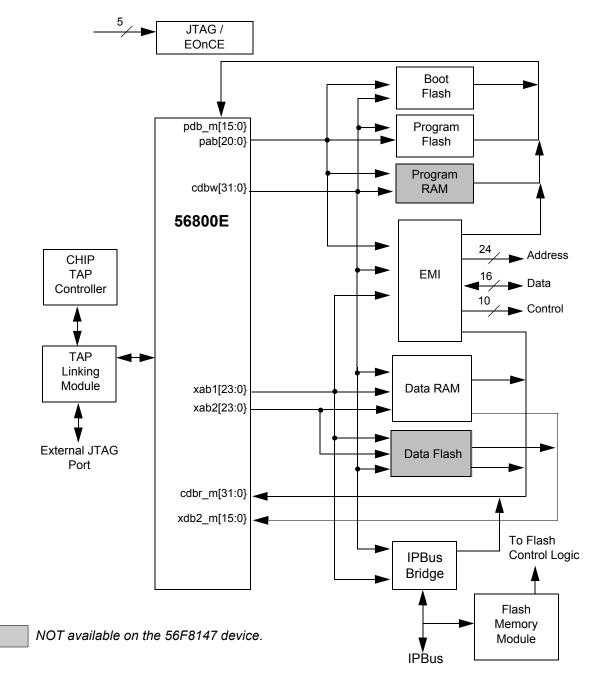

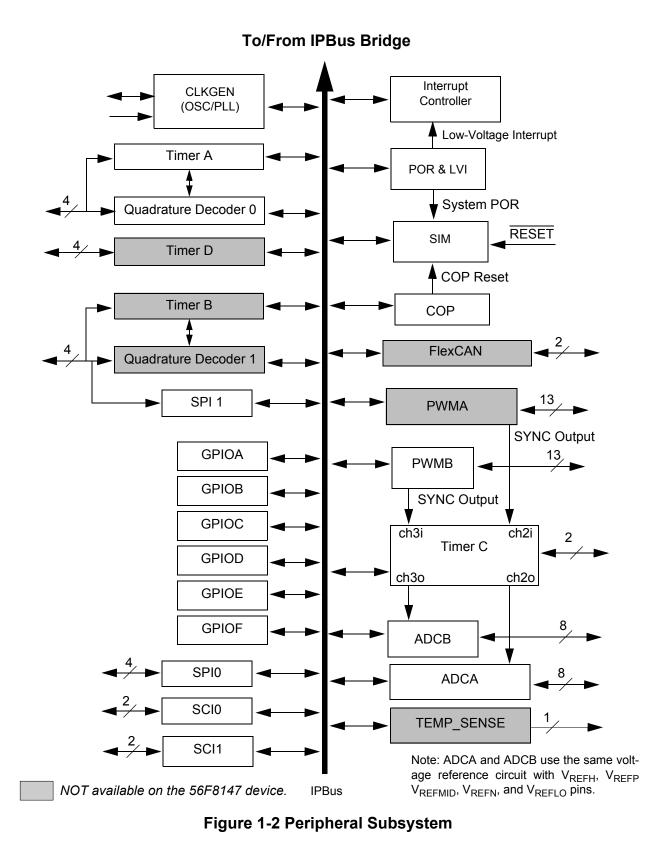

Note: Features in italics are NOT available in the 56F8147 device and are shaded in the following figures.

The 56F8347/56F8147 architecture is shown in **Figure 1-1** and **Figure 1-2**. **Figure 1-1** illustrates how the 56800E system buses communicate with internal memories, the external memory interface and the IPBus Bridge. **Table 1-2** lists the internal buses in the 56800E architecture and provides a brief description of their function. **Figure 1-2** shows the peripherals and control blocks connected to the IPBus Bridge. The figures do not show the on-board regulator and power and ground signals. They also do not show the multiplexing between peripherals or the dedicated GPIOs. Please see **Part 2**, **Signal/Connection Descriptions**, to see which signals are multiplexed with those of other peripherals.

Also shown in **Figure 1-2** are connections between the PWM, Timer C and ADC blocks. These connections allow the PWM and/or Timer C to control the timing of the start of ADC conversions. The Timer C channel indicated can generate periodic start (SYNC) signals to the ADC to start its conversions. In another operating mode, the PWM load interrupt (SYNC output) signal is routed internally to the Timer C input channel as indicated. The timer can then be used to introduce a controllable delay before generating its output signal. The timer output then triggers the ADC. To fully understand this interaction, please see the **56F8300 Peripheral User's Manual** for clarification on the operation of all three of these peripherals.

Figure 1-1 System Bus Interfaces

- **Note:** Flash memories are encapsulated within the Flash Memory (FM) Module. Flash control is accomplished by the I/O to the FM over the peripheral bus, while reads and writes are completed between the core and the Flash memories.

- **Note:** The primary data RAM port is 32 bits wide. Other data ports are 16 bits.

| Name                     | Function                                                                                                                                                                                                                                                          |  |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Program Memory Interface |                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| pdb_m[15:0]              | Program data bus for instruction word fetches or read operations.                                                                                                                                                                                                 |  |  |  |  |  |

| cdbw[15:0]               | Primary core data bus used for program memory writes. (Only these 16 bits of the cdbw[31:0] bus are used for writes to program memory.)                                                                                                                           |  |  |  |  |  |

| pab[20:0]                | Program memory address bus. Data is returned on pdb_m bus.                                                                                                                                                                                                        |  |  |  |  |  |

|                          | Primary Data Memory Interface Bus                                                                                                                                                                                                                                 |  |  |  |  |  |

| cdbr_m[31:0]             | Primary core data bus for memory reads. Addressed via xab1 bus.                                                                                                                                                                                                   |  |  |  |  |  |

| cdbw[31:0]               | Primary core data bus for memory writes. Addressed via xab1 bus.                                                                                                                                                                                                  |  |  |  |  |  |

| xab1[23:0]               | Primary data address bus. Capable of addressing bytes <sup>1</sup> , words, and long data types. Data is written on cdbw and returned on cdbr_m. Also used to access memory-mapped I/O.                                                                           |  |  |  |  |  |

|                          | Secondary Data Memory Interface                                                                                                                                                                                                                                   |  |  |  |  |  |

| xdb2_m[15:0]             | Secondary data bus used for secondary data address bus xab2 in the dual memory reads.                                                                                                                                                                             |  |  |  |  |  |

| xab2[23:0]               | Secondary data address bus used for the second of two simultaneous accesses. Capable of addressing only words. Data is returned on xdb2_m.                                                                                                                        |  |  |  |  |  |

| Peripheral Interface Bus |                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| IPBus [15:0]             | Peripheral bus accesses all on-chip peripherals registers. This bus operates at the same clock rate as the Primary Data Memory and therefore generates no delays when accessing the processor. Write data is obtained from cdbw. Read data is provided to cdbr_m. |  |  |  |  |  |

#### Table 1-2 Bus Signal Names

1. Byte accesses can only occur in the bottom half of the memory address space. The MSB of the address will be forced to 0.

# **1.5 Product Documentation**

The documents in **Table 1-3** are required for a complete description and proper design with the 56F8347 and 56F8147 devices. Documentation is available from local Freescale distributors, Freescale semiconductor sales offices, Freescale Literature Distribution Centers, or online at **http://www.freescale.com/dsp**.

| Торіс                                        | Description                                                                                                                | Order Number             |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------|

| DSP56800E<br>Reference Manual                | Detailed description of the 56800E family architecture,<br>and 16-bit controller core processor and the instruction<br>set | DSP56800ERM              |

| 56F8300 Peripheral<br>User Manual            | Detailed description of peripherals of the 56F8300 devices                                                                 | MC56F8300UM              |

| 56F8300 SCI/CAN<br>Bootloader User<br>Manual | Detailed description of the SCI/CAN Bootloaders 56F8300 family of devices                                                  | MC56F83xxBLUM            |

| 56F8347/56F8147<br>Technical Data Sheet      | Electrical and timing specifications, pin descriptions,<br>and package descriptions (this document)                        | MC56F8347                |

| Errata                                       | Details any chip issues that might be present                                                                              | MC56F8347E<br>MC56F8147E |

| Table 1-3 Chip | Documentation |

|----------------|---------------|

|----------------|---------------|

# 1.6 Data Sheet Conventions

This data sheet uses the following conventions:

OVERBAR

This is used to indicate a signal that is active when pulled low. For example, the RESET pin is active when low.

"asserted" A high true (active high) signal is high or a low true (active low) signal is low.

"deasserted" A high true (active high) signal is low or a low true (active low) signal is high.

| Examples: | Signal/Symbol | Logic State | Signal State | Voltage <sup>1</sup>             |

|-----------|---------------|-------------|--------------|----------------------------------|

|           | PIN           | True        | Asserted     | V <sub>IL</sub> /V <sub>OL</sub> |

|           | PIN           | False       | Deasserted   | V <sub>IH</sub> /V <sub>OH</sub> |

|           | PIN           | True        | Asserted     | V <sub>IH</sub> /V <sub>OH</sub> |

|           | PIN           | False       | Deasserted   | V <sub>IL</sub> /V <sub>OL</sub> |

1. Values for VIL, VOL, VIH, and VOH are defined by individual product specifications.

# Part 2 Signal/Connection Descriptions

# 2.1 Introduction

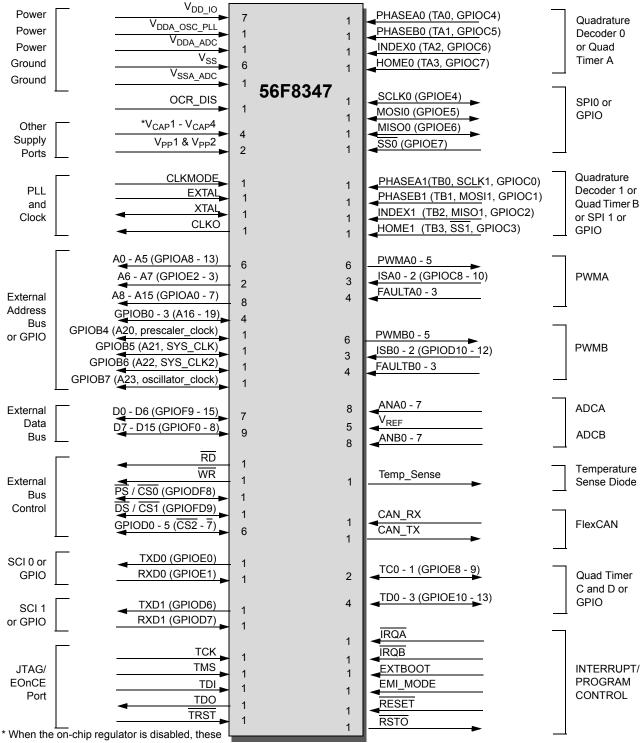

The input and output signals of the 56F8347 and 56F8147 are organized into functional groups, as detailed in **Table 2-1** and as illustrated in **Figure 2-2**. In **Table 2-2**, each table row describes the signal or signals present on a pin.

| Functional Oneur                                         | Number of Pi | Number of Pins in Package |  |  |  |

|----------------------------------------------------------|--------------|---------------------------|--|--|--|

| Functional Group                                         | 56F8347      | 56F8147                   |  |  |  |

| Power (V <sub>DD</sub> or V <sub>DDA</sub> )             | 9            | 9                         |  |  |  |

| Power Option Control                                     | 1            | 1                         |  |  |  |

| Ground (V <sub>SS</sub> or V <sub>SSA</sub> )            | 7            | 7                         |  |  |  |

| Supply Capacitors <sup>1</sup> & V <sub>PP</sub>         | 6            | 6                         |  |  |  |

| PLL and Clock                                            | 4            | 4                         |  |  |  |

| Address Bus                                              | 24           | 24                        |  |  |  |

| Data Bus                                                 | 16           | 16                        |  |  |  |

| Bus Control                                              | 10           | 10                        |  |  |  |

| Interrupt and Program Control                            | 6            | 6                         |  |  |  |

| Pulse Width Modulator (PWM) Ports                        | 26           | 13                        |  |  |  |

| Serial Peripheral Interface (SPI) Port 0                 | 4            | 4                         |  |  |  |

| Serial Peripheral Interface (SPI) Port 1                 | _            | 4                         |  |  |  |

| Quadrature Decoder Port 0 <sup>2</sup>                   | 4            | 4                         |  |  |  |

| Quadrature Decoder Port 1 <sup>3</sup>                   | 4            | _                         |  |  |  |

| Serial Communications Interface (SCI) Ports <sup>2</sup> | 4            | 4                         |  |  |  |

| CAN Ports                                                | 2            | _                         |  |  |  |

| Analog to Digital Converter (ADC) Ports                  | 21           | 21                        |  |  |  |

| Timer Module Ports                                       | 6            | 2                         |  |  |  |

| JTAG/Enhanced On-Chip Emulation (EOnCE)                  | 5            | 5                         |  |  |  |

| Temperature Sense                                        | 1            | _                         |  |  |  |

| Dedicated GPIO                                           | _            | 7                         |  |  |  |

1. If the on-chip regulator is disabled, the V<sub>CAP</sub> pins serve as 2.5V V<sub>DD</sub>  $_{\rm CORE}$  power inputs

2. Alternately, can function as Quad Timer pins

3. Pins in this section can function as Quad Timer, SPI #1, or GPIO

four pins become 2.5V V<sub>DD CORE</sub>.

#### Figure 2-1 56F8347 Signals Identified by Functional Group<sup>1</sup> (160-pin LQFP)

1. Alternate pin functionality is shown in parenthesis; pin direction/type shown is the default functionality.

these four pins become  $2.5V V_{DD_{CORE}}$ .

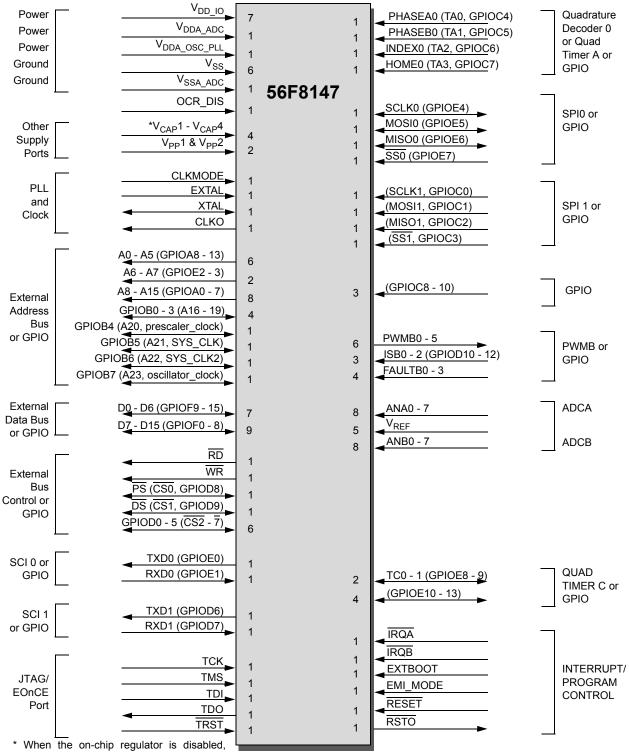

## Figure 2-2 56F8147 Signals Identified by Functional Group<sup>1</sup> (160-pin LQFP)

1. Alternate pin functionality is shown in parenthesis; pin direction/type shown is the default functionality.

# 2.2 Signal Pins

After reset, all pins are by default the primary function. Any alternate functionality must be programmed.

Note: Signals in italics are NOT available in the 56F8147 device.