Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### MC68020 MC68EC020

# MICROPROCESSORS USER'S MANUAL

**First Edition**

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and the Action Employer.

#### **PREFACE**

The M68020 User's Manual describes the capabilities, operation, and programming of the MC68020 32-bit, second-generation, enhanced microprocessor and the MC68EC020 32bit, second-generation, enhanced embedded microprocessor.

Throughout this manual, "MC68020/EC020" is used when information applies to both the MC68020 and the MC68EC020. "MC68020" and "MC68EC020" are used when information applies only to the MC68020 or MC68EC020, respectively.

For detailed information on the MC68020 and MC68EC020 instruction set, refer to M68000PM/AD, M68000 Family Programmer's Reference Manual.

This manual consists of the following sections:

- Section 1 Introduction Section 2 **Processing States** Section 3 Signal Description On-Chip Cache Memory Section 4 Section 5 **Bus Operation Exception Processing** Section 6 Section 7 Coprocessor Interface Description Instruction Execution Timing Section 8

- **Applications Information** Section 9 **Electrical Characteristics** Section 10

- Section 11 Ordering Information and Mechanical Data

- Appendix A Interfacing an MC68EC020 to a DMA Device That Supports a Three-Wire **Bus Arbitration Protocol**

#### NOTE

In this manual, assert and negate are used to specify forcing a signal to a particular state. In particular, assertion and assert refer to a signal that is active or true; negation and negate indicate a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent.

### **TABLE OF CONTENTS**

| Paragraph<br>Number                                                         | Title                                                                                                                                                                                                                                                                                                           | Page<br>Number                                       |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                                             | Section 1                                                                                                                                                                                                                                                                                                       |                                                      |

|                                                                             | Introduction                                                                                                                                                                                                                                                                                                    |                                                      |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.5.1<br>1.5.2<br>1.6<br>1.7             | Features Programming Model Data Types and Addressing Modes Overview Instruction Set Overview Virtual Memory and Virtual Machine Concepts Virtual Memory Virtual Machine Pipelined Architecture Cache Memory                                                                                                     | 1-4<br>1-8<br>1-10<br>1-10<br>1-12<br>1-12           |

|                                                                             | Section 2 Processing States                                                                                                                                                                                                                                                                                     |                                                      |

| 2.1<br>2.1.1<br>2.1.2<br>2.1.3<br>2.2<br>2.3<br>2.3.1<br>2.3.2              | Privilege Levels Supervisor Privilege Level User Privilege Level Changing Privilege Level Address Space Types Exception Processing Exception Vectors Exception Stack Frame                                                                                                                                      | 2-2<br>2-3<br>2-3<br>2-4<br>2-5                      |

|                                                                             | Section 3 Signal Description                                                                                                                                                                                                                                                                                    |                                                      |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11 | Signal Index Function Code Signals (FC2–FC0) Address Bus (A31–A0, MC68020)(A23–A0, MC68EC020) Data Bus (D31–D0) Transfer Size Signals (SIZ1, SIZ0) Asynchronous Bus Control Signals Interrupt Control Signals Bus Arbitration Control Signals Bus Exception Control Signals Emulator Support Signal Clock (CLK) | 3-2<br>3-2<br>3-2<br>3-2<br>3-4<br>3-5<br>3-6<br>3-6 |

| Paragraph<br>Number                                                                                                                                                               | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page<br>Number                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 3.12                                                                                                                                                                              | Power Supply Connections                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-7                                                                                                                                 |

| 3.13                                                                                                                                                                              | Signal Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-8                                                                                                                                 |

|                                                                                                                                                                                   | Section 4 On-Chip Cache Memory                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                     |

| 4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2                                                                                                                                               | On-Chip Cache Organization and Operation  Cache Reset  Cache Control  Cache Control Register (CACR)  Cache Address Register (CAAR)                                                                                                                                                                                                                                                                                                                                     | 4-3<br>4-3<br>4-3                                                                                                                   |

|                                                                                                                                                                                   | Section 5 Bus Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |

| 5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.4 | Bus Control Signals  Address Bus  Address Strobe  Data Bus  Data Strobe  Data Buffer Enable  Bus Cycle Termination Signals  Data Transfer Mechanism  Dynamic Bus Sizing  Misaligned Operands  Effects of Dynamic Bus Sizing and Operand Misalignment  Address, Size, and Data Bus Relationships  Cache Interactions  Bus Operation  Synchronous Operation with DSACK1/DSACK0  Data Transfer Cycles  Read Cycle  Write Cycle  Read-Modify-Write Cycle  CPU Space Cycles | 5-2<br>5-3<br>5-3<br>5-3<br>5-4<br>5-4<br>5-4<br>5-5<br>5-5<br>5-14<br>5-20<br>5-21<br>5-22<br>5-24<br>5-24<br>5-25<br>5-26<br>5-33 |

| 5.4<br>5.4.1<br>5.4.1.1<br>5.4.1.2<br>5.4.1.3<br>5.4.2<br>5.4.3<br>5.5<br>5.5.1                                                                                                   | Interrupt Acknowledge Bus Cycles Interrupt Acknowledge Cycle—Terminated Normally Autovector Interrupt Acknowledge Cycle Spurious Interrupt Cycle Breakpoint Acknowledge Cycle Coprocessor Communication Cycles Bus Exception Control Cycles Bus Errors                                                                                                                                                                                                                 | 5-45<br>5-48<br>5-48<br>5-50<br>5-53                                                                                                |

| Paragraph<br>Number | Title                                                        | Page<br>Number |

|---------------------|--------------------------------------------------------------|----------------|

| 5.5.2               | Retry Operation                                              | 5-56           |

| 5.5.3               | Halt Operation                                               |                |

| 5.5.4               | Double Bus Fault                                             |                |

| 5.6                 | Bus Synchronization                                          |                |

| 5.7                 | Bus Arbitration                                              |                |

| 5.7.1               | MC68020 Bus Arbitration                                      |                |

| 5.7.1.1             | Bus Request (MC68020)                                        |                |

| 5.7.1.2             | Bus Grant (MC68020)                                          |                |

| 5.7.1.3             | Bus Grant Acknowledge (MC68020)                              |                |

| 5.7.1.4             | Bus Arbitration Control (MC68020)                            |                |

| 5.7.2               | MC68EC020 Bus Arbitration                                    |                |

| 5.7.2.1             | Bus Request (MC68EC020)                                      |                |

| 5.7.2.2             | Bus Grant (MC68EC020)                                        |                |

| 5.7.2.3             | Bus Arbitration Control (MC68EC020)                          |                |

| 5.8                 | Reset Operation                                              | 5-76           |

|                     | Section 6                                                    |                |

|                     | Exception Processing                                         |                |

| 6.1                 | Exception Processing Sequence                                | 6-1            |

| 6.1.1               | Reset Exception                                              |                |

| 6.1.2               | Bus Error Exception                                          |                |

| 6.1.3               | Address Error Exception                                      |                |

| 6.1.4               | Instruction Trap Exception                                   |                |

| 6.1.5               | Illegal Instruction and Unimplemented Instruction Exceptions | 6-7            |

| 6.1.6               | Privilege Violation Exception                                |                |

| 6.1.7               | Trace Exception                                              | 6-9            |

| 6.1.8               | Format Error Exception                                       | 6-10           |

| 6.1.9               | Interrupt Exceptions                                         | 6-11           |

| 6.1.10              | Breakpoint Instruction Exception                             |                |

| 6.1.11              | Multiple Exceptions                                          | 6-17           |

| 6.1.12              | Return from Exception                                        | 6-19           |

| 6.2                 | Bus Fault Recovery                                           | 6-21           |

| 6.2.1               | Special Status Word (SSW)                                    |                |

| 6.2.2               | Using Software to Complete the Bus Cycles                    | 6-23           |

| 6.2.3               | Completing the Bus Cycles with RTE                           |                |

| 6.3                 | Coprocessor Considerations                                   |                |

| 6.4                 | Exception Stack Frame Formats                                | 6-25           |

| Paragraph            | Tialo                                                      | Page   |

|----------------------|------------------------------------------------------------|--------|

| Number               | Title                                                      | Number |

|                      | Section 7                                                  |        |

|                      | Coprocessor Interface Description                          |        |

| 7.1                  | Introduction                                               | 7-1    |

| 7.1.1                | Interface Features                                         | 7-2    |

| 7.1.2                | Concurrent Operation Support                               | 7-2    |

| 7.1.3                | Coprocessor Instruction Format                             | 7-3    |

| 7.1.4                | Coprocessor System Interface                               |        |

| 7.1.4.1              | Coprocessor Classification                                 |        |

| 7.1.4.2              | Processor-Coprocessor Interface                            | 7-5    |

| 7.1.4.3              | Coprocessor Interface Register Selection                   |        |

| 7.2                  | Coprocessor Instruction Types                              |        |

| 7.2.1                | Coprocessor General Instructions                           |        |

| 7.2.1.1              | Format                                                     |        |

| 7.2.1.2              | Protocol                                                   |        |

| 7.2.2                | Coprocessor Conditional Instructions                       |        |

| 7.2.2.1              | Branch on Coprocessor Condition Instruction                |        |

| 7.2.2.1.1            | Format                                                     |        |

| 7.2.2.1.2            | Protocol                                                   |        |

| 7.2.2.2              | Set on Coprocessor Condition Instruction                   |        |

| 7.2.2.2.1            | Format                                                     |        |

| 7.2.2.2.2            | Protocol                                                   |        |

| 7.2.2.3              | Test Coprocessor Condition, Decrement, and Branch Instruct |        |

| 7.2.2.3.1            | Format                                                     |        |

| 7.2.2.3.2            | Protocol                                                   |        |

| 7.2.2.4              | Trap on Coprocessor Condition Instruction                  |        |

| 7.2.2.4.1            | Format                                                     |        |

| 7.2.2.4.2            | Protocol                                                   |        |

| 7.2.3                | Coprocessor Context Save and Restore Instructions          |        |

| 7.2.3.1              | Coprocessor Internal State Frames                          |        |

| 7.2.3.2              | Coprocessor Format Words                                   |        |

| 7.2.3.2.1            | Empty/Reset Format Word                                    |        |

| 7.2.3.2.2            | Not-Ready Format Word                                      |        |

| 7.2.3.2.3            | Invalid Format Word                                        |        |

| 7.2.3.2.4            | Valid Format Word                                          |        |

| 7.2.3.3              | Coprocessor Context Save Instruction                       |        |

| 7.2.3.3.1            | Format                                                     |        |

| 7.2.3.3.2            | Protocol                                                   |        |

| 7.2.3.4<br>7.2.3.4.1 | Coprocessor Context Restore Instruction Format             |        |

| 7.2.3.4.1            |                                                            |        |

|                      | Protocol                                                   |        |

| 7.3                  | Coprocessor Interface Register Set                         | / -24  |

UM Rev 1

| Paragraph<br>Number | Title                                                     | Page<br>Number |

|---------------------|-----------------------------------------------------------|----------------|

| 7.3.1               | Response CIR                                              | 7-24           |

| 7.3.2               | Control CIR                                               | 7-24           |

| 7.3.3               | Save CIR                                                  | 7-25           |

| 7.3.4               | Restore CIR                                               | 7-25           |

| 7.3.5               | Operation Word CIR                                        |                |

| 7.3.6               | Command CIR                                               | 7-25           |

| 7.3.7               | Condition CIR                                             | 7-26           |

| 7.3.8               | Operand CIR                                               | 7-26           |

| 7.3.9               | Register Select CIR                                       | 7-27           |

| 7.3.10              | Instruction Address CIR                                   | 7-27           |

| 7.3.11              | Operand Address CIR                                       |                |

| 7.4                 | Coprocessor Response Primitives                           | 7-27           |

| 7.4.1               | ScanPC                                                    |                |

| 7.4.2               | Coprocessor Response Primitive General Format             | 7-28           |

| 7.4.3               | Busy Primitive                                            | 7-30           |

| 7.4.4               | Null Primitive                                            | 7-31           |

| 7.4.5               | Supervisor Check Primitive                                | 7-33           |

| 7.4.6               | Transfer Operation Word Primitive                         | 7-33           |

| 7.4.7               | Transfer from Instruction Stream Primitive                | 7-34           |

| 7.4.8               | Evaluate and Transfer Effective Address Primitive         | 7-35           |

| 7.4.9               | Evaluate Effective Address and Transfer Data Primitive    | 7-35           |

| 7.4.10              | Write to Previously Evaluated Effective Address Primitive | 7-37           |

| 7.4.11              | Take Address and Transfer Data Primitive                  | 7-39           |

| 7.4.12              | Transfer to/from Top of Stack Primitive                   | 7-40           |

| 7.4.13              | Transfer Single Main Processor Register Primitive         | 7-40           |

| 7.4.14              | Transfer Main Processor Control Register Primitive        |                |

| 7.4.15              | Transfer Multiple Main Processor Registers Primitive      | 7-42           |

| 7.4.16              | Transfer Multiple Coprocessor Registers Primitive         | 7-42           |

| 7.4.17              | Transfer Status Register and ScanPC Primitive             | 7-44           |

| 7.4.18              | Take Preinstruction Exception Primitive                   | 7-45           |

| 7.4.19              | Take Midinstruction Exception Primitive                   | 7-47           |

| 7.4.20              | Take Postinstruction Exception Primitive                  | 7-48           |

| 7.5                 | Exceptions                                                | 7-49           |

| 7.5.1               | Coprocessor-Detected Exceptions                           | 7-49           |

| 7.5.1.1             | Coprocessor-Detected Protocol Violations                  | 7-50           |

| 7.5.1.2             | Coprocessor-Detected Illegal Command or Condition Words.  |                |

| 7.5.1.3             | Coprocessor Data-Processing-Related Exceptions            |                |

| 7.5.1.4             | Coprocessor System-Related Exceptions                     |                |

| 7.5.1.5             | Format Errors                                             |                |

| 7.5.2               | Main-Processor-Detected Exceptions                        |                |

| 7.5.2.1             | Protocol Violations                                       |                |

| 7.5.2.2             | F-Line Emulator Exceptions                                | 7-54           |

| Paragraph<br>Number | Title                                     | Page<br>Number |

|---------------------|-------------------------------------------|----------------|

| 7.5.2.3             | Privilege Violations                      | 7-55           |

| 7.5.2.4             | cpTRAPcc Instruction Traps                |                |

| 7.5.2.5             | Trace Exceptions                          |                |

| 7.5.2.6             | Interrupts                                |                |

| 7.5.2.7             | Format Errors                             |                |

| 7.5.2.8             | Address and Bus Errors                    |                |

| 7.5.3               | Coprocessor Reset                         | 7-58           |

| 7.6                 | Coprocessor Summary                       |                |

|                     | Section 8 Instruction Execution Timing    |                |

| 8.1                 | Timing Estimation Factors                 | 8-1            |

| 8.1.1               | Instruction Cache and Prefetch            |                |

| 8.1.2               | Operand Misalignment                      |                |

| 8.1.3               | Bus/Sequencer Concurrency                 |                |

| 8.1.4               | Instruction Execution Overlap             |                |

| 8.1.5               | Instruction Stream Timing Examples        |                |

| 8.2                 | Instruction Timing Tables                 |                |

| 8.2.1               | Fetch Effective Address                   |                |

| 8.2.2               | Fetch Immediate Effective Address         |                |

| 8.2.3               | Calculate Effective Address               |                |

| 8.2.4               | Calculate Immediate Effective Address     |                |

| 8.2.5               | Jump Effective Address                    | 8-19           |

| 8.2.6               | MOVE Instruction                          |                |

| 8.2.7               | Special-Purpose MOVE Instruction          | 8-29           |

| 8.2.8               | Arithmetic/Logical Instructions           |                |

| 8.2.9               | Immediate Arithmetic/Logical Instructions |                |

| 8.2.10              | Binary-Coded Decimal Operations           |                |

| 8.2.11              | Single-Operand Instructions               |                |

| 8.2.12              | Shift/Rotate Instructions                 | 8-34           |

| 8.2.13              | Bit Manipulation Instructions             | 8-35           |

| 8.2.14              | Bit Field Manipulation Instructions       |                |

| 8.2.15              | Conditional Branch Instructions           |                |

| 8.2.16              | Control Instructions                      |                |

| 8.2.17              | Exception-Related Instructions            |                |

| 8.2.18              | Save and Restore Operations               |                |

|                     | Section 9 Applications Information        |                |

| 0.1                 | • •                                       | 0.4            |

| 9.1                 | Floating-Point Units                      | 9-1            |

| 9.2                 |                                           |                |

| 9.3                 | Power and Ground Considerations           | 9-9            |

### **TABLE OF CONTENTS (Concluded)**

| Paragraph<br>Number | Title                                                               | Page<br>Number |

|---------------------|---------------------------------------------------------------------|----------------|

| 9.4                 | Clock Driver                                                        | 9-10           |

| 9.5                 | Memory Interface                                                    |                |

| 9.6                 | Access Time Calculations                                            |                |

| 9.7                 | Module Support                                                      |                |

| 9.7.1               | Module Descriptor                                                   |                |

| 9.7.2               | Module Stack Frame                                                  |                |

| 9.8                 | Access Levels                                                       |                |

| 9.8.1               | Module Call                                                         |                |

| 9.8.2               | Module Return                                                       | 9-19           |

|                     | Section 10                                                          |                |

|                     | Electrical Characteristics                                          |                |

| 10.1                | Maximum Ratings                                                     |                |

| 10.2                | Thermal Considerations                                              | 10-1           |

| 10.2.1              | MC68020 Thermal Characteristics and                                 | 40.0           |

| 1000                | DC Electrical Characteristics                                       | 10-2           |

| 10.2.2              | MC68EC020 Thermal Characteristics and DC Electrical Characteristics | 10.4           |

| 10.3                | AC Electrical Characteristics                                       |                |

| 10.0                |                                                                     | 10 0           |

|                     | Section 11 Ordering Information and Mechanical Data                 |                |

| 11.1                | Standard Ordering Information                                       | 11 1           |

| 11.1.1              | Standard MC68020 Ordering Information                               |                |

| 11.1.2              | Standard MC68EC020 Ordering Information                             |                |

| 11.2                | Pin Assignments and Package Dimensions                              |                |

| 11.2.1              | MC68020 RC and RP Suffix—Pin Assignment                             |                |

| 11.2.2              | MC68020 RC Suffix—Package Dimensions                                |                |

| 11.2.3              | MC68020 RP Suffix—Package Dimensions                                | 11-4           |

| 11.2.4              | MC68020 FC and FE Suffix—Pin Assignment                             | 11-5           |

| 11.2.5              | MC68020 FC Suffix—Package Dimensions                                |                |

| 11.2.6              | MC68020 FE Suffix—Package Dimensions                                |                |

| 11.2.7              | MC68EC020 RP Suffix—Pin Assignment                                  |                |

| 11.2.8              | MC68EC020 RP Suffix—Package Dimensions                              |                |

| 11.2.9              | MC68EC020 FG Suffix—Pin Assignment                                  |                |

| 11.2.10             | MC68EC020 FG Suffix—Package Dimensions                              | 11-11          |

Appendix A

Interfacing an MC68EC020 to a DMA Device That

Supports a Three-Wire Bus Arbitration Protocol

### LIST OF ILLUSTRATIONS

| Figure<br>Numbe                                                                                                      |                                                                                                                                  | Page<br>Number                                                                                     |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5                                                                                      | MC68020/EC020 Block Diagram User Programming Model Supervisor Programming Model Supplement Status Register (SR) Instruction Pipe | 1-5<br>1-6<br>1-7                                                                                  |

| 2-1                                                                                                                  | General Exception Stack Frame                                                                                                    | 2-6                                                                                                |

| 3-1                                                                                                                  | Functional Signal Groups                                                                                                         | 3-1                                                                                                |

| 4-1<br>4-2<br>4-3                                                                                                    | MC68020/EC020 On-Chip Cache Organization  Cache Control Register  Cache Address Register                                         | 4-3                                                                                                |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8<br>5-10<br>5-11<br>5-12<br>5-13<br>5-14<br>5-15<br>5-16<br>5-17 | Relationship between External and Internal Signals                                                                               | 5-2<br>5-6<br>5-10<br>5-11<br>5-12<br>5-13<br>5-14<br>5-16<br>5-16<br>5-16<br>5-18<br>5-18<br>5-18 |

| 5-19<br>5-20<br>5-21                                                                                                 | Long-Word Read Cycle Flowchart                                                                                                   | 5-26<br>5-27<br>5-28                                                                               |

| 5-22<br>5-23                                                                                                         | Long-Word Read—8-Bit Port<br>Long-Word Read—16- and 32-Bit Ports                                                                 |                                                                                                    |

### **LIST OF ILLUSTRATIONS (Continued)**

| Figure<br>Numbe |                                                                | Page<br>Number |

|-----------------|----------------------------------------------------------------|----------------|

| 5-24            | Write Cycle Flowchart                                          | 5-33           |

| 5-25            | Read-Write-Read Cycles—32-Bit Port                             | 5-34           |

| 5-26            | Byte and Word Write Cycles—32-Bit Port                         |                |

| 5-27            | Long-Word Operand Write—8-Bit Port                             |                |

| 5-28            | Long-Word Operand Write—16-Bit Port                            |                |

| 5-29            | Read-Modify-Write Cycle Flowchart                              | 5-40           |

| 5-30            | Byte Read-Modify-Write Cycle—32-Bit Port (TAS Instruction)     | 5-41           |

| 5-31            | MC68020/EC020 CPU Space Address Encoding                       |                |

| 5-32            | Interrupt Acknowledge Cycle Flowchart                          |                |

| 5-33            | Interrupt Acknowledge Cycle Timing                             |                |

| 5-34            | Autovector Operation Timing                                    |                |

| 5-35            | Breakpoint Acknowledge Cycle Flowchart                         | 5-50           |

| 5-36            | Breakpoint Acknowledge Cycle Timing                            | 5-51           |

| 5-37            | Breakpoint Acknowledge Cycle Timing (Exception Signaled)       | 5-52           |

| 5-38            | Bus Error without DSACK1/DSACK0                                | 5-57           |

| 5-39            | Late Bus Error with DSACK1/DSACK0                              | 5-58           |

| 5-40            | Late Retry                                                     | 5-59           |

| 5-41            | Halt Operation Timing                                          |                |

| 5-42            | MC68020 Bus Arbitration Flowchart for Single Request           | 5-64           |

| 5-43            | MC68020 Bus Arbitration Operation Timing for Single Request    | 5-65           |

| 5-44            | MC68020 Bus Arbitration State Diagram                          | 5-67           |

| 5-45            | MC68020 Bus Arbitration Operation Timing—Bus Inactive          | 5-69           |

| 5-46            | MC68EC020 Bus Arbitration Flowchart for Single Request         | 5-71           |

| 5-47            | MC68EC020 Bus Arbitration Operation Timing for Single Request  | 5-72           |

| 5-48            | MC68EC020 Bus Arbitration State Diagram                        |                |

| 5-49            | MC68EC020 Bus Arbitration Operation Timing—Bus Inactive        |                |

| 5-50            | Interface for Three-Wire to Two-Wire Bus Arbitration           |                |

| 5-51            | Initial Reset Operation Timing                                 |                |

| 5-52            | RESET Instruction Timing                                       | 5-78           |

| 6-1             | Reset Operation Flowchart                                      |                |

| 6-2             | Interrupt Pending Procedure                                    |                |

| 6-3             | Interrupt Recognition Examples                                 |                |

| 6-4             | Assertion of IPEND (MC68020 Only)                              | 6-14           |

| 6-5             | Interrupt Exception Processing Flowchart                       |                |

| 6-6             | Breakpoint Instruction Flowchart                               |                |

| 6-7             | RTE Instruction for Throwaway Four-Word Frame                  | 6-20           |

| 6-8             | Special Status Word Format                                     | 6-22           |

| 7-1             | F-Line Coprocessor Instruction Operation Word                  | 7-3            |

| 7-2             | Asynchronous Non-DMA M68000 Coprocessor Interface Signal Usage |                |

| 7-3             | MC68020/EC020 CPU Space Address Encodings                      | 7-6            |

### **LIST OF ILLUSTRATIONS (Continued)**

| Figure<br>Numbe |                                                                      | Page<br>Number |

|-----------------|----------------------------------------------------------------------|----------------|

| 7-4             | Coprocessor Address Map in MC68020/EC020 CPU Space                   | 7-7            |

| 7-5             | Coprocessor Interface Register Set Map                               | 7-7            |

| 7-6             | Coprocessor General Instruction Format (cpGEN)                       | 7-8            |

| 7-7             | Coprocessor Interface Protocol for General Category Instructions     | 7-10           |

| 7-8             | Coprocessor Interface Protocol for Conditional Category Instructions |                |

| 7-9             | Branch on Coprocessor Condition Instruction Format (cpBcc.W)         | 7-12           |

| 7-10            | Branch on Coprocessor Condition Instruction Format (cpBcc.L)         | 7-12           |

| 7-11            | Set on Coprocessor Condition Instruction Format (cpScc)              | 7-13           |

| 7-12            | Test Coprocessor Condition, Decrement, and Branch                    |                |

|                 | Instruction Format (cpDBcc)                                          | 7-14           |

| 7-13            | Trap on Coprocessor Condition Instruction Format (cpTRAPcc)          | 7-15           |

| 7-14            | Coprocessor State Frame Format in Memory                             | 7-17           |

| 7-15            | Coprocessor Context Save Instruction Format (cpSAVE)                 | 7-20           |

| 7-16            | Coprocessor Context Save Instruction Protocol                        | 7-21           |

| 7-17            | Coprocessor Context Restore Instruction Format (cpRESTORE)           |                |

| 7-18            | Coprocessor Context Restore Instruction Protocol                     |                |

| 7-19            | Control CIR Format                                                   | 7-25           |

| 7-20            | Condition CIR Format                                                 |                |

| 7-21            | Operand Alignment for Operand CIR Accesses                           |                |

| 7-22            | Coprocessor Response Primitive Format                                |                |

| 7-23            | Busy Primitive Format                                                |                |

| 7-24            | Null Primitive Format                                                |                |

| 7-25            | Supervisor Check Primitive Format                                    |                |

| 7-26            | Transfer Operation Word Primitive Format                             |                |

| 7-27            | Transfer from Instruction Stream Primitive Format                    |                |

| 7-28            | Evaluate and Transfer Effective Address Primitive Format             |                |

| 7-29            | Evaluate Effective Address and Transfer Data Primitive Format        |                |

| 7-30            | Write to Previously Evaluated Effective Address Primitive Format     |                |

| 7-31            | Take Address and Transfer Data Primitive Format                      |                |

| 7-32            | Transfer to/from Top of Stack Primitive Format                       |                |

| 7-33            | Transfer Single Main Processor Register Primitive Format             |                |

| 7-34            | Transfer Main Processor Control Register Primitive Format            |                |

| 7-35            | Transfer Multiple Main Processor Registers Primitive Format          |                |

| 7-36            | Register Select Mask Format                                          |                |

| 7-37            | Transfer Multiple Coprocessor Registers Primitive Format             |                |

| 7-38            | Operand Format in Memory for Transfer to –(An)                       |                |

| 7-39            | Transfer Status Register and ScanPC Primitive Format                 |                |

| 7-40            | Take Preinstruction Exception Primitive Format                       |                |

| 7-41            | MC68020/EC020 Preinstruction Stack Frame                             |                |

| 7-42            | Take Midinstruction Exception Primitive Format                       |                |

| 7-43            | MC68020/EC020 Midinstruction Stack Frame                             |                |

| 7-44            | Take Postinstruction Exception Primitive Format                      | /-48           |

### LIST OF ILLUSTRATIONS (Concluded)

| Figur<br>Numb                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                         | Page<br>Number                                           |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 7-45                                                                                        | MC68020/EC020 Postinstruction Stack Frame                                                                                                                                                                                                                                                                                                                                                                               | 7-48                                                     |

| 8-1<br>8-2<br>8-3<br>8-4<br>8-5<br>8-6                                                      | Concurrent Instruction Execution                                                                                                                                                                                                                                                                                                                                                                                        | 8-3<br>8-5<br>8-6<br>8-7                                 |

| 9-1<br>9-2<br>9-3<br>9-4<br>9-5<br>9-6<br>9-7<br>9-8<br>9-9<br>9-10<br>9-11<br>9-12<br>9-13 | 32-Bit Data Bus Coprocessor Connection Chip Select Generation PAL Chip Select PAL Equations Bus Cycle Timing Diagram Example MC68020/EC020 Byte Select PAL System Configuration MC68020/EC020 Byte Select PAL Equations High-Resolution Clock Controller Alternate Clock Solution Access Time Computation Diagram Module Descriptor Format Module Entry Word Module Call Stack Frame Access Level Control Bus Registers | 9-3<br>9-4<br>9-7<br>9-8<br>9-11<br>9-12<br>9-15<br>9-16 |

| 10-1<br>10-2<br>10-3<br>10-4<br>10-5                                                        | Drive Levels and Test Points for AC Specifications  Clock Input Timing Diagram  Read Cycle Timing Diagram  Write Cycle Timing Diagram  Bus Arbitration Timing Diagram                                                                                                                                                                                                                                                   | 10-7<br>10-11<br>10-12                                   |

| Δ_1                                                                                         | Rus Arbitration Circuit—MC68EC020 (Two-Wire) to DMA (Three-Wire)                                                                                                                                                                                                                                                                                                                                                        | Δ_1                                                      |

### **LIST OF TABLES**

| Table<br>Numbe                         |                                                                                                                                                                                                                                       | Page<br>Number               |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 1-1<br>1-2                             | Addressing Modes Instruction Set                                                                                                                                                                                                      |                              |

| 2-1                                    | Address Space Encodings                                                                                                                                                                                                               |                              |

| 3-1<br>3-2                             | Signal IndexSignal Summary                                                                                                                                                                                                            | 3-3                          |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5        | DSACK1/DSACK0 Encodings and Results                                                                                                                                                                                                   | 5-5<br>5-7<br>5-7<br>5-8     |

| 5-6<br>5-7<br>5-8                      | Write Cycles                                                                                                                                                                                                                          | 5-20<br>5-22                 |

| 6-1<br>6-2<br>6-3<br>6-4<br>6-5        | Exception Vector Assignments                                                                                                                                                                                                          | 6-9<br>6-12<br>6-18          |

| 7-1<br>7-2<br>7-3<br>7-4<br>7-5<br>7-6 | cpTRAPcc Opmode Encodings Coprocessor Format Word Encodings Null Coprocessor Response Primitive Encodings Valid Effective Address Field Codes Main Processor Control Register Select Codes Exceptions Related to Primitive Processing | 7-18<br>7-32<br>7-36<br>7-41 |

| 8-1<br>8-2<br>8-3                      | Examples 1–4 Instruction Stream Execution Comparison                                                                                                                                                                                  | 8-11                         |

### **LIST OF TABLES (Continued)**

| Table<br>Numbe |                                                                     | Page<br>Numbei |

|----------------|---------------------------------------------------------------------|----------------|

| 9-1            | Data Bus Activity for Byte, Word, and Long-Word Ports               | 9-6            |

| 9-2            | V <sub>CC</sub> and GND Pin Assignments—MC68EC020 PPGA (RP Suffix)  | 9-10           |

| 9-3            | V <sub>CC</sub> and GND Pin Assignments—MC68EC020 PQFP (FG Sufffix) | 9-10           |

| 9-4            | Memory Access Time Equations at 16.67 and 25 MHz                    | 9-13           |

| 9-5            | Calculated t <sub>AVDV</sub> Values for Operation at Frequencies    |                |

|                | Less Than or Equal to the CPU Maximum Frequency Rating              | 9-14           |

| 9-6            | Access Status Register Codes                                        | 9-18           |

| 10-1           | θ <sub>JA</sub> vs. Airflow—MC68020 CQFP Package                    | 10-3           |

| 10-2           | Power vs. Rated Frequency (at T <sub>J</sub> Maximum = 110°C)       |                |

| 10-3           | Temperature Rise of Board vs. PD—MC68020 CQFP Package               |                |

| 10-4           | θ ι vs. Airflow—MC68EC020 PQFP Package                              |                |

#### MC68020/EC020 ACRONYM LIST

BCD — Binary-Coded Decimal

CAAR — Cache Address Register

CACR — Cache Control Register

CCR — Condition Code Register

CIR — Coprocessor Interface Register

CMOS — Complementary Metal Oxide Semiconductor

CPU — Central Processing Unit

CQFP — Ceramic Quad Flat Pack

DDMA — Dual-Channel Direct Memory Access

DFC — Destination Function Code Register

DMA — Direct Memory Access

DRAM — Dynamic Random Access Memory

FPCP — Floating-Point Coprocessor

HCMOS — High-Density Complementary Metal Oxide Semiconductor

IEEE — Institute of Electrical and Electronic Engineers

ISP — Interrupt Stack Pointer

LMB — Lower Middle Byte

LRAR — Limited Rate Auto Request

LSB — Least Significant Byte

MMU — Memory Management Unit

MPU — Microprocessor Unit

MSB — Most Significant Byte

MSP — Master Stack Pointer

NMOS — n-Type Metal Oxide Semiconductor

PAL — Programmable Array Logic

PC — Program Counter

PGA — Pin Grid Array

PMMU — Paged Memory Management Unit

PPGA — Plastic Pin Grid Array

PQFP — Plastic Quad Flat Pack

RAM — Random Access Memory

SFC — Source Function Code Register

SP — Stack Pointer

SR — Status Register

SSP — Supervisor Stack Pointer

SSW — Special Status Word

UMB — Upper Middle Byte

USP — User Stack Pointer

VBR — Vector Base Register

VLSI — Very Large Scale Integration

## SECTION 1 INTRODUCTION

The MC68020 is the first full 32-bit implementation of the M68000 family of microprocessors from Motorola. Using VLSI technology, the MC68020 is implemented with 32-bit registers and data paths, 32-bit addresses, a rich instruction set, and versatile addressing modes.

The MC68020 is object-code compatible with earlier members of the M68000 family and has the added features of new addressing modes in support of high-level languages, an on-chip instruction cache, and a flexible coprocessor interface with full IEEE floating-point support (the MC68881 and MC68882). The internal operations of this microprocessor operate in parallel, allowing multiple instructions to be executed concurrently.

The asynchronous bus structure of the MC68020 uses a nonmultiplexed bus with 32 bits of address and 32 bits of data. The processor supports a dynamic bus sizing mechanism that allows the processor to transfer operands to or from external devices while automatically determining device port size on a cycle-by-cycle basis. The dynamic bus interface allows access to devices of differing data bus widths, in addition to eliminating all data alignment restrictions.

The MC68EC020 is an economical high-performance embedded microprocessor based on the MC68020 and has been designed specifically to suit the needs of the embedded microprocessor market. The major differences in the MC68EC020 and the MC68020 are that the MC68EC020 has a 24-bit address bus and does not implement the following signals: ECS, OCS, DBEN, IPEND, and BGACK. Also, the available packages and frequencies differ for the MC68020 and MC68EC020 (see **Section 11 Ordering Information and Mechanical Data**.) Unless otherwise stated, information in this manual applies to both the MC68020 and the MC68EC020.

#### 1.1 FEATURES

The main features of the MC68020/EC020 are as follows:

- Object-Code Compatible with Earlier M68000 Microprocessors

- Addressing Mode Extensions for Enhanced Support of High-Level Languages

- New Bit Field Data Type Accelerates Bit-Oriented Applications—e.g., Video Graphics

- An On-Chip Instruction Cache for Faster Instruction Execution

- Coprocessor Interface to Companion 32-Bit Peripherals—the MC68881 and MC68882 Floating-Point Coprocessors and the MC68851 Paged Memory Management Unit

- Pipelined Architecture with High Degree of Internal Parallelism Allowing Multiple Instructions To Be Executed Concurrently

- · High-Performance Asynchronous Bus Is Nonmultiplexed and Full 32 Bits

- Dynamic Bus Sizing Efficiently Supports 8-/16-/32-Bit Memories and Peripherals

- · Full Support of Virtual Memory and Virtual Machine

- Sixteen 32-Bit General-Purpose Data and Address Registers

- Two 32-Bit Supervisor Stack Pointers and Five Special-Purpose Control Registers

- Eighteen Addressing Modes and Seven Data Types

- 4-Gbyte Direct Addressing Range for the MC68020

- 16-Mbyte Direct Addressing Range for the MC68EC020

- Selection of Processor Speeds for the MC68020: 16.67, 20, 25, and 33.33 MHz

- Selection of Processor Speeds for the MCEC68020: 16.67 and 25 MHz

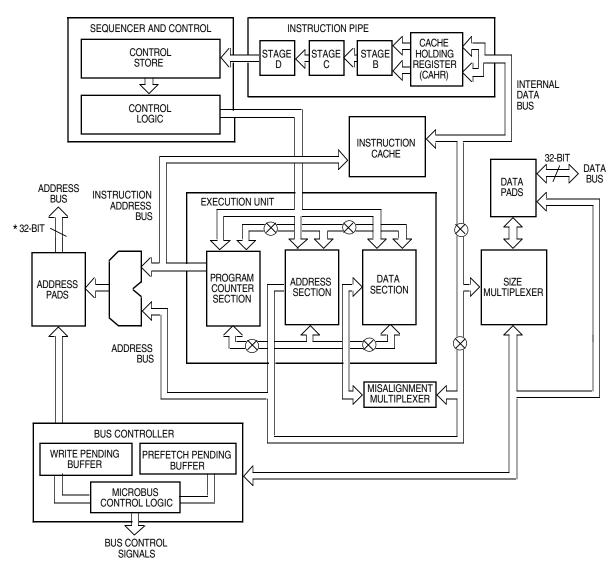

A block diagram of the MC68020/EC020 is shown in Figure 1-1.

1-2

\* 24-Bit for MC68EC020

Figure 1-1. MC68020/EC020 Block Diagram

#### 1.2 PROGRAMMING MODEL

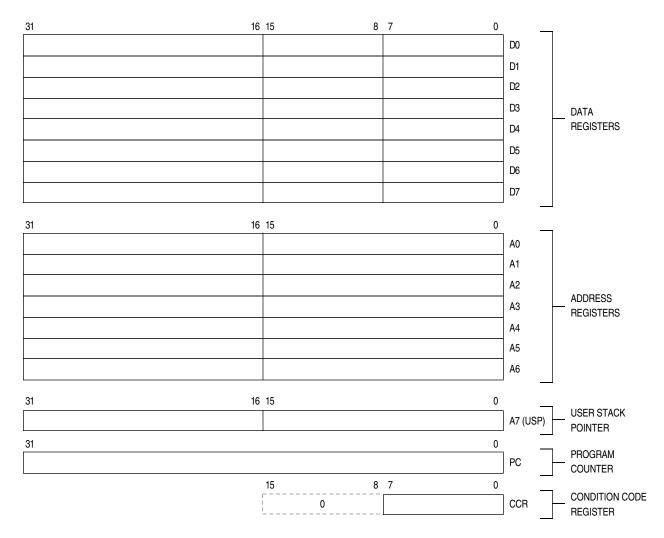

The programming model of the MC68020/EC020 consists of two groups of registers, the user model and the supervisor model, that correspond to the user and supervisor privilege levels, respectively. User programs executing at the user privilege level use the registers of the user model. System software executing at the supervisor level uses the control registers of the supervisor level to perform supervisor functions.

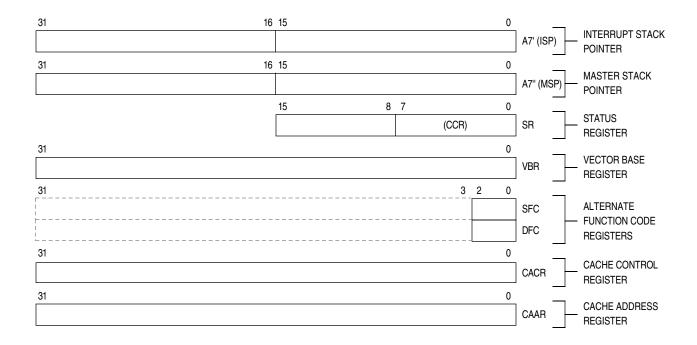

As shown in the programming models (see Figures 1-2 and 1-3), the MC68020/EC020 has 16 32-bit general-purpose registers, a 32-bit PC two 32-bit SSPs, a 16-bit SR, a 32-bit VBR, two 3-bit alternate function code registers, and two 32-bit cache handling (address and control) registers.

The user programming model remains unchanged from earlier M68000 family microprocessors. The supervisor programming model supplements the user programming model and is used exclusively by MC68020/EC020 system programmers who utilize the supervisor privilege level to implement sensitive operating system functions. The supervisor programming model contains all the controls to access and enable the special features of the MC68020/EC020. All application software, written to run at the nonprivileged user level, migrates to the MC68020/EC020 from any M68000 platform without modification.

Registers D7–D0 are data registers used for bit and bit field (1 to 32 bits), byte (8 bit), word (16 bit), long-word (32 bit), and quad-word (64 bit) operations. Registers A6–A0 and the USP, ISP, and MSP are address registers that may be used as software stack pointers or base address registers. Register A7 (shown as A7 in Figure 1-2 and as A7' and A7" in Figure 1-3) is a register designation that applies to the USP in the user privilege level and to either the ISP or MSP in the supervisor privilege level. In the supervisor privilege level, the active stack pointer (interrupt or master) is called the SSP. In addition, the address registers may be used for word and long-word operations. All of the 16 general-purpose registers (D7–D0, A7–A0) may be used as index registers.

The PC contains the address of the next instruction to be executed by the MC68020/EC020. During instruction execution and exception processing, the processor automatically increments the contents of the PC or places a new value in the PC, as appropriate.

Figure 1-2. User Programming Model

Figure 1-3. Supervisor Programming Model Supplement

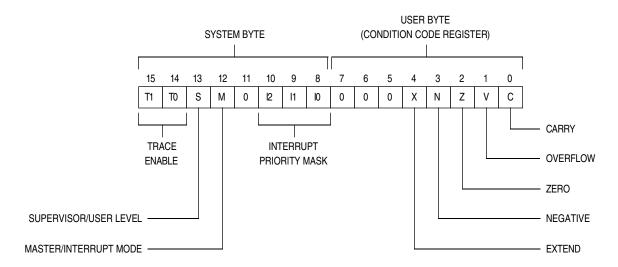

The SR (see Figure 1-4) stores the processor status. It contains the condition codes that reflect the results of a previous operation and can be used for conditional instruction execution in a program. The condition codes are extend (X), negative (N), zero (Z), overflow (V), and carry (C). The user byte, which contains the condition codes, is the only portion of the SR information available in the user privilege level, and it is referenced as the CCR in user programs. In the supervisor privilege level, software can access the entire SR, including the interrupt priority mask (three bits) and control bits that indicate whether the processor is in:

- 1. One of two trace modes (T1, T0)

- 2. Supervisor or user privilege level (S)

- 3. Master or interrupt mode (M)

Figure 1-4. Status Register (SR)

The VBR contains the base address of the exception vector table in memory. The displacement of an exception vector is added to the value in this register to access the vector table.

The alternate function code registers, SFC and DFC, contain 3-bit function codes. For the MC68020, function codes can be considered extensions of the 32-bit linear address that optionally provide as many as eight 4-Gbyte address spaces; for the MC68EC020, function codes can be considered extensions of the 24-bit linear address that optionally provide as many as eight 16-Mbyte address spaces. Function codes are automatically generated by the processor to select address spaces for data and program at the user and supervisor privilege levels and to select a CPU address space for processor functions (e.g., coprocessor communications). Registers SFC and DFC are used by certain instructions to explicitly specify the function codes for operations.

The CACR controls the on-chip instruction cache of the MC68020/EC020. The CAAR stores an address for cache control functions.

#### 1.3 DATA TYPES AND ADDRESSING MODES OVERVIEW

For detailed information on the data types and addressing modes supported by the MC68020/EC020, refer to M68000PM/AD, *M68000 Family Programmer's Reference Manual*.

The MC68020/EC020 supports seven basic data types:

- 1. Bits

- 2. Bit Fields (Fields of consecutive bits, 1–32 bits long)

- 3. BCD Digits (Packed: 2 digits/byte, Unpacked: 1 digit/byte)

- 4. Byte Integers (8 bits)

- 5. Word Integers (16 bits)

- 6. Long-Word Integers (32 bits)

- 7. Quad-Word Integers (64 bits)

In addition, the MC68020/EC020 instruction set supports operations on other data types such as memory addresses. The coprocessor mechanism allows direct support of floating-point operations with the MC68881 and MC68882 floating-point coprocessors as well as specialized user-defined data types and functions.

The 18 addressing modes listed in Table 1-1 include nine basic types:

- 1. Register Direct

- 2. Register Indirect

- 3. Register Indirect with Index

- 4. Memory Indirect

- 5. PC Indirect with Displacement

- PC Indirect with Index

- 7. PC Memory Indirect

- 8. Absolute

- 9. Immediate

The register indirect addressing modes have postincrement, predecrement, displacement, and index capabilities. The PC modes have index and offset capabilities. Both modes are extended to provide indirect reference through memory. In addition to these addressing modes, many instructions implicitly specify the use of the CCR, stack pointer, and/or PC.

Table 1-1. Addressing Modes

| Addressing Modes                                                                                         | Syntax                                           |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Register Direct Data Address                                                                             | Dn<br>An                                         |

| Register Indirect Address Address with Postincrement Address with Predecrement Address with Displacement | (An)<br>(An)+<br>-(An)<br>(d <sub>16</sub> , An) |

| Address Register Indirect with Index<br>8-Bit Displacement<br>Base Displacement                          | (d <sub>8</sub> , An, Xn)<br>(bd, An, Xn)        |

| Memory Indirect Postindexed Preindexed                                                                   | ([bd, An], Xn, od)<br>([bd, An, Xn], od)         |

| PC Indirect with Displacement                                                                            | (d <sub>16</sub> , PC)                           |

| PC Indirect with Index<br>8-Bit Displacement<br>Base Displacement                                        | (d <sub>8</sub> , PC, Xn)<br>(bd, PC, Xn)        |

| PC Indirect Postindexed Preindexed                                                                       | ([bd, PC], Xn, od)<br>([bd, PC, Xn], od)         |

| Absolute Data Addressing<br>Short<br>Long                                                                | (xxx).W<br>(xxx).L                               |

| Immediate                                                                                                | # <data></data>                                  |

#### NOTE:

Dn = Data Register, D7-D0

An = Address Register, A7-A0

d<sub>8</sub>, d<sub>16</sub> = A twos complement or sign-extended displacement added as part of the effective address calculation; size is 8 (d<sub>8</sub>) or 16 (d<sub>16</sub>) bits; when omitted, assemblers use a value of zero.

Xn = Address or data register used as an index register; form is Xn.SIZE\*SCALE, where SIZE is .W or .L (indicates index register size) and SCALE is 1, 2, 4, or 8 (index register is multiplied by SCALE); use of SIZE and/or SCALE is optional.

bd = A twos-complement base displacement; when present, size can be 16 or 32 bits.

od = Outer displacement added as part of effective address calculation after any memory indirection; use is optional with a size of 16 or 32 bits.

PC = Program Counter

<data> = Immediate value of 8, 16, or 32 bits

() = Effective Address

[] = Use as indirect access to long-word address.