Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# M68000

# 8-/16-/32-Bit Microprocessors User's Manual

**Ninth Edition**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

# **TABLE OF CONTENTS**

| Paragraph<br>Number | Title                           | Page<br>Number |

|---------------------|---------------------------------|----------------|

|                     | Section 1                       |                |

|                     | Overview                        |                |

| 1.1                 | MC68000                         | 1-1            |

| 1.2                 | MC68008                         | 1-2            |

| 1.3                 | MC68010                         | 1-2            |

| 1.4                 | MC68HC000                       |                |

| 1.5                 | MC68HC001                       | 1-3            |

| 1.6                 | MC68EC000                       | 1-3            |

|                     | Section 2                       |                |

|                     | Introduction                    |                |

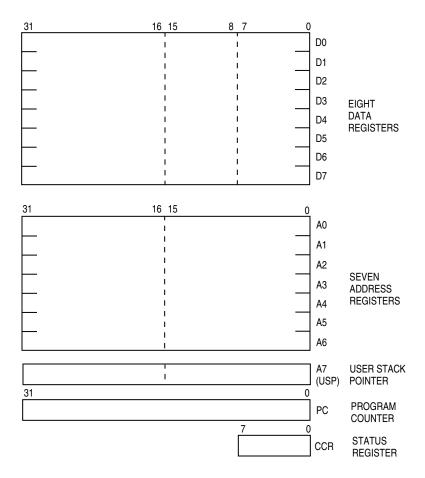

| 2.1                 | Programmer's Model              | 2-1            |

| 2.1.1               | User's Programmer's Model       |                |

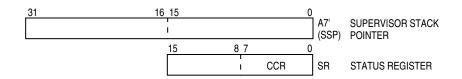

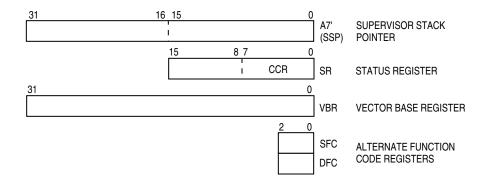

| 2.1.2               | Supervisor Programmer's Model   |                |

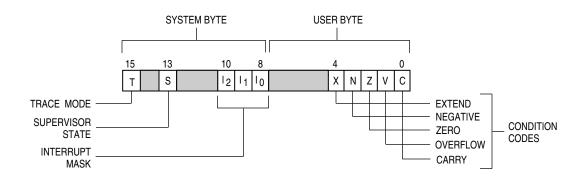

| 2.1.3               | Status Register                 | 2-3            |

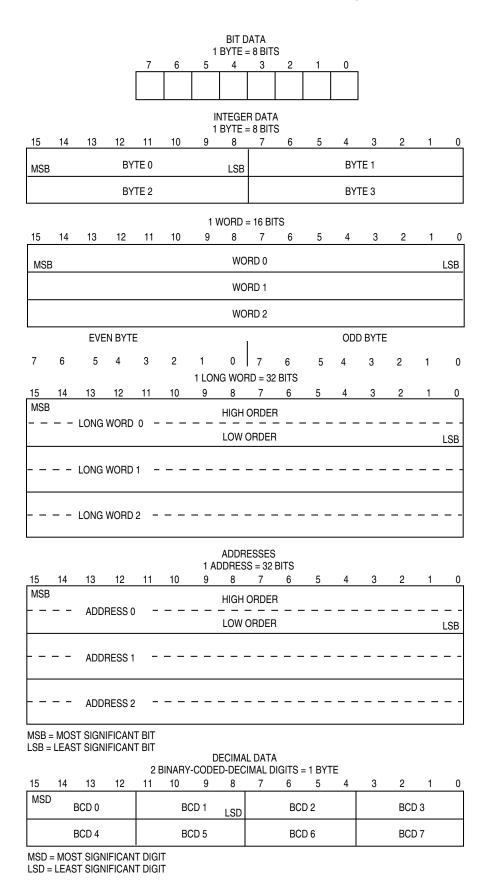

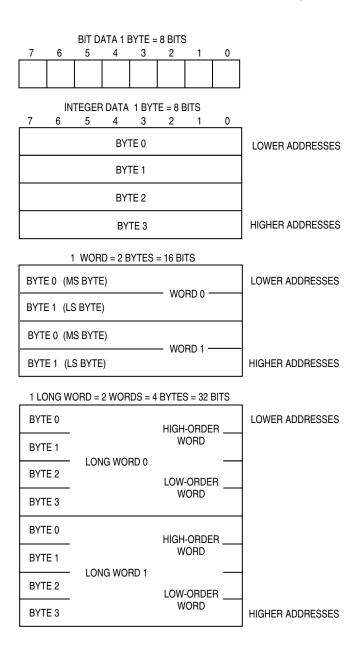

| 2.2                 | Data Types and Addressing Modes |                |

| 2.3                 | Data Organization In Registers  | 2-5            |

| 2.3.1               | Data Registers                  | 2-5            |

| 2.3.2               | Address Registers               | 2-6            |

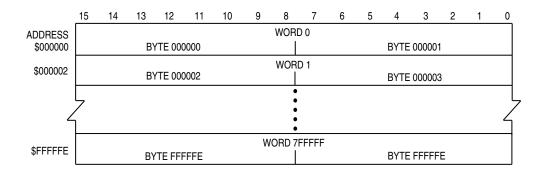

| 2.4                 | Data Organization In Memory     |                |

| 2.5                 | Instruction Set Summary         | 2-8            |

|                     | Section 3                       |                |

|                     | Signal Description              |                |

| 3.1                 | Address Bus                     | 3-3            |

| 3.2                 | Data Bus                        |                |

| 3.3                 | Asynchronous Bus Control        |                |

| 3.4                 | Bus Arbitration Control         | 3-5            |

| 3.5                 | Interrupt Control               | 3-6            |

| 3.6                 | System Control                  | 3-7            |

| 3.7                 | M6800 Peripheral Control        | 3-8            |

| 3.8                 | Processor Function Codes        | 3-8            |

| 3.9                 | Clock                           |                |

| 3.10                | Power Supply                    | 3-9            |

| 3.11                | Signal Summary                  | 3-10           |

| Section 4   S-Bit Bus Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Paragraph<br>Number | Title                                                  | Page<br>Numbe |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------|---------------|

| 4.1       Data Transfer Operations       4-1         4.1.1       Read Operations       4-1         4.1.2       Write Cycle       4-3         4.1.3       Read-Modify-Write Cycle       4-5         4.2       Other Bus Operations       4-8         Section 5         16-Bit Bus Operations         5-1         5.1       Data Transfer Operations       5-1         5.1.1       Read Operations       5-1         5.1.2       Write Cycle       5-4         5.1.3       Read-Modify-Write Cycle       5-7         5.1.4       CPU Space Cycle       5-7         5.1.4       CPU Space Cycle       5-7         5.1.4       CPU Space Cycle       5-7         5.1.2       Requesting The Bus       5-1         5.1       Requesting The Bus       5-1         5.2.1       Requesting The Bus Grant       5-1         5.2.2       Receiving The Bus Grant       5-1         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.3       Bus Error and Halt Operation       5-24         5.4.1       Bus Error operation       5-26         5.4.2       Retryin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     |                                                        |               |

| 4.1.1       Read Operations       4-1         4.1.2       Write Cycle       4-3         4.1.3       Read-Modify-Write Cycle       4-5         4.2       Other Bus Operations       4-8         Section 5         16-Bit Bus Operations         5-1         5.1.1       Read Operations       5-1         5.1.2       Write Cycle       5-4         5.1.3       Read-Modify-Write Cycle       5-7         5.1.4       CPU Space Cycle       5-9         5.2       Bus Arbitration       5-11         5.2.1       Requesting The Bus       5-14         5.2.2       Receiving The Bus Grant       5-15         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.3       Bus Arbitration Control       5-15         5.3       Bus Arbitration Control       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Operation       5-24         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Op                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     | 8-Bit Bus Operations                                   |               |

| 4.1.1       Read Operations       4-1         4.1.2       Write Cycle       4-3         4.1.3       Read-Modify-Write Cycle       4-5         4.2       Other Bus Operations       4-8         Section 5         16-Bit Bus Operations         5-1         5.1.1       Read Operations       5-1         5.1.2       Write Cycle       5-4         5.1.3       Read-Modify-Write Cycle       5-7         5.1.4       CPU Space Cycle       5-9         5.2       Bus Arbitration       5-11         5.2.1       Requesting The Bus       5-14         5.2.2       Receiving The Bus Grant       5-15         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.3       Bus Arbitration Control       5-15         5.3       Bus Arbitration Control       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Operation       5-24         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Op                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.1                 | Data Transfer Operations                               | 4-1           |

| 4.1.2       Write Cycle       4-3         4.1.3       Read-Modify-Write Cycle       4-5         4.2       Other Bus Operations       4-8         Section 5         16-Bit Bus Operations         5.1       Data Transfer Operations       5-1         5.1.1       Read Operations       5-1         5.1.2       Write Cycle       5-4         5.1.3       Read-Modify-Write Cycle       5-7         5.1.4       CPU Space Cycle       5-9         5.2       Bus Arbitration       5-1         5.2.1       Requesting The Bus       5-1         5.2.2       Receiving The Bus Grant       5-15         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.3       Bus Arbitration Control       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Operation       5-23         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30 </td <td></td> <td>•</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     | •                                                      |               |

| 4.1.3       Read-Modify-Write Cycle       4-5         4.2       Other Bus Operations       4-8         Section 5         16-Bit Bus Operations         5.1       Data Transfer Operations       5-1         5.1.1       Read Operations       5-1         5.1.2       Write Cycle       5-4         5.1.3       Read-Modify-Write Cycle       5-7         5.1.4       CPU Space Cycle       5-9         5.2       Bus Arbitration       5-11         5.2.1       Requesting The Bus       5-14         5.2.2       Receiving The Bus Grant       5-15         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Operation       5-23         5.4.1       Bus Error Operation       5-24         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-27         5.4       Double Bus Fault<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     | •                                                      |               |

| Section 5   Tight Bus Operations   Section 5   Tight Bus Operations   Section 5   Section 6   Sectio |                     | •                                                      |               |

| 16-Bit Bus Operations         5-1           5.1         Data Transfer Operations         .5-1           5.1.1         Read Operations         .5-1           5.1.2         Write Cycle         .5-4           5.1.3         Read-Modify-Write Cycle         .5-9           5.1.4         CPU Space Cycle         .5-9           5.2         Bus Arbitration         .5-11           5.2.1         Requesting The Bus         .5-14           5.2.2         Receiving The Bus Grant         .5-15           5.2.3         Acknowledgment of Mastership (3-Wire Arbitration Only)         .5-15           5.3         Bus Arbitration Control         .5-15           5.4         Bus Error and Halt Operation         .5-23           5.4.1         Bus Error Operation         .5-23           5.4.1         Bus Error Operation         .5-24           5.4.2         Retrying The Bus Cycle         .5-26           5.4.3         Halt Operation         .5-27           5.4.4         Double Bus Fault         .5-28           5.5         Reset Operation         .5-29           5.6         The Relationship of DTACK, BERR, and HALT         .5-30           5.7         Asynchronous Operation <td< td=""><td>_</td><td>· · · · · · · · · · · · · · · · · · ·</td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                   | · · · · · · · · · · · · · · · · · · ·                  |               |

| 5.1       Data Transfer Operations       5-1         5.1.1       Read Operations       5-1         5.1.2       Write Cycle       5-4         5.1.3       Read-Modify-Write Cycle       5-7         5.1.4       CPU Space Cycle       5-9         5.2       Bus Arbitration       5-11         5.2.1       Requesting The Bus       5-14         5.2.2       Receiving The Bus Grant       5-15         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.3       Bus Arbitration Control       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error And Halt Operation       5-23         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-35         Section 6         Exception Processing         6.1       Privilege Mode <t< th=""><th></th><th></th><th></th></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |                                                        |               |

| 5.1.1       Read Operations       5-1         5.1.2       Write Cycle       5-4         5.1.3       Read-Modify-Write Cycle       5-7         5.1.4       CPU Space Cycle       5-9         5.2       Bus Arbitration       5-11         5.2.1       Requesting The Bus       5-14         5.2.2       Receiving The Bus Grant       5-15         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.3       Bus Arbitration Control       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Aperation       5-23         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-24         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6         Exception Processing         6.1       Privilege Mode       6-2         6.1.3       Privilege Mode Changes       6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | 16-Bit Bus Operations                                  |               |

| 5.1.2       Write Cycle       5-4         5.1.3       Read-Modify-Write Cycle       5-7         5.1.4       CPU Space Cycle       5-9         5.2       Bus Arbitration       5-11         5.2.1       Requesting The Bus       5-14         5.2.2       Receiving The Bus Grant       5-15         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.3       Bus Arbitration Control       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Operation       5-24         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-28         5.5       Reset Operation       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6         Exception Processing         6.1       Privilege Modes       6-2         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.1                 | Data Transfer Operations                               | 5-1           |

| 5.1.3       Read-Modify-Write Cycle       5-7         5.1.4       CPU Space Cycle       5-9         5.2       Bus Arbitration       5-11         5.2.1       Requesting The Bus       5-14         5.2.2       Receiving The Bus Grant       5-15         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.3       Bus Arbitration Control       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Operation       5-23         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-35         Section 6         Exception Processing         6.1       Privilege Modes       6-1         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.1.1               | Read Operations                                        | 5-1           |

| 5.1.4       CPU Space Cycle       5-9         5.2       Bus Arbitration       5-11         5.2.1       Requesting The Bus       5-14         5.2.2       Receiving The Bus Grant       5-15         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.3       Bus Arbitration Control       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Operation       5-24         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6         Exception Processing         6.1       Privilege Mode       6-2         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing <td< td=""><td>5.1.2</td><td>Write Cycle</td><td> 5-4</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.1.2               | Write Cycle                                            | 5-4           |

| 5.2       Bus Arbitration       5-11         5.2.1       Requesting The Bus       5-14         5.2.2       Receiving The Bus Grant       5-15         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.3       Bus Arbitration Control       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Operation       5-24         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6         Exception Processing         6.1       Privilege Modes       6-1         6.1.1       Supervisor Mode       6-2         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing <t< td=""><td>5.1.3</td><td>Read-Modify-Write Cycle</td><td>5-7</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.1.3               | Read-Modify-Write Cycle                                | 5-7           |

| 5.2.1       Requesting The Bus       5-14         5.2.2       Receiving The Bus Grant       5-15         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.3       Bus Arbitration Control       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Operation       5-24         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6         Exception Processing         6.1       Privilege Modes       6-1         6.1.1       Supervisor Mode       6-2         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing       6-4         6.2.1       Exception Vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.1.4               | CPU Space Cycle                                        | 5-9           |

| 5.2.2       Receiving The Bus Grant       5-15         5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.3       Bus Arbitration Control       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Operation       5-24         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6         Exception Processing         6.1       Privilege Modes       6-1         6.1.1       Supervisor Mode       6-2         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing       6-4         6.2.1       Exception Vectors       6-4         6.2.2       Kinds Of Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.2                 | Bus Arbitration                                        | 5-11          |

| 5.2.3       Acknowledgment of Mastership (3-Wire Arbitration Only)       5-15         5.3       Bus Arbitration Control       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Operation       5-24         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.2.1               | Requesting The Bus                                     | 5-14          |

| 5.3       Bus Arbitration Control       5-15         5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Operation       5-24         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.2.2               | Receiving The Bus Grant                                | 5-15          |

| 5.4       Bus Error and Halt Operation       5-23         5.4.1       Bus Error Operation       5-24         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6         Exception Processing         6.1       Privilege Modes       6-1         6.1.1       Supervisor Mode       6-2         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing       6-4         6.2.1       Exception Vectors       6-4         6.2.2       Kinds Of Exceptions       6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.2.3               | Acknowledgment of Mastership (3-Wire Arbitration Only) | 5-15          |

| 5.4.1       Bus Error Operation       5-24         5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6         Exception Processing         6.1       Privilege Modes       6-1         6.1.1       Supervisor Mode       6-2         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing       6-4         6.2.1       Exception Vectors       6-4         6.2.2       Kinds Of Exceptions       6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.3                 | Bus Arbitration Control                                | 5-15          |

| 5.4.2       Retrying The Bus Cycle       5-26         5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6         Exception Processing         6.1       Privilege Modes       6-1         6.1.1       Supervisor Mode       6-2         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing       6-4         6.2.1       Exception Vectors       6-4         6.2.2       Kinds Of Exceptions       6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.4                 | Bus Error and Halt Operation                           | 5-23          |

| 5.4.3       Halt Operation       5-27         5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6         Exception Processing         6.1       Privilege Modes       6-1         6.1.1       Supervisor Mode       6-2         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing       6-4         6.2.1       Exception Vectors       6-4         6.2.2       Kinds Of Exceptions       6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.4.1               | ·                                                      |               |

| 5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6         Exception Processing         6.1       Privilege Modes       6-1         6.1.1       Supervisor Mode       6-2         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing       6-4         6.2.1       Exception Vectors       6-4         6.2.2       Kinds Of Exceptions       6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.4.2               | Retrying The Bus Cycle                                 | 5-26          |

| 5.4.4       Double Bus Fault       5-28         5.5       Reset Operation       5-29         5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.4.3               | Halt Operation                                         | 5-27          |

| 5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.4.4               |                                                        |               |

| 5.6       The Relationship of DTACK, BERR, and HALT       5-30         5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.5                 | Reset Operation                                        | 5-29          |

| 5.7       Asynchronous Operation       5-32         5.8       Synchronous Operation       5-35         Section 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.6                 |                                                        |               |

| Synchronous Operation         5-35           Section 6           Exception Processing           6.1         Privilege Modes         6-1           6.1.1         Supervisor Mode         6-2           6.1.2         User Mode         6-2           6.1.3         Privilege Mode Changes         6-2           6.1.4         Reference Classification         6-3           6.2         Exception Processing         6-4           6.2.1         Exception Vectors         6-4           6.2.2         Kinds Of Exceptions         6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.7                 | ·                                                      |               |

| Exception Processing           6.1         Privilege Modes         6-1           6.1.1         Supervisor Mode         6-2           6.1.2         User Mode         6-2           6.1.3         Privilege Mode Changes         6-2           6.1.4         Reference Classification         6-3           6.2         Exception Processing         6-4           6.2.1         Exception Vectors         6-4           6.2.2         Kinds Of Exceptions         6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.8                 |                                                        |               |

| 6.1       Privilege Modes       6-1         6.1.1       Supervisor Mode       6-2         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing       6-4         6.2.1       Exception Vectors       6-4         6.2.2       Kinds Of Exceptions       6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     | Section 6                                              |               |

| 6.1.1       Supervisor Mode       6-2         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing       6-4         6.2.1       Exception Vectors       6-4         6.2.2       Kinds Of Exceptions       6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     | Exception Processing                                   |               |

| 6.1.1       Supervisor Mode       6-2         6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing       6-4         6.2.1       Exception Vectors       6-4         6.2.2       Kinds Of Exceptions       6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6.1                 | Privilege Modes                                        | 6-1           |

| 6.1.2       User Mode       6-2         6.1.3       Privilege Mode Changes       6-2         6.1.4       Reference Classification       6-3         6.2       Exception Processing       6-4         6.2.1       Exception Vectors       6-4         6.2.2       Kinds Of Exceptions       6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6.1.1               | · · · · · · · · · · · · · · · · · · ·                  |               |

| 6.1.3Privilege Mode Changes6-26.1.4Reference Classification6-36.2Exception Processing6-46.2.1Exception Vectors6-46.2.2Kinds Of Exceptions6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6.1.2               | ·                                                      |               |