Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **Freescale Semiconductor**

Data Sheet: Technical Data

Document Number: IMX25CEC Rev. 10, 07/2013

## MCIMX25

#### **Package Information**

Plastic package Case 5284 17 x 17 mm, 0.8 mm Pitch Case 2107 12 x 12 mm, 0.5 mm Pitch

#### **Ordering Information**

See Table 1 on page 3 for ordering information.

#### 1.2. Block Diagram ......5 2.1. Special Signal Considerations . . . . . . . . . . . . . . . . . 9 3. Electrical Characteristics ......11 3.2. Supply Power-Up/Power-Down Requirements and 3.4. Thermal Characteristics ................................20 3.7. Module Timing and Electrical Parameters . . . . . 41 4. Package Information and Contact Assignment . . . . . . 124 4.1. 400 MAPBGA—Case 17x17 mm, 0.8 mm Pitch . 124 4.2. Ground, Power, Sense, and Reference Contact Assignments Case 17x17 mm, 0.8 mm Pitch . . . 125 Signal Contact Assignments—17 x 17 mm, 0.8 mm 4.4. i.MX25 17x17 Package Ball Map ......135 4.5. 347 MAPBGA—Case 12 x 12 mm, 0.5 mm Pitch 138 4.6. Ground, Power, Sense, and Reference Contact Assignments Case 12x12 mm, 0.5 mm Pitch . . . 139 4.7. Signal Contact Assignments—12 x 12 mm, 0.5 mm Pitch ......140

# ARM BOWERED

## i.MX25 Applications Processor for Consumer and Industrial Products

## 1 Introduction

Silicon Version 1.2

The i.MX25 multimedia applications processor has the right mix of high performance, low power, and integration to support the growing needs of the industrial and general embedded markets.

At the core of the i.MX25 is Freescale's fast, proven, power-efficient implementation of the ARM® 926EJ-S<sup>TM</sup> core, with speeds of up to 400 MHz. The i.MX25 includes support for up to 133 MHz DDR2 memory, integrated 10/100 Ethernet MAC, and two on-chip USB PHYs. The device is suitable for a wide range of applications, including the following:

- Graphical remote controls

- Human Machine Interface (HMI)

- Residential and commercial control panels

- Residential gateway (smart metering)

- Handheld scanners and printers

- Electronic point-of-sale terminals

- Patient-monitoring devices

Features of the i.MX25 processor include the following:

- Advanced power management—The heart of the device is a level of power management

throughout the IC that enables the multimedia features and peripherals to achieve minimum system

power consumption in active and various low-power modes. Power management techniques allow

the designer to deliver a feature-rich product that requires levels of power far lower than typical

industry expectations.

- Multimedia powerhouse—The multimedia performance of the i.MX25 processor is boosted by a 16 KB L1 instruction and data cache system and further enhanced by an LCD controller (with alpha blending), a CMOS image sensor interface, an A/D controller (integrated touchscreen controller), and a programmable Smart DMA (SDMA) controller.

- 128 Kbytes on-chip SRAM—The additional 128 Kbyte on-chip SRAM makes the device ideal for eliminating external RAM in applications with small footprint RTOS. The on-chip SRAM allows the designer to enable an ultra low power LCD refresh.

- Interface flexibility—The device interface supports connection to all common types of external memories: MobileDDR, DDR, DDR2, NOR Flash, PSRAM, SDRAM and SRAM, NAND Flash, and managed NAND.

- Increased security—Because the need for advanced security for tethered and untethered devices continues to increase, the i.MX25 processor delivers hardware-enabled security features that enable secure e-commerce, Digital Rights Management (DRM), information encryption, robust tamper detection, secure boot, and secure software downloads.

- On-chip PHY—The device includes an HS USB OTG PHY and FS USB HOST PHY.

- Fast Ethernet—For rapid external communication, a Fast Ethernet Controller (FEC) is included.

- i.MX25 only supports Little Endian mode.

## 1.1 Ordering Information

Table 1 provides ordering information for the i.MX25.

**Table 1. Ordering Information**

| Description | Part Number     | Silicon<br>Version | Projected<br>Temperature<br>Range (°C) | Temperature Package                     |           |

|-------------|-----------------|--------------------|----------------------------------------|-----------------------------------------|-----------|

| i.MX253     | MCIMX253DVM4    | 1.1                | -20 to +70                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX257     | MCIMX257DVM4    | 1.1                | -20 to +70                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX253     | MCIMX253CVM4    | 1.1                | -40 to +85                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX257     | MCIMX257CVM4    | 1.1                | -40 to +85                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX258     | MCIMX258CVM4    | 1.1                | -40 to +85                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX253     | MCIMX253DJM4    | 1.1                | -20 to +70                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX257     | MCIMX257DJM4    | 1.1                | -20 to +70                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX253     | MCIMX253CJM4    | 1.1                | -40 to +85                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX257     | MCIMX257CJM4    | 1.1                | -40 to +85                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX258     | MCIMX258CJM4    | 1.1                | -40 to +85                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX253     | MCIMX253DJM4A   | 1.2                | -20 to +70                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX257     | MCIMX257DJM4A   | 1.2                | -20 to +70                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX257     | MCIMX257DJM4AR2 | 1.2                | -20 to +70                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX253     | MCIMX253CJM4A   | 1.2                | -40 to +85                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 | Table 103 |

| i.MX257     | MCIMX257CJM4A   | 1.2                | -40 to +85                             | 17 x 17 mm, 0.8 mm pitch,<br>MAPBGA-400 |           |

| i.MX258     | MCIMX258CJM4A   | 1.2                | -40 to +85                             | 17 x 17 mm, 0.8 mm pitch, MAPBGA-400    |           |

| i.MX257     | MCIMX257CJN4A   | 1.2                | -40 to +85                             | 12 x 12mm, 0.5mm pitch,<br>MAPBGA-347   | Table 107 |

Table 2 shows the functional differences between the different parts in the i.MX25 family.

#### Table 2. i.MX25 Parts Functional Differences

| Features                   | MCIMX253    | MCIMX257    | MCIMX258    |

|----------------------------|-------------|-------------|-------------|

| Core                       | ARM 926EJ-S | ARM 926EJ-S | ARM 926EJ-S |

| CPU Speed                  | 400 MHz     | 400 MHz     | 400 MHz     |

| L1 I/D Cache               | 16K I/D     | 16K I/D     | 16K I/D     |

| On-chip SRAM               | 128 KB      | 128 KB      | 128 KB      |

| PATA/CE-ATA                | Yes         | Yes         | Yes         |

| LCD Controller             | Yes         | Yes         | Yes         |

| Touchscreen                | _           | Yes         | Yes         |

| CSI                        | _           | Yes         | Yes         |

| FlexCAN (2)                | _           | Yes         | Yes         |

| ESAI                       | _           | Yes         | Yes         |

| SIM (2)                    | _           | Yes         | Yes         |

| Security                   | _           | _           | Yes         |

| 10/100 Ethernet            | Yes         | Yes         | Yes         |

| HS USB 2.0 OTG + PHY       | Yes         | Yes         | Yes         |

| HS USB 2.0 Host + PHY      | Yes         | Yes         | Yes         |

| 12-bit ADC                 | Yes         | Yes         | Yes         |

| SD/SDIO/MMC (2)            | Yes         | Yes         | Yes         |

| External Memory Controller | Yes         | Yes         | Yes         |

| I <sup>2</sup> C (3)       | Yes         | Yes         | Yes         |

| SSI/I2S (2)                | Yes         | Yes         | Yes         |

| CSPI (2)                   | Yes         | Yes         | Yes         |

| UART (5)                   | Yes         | Yes         | Yes         |

## 1.2 Block Diagram

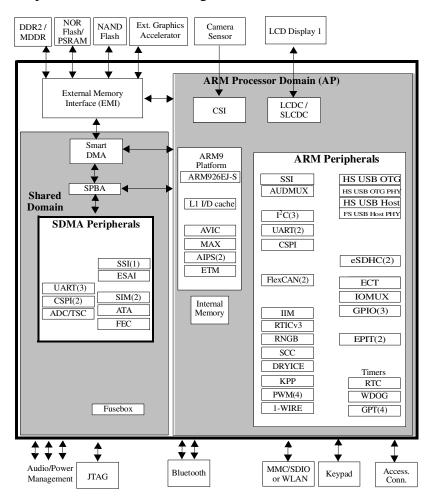

Figure 1 shows the simplified interface block diagram.

Figure 1. i.MX25 Simplified Interface Block Diagram

## 2 Features

Table 3 describes the digital and analog modules of the device.

Table 3. i.MX25 Digital and Analog Modules

| Block<br>Mnemonic | Block Name                                        | Subsystem                 | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|---------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-WIRE            | 1-Wire<br>Interface                               | Connectivity peripherals  | 1-Wire support provided for interfacing with an on-board EEPROM, and smart battery interfaces, for example: Dallas DS2502.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ARM9 or<br>ARM926 | ARM926<br>platform and<br>memory                  | ARM                       | The ARM926 Platform consists of the ARM 926EJ-S core, the ETM real-time debug modules, a 5x5 Multi-Layer AHB crossbar switch, and a "primary AHB" complex. It contains the 16 Kbyte L1 instruction cache, 16 Kbyte L1 data cache, 32 Kbyte ROM and 128 Kbyte RAM.                                                                                                                                                                                                                                                                                                  |

| ATA               | ATA module                                        | Connectivity peripherals  | The ATA module is an AT attachment host interface. Its main use is to interface with IDE hard disc drives and ATAPI optical disc drives. It interfaces with the ATA device over a number of ATA signals.                                                                                                                                                                                                                                                                                                                                                           |

| AUDMUX            | Digital audio<br>mux                              | Multimedia<br>peripherals | The AUDMUX is a programmable interconnect for voice, audio, and synchronous data routing between host serial interfaces (SSIs) and peripheral serial interfaces (audio codecs). The AUDMUX has two sets of interfaces: internal ports to on-chip peripherals, and external ports to off-chip audio devices. Data is routed by configuring the appropriate internal and external ports.                                                                                                                                                                             |

| ССМ               | Clock control<br>module                           | Clocks                    | This block generates all clocks for the iMX25 system. The CCM also manages the ARM926 Platform's low-power modes (wait, stop, and doze) by disabling peripheral clocks appropriately for power conservation.                                                                                                                                                                                                                                                                                                                                                       |

| CSPI(3)           | Configurable<br>serial<br>peripheral<br>interface | Connectivity peripherals  | This module is a serial interface equipped with data FIFOs. Each master/slave-configurable SPI module is capable of interfacing to both serial port interface master and slave devices. The CSPI ready (SPI_RDY) and Slave Select (SS) control signals enable fast data communication with fewer software interrupts.                                                                                                                                                                                                                                              |

| DRYICE            | Drylce module                                     | Security                  | Drylce provides volatile key storage for Point-of-Sale (POS) terminals, and a trusted time source for Digital Rights Management (DRM) schemes. Several tamper-detect circuits are also provided to support key erasure and time invalidation in the event of tampering. Alarms and/or interrupts can also assert if tampering is detected. Drylce also includes a Real Time clock (RTC) that can be used in secure and non-secure applications.                                                                                                                    |

| EMI               | External<br>memory<br>interface                   | Connectivity peripherals  | <ul> <li>The External Memory Interface (EMI) module provides access to external memory for the ARM and other masters. It is composed of four main submodules:</li> <li>M3IF provides arbitration between multiple masters requesting access to the external memory.</li> <li>Enhanced SDRAM/LPDDR memory controller (ESDCTL) interfaces to DDR2 and SDR interfaces.</li> <li>NAND Flash controller (NFC) provides an interface to NAND Flash memories.</li> <li>Wireless External Interface Memory controller (WEIM) interfaces to NOR Flash and PSRAM.</li> </ul> |

Table 3. i.MX25 Digital and Analog Modules (continued)

| Block<br>Mnemonic | Block Name                                                           | Subsystem                  | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|----------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EPIT(2)           | Enhanced periodic interrupt timer                                    | Timer<br>peripherals       | Each Enhanced Periodic Interrupt Timer (EPIT) is a 32-bit set-and-forget timer that starts counting after the EPIT is enabled by software. It is capable of providing precise interrupts at regular intervals with minimal processor intervention. It has a 12-bit prescaler to adjust the input clock frequency to the required time setting for the interrupts, and the counter value can be programmed on the fly.                                                                                                                                                                                                                                                                                                                                                                    |

| ESAI              | Enhanced<br>serial audio<br>interface                                | Connectivity peripherals   | ESAI provides a full-duplex serial port for serial communication with a variety of serial devices, including industry-standard codecs, SPDIF transceivers, and other DSPs. The ESAI consists of independent transmitter and receiver sections, each section with its own clock generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| eSDHC(2)          | Enhanced<br>multimedia<br>card/<br>secure digital<br>host controller | Connectivity peripherals   | The features of the eSDHC module, when serving as host, include the following:  Conforms to the SD host controller standard specification version 2.0  Compatible with the JEDEC MMC system specification version 4.2  Compatible with the SD memory card specification version 2.0  Compatible with the SDIO specification version 1.2  Designed to work with SD memory, miniSD memory, SDIO, miniSDIO, SD combo, MMC and MMC RS cards  Configurable to work in one of the following modes:  —SD/SDIO 1-bit, 4-bit  —MMC 1-bit, 4-bit, 8-bit  Full-/high-speed mode  Host clock frequency variable between 32 kHz and 52 MHz  Up to 200-Mbps data transfer for SD/SDIO cards using four parallel data lines  Up to 416-Mbps data transfer for MMC cards using eight parallel data lines |

| FEC               | Fast ethernet controller                                             | Connectivity peripherals   | The Ethernet Media Access Controller (MAC) is designed to support both 10-and 100-Mbps Ethernet networks compliant with IEEE 802.3 <sup>®</sup> standard. An external transceiver interface and transceiver function are required to complete the interface to the media                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| FlexCAN(2)        | Controller<br>area network<br>module                                 | Connectivity peripherals   | The Controller Area Network (CAN) protocol is primarily designed to be used as a vehicle serial data bus running at 1 MBps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GPIO(4)           | General<br>purpose I/O<br>modules                                    | System control peripherals | Used for general purpose input/output to external ICs. Each GPIO module supports 32 bits of I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPT(4)            | General<br>purpose<br>timers                                         | Timer<br>peripherals       | Each GPT is a 32-bit free-running or set-and-forget mode timer with programmable prescaler and compare and capture register. A timer counter value can be captured using an external event and can be configured to trigger a capture event on either the leading or trailing edges of an input pulse. When the timer is configured to operate in set-and-forget mode, it is capable of providing precise interrupts at regular intervals with minimal processor intervention. The counter has output compare logic to provide the status and interrupt at comparison. This timer can be configured to run either on an external clock or on an internal clock.                                                                                                                          |

Table 3. i.MX25 Digital and Analog Modules (continued)

| Block<br>Mnemonic   | Block Name                                           | Subsystem                  | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sup>2</sup> C(3) | I <sup>2</sup> C module                              | Connectivity peripherals   | Inter-IC Communication (I <sup>2</sup> C) is an industry-standard, bidirectional serial bus that provides a simple, efficient method of data exchange, minimizing the interconnection between devices. I <sup>2</sup> C is suitable for applications requiring occasional communications over a short distance between many devices. The interface operates up to 100 kbps with maximum bus loading and timing. The I <sup>2</sup> C system is a true multiple-master bus, including arbitration and collision detection that prevents data corruption if multiple devices attempt to control the bus simultaneously. This feature supports complex applications with multiprocessor control and can be used for rapid testing and alignment of end products through external connections to an assembly-line computer. |

| IIM                 | IC<br>Identification<br>Module                       | Security                   | The IIM provides the primary user-visible mechanism for interfacing with on-chip fuse elements. Among the uses for the fuses are unique chip identifiers, mask revision numbers, cryptographic keys, and various control signals requiring a fixed value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IOMUX               | I/O multiplexer                                      | Pins                       | Each I/O multiplexer provides a flexible, scalable multiplexing solution:     Up to eight output sources multiplexed per pin     Up to four destinations for each input pin     Unselected input paths are held at constant level for reduced power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| KPP                 | Keypad port                                          | Connectivity peripherals   | KPP can be used for either keypad matrix scanning or general purpose I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LCDC                | LCD<br>Controller                                    | Multimedia<br>peripherals  | LCDC provides display data for external gray-scale or color LCD panels. LCDC is capable of supporting black-and-white, gray-scale, passive-matrix color (passive color or CSTN), and active-matrix color (active color or TFT) LCD panels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MAX                 | ARM platform<br>multilayer<br>AHB crossbar<br>switch | ARM platform               | MAX concurrently supports up to five simultaneous connections between master ports and slave ports. MAX allows for concurrent transactions to occur from any master port to any slave port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PWM(4)              | Pulse width modulation                               | Connectivity peripherals   | The Pulse-Width Modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images. It can also generate tones. The PWM uses 16-bit resolution and a 4x16 data FIFO to generate sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SDMA                | Smart DMA engine                                     | System control             | The SDMA provides DMA capabilities inside the processor. It is a shared module that implements 32 DMA channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SIM(2)              | Subscriber identity module interface                 | Connectivity peripherals   | The SIM is an asynchronous interface designed to facilitate communication with SIM cards or pre-paid phone cards. This module was designed based on the ISO7816 standard; however, the module does require an external companion controller to allow communication to certain smart cards or to pass certain certifications, such as EMV.  The SIM supports only 11 and 12ETU cards and can communicate at the default rate, which is obtained at Fi/Di=372/1. An external companion controller is required to support cards aligned on 10.8 or 11.8ETU and to support other rates, such as those obtained at Fi/Di=372/2 and Fi/Di=372/4.                                                                                                                                                                              |

| SJC                 | Secure JTAG interface                                | System control peripherals | The System JTAG Controller (SJC) provides debug and test control with maximum security.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 3. i.MX25 Digital and Analog Modules (continued)

| Block<br>Mnemonic | Block Name                                       | Subsystem                 | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|--------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLCD              | Smart LCD controller                             | Multimedia<br>peripherals | The SLCDC module transfers data from the display memory buffer to the external display device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SPBA              | Shared peripheral bus arbiter                    | System control            | The SPBA controls access to the shared peripherals. It supports shared peripheral ownership and access rights to an owned peripheral.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SSI(2)            | I2S/SSI/AC97<br>interface                        | Connectivity peripherals  | The SSI is a full-duplex serial port that allows the processor to communicate with a variety of serial protocols, including the Freescale Semiconductor SPI standard and the inter-IC sound bus standard (I2S). The SSIs interface to the AUDMUX for flexible audio routing.                                                                                                                                                                                                                                                                                                                              |

| TSC (and ADC)     | Touchscreen<br>controller (and<br>A/D converter) | Multimedia<br>peripherals | The touchscreen controller and associated Analog-to-Digital Converter (ADC) together provide a resistive touchscreen solution. The module implements simultaneous touchscreen control and auxiliary ADC operation for temperature, voltage, and other measurement functions.                                                                                                                                                                                                                                                                                                                              |

| UART(5)           | UART<br>interface                                | Connectivity peripherals  | <ul> <li>Each of the UART modules supports the following serial data transmit/receive protocols and configurations:</li> <li>7- or 8-bit data words, one or two stop bits, programmable parity (even, odd, or none)</li> <li>Programmable baud rates up to 4 MHz. This is a higher maximum baud rate than the 1.875 MHz specified by the TIA/EIA-232-F standard and previous Freescale UART modules. 32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA-1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul> |

| USBOTG<br>USBHOST | High-speed<br>USB<br>on-the-go                   | Connectivity peripherals  | The USB module provides high-performance USB On-The-Go (OTG) and host functionality (up to 480 Mbps), compliant with the USB 2.0 specification, the OTG supplement, and the ULPI 1.0 Low Pin Count specification. The module has DMA capabilities for handling data transfer between internal buffers and system memory. An OTG HS PHY and HOST FS PHY are also integrated.                                                                                                                                                                                                                               |

## 2.1 Special Signal Considerations

Special signal considerations are listed in Table 4. The package contact assignment is found in Section 4, "Package Information and Contact Assignment." Signal descriptions are provided in the reference manual.

**Table 4. Signal Considerations**

| Signal     | Description                                                                                                                                                                                                                                      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BAT_VDD    | Drylce backup power supply input.                                                                                                                                                                                                                |

| CLK0       | Clock-out pin; renders the internal clock visible to users for debugging. The clock source is controllable through CRM registers. This pin can also be configured (through muxing) to work as a normal GPIO.                                     |

| CLK_SEL    | Used to select the ARM clock source from MPLL out or from external EXT_ARMCLK. In normal operation, CLK_SEL should be connected to GND.                                                                                                          |

| EXT_ARMCLK | Primarily for Freescale factory use. There is no internal on-chip pull-up/down on this pin, so it must be externally connected to GND or VDD. Aside from factory use, this pin can also be configured (through muxing) to work as a normal GPIO. |

i.MX25 Applications Processor for Consumer and Industrial Products, Rev. 10

#### **Table 4. Signal Considerations (continued)**

| Signal                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MESH_C, MESH_D              | Wire-mesh tamper detect pins that can be routed at the PCB board to detect attempted tampering of a protected wire. When security measures are implemented, MESH_C should be pulled-up or connected to NVCC_DRYICE and triggers a tamper event when floating or when connected to MESH_D. MESH_D should be pulled-down or connected to GND and triggers an event when floating or connected to MESH_C. These pins can be left unconnected if the DryIce security features are not being used.                                                                             |

| NVCC_DRYICE                 | This is the Drylce power supply output. The supply source is QVDD when the i.MX25 is in run mode. When i.MX25 is in reduced power mode, the Drylce supply source is the BATT_VDD supply. This pin can be used to power external Drylce components (external tamper detect, wire-mesh tamper detect). In order to guarantee the power-loss protection feature which guarantees that RTC and/or secure keys be maintained after power-off an external capacitor no less than 4 $\mu F$ must be connected to this supply output pin. A 4.7 $\mu F$ capacitor is recommended. |

| OSC_BYP                     | The 32 kHz oscillator bypass-control pin. If this signal is pulled down, then OSC32K_EXTAL and OSC32K_XTAL analog pins should be tied to the external 32.768 kHz crystal circuit. If on the other hand the signal is pulled up, then the external 32 kHz oscillator output clock must be connected to OSC32K_EXTAL analog pin, and OSC32K_XTAL can be no connect (NC).                                                                                                                                                                                                    |

| OSC32K_EXTAL<br>OSC32K_XTAL | These analog pins are connected to an external 32 kHz CLK circuit depending on the state of OSC_BYP pin (see the description of OSC_BYP under the preceding bullet). The 32 kHz reference CLK is required for normal operation.                                                                                                                                                                                                                                                                                                                                           |

| POWER_FAIL                  | An interrupt from PMIC, which should be connected to a low-battery detection circuit. This signal is internally connected to an on-chip 100 k $\Omega$ pull-down device. If there is no low-battery detection, then users can tie this pin to GND through a pull-down resistor, or leave the signal as NC. This pin can also be configured to work as a normal GPIO.                                                                                                                                                                                                      |

| REF                         | External ADC reference voltage. REF may be tied to GND if the user plans to only use the internally generated 2.5 V reference supply.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SJC_MOD                     | Must be externally connected to GND for normal operation. Termination to GND through an external pull-down resistor (such as 1 k $\Omega$ ) is allowed, but the value should be much smaller than the on-chip 100 k $\Omega$ pull-up.                                                                                                                                                                                                                                                                                                                                     |

| TAMPER_A,<br>TAMPER _B      | Drylce external tamper detect pins, active high. If TAMPER_A or TAMPER_B is connected to NVCC_DRYICE, then external tampering is detected. These pins can be left unconnected if the Drylce security features are not being used.                                                                                                                                                                                                                                                                                                                                         |

| TEST_MODE                   | For Freescale factory use only. This signal is internally connected to an on-chip pull-down device. Users must either float this signal or tie it to GND.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| UPLL_BYPCLK                 | Primarily for Freescale factory use. There is no internal on-chip pull-up/down on this pin, so it must be externally connected to GND or VDD. Aside from factory use, this pin can also be configured (through muxing) to work as a normal GPIO.                                                                                                                                                                                                                                                                                                                          |

| USBPHY1_RREF                | Determines the reference current for the USB PHY1 bandgap reference. An external 10 k $\Omega$ 1% resistor to GND is required.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| USBPHY2_DM<br>USBPHY2_DP    | The output impedance of these signals is expected at 10 $\Omega$ . It is recommended to also have on-board 33 $\Omega$ series resistors (close to the pins).                                                                                                                                                                                                                                                                                                                                                                                                              |

## 3 Electrical Characteristics

This section provides the device-level and module-level electrical characteristics for the i.MX25.

## 3.1 i.MX25 Chip-Level Conditions

This section provides the chip-level electrical characteristics for the IC.

#### 3.1.1 DC Absolute Maximum Ratings

Table 5 provides the DC absolute maximum operating conditions.

#### **CAUTION**

- Stresses beyond those listed under Table 5 may cause permanent damage to the device.

- Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- Table 5 gives stress ratings only—functional operation of the device is not implied beyond the conditions indicated in Table 6.

Table 5. DC Absolute Maximum Ratings

meter Symbol Mir

| Parameter                        | Symbol               | Min. | Max.                   | Units |

|----------------------------------|----------------------|------|------------------------|-------|

| Supply voltage                   | $QV_DD$              | -0.5 | 1.52                   | V     |

| Supply voltage (level shift i/o) | $V_{DDIOmax}$        | -0.5 | 3.6                    | V     |

| ESD damage immunity:             | $V_{\sf esd}$        |      |                        | V     |

| Human body model (HBM)           |                      | _    | 2500                   |       |

| Charge device model (CDM)        |                      | _    | 400                    |       |

| Machine model (MM)               |                      | _    | 200                    |       |

| Input voltage range              | V <sub>Imax</sub>    | -0.5 | NV <sub>DD</sub> + 0.3 | V     |

| Storage temperature range        | T <sub>storage</sub> | -40  | 105                    | °C    |

## 3.1.2 DC Operating Conditions

Table 6 provides the DC recommended operating conditions.

**Table 6. DC Operating Conditions**

| Parameter                                | Symbol                 | Min. | Тур. | Max. | Units |

|------------------------------------------|------------------------|------|------|------|-------|

| Core supply voltage (at 266 MHz)         | QV <sub>DD</sub>       | 1.15 | 1.34 | 1.52 | V     |

| Core supply voltage (at 400 MHz)         | QV <sub>DD</sub>       | 1.38 | 1.45 | 1.52 | V     |

| Coin battery <sup>1</sup><br>BAT_VDD     | V <sub>DD_BAT</sub>    | 1.15 | _    | 1.55 | ٧     |

| I/O supply voltage, GPIO<br>NFC,CSI,SDIO | NV <sub>DD_GPIO1</sub> | 1.75 | _    | 3.6  | V     |

i.MX25 Applications Processor for Consumer and Industrial Products, Rev. 10

**Table 6. DC Operating Conditions (continued)**

| Parameter                                                               | Symbol                                | Min.     | Тур.                | Max.                | Units |

|-------------------------------------------------------------------------|---------------------------------------|----------|---------------------|---------------------|-------|

| I/O supply voltage, GPIO<br>CRM,LCDC,JTAG,MISC                          | NV <sub>DD_GPIO2</sub>                | 3.0      | 3.3                 | 3.6                 | _     |

| I/O supply voltage DDR (Mobile DDR mode)<br>EMI1, EMI2                  | NV <sub>DD_MDDR</sub>                 | 1.75     | _                   | 1.95                | V     |

| I/O supply voltage DDR (DDR2 mode)<br>EMI1,EMI2                         | NV <sub>DD_DDR2</sub>                 | 1.75     | _                   | 1.9                 | V     |

| I/O supply voltage DDR (SDRAM mode)<br>EMI1,EMI2                        | NV <sub>DD_SDRAM</sub>                | 1.75     | _                   | 3.6                 | V     |

| Supply of USBPHY1 (HS) USBPHY1_VDDA_BIAS, USBPHY1_UPLL_VDD,USBPHY1_VDDA | V <sub>DD_usbphy1</sub>               | 3.17     | 3.3                 | 3.43                | V     |

| Supply of USBPHY2 (FS) USBPHY2_VDD                                      | V <sub>DD_usbphy2</sub>               | 3.0      | 3.3                 | 3.6                 | V     |

| Supply of OSC24M<br>OSC24M_VDD                                          | V <sub>DD_OSC24M</sub>                | 3.0      | 3.3                 | 3.6                 | V     |

| Supply of PLL MPLL_VDD,UPLL_VDD                                         | V <sub>DD_PLL</sub>                   | 1.4      | _                   | 1.65                | V     |

| Supply of touchscreen ADC<br>NVCC_ADC                                   | V <sub>DD_tsc</sub>                   | 3.0      | 3.3                 | 3.6                 | V     |

| External reference of touchscreen ADC<br>Ref                            | Vref                                  | 2.5      | V <sub>DD_tsc</sub> | V <sub>DD_tsc</sub> | V     |

| Fusebox program supply voltage<br>FUSE_VDD <sup>2</sup>                 | FUSEV <sub>DD</sub><br>(program mode) | 3.3 ± 5% | _                   | 3.6                 | V     |

| Supply output <sup>3</sup> NVCC_DRYICE                                  | V <sub>DD</sub> _                     | 1.0      | _                   | 1.55                | V     |

| Operating ambient temperature                                           | T <sub>A</sub>                        | -40      | _                   | 85                  | °C    |

V<sub>DD\_BAT</sub> must always be powered by battery in security application. In non-security case, V<sub>DD\_BAT</sub> can be connected to QV<sub>DD</sub>.

The fusebox read supply is connected to supply of the full speed USBPHY2\_VDD. FUSE\_VDD is only used for programming. It is recommended that FUSE\_VDD be connected to ground when not being used for programming. See Table 7 for current parameters.

<sup>&</sup>lt;sup>3</sup> NVCC\_DRYICE is a supply output. An external capacitor no less than 4 μF must be connected to it. A 4.7 μF capacitor is recommended.

#### 3.1.3 Fusebox Supply Current Parameters

Table 7 lists the fusebox supply current parameters.

**Table 7. Fusebox Supply Current Parameters**

| Parameter                                                                                                  | Symbol               | Min. | Тур. | Max. | Units |

|------------------------------------------------------------------------------------------------------------|----------------------|------|------|------|-------|

| eFuse program current <sup>1</sup> Current to program one eFuse bit The associated VDD_FUSE supply = 3.6 V | I <sub>program</sub> | 26   | 35   | 62   | mA    |

| eFuse read current <sup>2</sup><br>Current to read an 8-bit eFuse word                                     | I <sub>read</sub>    | _    | 12.5 | 15   | mA    |

The current I<sub>program</sub> is during program time (t<sub>program</sub>).

## 3.1.4 Interface Frequency Limits

Table 8 provides information for interface frequency limits.

**Table 8. Interface Frequency Limits**

| Parameter                        | Min. | Тур.   | Max. | Units |

|----------------------------------|------|--------|------|-------|

| JTAG: TCK Frequency of Operation | DC   | 5      | 10   | MHz   |

| OSC24M_XTAL Oscillator           | _    | 24     | _    | MHz   |

| OSC32K_XTAL Oscillator           | _    | 32.768 | _    | kHz   |

Table 9 provides the recommended external crystal specifications.

**Table 9. Recommended External Crystal Specifications**

|                     | 24 MHz      | 32.768 kHz                          |

|---------------------|-------------|-------------------------------------|

| Frequency Tolerance | <= ± 30 ppm | <= ± 30 ppm                         |

| ESR                 | < 80 Ω      | 50 K~60 K                           |

| Load Capacitor      | 8 pF–12 pF  | 6 pF-8 pF (12 pF-16 pF on each pin) |

| Shunt Capacitor     | < 7 pF      | 1 pF                                |

| Drive Level         | > 150 μW    | > 1 µW                              |

Table 10 provides the recommended external reference clock oscillator specifications (when reference is used from an external clock source).

Table 10. Recommended External Reference Clock Specifications

|                     | 24 MHz         | 32.768 kHz     |

|---------------------|----------------|----------------|

| V <sub>OH</sub>     | min = 0.7* VDD | min = 0.7* VDD |

| V <sub>OL</sub>     | max = 0.3* VDD | max = 0.3* VDD |

| Frequency Tolerance | = 30 ppm       | = 30 ppm       |

i.MX25 Applications Processor for Consumer and Industrial Products, Rev. 10

<sup>&</sup>lt;sup>2</sup> The current I<sub>read</sub> is present for approximately 50 ns of the read access to the 8-bit word.

Table 10. Recommended External Reference Clock Specifications (continued)

| T <sub>RISE</sub> | 1% T <sub>CLOCK</sub> | 1% T <sub>CLOCK</sub> |

|-------------------|-----------------------|-----------------------|

| T <sub>FALL</sub> | 1% T <sub>CLOCK</sub> | 1% T <sub>CLOCK</sub> |

| Duty Cycle        | 50%                   | 50%                   |

## 3.1.5 USB\_PHY Current Consumption

Table 11 provides information for USB\_PHY current consumption.

Table 11. USB PHY Current Consumption<sup>1</sup>

| Parameter                                                    | Condition      | ons | Typ.<br>(@Typ. Temp) | Max.<br>(@Max. Temp) | Unit |

|--------------------------------------------------------------|----------------|-----|----------------------|----------------------|------|

| Analog supply                                                |                | Rx  | 11.4                 | _                    |      |

| USBPHY1_VDDA_BIAS, USBPHY1_UPLL_VDD,<br>USBPHY1_VDDA (3.3 V) | Full speed     | Tx  | 22,6                 | _                    | mA   |

|                                                              | Llight and and |     | 21.5                 | _                    |      |

|                                                              | High speed     | Tx  | 33.8                 | _                    |      |

|                                                              | Suspend        | _   | 0.6                  |                      | μΑ   |

| Analog supply                                                |                | Rx  | 120                  | _                    | μΑ   |

| USBPHY2_VDD (3.3 V)                                          | Full Speed     | Tx  | 25                   | _                    | mA   |

|                                                              |                | Rx  | 252                  | _                    | μА   |

|                                                              | Low Speed      | Tx  | 5.5                  | _                    | mA   |

| All supplies                                                 | Suspend        |     | 50                   | 100                  | μΑ   |

<sup>1</sup> Values must be verified

#### 3.1.6 Power Modes

Table 12 describes the core, clock, and module settings for the different power modes of the processor.

Table 12. i.MX25 Power Mode Settings

| Core/Clock/Module  | Power Mode            |                            |                         |                     |                     |  |  |  |

|--------------------|-----------------------|----------------------------|-------------------------|---------------------|---------------------|--|--|--|

| Core/Clock/wiodule | Doze                  | Wait                       | Stop/Sleep <sup>1</sup> | Run (266 MHz)       | Run (400 MHz)       |  |  |  |

| ARM core           | Platform clock is off | In wait-for-interrupt mode | _                       | Active @<br>266 MHz | Active @<br>400 MHz |  |  |  |

| Well bias          | On                    | Off                        | On                      | Off                 | Off                 |  |  |  |

| MCU PLL            | On                    | On                         | Off                     | On                  | On                  |  |  |  |

| USB PLL            | Off                   | Off                        | Off                     | On                  | On                  |  |  |  |

| OSC24M             | On                    | On                         | Off                     | On                  | On                  |  |  |  |

| OSC32K             | On                    | On                         | On                      | On                  | On                  |  |  |  |

| Other modules      | Off                   | Off                        | Off                     | On                  | On                  |  |  |  |

<sup>&</sup>lt;sup>1</sup> Sleep mode differs from stop mode in that the core voltage is reduced to 1 V.

Table 13 shows typical current consumption for the various power supplies under the various power modes.

**Table 13. i.MX25 Power Mode Current Consumption**

|                        | D 0 11                                                    | Voltage | Cu      | rrent Consumpt | ion for Power Mod | les <sup>1</sup> |  |

|------------------------|-----------------------------------------------------------|---------|---------|----------------|-------------------|------------------|--|

| Power Group            | Power Supplies                                            | Setting | Doze    | Wait           | Stop              | Sleep            |  |

| NVCC_EMI               | NVCC_EMI1<br>NVCC_EMI2                                    | 3.0 V   | 5 μΑ    | 3.15 μΑ        | 3.51 μΑ           | 3.61 μΑ          |  |

| NVCC_CRM               | NVCC_CRM                                                  | 3.0 V   | 1.15 μΑ | 4.31 μΑ        | 0.267 μΑ          | 0.32 μΑ          |  |

| NVCC_<br>OTHER         | NVCC_SDIO NVCC_CSI NVCC_NFC NVCC_JTAG NVCC_LCDC NVCC_MISC | 3.0 V   | 31.2 μΑ | 29.5 μΑ        | 31.7 μΑ           | 32.1 μΑ          |  |

| NVCC_ADC               | NVCC_ADC                                                  | 3.0 V   | 163 μΑ  | 3.25 μΑ        | 1.14 μΑ           | 0.871 μΑ         |  |

| OSC24M                 | OSC24M_<br>VDD                                            | 3.0 V   | 906 μΑ  | 903 μΑ         | 10.2 μA mA        | 10.5 μΑ          |  |

| PLL_VDD                | MPLL_VDD<br>UPLL_VDD                                      | 1.4 V   | 6.83 mA | 6.83 mA        | 38.9 μΑ           | 39.1 μΑ          |  |

| QVDD                   | QVDD                                                      | 1.15 V  | 8.79 mA | 11.28 mA       | 842 μΑ            | 665 μΑ           |  |

| USBPHY1_<br>VDDA       | USBPHY1_<br>VDDA                                          | 3.17 V  | 240 μΑ  | 240 μΑ         | 241 μΑ            | 242 μΑ           |  |

| USBPHY1_<br>VDDA_VBIAS | USBPHY1_<br>VDDA_VBIAS                                    | 3.17 V  | 0.6 μΑ  | 1.46 μΑ        | 0.328 μΑ          | 0.231 μΑ         |  |

| USBPHY1_<br>UPLL_VDD   | USBPHY1_<br>UPLL_VDD                                      | 3.17 V  | 201 μΑ  | 201 μΑ         | 191 μΑ            | 191 μΑ           |  |

| USBPHY2                | USBPHY2_<br>VDD                                           | 3.0 V   | 158 μΑ  | 0158 μΑ        | 164 μΑ            | 164 μΑ           |  |

<sup>&</sup>lt;sup>1</sup> Values are typical, under typical use conditions.

In the reduced power mode, shown in Table 14, the i.MX25 is powered down, while the RTC clock and the secure keys (in secure-use case), remain operational. BAT\_VDD is tied to a battery while all other supplies are turned off.

#### NOTE

In this low-power mode, i.MX25 cannot be woken up with an interrupt; it must be powered back up before it can detect any events.

Table 14. iMX25 Reduced Power Mode Current Consumption

| Power Group | Power Supply | Voltage Setting | Typical Current Consumption |

|-------------|--------------|-----------------|-----------------------------|

| BAT_VDD     | BAT_VDD      | 1.15 V          | 9.95 μΑ                     |

|             |              | 1.55 V          | 12.6 μΑ                     |

## 3.2 Supply Power-Up/Power-Down Requirements and Restrictions

Any i.MX25 board design must comply with the power-up and power-down sequence guidelines given in this section to ensure reliable operation of the device. Recommended power-up and power-down sequences are given in the following subsections.

#### **CAUTION**

Deviations from the guidelines in this section may result in the following situations:

- Excessive current during power-up phase

- Prevention of the device from booting

- Irreversible damage to the i.MX25 (worst-case scenario)

#### NOTE

For security applications, the coin battery must be connected during both power-up and power-down sequences to ensure that security keys are not unintentionally erased.

## 3.2.1 Power-Up Sequence

For those users that are not using DryIce/SRTC, the following power-up sequence is recommended:

- 1. Assert power on reset (POR).

- 2. Turn on QVDD digital logic domain supplies.

- 3. Turn on NVCCx digital I/O power supplies after QVDD is stable.

- 4. Turn on all other analog power supplies, including USBPHY1\_VDDA\_BIAS, USBPHY1\_UPLL\_VDD, USBPHY1\_VDDA, USBPHY2\_VDD, OSC24M\_VDD, MPPLL\_VDD, UPLL\_VDD, NVCC\_ADC, and FUSEVDD (FUSEVDD is tied to GND if fuses are not programmed), after all NVCCx digital I/O supplies are stable.

- 5. Negate the POR signal.

#### NOTE

- The user is advised to connect FUSEVDD to GND except when fuses are programmed, to prevent unintentional blowing of fuses.

- Other power-up sequences may be possible; however, the above sequence has been verified and is recommended.

- There is a 1 ms minimum time between supplies coming up, and a 1 ms minimum time between POR\_B assert and de-assert.

- The dV/dT should be no faster than 0.25 V/µs for all power supplies, to avoid triggering ESD circuit.

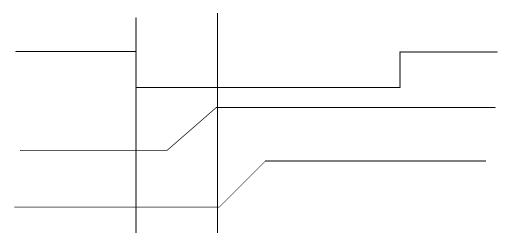

Figure 2 shows the power-up sequence diagram. After POR\_B is asserted, Core VDD and NVDDx can be powered up. After Core VDD and NVDDx are stable, the analog supplies can be powered up.

Figure 2. Power-Up Sequence Diagram

## 3.2.2 Power-Down Sequence

There are no special requirements for the power-down sequence. All power supplies can be shut down at the same time.

## 3.2.3 SRTC Drylce Power-Up/Down Sequence

In order to guarantee Drylce power-loss protection, including retention of SRTC time data during power down, users must do the following:

- Place a proper capacitor on the NVCC\_DRYICE output pin, and

- Implement the below power-up/down sequence

- 1. Assert power on reset (POR).

- 2. Turn on NVCC\_CRM.

- 3. Turn on QVDD digital logic domain supplies for not less than 1 ms and not more than 32 ms, after NVCC CRM reaches 90% of 3.3 V.

i.MX25 Applications Processor for Consumer and Industrial Products, Rev. 10

#### NOTE

This is to guarantee that POR is stable already at NVCC\_CRM/QVDD power domain interface before QVDD is turned on, and POR instantly propagates to QVDD domain after QVDD is turned on.

- 4. Turn on other NVCCx digital I/O power supplies for not less than 1 ms and not more than 32 ms, after QVDD reaches 90% of 1.2 V.

- 5. Turn on all other analog power supplies, including USBPHY1\_VDDA\_BIAS, USBPHY1\_UPLL\_VDD, USBPHY1\_VDDA, USBPHY2\_VDD, NVCC\_ADC, OSC24M\_VDD, MPPLL\_VDD, UPLL\_VDD, and FUSEVDD (FUSEVDD is tied to GND if fuses are not programmed) for not less than 1 ms and not more than 32 ms, after NVCCx reaches 90% of 3.3 V.

#### NOTE

This is to guarantee that analog peripherals can get properly initialized (reset) values from QVDD domain and NVCCx domain.

6. Negate the POR signal for at least 90 µs after all previous steps.

#### **NOTE**

- This is to guarantee that both POR logic and clocks are stable inside the i.MX25 chip, before POR is removed.

- The dV/dT should be no faster than 0.25 V/us for all power supplies, to avoid triggering ESD circuit.

In addition, the following power-down sequence is recommended:

- 1. Turn off power for analog parts, including USBPHY1\_VDDA\_BIAS, USBPHY1\_UPLL\_VDD, USBPHY1\_VDDA, USBPHY2\_VDD, NVCC\_ADC, and FUSEVDD (FUSEVDD is tied to GND if fuses are not programmed).

- 2. Turn off QVDD.

- 3. Turn off NVCCx, PLL, OSC, and other powers.

#### NOTE

The power-down steps can be executed simultaneously, or very shortly one after another.

#### 3.3 Power Characteristics

Table 15 shows values representing maximum current numbers for the i.MX25 under worst case voltage and temperature conditions. These values are derived from the i.MX25 with core clock speed up to 400 MHz. Additionally, no power saving techniques such as clock gating were implemented when measuring these values. Common supplies are bundled according to the i.MX25 power-up sequence requirements. Peak numbers are provided for system designers so that the i.MX25 power supply requirements are satisfied during startup and transient conditions. Freescale recommends that system

current measurements are taken with customer-specific use-cases to reflect the normal operating conditions in the end system.

**Table 15. Power Consumption**

| Power Supply                                                                              | Voltage (V) | Max Current (mA) |

|-------------------------------------------------------------------------------------------|-------------|------------------|

| QVDD                                                                                      | 1.52        | 360              |

| NVCC_EMI1, NVCC_EMI2                                                                      | 1.9         | 30               |

| NVCC_CRM, NVCC_SDIO, NVCC_CSI,<br>NVCC_NFC, NVCC_JTAG, NVCC_LCDC,<br>NVCC_MISC            | 3.6         | 110              |

| MPLL_VDD, UPLL_VDD                                                                        | 1.65        | 20               |

| USBPHY1_VDDA_BIAS,USBPHY1_UPLL_VDD,<br>USBPHY1_VDDA, USBPHY2_VDD,<br>OSC24M_VDD, NVCC_ADC | 3.3         | 40               |

| FUSE_VDD <sup>1</sup>                                                                     | 3.6         | 62               |

| BATT_VDD                                                                                  | 1.55        | 0.030            |

<sup>&</sup>lt;sup>1</sup> The FUSE\_VDD rail is connected to ground. it only needs a voltage if the system fuse burning is needed.

The method for obtaining the maximum current is as follows:

- 1. Measure the worst case power consumption on individual rails using directed test on i.MX25.

- 2. Correlate the worst case power consumption power measurements with the worst case power consumption simulations.

- 3. Combine common voltage rails based on the power supply sequencing requirements (add the worst case power consumption on each rail within some test cases from several test cases run, to maximize different rails in the power group).

- 4. Guard the worst case numbers for temperature and process variation.

- 5. The sum of individual rails is greater than the real world power consumption, since a real system does not typically maximize the power consumption on all peripherals simultaneously.

- 6. BATT\_VDD current is measured when the system is in reduced power mode maintaining the RTC. When the system is in run mode, QVDD is used to supply the DryIce, so this current becomes negligible. See Table 12, for more details on the power modes.

#### NOTE

The values mentioned above should not be taken as a typical max run data for specific use cases. These values are Absolute MAX data. Freescale recommends that the system current measurements are taken with customer-specific use-cases to reflect normal operating conditions in the end system.

#### 3.4 Thermal Characteristics

The thermal resistance characteristics for the device are given in Table 16. These values are measured under the following conditions:

- Two-layer substrate

- Substrate solder mask thickness: 0.025 mm

- Substrate metal thicknesses: 0.016 mm

- Substrate core thickness: 0.200 mm

- Core through I.D: 0.118 mm, Core through plating 0.016 mm.

- Flag: Trace style with ground balls under the die connected to the flag

- Die Attach: 0.033 mm non-conductive die attach, k = 0.3 W/m K

- Mold compound: Generic mold compound; k = 0.9 W/m K

**Table 16. Thermal Resistance Data**

| Rating                                              | Condition               | Symbol              | Value | Unit |

|-----------------------------------------------------|-------------------------|---------------------|-------|------|

| Junction to ambient <sup>1</sup> natural convection | Single layer board (1s) | R <sub>eJA</sub>    | 55    | °C/W |

| Junction to ambient <sup>1</sup> natural convection | Four layer board (2s2p) | R <sub>eJA</sub>    | 33    | °C/W |

| Junction to ambient <sup>1</sup> (@200 ft/min)      | Single layer board (1s) | R <sub>eJMA</sub>   | 46    | °C/W |

| Junction to ambient <sup>1</sup> (@200 ft/min)      | Four layer board (2s2p) | R <sub>eJMA</sub>   | 29    | °C/W |

| Junction to boards <sup>2</sup>                     | _                       | R <sub>eJB</sub>    | 22    | °C/W |

| Junction to case (top) <sup>3</sup>                 | _                       | R <sub>eJCtop</sub> | 13    | °C/W |

| Junction to package top <sup>4</sup>                | Natural convection      | $\Psi_{JT}$         | 2     | °C/W |

Junction-to-ambient thermal resistance determined per JEDC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

#### 3.5 I/O DC Parameters

This section includes the DC parameters of the following I/O types:

- DDR I/O: Mobile DDR (mDDR), double data rate (DDR2), or synchronous dynamic random access memory (SDRAM)

- General purpose I/O (GPIO)

Junction-to-board thermal resistance determined per JEDC JESD51-8. Thermal test board meets JEDEC specification for this package.

Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

<sup>&</sup>lt;sup>4</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, this thermal characterization parameter is written as Psi-JT.

#### NOTE

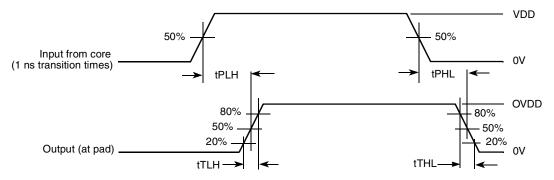

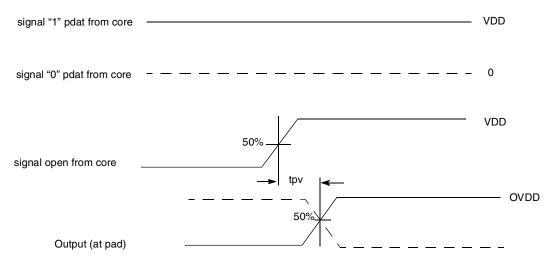

The term 'OVDD' in this section refers to the associated supply rail of an input or output. The association is shown in the "Signal Multiplexing" chapter of the reference manual.

#### 3.5.1 DDR I/O DC Parameters