Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# ala Sami

### ale Semiconductor

Data Sheet: Technical Data

Document Number: MCIMX35SR2AEC Rev. 10, 06/2012

### **IMX35**

#### Package Information

Plastic Package Case 5284 17 x 17 mm, 0.8 mm Pitch

#### Ordering Information

See Table 1 on page 3 for ordering information.

## i.MX35 Applications Processors for Automotive Products

### 1 Introduction

The i.MX35 Auto Application Processor family is designed for automotive infotainment and navigation applications. These processors are AECQ100 Grade 3 qualified and rated for ambient operating temperatures up to 85 °C.

Based on an ARM11 microprocessor core running at up to 532 MHz, the device offers the following features and optimized system cost for the target applications.

- Audio connectivity and telematics:

- Compressed audio playback from storage devices (CD, USB, HDD or SD card)

- PlayFromDevice (1-wire and 2-wire support) for portable media players

- iPod/iPhone control and playback

- High-speed CD ripping to USB, SD/MMC or HDD for virtual CD changer

- Audio processing for hands-free telephony: Bluetooth, AEC/NS, and microphone beam forming

- Speech recognition

| 1. | Intro | duction                                         | 1     |

|----|-------|-------------------------------------------------|-------|

|    | 1.1.  | Features                                        | 2     |

|    | 1.2   | Ordering Information                            | 3     |

|    | 1.3.  | Block Diagram                                   | 5     |

| 2  | Fund  | ctional Description and Application Information | 4     |

|    | 2.1.  | Application Processor Domain Overview           | 5     |

|    | 2.2.  | Shared Domain Overview                          | 6     |

|    | 2.3.  | Advanced Power Management Overview              | 6     |

|    | 2.4.  | ARM11 Microprocessor Core                       | 6     |

|    | 2.5.  | Module Inventory                                | 7     |

| 3. | Sign  | al Descriptions: Special Function Related Pins  | 12    |

| 4. | Elec  | trical Characteristics                          | 13    |

|    | 4.1.  | i.MX35 Chip-Level Conditions                    | 13    |

|    | 4.2.  | Power Modes                                     | 15    |

|    | 4.3.  | Supply Power-Up/Power-Down Requirements a       | nd    |

|    |       | Restrictions                                    | 16    |

|    | 4.4.  | Reset Timing                                    | 18    |

|    | 4.5.  | Power Characteristics                           | 19    |

|    | 4.6.  | Thermal Characteristics                         | 20    |

|    | 4.7.  | I/O Pin DC Electrical Characteristics           | 21    |

|    | 4.8.  | I/O Pin AC Electrical Characteristics           |       |

|    | 4.9.  | Module-Level AC Electrical Specifications       |       |

| 5. | Pack  | kage Information and Pinout                     |       |

|    | 5.1.  | MAPBGA Production Package 1568-01, 17 × 17      | 7 mm  |

|    |       | 0.8 Pitch                                       |       |

|    | 5.2.  | MAPBGA Signal Assignments                       | 133   |

| 6. | Prod  | luct Documentation                              | 145   |

| 7. | Revi  | sion History                                    | . 146 |

- A/V connectivity and navigation:

- Includes audio connectivity and telematics features

- Map display and route calculation

- QVGA video decode, WVGA video display

- Sophisticated graphical user interface

The i.MX35 processor takes advantage of the ARM1136JF-S<sup>TM</sup> core running at 532 MHz that is boosted by a multilevel cache system, and features peripheral devices such as an autonomous image processing unit, a vector floating point (VFP11) co-processor, and a RISC-based DMA controller.

The i.MX35 supports connections to various types of external memories, such as SDRAM, mobile DDR and DDR2, SLC and MLC NAND Flash, NOR Flash and SRAM. The device can be connected to a variety of external devices such as high-speed USB2.0 OTG, ATA, MMC/SDIO, and Compact Flash.

#### 1.1 Features

The i.MX35 is designed for automotive infotainment video-enabled applications. It provides low-power solutions for applications demanding high-performance multimedia and graphics.

The i.MX35 is based on the ARM1136 platform, which has the following features:

- ARM1136JF-S processor, version r1p3

- 16-Kbyte L1 instruction cache

- 16-Kbyte L1 data cache

- 128-Kbyte L2 cache, version r0p4

- 128 Kbytes of internal SRAM

- Vector floating point unit (VFP11)

To boost multimedia performance, the following hardware accelerators are integrated:

- Image processing unit (IPU)

- OpenVG 1.1 graphics processing unit (GPU) (not available for the MCIMX351)

The MCIMX35 provides the following interfaces to external devices (some of these interfaces are muxed and not available simultaneously):

- 2 controller area network (CAN) interfaces

- 2 SDIO/MMC interfaces, 1 SDIO/CE-ATA interface (CE-ATA is not available for the MCIMX351)

- 32-bit mobile DDR, DDR2 (4-bank architecture), and SDRAM (up to 133 MHz)

- 2 configurable serial peripheral interfaces (CSPI) (up to 52 Mbps each)

- Enhanced serial audio interface (ESAI)

- 2 synchronous serial interfaces (SSI)

- Ethernet MAC 10/100 Mbps

- 1 USB 2.0 host with ULPI interface or internal full-speed PHY. Up to 480 Mbps if external HS PHY is used.

- 1 USB 2.0 OTG (up to 480 Mbps) controller with internal high-speed OTG PHY

- Flash controller—MLC/SLC NAND and NOR

- GPIO with interrupt capabilities

- 3 I<sup>2</sup>C modules (up to 400 Kbytes each)

- JTAG

- Key pin port

- Media local bus (MLB) interface

- Asynchronous sample rate converter (ASRC)

- 1-Wire

- Parallel camera sensor (4/8/10/16-bit data port for video color models: YCC, YUV, 30 Mpixels/s)

- Parallel display (primary up to 24-bit, 1024 x 1024)

- Parallel ATA (up to 66 Mbytes) (not available for the MCIMX351)

- PWM

- SPDIF transceiver

- 3 UART (up to 4.0 Mbps each)

### 1.2 Ordering Information

Table 1 provides the ordering information for the i.MX35 processors for automotive applications.

**Table 1. Ordering Information**

| Description | Part Number   | Silicon<br>Revision | Package <sup>1</sup> | Speed                | Operating<br>Temperature<br>Range (°C) | Signal Ball<br>Map<br>Locations | Ball Map |

|-------------|---------------|---------------------|----------------------|----------------------|----------------------------------------|---------------------------------|----------|

| i.MX351     | MCIMX351AVM4B | 2.0                 | 5284                 | 400 MHz              | -40 to 85                              | Table 94                        | Table 96 |

| i.MX351     | MCIMX351AVM5B | 2.0                 | 5284                 | 532 MHz <sup>2</sup> | -40 to 85                              | Table 94                        | Table 96 |

| i.MX355     | MCIMX355AVM4B | 2.0                 | 5284                 | 400 MHz              | -40 to 85                              | Table 94                        | Table 96 |

| i.MX355     | MCIMX355AVM5B | 2.0                 | 5284                 | 532 MHz <sup>2</sup> | -40 to 85                              | Table 94                        | Table 96 |

| i.MX356     | MCIMX356AVM4B | 2.0                 | 5284                 | 400 MHz              | -40 to 85                              | Table 94                        | Table 96 |

| i.MX356     | MCIMX356AVM5B | 2.0                 | 5284                 | 532 MHz <sup>2</sup> | -40 to 85                              | Table 94                        | Table 96 |

| i.MX351     | MCIMX351AJQ4C | 2.1                 | 5284                 | 400MHz               | -40 to 85                              | Table 95                        | Table 97 |

| i.MX351     | MCIMX351AJQ5C | 2.1                 | 5284                 | 532MHz <sup>2</sup>  | -40 to 85                              | Table 95                        | Table 97 |

| i.MX355     | MCIMX355AJQ4C | 2.1                 | 5284                 | 400MHz               | -40 to 85                              | Table 95                        | Table 97 |

| i.MX355     | MCIMX355AJQ5C | 2.1                 | 5284                 | 532MHz <sup>2</sup>  | -40 to 85                              | Table 95                        | Table 97 |

| i.MX356     | MCIMX356AJQ4C | 2.1                 | 5284                 | 400MHz               | -40 to 85                              | Table 95                        | Table 97 |

| i.MX356     | MCIMX356AJQ5C | 2.1                 | 5284                 | 532MHz <sup>2</sup>  | -40 to 85                              | Table 95                        | Table 97 |

| i.MX356     | SCIMX356BVMB  | 2                   | 5284                 | 532MHz               | -40 to 85                              | Table 94                        | Table 96 |

<sup>1</sup> Case 5284 is RoHS-compliant, lead-free, MSL = 3, 1.

<sup>&</sup>lt;sup>2</sup> 532 MHz rated devices meet all specifications of 400 MHz rated devices. A 532 MHz device can be substituted in place of a 400 MHz device.

The ball map for silicon revision 2.1 is different than the ballmap for silicon revision 2.0. The layout for each revision is not compatible, so it is important that the correct ballmap be used to implement the layout. See Section 5, "Package Information and Pinout."

Table 2 shows the functional differences between the different parts in the i.MX35 family.

Table 2. Functional Differences in the i.MX35 Parts

| Module                                                                                                                         | MCIMX351 | MCIMX353 | MCIMX355 | MCIMX356 | MCIMX357 |

|--------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|

| I2C (3)                                                                                                                        | Yes      | Yes      | Yes      | Yes      | Yes      |

| CSPI (2)                                                                                                                       | Yes      | Yes      | Yes      | Yes      | Yes      |

| SSI/I2S (2)                                                                                                                    | Yes      | Yes      | Yes      | Yes      | Yes      |

| ESAI                                                                                                                           | Yes      | Yes      | Yes      | Yes      | Yes      |

| SPDIF I/O                                                                                                                      | Yes      | Yes      | Yes      | Yes      | Yes      |

| USB HS Host                                                                                                                    | Yes      | Yes      | Yes      | Yes      | Yes      |

| USB OTG                                                                                                                        | Yes      | Yes      | Yes      | Yes      | Yes      |

| FlexCAN (2)                                                                                                                    | Yes      | Yes      | Yes      | Yes      | Yes      |

| MLB                                                                                                                            | Yes      | Yes      | Yes      | Yes      | Yes      |

| Ethernet                                                                                                                       | Yes      | Yes      | Yes      | Yes      | Yes      |

| 1-Wire                                                                                                                         | Yes      | Yes      | Yes      | Yes      | Yes      |

| KPP                                                                                                                            | Yes      | Yes      | Yes      | Yes      | Yes      |

| SDIO/MMC (2)                                                                                                                   | Yes      | Yes      | Yes      | Yes      | Yes      |

| SDIO/Memory Stick                                                                                                              | Yes      | Yes      | Yes      | Yes      | Yes      |

| External Memory Controller (EMC)                                                                                               | Yes      | Yes      | Yes      | Yes      | Yes      |

| JTAG                                                                                                                           | Yes      | Yes      | Yes      | Yes      | Yes      |

| PATA                                                                                                                           | _        | Yes      | Yes      | Yes      | Yes      |

| CE-ATA                                                                                                                         | _        | Yes      | Yes      | Yes      | Yes      |

| Image Processing Unit (IPU) (inversion and rotation, pre- and post-processing, camera interface, blending, display controller) | _        | Yes      | Yes      | Yes      | Yes      |

| Open VG graphics acceleration (GPU)                                                                                            | _        | Yes      | _        | Yes      | Yes      |

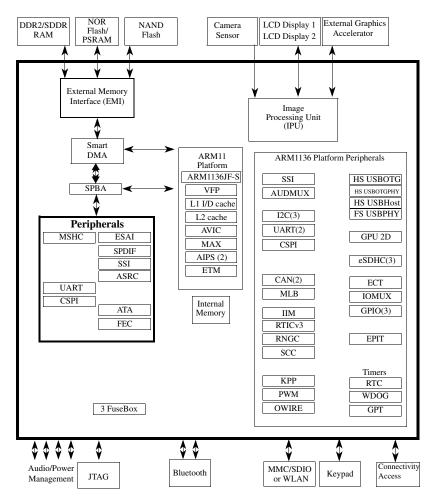

### 1.3 Block Diagram

Figure 1 is the i.MX35 simplified interface block diagram.

Figure 1. i.MX35 Simplified Interface Block Diagram

### 2 Functional Description and Application Information

The i.MX35 consists of the following major subsystems:

- ARM1136 Platform—AP domain

- SDMA Platform and EMI—Shared domain

### 2.1 Application Processor Domain Overview

The applications processor (AP) and its domain are responsible for running the operating system and applications software, providing the user interface, and supplying access to integrated and external peripherals. The AP domain is built around an ARM1136JF-S core with 16-Kbyte instruction and data L1 caches, an MMU, a 128-Kbyte L2 cache, a multiported crossbar switch, and advanced debug and trace interfaces.

The i.MX35 core is intended to operate at a maximum frequency of 532 MHz to support the required multimedia use cases. Furthermore, an image processing unit (IPU) is integrated into the AP domain to offload the ARM11 core from performing functions such as color space conversion, image rotation and scaling, graphics overlay, and pre- and post-processing.

The functionality of AP Domain peripherals includes the user interface; the connectivity, display, security, and memory interfaces; and 128 Kbytes of multipurpose SRAM.

#### 2.2 Shared Domain Overview

The shared domain is composed of the shared peripherals, a smart DMA engine (SDMA) and a number of miscellaneous modules. For maximum flexibility, some peripherals are directly accessible by the SDMA engine.

The i.MX35 has a hierarchical memory architecture including L1 caches and a unified L2 cache. This reduces the bandwidth demands for the external bus and external memory. The external memory subsystem supports a flexible external memory system, including support for SDRAM (SDR, DDR2 and mobile DDR) and NAND Flash.

### 2.3 Advanced Power Management Overview

To address the continuing need to reduce power consumption, the following techniques are incorporated in the i.MX35:

- Clock gating

- Power gating

- Power-optimized synthesis

- Well biasing

The insertion of gating into the clock paths allows unused portions of the chip to be disabled. Because static CMOS logic consumes only leakage power, significant power savings can be realized.

"Well biasing" is applying a voltage that is greater than  $V_{DD}$  to the nwells, and one that is lower than  $V_{SS}$  to the pwells. The effect of applying this well back bias voltage reduces the subthreshold channel leakage. For the 90-nm digital process, it is estimated that the subthreshold leakage is reduced by a factor of ten over the nominal leakage. Additionally, the supply voltage for internal logic can be reduced from 1.4 V to 1.22 V.

### 2.4 ARM11 Microprocessor Core

The CPU of the i.MX35 is the ARM1136JF-S core, based on the ARM v6 architecture. This core supports the ARM Thumb<sup>®</sup> instruction sets, features Jazelle<sup>®</sup> technology (which enables direct execution of Java byte codes) and a range of SIMD DSP instructions that operate on 16-bit or 8-bit data values in 32-bit registers.

The ARM1136JF-S processor core features are as follows:

- Integer unit with integral EmbeddedICE<sup>TM</sup> logic

- Eight-stage pipeline

- Branch prediction with return stack

- Low-interrupt latency

- Instruction and data memory management units (MMUs), managed using micro TLB structures backed by a unified main TLB

- Instruction and data L1 caches, including a non-blocking data cache with hit-under-miss

- Virtually indexed/physically addressed L1 caches

- 64-bit interface to both L1 caches

- Write buffer (bypassable)

- High-speed Advanced Micro Bus Architecture (AMBA)<sup>TM</sup> L2 interface

- Vector floating point co-processor (VFP) for 3D graphics and hardware acceleration of other floating-point applications

- ETM<sup>TM</sup> and JTAG-based debug support

Table 3 summarizes information about the i.MX35 core.

Table 3. i.MX35 Core

| Core                | Core                | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Integrated Memory                                                                                                                                    |

|---------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acronym             | Name                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Features                                                                                                                                             |

| ARM11 or<br>ARM1136 | ARM1136<br>Platform | The ARM1136™ platform consists of the ARM1136JF-S core, the ETM real-time debug modules, a 6 × 5 multi-layer AHB crossbar switch (MAX), and a vector floating processor (VFP).  The i.MX35 provides a high-performance ARM11 microprocessor core and highly integrated system functions. The ARM Application Processor (AP) and other subsystems address the needs of the personal, wireless, and portable product market with integrated peripherals, advanced processor core, and power management capabilities. | <ul> <li>16-Kbyte instruction cache</li> <li>16-Kbyte data cache</li> <li>128-Kbyte L2 cache</li> <li>32-Kbyte ROM</li> <li>128-Kbyte RAM</li> </ul> |

### 2.5 Module Inventory

Table 4 shows an alphabetical listing of the modules in the MCIMX35. For extended descriptions of the modules, see the MCIMX35 reference manual.

**Table 4. Digital and Analog Modules**

| Block<br>Mnemonic | Block Name                         | Domain <sup>1</sup> | Subsystem                          | Brief Description                                                                                                                                                                                                                                                                                                                    |

|-------------------|------------------------------------|---------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-WIRE            | 1-Wire interface                   | ARM                 | ARM1136<br>platform<br>peripherals | 1-Wire provides the communication line to a 1-Kbit add-only memory. the interface can send or receive 1 bit at a time.                                                                                                                                                                                                               |

| ASRC              | Asynchronous sample rate converter | SDMA                | Connectivity peripherals           | The ASRC is designed to convert the sampling rate of a signal associated to an input clock into a signal associated to a different output clock. It supports a concurrent sample rate conversion of about –120 dB THD+N. The sample rate conversion of each channel is associated to a pair of incoming and outgoing sampling rates. |

Table 4. Digital and Analog Modules (continued)

| Block<br>Mnemonic | Block Name                                        | Domain <sup>1</sup> | Subsystem                                                                                                                                                                                                                                                                                                                                                                                                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATA               | ATA module                                        | SDMA                | Connectivity peripherals                                                                                                                                                                                                                                                                                                                                                                                    | The ATA block is an AT attachment host interface. Its main use is to interface with IDE hard disk drives and ATAPI optical disk drives. It interfaces with the ATA device over a number of ATA signals.                                                                                                                                                                                                             |

| AUDMUX            | Digital audio<br>mux                              | ARM                 | Multimedia peripherals  The AUDMUX is a programmable interconnect for voice, audio, an synchronous data routing between host serial interfaces (SSIs) an peripheral serial interfaces (audio codecs). The AUDMUX has two sets of interfaces: internal ports to on-chip peripherals and external ports to off-chip audio devices. Data is routed by configuring the appropriate internal and external ports. |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CAN(2)            | CAN module                                        | ARM                 | Connectivity peripherals                                                                                                                                                                                                                                                                                                                                                                                    | The CAN protocol is primarily designed to be used as a vehicle serial data bus running at 1 Mbps.                                                                                                                                                                                                                                                                                                                   |

| CCM               | Clock control module                              | ARM                 | Clocks                                                                                                                                                                                                                                                                                                                                                                                                      | This block generates all clocks for the peripherals in the SDMA platform. The CCM also manages ARM1136 platform low-power modes (WAIT, STOP), disabling peripheral clocks appropriately for power conservation, and provides alternate clock sources for the ARM1136 and SDMA platforms.                                                                                                                            |

| CSPI(2)           | Configurable<br>serial<br>peripheral<br>interface | SDMA,<br>ARM        | Connectivity peripherals                                                                                                                                                                                                                                                                                                                                                                                    | This module is a serial interface equipped with data FIFOs; each master/slave-configurable SPI module is capable of interfacing to both serial port interface master and slave devices. The CSPI ready (SPI_RDY) and slave select (SS) control signals enable fast data communication with fewer software interrupts.                                                                                               |

| ECT               | Embedded<br>cross trigger                         | SDMA,<br>ARM        | Debug                                                                                                                                                                                                                                                                                                                                                                                                       | ECT (embedded cross trigger) is an IP for real-time debug purposes. It is a programmable matrix allowing several subsystems to interact with each other. ECT receives signals required for debugging purposes (from cores, peripherals, buses, external inputs, and so on) and propagates them (propagation programmed through software) to the different debug resources available within the SoC.                 |

| ЕМІ               | External<br>memory<br>interface                   | SDMA                | External<br>memory<br>interface                                                                                                                                                                                                                                                                                                                                                                             | The EMI module provides access to external memory for the ARM and other masters. It is composed of the following main submodules:  M3IF—provides arbitration between multiple masters requesting access to the external memory.  SDRAM CTRL—interfaces to mDDR, DDR2 (4-bank architecture type), and SDR interfaces.  NANDFC—provides an interface to NAND Flash memories.  WEIM—interfaces to NOR Flash and PSRAM. |

| EPIT(2)           | Enhanced<br>periodic<br>interrupt timer           | ARM                 | Timer<br>peripherals                                                                                                                                                                                                                                                                                                                                                                                        | Each EPIT is a 32-bit "set-and-forget" timer that starts counting after the EPIT is enabled by software. It is capable of providing precise interrupts at regular intervals with minimal processor intervention. It has a 12-bit prescaler to adjust the input clock frequency to the required time setting for the interrupts, and the counter value can be programmed on the fly.                                 |

**Table 4. Digital and Analog Modules (continued)**

| Block<br>Mnemonic | Block Name                                    | Domain <sup>1</sup> | Subsystem                 | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-----------------------------------------------|---------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ESAI              | Enhanced<br>serial audio<br>interface         | SDMA                | Connectivity peripherals  | The enhanced serial audio interface (ESAI) provides a full-duplex serial port for serial communication with a variety of serial devices, including industry-standard codecs, SPDIF transceivers, and other DSPs. The ESAI consists of independent transmitter and receiver sections, each section with its own clock generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| eSDHCv2<br>(3)    | Enhanced<br>secure digital<br>host controller | ARM                 | Connectivity peripherals  | The eSDHCv2 consists of four main modules: CE-ATA, MMC, SD and SDIO. CE-ATA is a hard drive interface that is optimized for embedded applications of storage. The MultiMediaCard (MMC) is a universal, low-cost, data storage and communication media to applications such as electronic toys, organizers, PDAs, and smart phones. The secure digital (SD) card is an evolution of MMC and is specifically designed to meet the security, capacity, performance, and environment requirements inherent in emerging audio and video consumer electronic devices. SD cards are categorized into Memory and I/O. A memory card enables a copyright protection mechanism that complies with the SDMI security standard. SDIO cards provide high-speed data I/O (such as wireless LAN via SDIO interface) with low power consumption.  Note: CE-ATA is not available for the MCIMX351. |

| FEC               | Ethernet                                      | SDMA                | Connectivity peripherals  | The Ethernet media access controller (MAC) is designed to support both 10 and 100 Mbps Ethernet/IEEE 802.3 networks. An external transceiver interface and transceiver function are required to complete the interface to the media                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GPIO(3)           | General<br>purpose I/O<br>modules             | ARM                 | Pins                      | Used for general purpose input/output to external ICs. Each GPIO module supports 32 bits of I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GPT               | General<br>purpose timers                     | ARM                 | Timer<br>peripherals      | Each GPT is a 32-bit free-running or set-and-forget mode timer with a programmable prescaler and compare and capture registers. A timer counter value can be captured using an external event and can be configured to trigger a capture event on either the leading or trailing edges of an input pulse. When the timer is configured to operate in set-and-forget mode, it is capable of providing precise interrupts at regular intervals with minimal processor intervention. The counter has output compare logic to provide the status and interrupt at comparison. This timer can be configured to run either on an external clock or on an internal clock.                                                                                                                                                                                                                |

| GPU2D             | Graphics<br>processing unit<br>2Dv1           | ARM                 | Multimedia<br>peripherals | This module accelerates OpenVG and GDI graphics.  Note: Not available for the MCIMX351.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

**Table 4. Digital and Analog Modules (continued)**

| Block<br>Mnemonic   | Block Name                                  | Domain <sup>1</sup> | Subsystem                          | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|---------------------------------------------|---------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sup>2</sup> C(3) | I <sup>2</sup> C module                     | ARM                 | ARM1136<br>platform<br>peripherals | Inter-integrated circuit (I <sup>2</sup> C) is an industry-standard, bidirectional serial bus that provides a simple, efficient method of data exchange, minimizing the interconnection between devices. I <sup>2</sup> C is suitable for applications requiring occasional communications over a short distance among many devices. The interface operates at up to 100 kbps with maximum bus loading and timing. The I <sup>2</sup> C system is a true multiple-master bus, with arbitration and collision detection that prevent data corruption if multiple devices attempt to control the bus simultaneously. This feature supports complex applications with multiprocessor control and can be used for rapid testing and alignment of end products through external connections to an assembly-line computer. |

| IIM                 | IC identification module                    | ARM                 | Security<br>modules                | The IIM provides the primary user-visible mechanism for interfacing with on-chip fuse elements. Among the uses for the fuses are unique chip identifiers, mask revision numbers, cryptographic keys, and various control signals requiring a fixed value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IOMUX               | External<br>signals and pin<br>multiplexing | ARM                 | Pins                               | Each I/O multiplexer provides a flexible, scalable multiplexing solution with the following features:  Up to eight output sources multiplexed per pin  Up to four destinations for each input pin  Unselected input paths held at constant levels for reduced power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| IPUv1               | Image processing unit                       | ARM                 | Multimedia<br>peripherals          | <ul> <li>The IPU supports video and graphics processing functions. It also provides the interface for image sensors and displays. The IPU performs the following main functions:</li> <li>Preprocessing of data from the sensor or from the external system memory</li> <li>Postprocessing of data from the external system memory</li> <li>Post-filtering of data from the system memory with support of the MPEG-4 (both deblocking and deringing) and H.264 post-filtering algorithms</li> <li>Displaying video and graphics on a synchronous (dumb or memory-less) display</li> <li>Displaying video and graphics on an asynchronous (smart) display</li> <li>Transferring data between IPU sub-modules and to/from the system memory with flexible pixel reformatting</li> </ul>                                |

| KPP                 | Keypin port                                 | ARM                 | Connectivity peripherals           | Can be used for either keypin matrix scanning or general purpose I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MLB                 | Media local<br>bus                          | ARM                 | Connectivity peripherals           | The MLB is designed to interface to an automotive MOST ring.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OSCAUD              | OSC audio<br>reference<br>oscillator        | Analog              | Clock                              | The OSCAUDIO oscillator provides a stable frequency reference for the PLLs. This oscillator is designed to work in conjunction with an external 24.576-MHz crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

**Table 4. Digital and Analog Modules (continued)**

| Block<br>Mnemonic | Block Name                                             | Domain <sup>1</sup>                 | Subsystem                          | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-------------------|--------------------------------------------------------|-------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OSC24M            | OSC24M<br>24-MHz<br>reference<br>oscillator            | Analog                              | Clock                              | The signal from the external 24-MHz crystal is the source of the CLK24M signal fed into USB PHY as the reference clock and to the real time clock (RTC).                                                                                                                                                                                                                                                                                                                                                                             |  |

| MPLL<br>PPLL      | Digital<br>phase-locked<br>loops                       | SDMA                                | Clocks                             | DPLLs are used to generate the clocks:  MCU PLL (MPLL)—programmable  Peripheral PLL (PPLL)—programmable                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| PWM               | Pulse-width<br>modulator                               | ARM                                 | ARM1136<br>platform<br>peripherals | The pulse-width modulator (PWM) is optimized to generate sound from stored sample audio images; it can also generate tones.                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| RTC               | Real-time<br>clock                                     | ARM                                 | Clocks                             | Provides the ARM1136 platform with a clock function (days, hours, minutes, seconds) and includes alarm, sampling timer, and minute stopwatch capabilities.                                                                                                                                                                                                                                                                                                                                                                           |  |

| SDMA              | Smart DMA<br>engine                                    | SDMA                                | System controls                    | The SDMA provides DMA capabilities inside the processor. It is a shared module that implements 32 DMA channels and has an interface to connect to the ARM1136 platform subsystem, EMI interface, and the peripherals.                                                                                                                                                                                                                                                                                                                |  |

| SJC               | Secure JTAG controller                                 | ARM                                 | Pins                               | The secure JTAG controller (SJC) provides debug and test control with maximum security.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| SPBA              | SDMA<br>peripheral bus<br>arbiter                      | SDMA                                | System controls                    | The SPBA controls access to the SDMA peripherals. It supports shared peripheral ownership and access rights to an owned peripheral.                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| S/PDIF            | Serial audio interface                                 | SDMA                                | Connectivity peripherals           | Sony/Philips digital transceiver interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| SSI(2)            | Synchronous<br>serial interface                        | SDMA,<br>ARM(2)                     | Connectivity peripherals           | The SSI is a full-duplex serial port that allows the processor connected to it to communicate with a variety of serial protocols, including the Freescale Semiconductor SPI standard and the I <sup>2</sup> C sound (I <sup>2</sup> S) bus standard. The SSIs interface to the AUDMUX for flexible audio routing.                                                                                                                                                                                                                    |  |

| UART(3)           | Universal<br>asynchronous<br>receiver/trans<br>mitters | ARM<br>(UART1,2)<br>SDMA<br>(UART3) | Connectivity peripherals           | Each UART provides serial communication capability with external devices through an RS-232 cable using the standard RS-232 non-return-to-zero (NRZ) encoding format. Each module transmits and receives characters containing either 7 or 8 bits (program-selectable). Each UART can also provide low-speed IrDA compatibility through the use of external circuitry that converts infrared signals to electrical signals (for reception) or transforms electrical signals to signals that drive an infrared LED (for transmission). |  |

**Table 4. Digital and Analog Modules (continued)**

| Block<br>Mnemonic | Block Name                  | Domain <sup>1</sup> | Subsystem                | Brief Description                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|-----------------------------|---------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USBOH             | High-speed<br>USB on-the-go | SDMA                | Connectivity peripherals | The USB module provides high performance USB on-the-go (OTG) functionality (up to 480 Mbps), compliant with the USB 2.0 specification, the OTG supplement, and the ULPI 1.0 low pin count specification. The module has DMA capabilities handling data transfer between internal buffers and system memory.                                                                              |

| WDOG              | Watchdog<br>modules         | ARM                 | Timer<br>peripherals     | Each module protects against system failures by providing a method of escaping from unexpected events or programming errors. Once activated, the timer must be serviced by software on a periodic basis. If servicing does not take place, the watchdog times out and then either asserts a system reset signal or an interrupt request signal, depending on the software configuration. |

<sup>&</sup>lt;sup>1</sup> ARM = ARM1136 platform, SDMA = SDMA platform

## 3 Signal Descriptions: Special Function Related Pins

Some special functional requirements are supported in the device. The details about these special functions and the corresponding pin names are listed in Table 5.

**Table 5. Special Function Related Pins**

| Function Name             | Pin Name   | Mux Mode | Detailed Description                                                                                                                                                                                                                                                   |

|---------------------------|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External ARM Clock        | EXT_ARMCLK | ALT0     | External clock input for ARM clock.                                                                                                                                                                                                                                    |

| External Peripheral Clock | I2C1_CLK   | ALT6     | External peripheral clock source.                                                                                                                                                                                                                                      |

| External 32-kHz Clock     | CAPTURE    | ALT4     | External clock input of 32 kHz, used when the internal                                                                                                                                                                                                                 |

|                           | CSPI1_SS1  | ALT2     | 24M Oscillator is powered off, which could be configured either from CAPTURE or CSPI1_SS1.                                                                                                                                                                             |

| Clock Out                 | CLKO       | ALT0     | Clock-out pin from CCM, clock source is controllable and can also be used for debug.                                                                                                                                                                                   |

| Power Ready               | GPIO1_0    | ALT1     | PMIC power-ready signal, which can be configured                                                                                                                                                                                                                       |

|                           | TX1        | ALT1     | either from GPIO1_0 or TX1.                                                                                                                                                                                                                                            |

| Tamper Detect             | GPIO1_1    | ALT6     | Tamper-detect logic is used to issue a security violation. This logic is activated if the tamper-detect input is asserted. Tamper-detect logic is enabled by the bit of IOMUXC_GPRA[2]. After enabling the logic, it is impossible to disable it until the next reset. |

### 4 Electrical Characteristics

The following sections provide the device-level and module-level electrical characteristics for the i.MX35 processor.

### 4.1 i.MX35 Chip-Level Conditions

This section provides the device-level electrical characteristics for the IC. See Table 6 for a quick reference to the individual tables and sections.

Table 6. i.MX35 Chip-Level Conditions

| Characteristics          | Table/Location     |

|--------------------------|--------------------|

| Absolute Maximum Ratings | Table 7 on page 13 |

| i.MX35 Operating Ranges  | Table 8 on page 14 |

| Interface Frequency      | Table 9 on page 15 |

#### **CAUTION**

Stresses beyond those listed in Table 7 may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in Table 8 is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

**Table 7. Absolute Maximum Ratings**

| Parameter                 | Symbol                          | Min. | Max.              | Units |

|---------------------------|---------------------------------|------|-------------------|-------|

| Supply voltage (core)     | VDD <sub>max</sub> <sup>1</sup> | -0.5 | 1.47              | V     |

| Supply voltage (I/O)      | NVCC <sub>max</sub>             | -0.5 | 3.6               | V     |

| Input voltage range       | V <sub>Imax</sub>               | -0.5 | 3.6               | V     |

| Storage temperature       | T <sub>storage</sub>            | -40  | 125               | °C    |

| ESD damage immunity:      | V <sub>esd</sub>                |      |                   | V     |

| Human Body Model (HBM)    |                                 | _    | 2000 <sup>2</sup> |       |

| Charge Device Model (CDM) |                                 | _    | 500 <sup>3</sup>  |       |

<sup>1</sup> VDD is also known as QVCC.

<sup>&</sup>lt;sup>2</sup> HBM ESD classification level according to the AEC-Q100-002 standard

<sup>&</sup>lt;sup>3</sup> Corner pins max. 750 V

### 4.1.1 i.MX35 Operating Ranges

Table 8 provides the recommended operating ranges. The term NVCC in this section refers to the associated supply rail of an input or output.

Table 8. i.MX35 Operating Ranges

| Parameter                                    | Symbol                | Min. | Typical | Max. | Units |

|----------------------------------------------|-----------------------|------|---------|------|-------|

| Core Operating Voltage<br>0 < fARM < 400 MHz | $V_{DD}$              | 1.22 | _       | 1.47 | V     |

| Core Operating Voltage<br>0 < fARM < 532 MHz |                       | 1.33 | _       | 1.47 | V     |

| State Retention Voltage                      |                       | 1    | _       | _    | V     |

| EMI <sup>1</sup>                             | NVCC_EMI1,2,3         | 1.7  | _       | 3.6  | V     |

| WTDG, Timer, CCM, CSPI1                      | NVCC_CRM              | 1.75 | _       | 3.6  | V     |

| NANDF                                        | NVCC_NANDF            | 1.75 | _       | 3.6  | V     |

| ATA, USB generic                             | NVCC_ATA              | 1.75 | _       | 3.6  | V     |

| eSDHC1                                       | NVCC_SDIO             | 1.75 | _       | 3.6  | V     |

| CSI, SDIO2                                   | NVCC_CSI              | 1.75 | _       | 3.6  | V     |

| JTAG                                         | NVCC_JTAG             | 1.75 | _       | 3.6  | V     |

| LCDC, TTM, I2C1                              | NVCC_LCDC             | 1.75 | _       | 3.6  | V     |

| I2Sx2,ESAI, I2C2, UART2, UART1, FEC          | NVCC_MISC             | 1.75 | _       | 3.6  | V     |

| MLB                                          | NVCC_MLB <sup>2</sup> | 1.75 | _       | 3.6  | V     |

| USB OTG PHY                                  | PHY1_VDDA             | 3.17 | 3.3     | 3.43 | V     |

| USB OTG PHY                                  | USBPHY1_VDDA_BIAS     | 3.17 | 3.3     | 3.43 | V     |

| USB OTG PHY                                  | USBPHY1_UPLLVDD       | 3.17 | 3.3     | 3.43 | V     |

| USB HOST PHY                                 | PHY2_VDD              | 3.0  | 3.3     | 3.6  | V     |

| OSC24M                                       | OSC24M_VDD            | 3.0  | 3.3     | 3.6  | V     |

| OSC_AUDIO                                    | OSC_AUDIO_VDD         | 3.0  | 3.3     | 3.6  | V     |

| MPLL                                         | MVDD                  | 1.4  | _       | 1.65 | V     |

| PPLL                                         | PVDD                  | 1.4  | _       | 1.65 | V     |

| Fusebox program supply voltage               | FUSE_VDD <sup>3</sup> | 3.0  | 3.6     | 3.6  | V     |

| Operating ambient temperature range          | ТА                    | -40  | _       | 85   | °C    |

| Junction temperature range                   | TJ                    | -40  | _       | 105  | °C    |

<sup>&</sup>lt;sup>1</sup> EMI I/O interface power supply should be set up according to external memory. For example, if using SDRAM then NVCC\_EMI1,2,3 should all be set at 3.3 V (typ.). If using MDDR or DDR2, NVC\_EMI1,2,3 must be set at 1.8 V (typ.).

MLB interface I/O pads can be programmed to function as GPIO by setting NVCC\_MLB to 1.8 or 3.3 V, but if used as MLB pads, NVCC\_MLB must be set to 2.5 V in order to be compliant with external MOST devices. NVCC\_MLB may be left floating.

The Fusebox read supply is connected to supply of the full speed USB PHY. FUSE\_VDD is only used for programming. It is recommended that FUSE\_VDD be connected to ground when not being used for programming. FUSE\_VDD should be supplied by following the power up sequence given in Section 4.3.1, "Powering Up."

### 4.1.2 Interface Frequency Limits

Table 9 provides information on interface frequency limits.

#### **Table 9. Interface Frequency**

| ID | Parameter          | Symbol            | Min. | Тур. | Max. | Units |

|----|--------------------|-------------------|------|------|------|-------|

| 1  | JTAG TCK Frequency | f <sub>JTAG</sub> | DC   | 5    | 10   | MHz   |

### 4.2 Power Modes

Table 10 provides descriptions of the power modes of the i.MX35 processor.

Table 10. i.MX35 Power Modes

| Power<br>Mode | Description                                                                                                                                                                                                                                                                                                                                                        | QVCC (ARM/L2<br>Peripheral) |        | MVDD/PVDD |       | OSC24M_VDD<br>OSC_AUDO_VDD |      |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------|-----------|-------|----------------------------|------|

| Wiode         |                                                                                                                                                                                                                                                                                                                                                                    | Тур.                        | Max.   | Тур.      | Max.  | Тур.                       | Max. |

| Wait          | VDD1,2,3,4 = 1.1 V (min.) ARM is in wait for interrupt mode. MAX is active. L2 cache is kept powered. MCU PLL is on (400 MHz) PER PLL is off (can be configured) (default: 300 MHz) Module clocks are gated off (can be configured by CGR register). OSC 24M is ON. OSC audio is off (can be configured). RNGC internal osc is off.                                | 16 mA                       | 170 mA | 7.2 mA    | 14 mA | 1.2 mA                     | 3 mA |

| Doze          | VDD1,2,3,4 = 1.1 V (min.) ARM is in wait for interrupt mode. MAX is halted. L2 cache is kept powered. L2 cache control logic off. AWB enabled. MCU PLL is on(400 MHz) PER PLL is off (can be configured). (300 Mhz). Module clocks are gated off (can be configured by CGR register). OSC 24M is ON. OSC audio is off (can be configured) RNGC internal osc is off | 12.4 mA                     | 105 mA | 7.2 mA    | 14 mA | 1.2 mA                     | 3 mA |

Table 10. i.MX35 Power Modes (continued)

| Power<br>Mode | Description                                                                                                                                                                                                                                                        |        | QVCC (ARM/L2<br>Peripheral) |        | MVDD/PVDD |        | OSC24M_VDD<br>OSC_AUDO_VDD |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------|--------|-----------|--------|----------------------------|--|

| Mode          |                                                                                                                                                                                                                                                                    | Тур.   | Max.                        | Тур.   | Max.      | Тур.   | Max.                       |  |

| Stop          | VDD1,2,3,4 = 1.1 V (min.) ARM is in wait for interrupt mode. MAX is halted L2 cache is kept powered. L2 cache control logic off. AWB enabled. MCU PLL is off. PER PLL is off. All clocks are gated off. OSC 24 MHz is on OSC audio is off RNGC internal osc is off | 1.1 mA | 77 mA                       | 400 μΑ | 2.2 mA    | 1.2 mA | 2.2 mA                     |  |

| Static        | VDD1,2,3,4 = 1.1 V (min.) ARM is in wait for interrupt mode. MAX is halted L2 cache is kept powered. L2 cache control logic off. AWB enabled. MCU PLL is off. PER PLL is off. All clocks are gated off. OSC 24MHz is on OSC audio is off RNGC internal osc is off  | 820 µA | 72 mA                       | 50 μA  | 1.7 mA    | 24 μΑ  | 35 µA                      |  |

**Note:** Typical column: TA = 25 °C **Note:** Maximum column: TA = 85 °C

### 4.3 Supply Power-Up/Power-Down Requirements and Restrictions

This section provides power-up and power-down sequence guidelines for the i.MX35 processor.

#### **CAUTION**

Any i.MX35 board design must comply with the power-up and power-down sequence guidelines as described in this section to guarantee reliable operation of the device. Any deviation from these sequences can result in irreversible damage to the i.MX35 processor (worst-case scenario).

#### **NOTE**

Deviation from these sequences may also result in one or more of the following:

- Excessive current during power-up phase

- Prevent the device from booting

- Programming of unprogrammed fuses

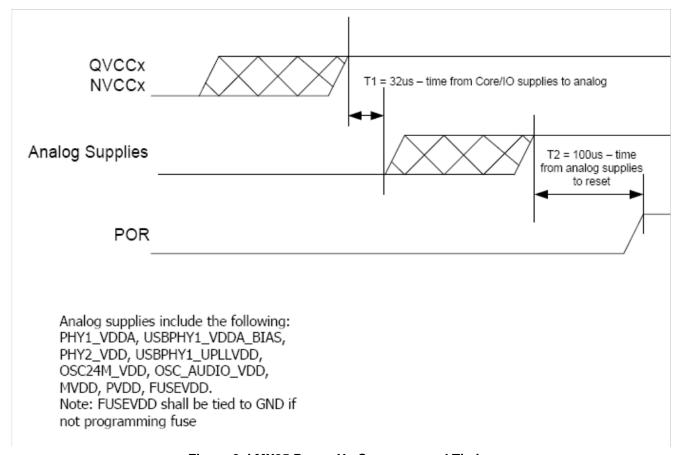

#### 4.3.1 Powering Up

The power-up sequence should be completed as follows:

- 1. Assert Power on Reset ( $\overline{POR}$ ).

- 2. Turn on digital logic domain and IO power supply: VDDn, NVCCx

- 3. Wait until VDDn and NVCCx power supplies are stable + 32  $\mu$ s.

- 4. Turn on all other power supplies: PHY1\_VDDA, USBPHY1\_VDDA\_BIAS, PHY2\_VDD, USBPHY1\_UPLLVDD, OSC24M\_VDD, OSC\_AUDIO\_VDD, MVDD, PVDD, FUSEVDD. (Always FUSE\_VDD should be connected to ground, except when eFuses are to be programmed.)

- 5. Wait until PHY1\_VDDA, USBPHY1\_VDDA\_BIAS, PHY2\_VDD, USBPHY1\_UPLLVDD, OSC24M\_VDD, OSC\_AUDIO\_VDD, MVDD, PVDD, (FUSEVDD, optional). Power supplies are stable + 100 μs.

- 6. Deassert the  $\overline{POR}$  signal.

Figure 2 shows the power-up sequence and timing.

Figure 2. i.MX35 Power-Up Sequence and Timing

### 4.3.2 Powering Down

The power-up sequence in reverse order is recommended for powering down. However, all power supplies can be shut down at the same time.

### 4.4 Reset Timing

There are two ways of resetting the i.MX35 using external pins:

- Power On Reset (using the POR\_B pin)

- System Reset (using the RESET\_IN\_B pin)

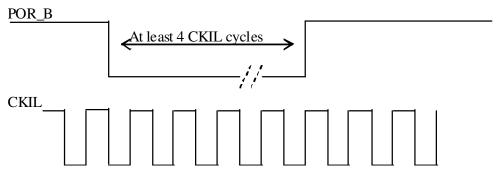

#### 4.4.1 Power On Reset

POR\_B is normally connected to a power management integrated circuit (PMIC). The PMIC asserts POR\_B while the power supplies are turned on and negates POR\_B after the power up sequence is finished. See Figure 2.

Assuming the i.MX35 chip is already fully powered; it is still possible to reset all of the modules to their default reset by asserting POR\_B for at least 4 CKIL cycles and later de-asserting POR\_B. This method of resetting the i.MX35 can also be supported by tying the POR\_B and RESET\_IN\_B pins together.

Figure 3. Timing Between POR\_B and CKIL for Complete Reset of i.MX35

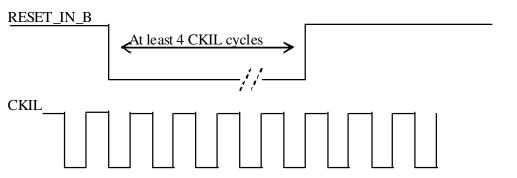

#### 4.4.2 System Reset

System reset can be achieved by asserting RESET\_IN\_B for at least 4 CKIL cycles and later negating RESET\_IN\_B. The following modules are not reset upon system reset: RTC, PLLs, CCM, and IIM. POR\_B pin must be deasserted all the time.

Figure 4. Timing Between RESET\_IN\_B and CKIL for i.MX35 System Reboot

#### 4.5 Power Characteristics

The table shows values representing maximum current numbers for the i.MX35 under worst case voltage and temperature conditions. These values are derived from the i.MX35 with core clock speeds up to 532 MHz. Common supplies have been bundled according to the i.MX35 power-up sequence requirements. Peak numbers are provided for system designers so that the i.MX35 power supply requirements will be satisfied during startup and transient conditions. Freescale recommends that system current measurements be taken with customer-specific use-cases to reflect normal operating conditions in the end system.

**Table 11. Power Consumption**

| Power Supply                                                                       | Voltage (V) | Max Current (mA) |

|------------------------------------------------------------------------------------|-------------|------------------|

| QVCC                                                                               | 1.47        | 400              |

| MVDD, PVDD                                                                         | 1.65        | 20               |

| NVCC_EMI1, NVCC_EMI2, NVCC_EMI3, NVCC_LCDC, NVCC_NFC                               | 1.9         | 90               |

| FUSE_VDD <sup>1</sup>                                                              | 3.6         | 62               |

| NVCC_MISC, NVCC_CSI, NVCC_SDIO, NVCC_CRM, NVCC_ATA, NVCC_MLB, NVCC_JTAG            | 3.6         | 60               |

| OSC24M_VDD, OSC_AUDIO_VDD, PHY1_VDDA, PHY2_VDD, USBPHY1_UPLLVDD, USBPHY1_VDDA_BIAS | 3.6         | 25               |

<sup>&</sup>lt;sup>1</sup> This rail is connected to ground; it only needs a voltage if eFuses are to be programmed. FUSE\_VDD should be supplied by following the power up sequence given in Section 4.3.1, "Powering Up."

The method for obtaining max current is as follows:

- 1. Measure worst case power consumption on individual rails using directed test on i.MX35.