Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Freescale Semiconductor Inc.

Data Sheet: Technical Data

Document Number: IMX6DQAEC

Rev. 4, 07/2015

MCIMX6QxAxxxxC MCIMX6QxAxxxxD MCIMX6DxAxxxxC MCIMX6DxAxxxxD

# i.MX 6Dual/6Quad Automotive and Infotainment Applications Processors

# Package Information Case FCPBGA 21 x 21 mm, 0.8 mm pitch

#### Ordering Information

See Table 1

# 1 Introduction

The i.MX 6Dual and i.MX 6Quad automotive and infotainment processors represent Freescale Semiconductor's latest achievement in integrated multimedia applications processors. These processors are part of a growing family of multimedia-focused products that offer high-performance processing with a high degree of functional integration. These processors target the needs of the growing aut1omotive infotainment, telematics, HMI, and display-based cluster markets. The i.MX 6Dual/6Quad processors feature the Freescale advanced implementation of the quad ARM® Cortex®-A9 core, which operates at speeds up to 1 GHz. They include 2D and 3D graphics processors, 3D 1080p video processing, and integrated power management. Each processor provides a 64-bit DDR3/LVDDR3/LPDDR2-1066 memory interface and a number of other interfaces for connecting peripherals, such as WLAN, Bluetooth<sup>®</sup>, GPS, hard drive, displays, and camera sensors.

| 1 | Intro | Introduction                                      |  |  |  |  |  |

|---|-------|---------------------------------------------------|--|--|--|--|--|

|   | 1.1   | Ordering Information                              |  |  |  |  |  |

|   | 1.2   | Features                                          |  |  |  |  |  |

|   | 1.3   | Updated Signal Naming Convention 8                |  |  |  |  |  |

| 2 | Archi | tectural Overview                                 |  |  |  |  |  |

|   | 2.1   | Block Diagram                                     |  |  |  |  |  |

| 3 | Modu  | ıles List                                         |  |  |  |  |  |

|   | 3.1   | Special Signal Considerations                     |  |  |  |  |  |

|   | 3.2   | Recommended Connections for Unused Analog         |  |  |  |  |  |

|   |       | Interfaces                                        |  |  |  |  |  |

| 4 | Elect | rical Characteristics                             |  |  |  |  |  |

|   | 4.1   | Chip-Level Conditions                             |  |  |  |  |  |

|   | 4.2   | Power Supplies Requirements and Restrictions 32   |  |  |  |  |  |

|   | 4.3   | Integrated LDO Voltage Regulator Parameters 33    |  |  |  |  |  |

|   | 4.4   | PLL Electrical Characteristics                    |  |  |  |  |  |

|   | 4.5   | On-Chip Oscillators                               |  |  |  |  |  |

|   | 4.6   | I/O DC Parameters                                 |  |  |  |  |  |

|   | 4.7   | I/O AC Parameters                                 |  |  |  |  |  |

|   | 4.8   | Output Buffer Impedance Parameters 47             |  |  |  |  |  |

|   | 4.9   | System Modules Timing 51                          |  |  |  |  |  |

|   | 4.10  | General-Purpose Media Interface (GPMI) Timing. 66 |  |  |  |  |  |

|   |       | External Peripheral Interface Parameters 75       |  |  |  |  |  |

| 5 | Boot  | Mode Configuration                                |  |  |  |  |  |

|   | 5.1   | Boot Mode Configuration Pins                      |  |  |  |  |  |

|   | 5.2   | Boot Devices Interfaces Allocation                |  |  |  |  |  |

| 6 |       | age Information and Contact Assignments 144       |  |  |  |  |  |

|   | 6.1   | Updated Signal Naming Convention 144              |  |  |  |  |  |

|   | 6.2   | 21 x 21 mm Package Information 144                |  |  |  |  |  |

| 7 | Revis | sion History                                      |  |  |  |  |  |

2

#### Introduction

The i.MX 6Dual/6Quad processors are specifically useful for applications such as the following:

- Automotive navigation and entertainment

- Graphics rendering for Human Machine Interfaces (HMI)

- High-performance speech processing with large databases

- Audio playback

The i.MX 6Dual/6Quad processors offers numerous advanced features, such as:

- Multilevel memory system—The multilevel memory system of each processor is based on the L1 instruction and data caches, L2 cache, and internal and external memory. The processors support many types of external memory devices, including DDR3, low voltage DDR3, LPDDR2, NOR Flash, PSRAM, cellular RAM, NAND Flash (MLC and SLC), OneNAND<sup>TM</sup>, and managed NAND, including eMMC up to rev 4.4/4.41.

- Smart speed technology—The processors have power management throughout the device that enables the rich suite of multimedia features and peripherals to consume minimum power in both active and various low power modes. Smart speed technology enables the designer to deliver a feature-rich product, requiring levels of power far lower than industry expectations.

- Dynamic voltage and frequency scaling—The processors improve the power efficiency of devices by scaling the voltage and frequency to optimize performance.

- Multimedia powerhouse—The multimedia performance of each processor is enhanced by a multilevel cache system, Neon<sup>®</sup> MPE (Media Processor Engine) co-processor, a multi-standard hardware video codec, 2 autonomous and independent image processing units (IPU), and a programmable smart DMA (SDMA) controller.

- Powerful graphics acceleration—Each processor provides three independent, integrated graphics processing units: an OpenGL<sup>®</sup> ES 2.0 3D graphics accelerator with four shaders (up to 200 MTri/s and OpenCL support), 2D graphics accelerator, and dedicated OpenVG<sup>TM</sup> 1.1 accelerator.

- Interface flexibility—Each processor supports connections to a variety of interfaces: LCD controller for up to four displays (including parallel display, HDMI1.4, MIPI display, and LVDS display), dual CMOS sensor interface (parallel or through MIPI), high-speed USB on-the-go with PHY, high-speed USB host with PHY, multiple expansion card ports (high-speed MMC/SDIO host and other), 10/100/1000 Mbps Gigabit Ethernet controller, and a variety of other popular interfaces (such as UART, I<sup>2</sup>C, and I<sup>2</sup>S serial audio, SATA-II, and PCIe-II).

- Automotive environment support—Each processor includes interfaces, such as two CAN ports, an MLB150/50 port, an ESAI audio interface, and an asynchronous sample rate converter for multichannel/multisource audio.

- Advanced security—The processors deliver hardware-enabled security features that enable secure

e-commerce, digital rights management (DRM), information encryption, secure boot, and secure

software downloads. The security features are discussed in detail in the i.MX 6Dual/6Quad

security reference manual (IMX6DQ6SDLSRM).

- Integrated power management—The processors integrate linear regulators and internally generate voltage levels for different domains. This significantly simplifies system power management structure.

# 1.1 Ordering Information

Table 1shows examples of orderable part numbers covered by this data sheet. This table does not include all possible orderable part numbers. The latest part numbers are available on freescale.com/imx6series. If your desired part number is not listed in the table, or you have questions about available parts, see freescale.com/imx6series or contact your Freescale representative.

**Table 1. Example Orderable Part Numbers**

| Part Number     | Quad/Dual CPU | Options          | Speed <sup>1</sup><br>Grade | Temperature<br>Grade | Package                                         |

|-----------------|---------------|------------------|-----------------------------|----------------------|-------------------------------------------------|

| MCIMX6Q6AVT10AC | i.MX 6Quad    | With VPU, GPU    | 1 GHz                       | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6Q6AVT10AD | i.MX 6Quad    | With VPU, GPU    | 1 GHz                       | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6Q4AVT10AC | i.MX 6Quad    | With GPU, no VPU | 1 GHz                       | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6Q4AVT10AD | i.MX 6Quad    | With GPU, no VPU | 1 GHz                       | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6Q6AVT08AC | i.MX 6Quad    | With VPU, GPU    | 852 MHz                     | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6Q6AVT08AD | i.MX 6Quad    | With VPU, GPU    | 852 MHz                     | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6Q4AVT08AC | i.MX 6Quad    | With GPU, no VPU | 852 MHz                     | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6Q4AVT08AD | i.MX 6Quad    | With GPU, no VPU | 852 MHz                     | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6D6AVT10AC | i.MX 6Dual    | With VPU, GPU    | 1 GHz                       | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6D6AVT10AD | i.MX 6Dual    | With VPU, GPU    | 1 GHz                       | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6D4AVT10AC | i.MX 6Dual    | With GPU, no VPU | 1 GHz                       | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6D4AVT10AD | i.MX 6Dual    | With GPU, no VPU | 1 GHz                       | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6D6AVT08AC | i.MX 6Dual    | With VPU, GPU    | 852 MHz                     | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6D6AVT08AD | i.MX 6Dual    | With VPU, GPU    | 852 MHz                     | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6D4AVT08AC | i.MX 6Dual    | With GPU, no VPU | 852 MHz                     | Automotive1          | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

| MCIMX6D4AVT08AD | i.MX 6Dual    | With GPU, no VPU | 852 MHz                     | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, FCPBGA (lidded) |

<sup>1</sup> If a 24 MHz input clock is used (required for USB), the maximum SoC speed is limited to 996 MHz.

#### Introduction

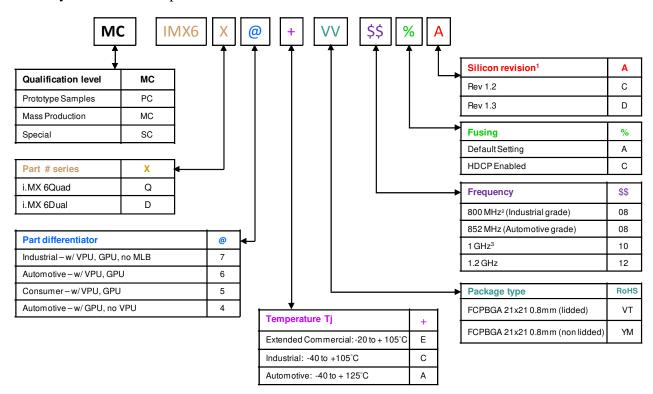

Figure 1 describes the part number nomenclature to identify the characteristics of the specific part number you have (for example, cores, frequency, temperature grade, fuse options, silicon revision). Figure 1 applies to the i.MX 6Dual/6Quad.

The two characteristics that identify which data sheet a specific part applies to are the part number series field and the temperature grade (junction) field:

- The i.MX 6Dual/6Quad Automotive and Infotainment Applications Processors data sheet (IMX6DQAEC) covers parts listed with "A (Automotive temp)"

- The i.MX 6Dual/6Quad Applications Processors for Consumer Products data sheet (IMX6DQCEC) covers parts listed with "D (Commercial temp)" or "E (Extended Commercial temp)"

- The i.MX 6Dual/6Quad Applications Processors for Industrial Products data sheet (IMX6DQIEC) covers parts listed with "C (Industrial temp)"

Ensure that you have the right data sheet for your specific part by checking the temperature grade (junction) field and matching it to the right data sheet. If you have questions, see freescale.com/imx6series or contact your Freescale representative.

<sup>1.</sup> See the freescale.com\imx6series Web page for latest information on the available silicon revision.

Figure 1. Part Number Nomenclature—i.MX 6Quad and i.MX 6Dual

<sup>2.</sup> If a 24 MHz input clock is used (required for USB), the maximum SoC speed is limited to 792 MHz.

<sup>3.</sup> If a 24 MHz input clock is used (required for USB), the maximum SoC speed is limited to 996 MHz.

## 1.2 Features

The i.MX 6Dual/6Quad processors are based on ARM Cortex-A9 MPCore platform, which has the following features:

- ARM Cortex-A9 MPCore 4xCPU processor (with TrustZone®)

- The core configuration is symmetric, where each core includes:

- 32 KByte L1 Instruction Cache

- 32 KByte L1 Data Cache

- Private Timer and Watchdog

- Cortex-A9 NEON MPE (Media Processing Engine) Co-processor

## The ARM Cortex-A9 MPCore complex includes:

- General Interrupt Controller (GIC) with 128 interrupt support

- Global Timer

- Snoop Control Unit (SCU)

- 1 MB unified I/D L2 cache, shared by two/four cores

- Two Master AXI (64-bit) bus interfaces output of L2 cache

- Frequency of the core (including Neon and L1 cache) as per Table 6.

- NEON MPE coprocessor

- SIMD Media Processing Architecture

- NEON register file with 32x64-bit general-purpose registers

- NEON Integer execute pipeline (ALU, Shift, MAC)

- NEON dual, single-precision floating point execute pipeline (FADD, FMUL)

- NEON load/store and permute pipeline

The SoC-level memory system consists of the following additional components:

- Boot ROM, including HAB (96 KB)

- Internal multimedia / shared, fast access RAM (OCRAM, 256 KB)

- Secure/non-secure RAM (16 KB)

- External memory interfaces:

- 16-bit, 32-bit, and 64-bit DDR3-1066, LVDDR3-1066, and 1/2 LPDDR2-1066 channels, supporting DDR interleaving mode, for 2x32 LPDDR2-1066

- 8-bit NAND-Flash, including support for Raw MLC/SLC, 2 KB, 4 KB, and 8 KB page size, BA-NAND, PBA-NAND, LBA-NAND, OneNAND<sup>TM</sup> and others. BCH ECC up to 40 bit.

- 16/32-bit NOR Flash. All EIMv2 pins are muxed on other interfaces.

- 16/32-bit PSRAM, Cellular RAM

Each i.MX 6Dual/6Quad processor enables the following interfaces to external devices (some of them are muxed and not available simultaneously):

• Hard Disk Drives—SATA II, 3.0 Gbps

#### Introduction

- Displays—Total five interfaces available. Total raw pixel rate of all interfaces is up to 450 Mpixels/sec, 24 bpp. Up to four interfaces may be active in parallel.

- One Parallel 24-bit display port, up to 225 Mpixels/sec (for example, WUXGA at 60 Hz or dual HD1080 and WXGA at 60 Hz)

- LVDS serial ports—One port up to 165 Mpixels/sec or two ports up to 85 MP/sec (for example, WUXGA at 60 Hz) each

- HDMI 1.4 port

- MIPI/DSI, two lanes at 1 Gbps

### Camera sensors:

- Parallel Camera port (up to 20 bit and up to 240 MHz peak)

- MIPI CSI-2 serial camera port, supporting up to 1000 Mbps/lane in 1/2/3-lane mode and up to 800 Mbps/lane in 4-lane mode. The CSI-2 Receiver core can manage one clock lane and up to four data lanes. Each i.MX 6Dual/6Quad processor has four lanes.

## • Expansion cards:

- Four MMC/SD/SDIO card ports all supporting:

- 1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR-104 mode (104 MB/s max)

- 1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)

#### • USB:

- One High Speed (HS) USB 2.0 OTG (Up to 480 Mbps), with integrated HS USB PHY

- Three USB 2.0 (480 Mbps) hosts:

- One HS host with integrated High Speed PHY

- Two HS hosts with integrated HS-IC USB (High Speed Inter-Chip USB) PHY

- Expansion PCI Express port (PCIe) v2.0 one lane

- PCI Express (Gen 2.0) dual mode complex, supporting Root complex operations and Endpoint operations. Uses x1 PHY configuration.

- Miscellaneous IPs and interfaces:

- SSI block capable of supporting audio sample frequencies up to 192 kHz stereo inputs and outputs with I<sup>2</sup>S mode

- ESAI is capable of supporting audio sample frequencies up to 260kHz in I2S mode with 7.1 multi channel outputs

- Five UARTs, up to 5.0 Mbps each:

- Providing RS232 interface

- Supporting 9-bit RS485 multidrop mode

- One of the five UARTs (UART1) supports 8-wire while others four supports 4-wire. This is due to the SoC IOMUX limitation, since all UART IPs are identical.

- Five eCSPI (Enhanced CSPI)

- Three I2C, supporting 400 kbps

- Gigabit Ethernet Controller (IEEE1588 compliant), 10/100/1000<sup>1</sup> Mbps

- Four Pulse Width Modulators (PWM)

- System JTAG Controller (SJC)

- GPIO with interrupt capabilities

- 8x8 Key Pad Port (KPP)

- Sony Philips Digital Interconnect Format (SPDIF), Rx and Tx

- Two Controller Area Network (FlexCAN), 1 Mbps each

- Two Watchdog timers (WDOG)

- Audio MUX (AUDMUX)

- MLB (MediaLB) provides interface to MOST Networks (150 Mbps) with the option of DTCP cipher accelerator

The i.MX 6Dual/6Quad processors integrate advanced power management unit and controllers:

- Provide PMU, including LDO supplies, for on-chip resources

- Use Temperature Sensor for monitoring the die temperature

- Support DVFS techniques for low power modes

- Use Software State Retention and Power Gating for ARM and MPE

- Support various levels of system power modes

- Use flexible clock gating control scheme

The i.MX 6Dual/6Quad processors use dedicated hardware accelerators to meet the targeted multimedia performance. The use of hardware accelerators is a key factor in obtaining high performance at low power consumption numbers, while having the CPU core relatively free for performing other tasks.

The i.MX 6Dual/6Quad processors incorporate the following hardware accelerators:

- VPU—Video Processing Unit

- IPUv3H—Image Processing Unit version 3H (2 IPUs)

- GPU3Dv4—3D Graphics Processing Unit (OpenGL ES 2.0) version 4

- GPU2Dv2—2D Graphics Processing Unit (BitBlt)

- GPUVG—OpenVG 1.1 Graphics Processing Unit

- ASRC—Asynchronous Sample Rate Converter

Security functions are enabled and accelerated by the following hardware:

- ARM TrustZone including the TZ architecture (separation of interrupts, memory mapping, etc.)

- SJC—System JTAG Controller. Protecting JTAG from debug port attacks by regulating or blocking the access to the system debug features.

- CAAM—Cryptographic Acceleration and Assurance Module, containing 16 KB secure RAM and True and Pseudo Random Number Generator (NIST certified)

- SNVS—Secure Non-Volatile Storage, including Secure Real Time Clock

i.MX 6Dual/6Quad Automotive and Infotainment Applications Processors, Rev. 4, 07/2015

Freescale Semiconductor Inc.

<sup>1.</sup> The theoretical maximum performance of 1 Gbps ENET is limited to 470 Mbps (total for Tx and Rx) due to internal bus throughput limitations. The actual measured performance in optimized environment is up to 400 Mbps. For details, see the ERR004512 erratum in the i.MX 6Dual/6Quad errata document (IMX6DQCE).

#### Introduction

- CSU—Central Security Unit. Enhancement for the IC Identification Module (IIM). Will be configured during boot and by eFUSEs and will determine the security level operation mode as well as the TZ policy.

- A-HAB—Advanced High Assurance Boot—HABv4 with the new embedded enhancements: SHA-256, 2048-bit RSA key, version control mechanism, warm boot, CSU, and TZ initialization.

# 1.3 Updated Signal Naming Convention

The signal names of the i.MX 6 series of products have been standardized to better align the signal names within the family and across the documentation. Some of the benefits of these changes are as follows:

- The names are unique within the scope of an SoC and within the series of products

- Searches will return all occurrences of the named signal

- The names are consistent between i.MX 6 series products implementing the same modules

- The module instance is incorporated into the signal name

This change applies only to signal names. The original ball names have been preserved to prevent the need to change schematics, BSDL models, IBIS models, etc.

Throughout this document, the updated signal names are used except where referenced as a ball name (such as the Functional Contact Assignments table, Ball Map table, and so on). A master list of the signal name changes is in the document, *IMX 6 Series Signal Name Mapping* (EB792). This list can be used to map the signal names used in older documentation to the new standardized naming conventions.

# 2 Architectural Overview

The following subsections provide an architectural overview of the i.MX 6Dual/6Quad processor system.

# 2.1 Block Diagram

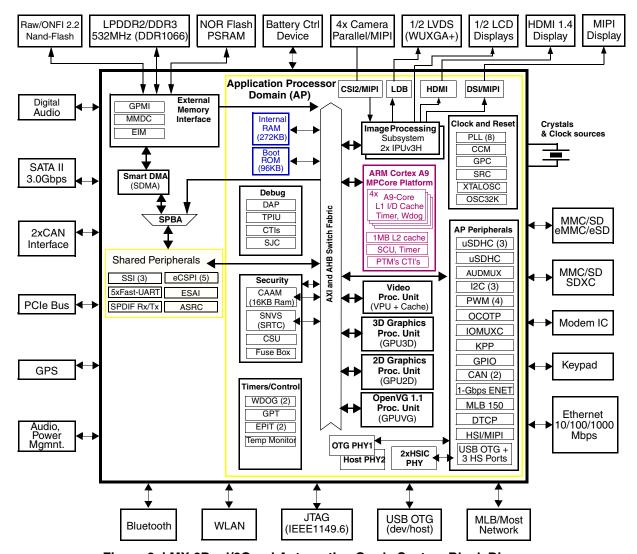

Figure 2 shows the functional modules in the i.MX 6Dual/6Quad processor system.

Figure 2. i.MX 6Dual/6Quad Automotive Grade System Block Diagram

### NOTE

The numbers in brackets indicate number of module instances. For example, PWM (4) indicates four separate PWM peripherals.

**Modules List**

# 3 Modules List

The i.MX 6Dual/6Quad processors contain a variety of digital and analog modules. Table 2 describes these modules in alphabetical order.

Table 2. i.MX 6Dual/6Quad Modules List

| Block<br>Mnemonic | Block Name                                                                          | Subsystem                               | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 512x8 Fuse<br>Box | Electrical Fuse Array                                                               | Security                                | Electrical Fuse Array. Enables to setup Boot Modes, Security Levels, Security Keys, and many other system parameters. The i.MX 6Dual/6Quad processors consist of 512x8-bit fuse box accessible through OCOTP_CTRL interface.                                                                                                                                                                                                                                                                                                                                  |

| APBH-DMA          | NAND Flash and<br>BCH ECC DMA<br>Controller                                         | System<br>Control<br>Peripherals        | DMA controller used for GPMI2 operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ARM               | ARM Platform                                                                        | ARM                                     | The ARM Cortex-A9 platform consists of 4x (four) Cortex-A9 cores version r2p10 and associated sub-blocks, including Level 2 Cache Controller, SCU (Snoop Control Unit), GIC (General Interrupt Controller), private timers, Watchdog, and CoreSight debug modules.                                                                                                                                                                                                                                                                                            |

| ASRC              | Asynchronous<br>Sample Rate<br>Converter                                            | Multimedia<br>Peripherals               | The Asynchronous Sample Rate Converter (ASRC) converts the sampling rate of a signal associated to an input clock into a signal associated to a different output clock. The ASRC supports concurrent sample rate conversion of up to 10 channels of about -120dB THD+N. The sample rate conversion of each channel is associated to a pair of incoming and outgoing sampling rates. The ASRC supports up to three sampling rate pairs.                                                                                                                        |

| AUDMUX            | Digital Audio Mux                                                                   | Multimedia<br>Peripherals               | The AUDMUX is a programmable interconnect for voice, audio, and synchronous data routing between host serial interfaces (for example, SSI1, SSI2, and SSI3) and peripheral serial interfaces (audio and voice codecs). The AUDMUX has seven ports with identical functionality and programming models. A desired connectivity is achieved by configuring two or more AUDMUX ports.                                                                                                                                                                            |

| BCH40             | Binary-BCH ECC<br>Processor                                                         | System<br>Control<br>Peripherals        | The BCH40 module provides up to 40-bit ECC encryption/decryption for NAND Flash controller (GPMI)                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CAAM              | Cryptographic<br>Accelerator and<br>Assurance Module                                | Security                                | CAAM is a cryptographic accelerator and assurance module. CAAM implements several encryption and hashing functions, a run-time integrity checker, and a Pseudo Random Number Generator (PRNG). The pseudo random number generator is certified by Cryptographic Algorithm Validation Program (CAVP) of National Institute of Standards and Technology (NIST). Its DRBG validation number is 94 and its SHS validation number is 1455.  CAAM also implements a Secure Memory mechanism. In i.MX 6Dual/6Quad processors, the security memory provided is 16 KB. |

| CCM<br>GPC<br>SRC | Clock Control<br>Module, General<br>Power Controller,<br>System Reset<br>Controller | Clocks,<br>Resets, and<br>Power Control | These modules are responsible for clock and reset distribution in the system, and also for the system power management.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Block<br>Mnemonic                         | Block Name                           | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------|--------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSI                                       | MIPI CSI-2 Interface                 | Multimedia<br>Peripherals        | The CSI IP provides MIPI CSI-2 standard camera interface port. The CSI-2 interface supports up to 1 Gbps for up to 3 data lanes and up to 800 Mbps for 4 data lanes.                                                                                                                                                                                                                                            |

| CSU                                       | Central Security Unit                | Security                         | The Central Security Unit (CSU) is responsible for setting comprehensive security policy within the i.MX 6Dual/6Quad platform. The Security Control Registers (SCR) of the CSU are set during boot time by the HAB and are locked to prevent further writing.                                                                                                                                                   |

| CTI-0<br>CTI-1<br>CTI-2<br>CTI-3<br>CTI-4 | Cross Trigger<br>Interfaces          | Debug / Trace                    | Cross Trigger Interfaces allows cross-triggering based on inputs from masters attached to CTIs. The CTI module is internal to the Cortex-A9 Core Platform.                                                                                                                                                                                                                                                      |

| СТМ                                       | Cross Trigger Matrix                 | Debug / Trace                    | Cross Trigger Matrix IP is used to route triggering events between CTIs. The CTM module is internal to the Cortex-A9 Core Platform.                                                                                                                                                                                                                                                                             |

| DAP                                       | Debug Access Port                    | System<br>Control<br>Peripherals | The DAP provides real-time access for the debugger without halting the core to:  • System memory and peripheral registers  • All debug configuration registers  The DAP also provides debugger access to JTAG scan chains. The DAP module is internal to the Cortex-A9 Core Platform.                                                                                                                           |

| DCIC-0<br>DCIC-1                          | Display Content<br>Integrity Checker | Automotive IP                    | The DCIC provides integrity check on portion(s) of the display. Each i.MX 6Dual/6Quad processor has two such modules, one for each IPU.                                                                                                                                                                                                                                                                         |

| DSI                                       | MIPI DSI interface                   | Multimedia<br>Peripherals        | The MIPI DSI IP provides DSI standard display port interface. The DSI interface support 80 Mbps to 1 Gbps speed per data lane.                                                                                                                                                                                                                                                                                  |

| DTCP                                      | DTCP                                 | MM                               | Provides encryption function according to Digital Transmission Content Protection standard for traffic over MLB150.                                                                                                                                                                                                                                                                                             |

| eCSPI1-5                                  | Configurable SPI                     | Connectivity<br>Peripherals      | Full-duplex enhanced Synchronous Serial Interface. It is configurable to support Master/Slave modes, four chip selects to support multiple peripherals.                                                                                                                                                                                                                                                         |

| ENET                                      | Ethernet Controller                  | Connectivity<br>Peripherals      | The Ethernet Media Access Controller (MAC) is designed to support 10/100/1000 Mbps Ethernet/IEEE 802.3 networks. An external transceiver interface and transceiver function are required to complete the interface to the media. The i.MX 6Dual/6Quad processors also consist of hardware assist for IEEE 1588 standard. For details, see the ENET chapter of the i.MX 6Dual/6Quad reference manual (IMX6DQRM). |

|                                           |                                      |                                  | <b>Note:</b> The theoretical maximum performance of 1 Gbps ENET is limited to 470 Mbps (total for Tx and Rx) due to internal bus throughput limitations. The actual measured performance in optimized environment is up to 400 Mbps. For details, see the ERR004512 erratum in the i.MX 6Dual/6Quad errata document (IMX6DQCE).                                                                                 |

## **Modules List**

| Block<br>Mnemonic                                                  | Block Name                           | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------|--------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EPIT-1<br>EPIT-2                                                   | Enhanced Periodic<br>Interrupt Timer | Timer<br>Peripherals             | Each EPIT is a 32-bit "set and forget" timer that starts counting after the EPIT is enabled by software. It is capable of providing precise interrupts at regular intervals with minimal processor intervention. It has a 12-bit prescaler for division of input clock frequency to get the required time setting for the interrupts to occur, and counter value can be programmed on the fly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ESAI                                                               | Enhanced Serial<br>Audio Interface   | Connectivity<br>Peripherals      | The Enhanced Serial Audio Interface (ESAI) provides a full-duplex serial port for serial communication with a variety of serial devices, including industry-standard codecs, SPDIF transceivers, and other processors. The ESAI consists of independent transmitter and receiver sections, each section with its own clock generator. All serial transfers are synchronized to a clock. Additional synchronization signals are used to delineate the word frames. The normal mode of operation is used to transfer data at a periodic rate, one word per period. The network mode is also intended for periodic transfers; however, it supports up to 32 words (time slots) per period. This mode can be used to build time division multiplexed (TDM) networks. In contrast, the on-demand mode is intended for non-periodic transfers of data and to transfer data serially at high speed when the data becomes available.  The ESAI has 12 pins for data and clocking connection to external devices. |

| FlexCAN-1<br>FlexCAN-2                                             | Flexible Controller<br>Area Network  | Connectivity<br>Peripherals      | The CAN protocol was primarily, but not only, designed to be used as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the Electromagnetic interference (EMI) environment of a vehicle, cost-effectiveness and required bandwidth. The FlexCAN module is a full implementation of the CAN protocol specification, Version 2.0 B, which supports both standard and extended message frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIO-1<br>GPIO-2<br>GPIO-3<br>GPIO-4<br>GPIO-5<br>GPIO-6<br>GPIO-7 | General Purpose I/O<br>Modules       | System<br>Control<br>Peripherals | Used for general purpose input/output to external devices. Each GPIO module supports 32 bits of I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| GPMI                                                               | General Purpose<br>Media Interface   | Connectivity<br>Peripherals      | The GPMI module supports up to 8x NAND devices. 40-bit ECC encryption/decryption for NAND Flash controller (GPMI2). The GPMI supports separate DMA channels per NAND device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GPT                                                                | General Purpose<br>Timer             | Timer<br>Peripherals             | Each GPT is a 32-bit "free-running" or "set and forget" mode timer with programmable prescaler and compare and capture register. A timer counter value can be captured using an external event and can be configured to trigger a capture event on either the leading or trailing edges of an input pulse. When the timer is configured to operate in "set and forget" mode, it is capable of providing precise interrupts at regular intervals with minimal processor intervention. The counter has output compare logic to provide the status and interrupt at comparison. This timer can be configured to run either on an external clock or on an internal clock.                                                                                                                                                                                                                                                                                                                                    |

| Block<br>Mnemonic                                              | Block Name                                    | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|----------------------------------------------------------------|-----------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GPU2Dv2                                                        | Graphics Processing<br>Unit-2D, ver. 2        | Multimedia<br>Peripherals        | The GPU2Dv2 provides hardware acceleration for 2D graphics algorithms, such as Bit BLT, stretch BLT, and many other 2D functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| GPU2Dv4                                                        | Graphics Processing<br>Unit, ver. 4           | Multimedia<br>Peripherals        | The GPU2Dv4 provides hardware acceleration for 3D graphics algorithms with sufficient processor power to run desktop quality interactive graphics applications on displays up to HD1080 resolution. The GPU3D provides OpenGL ES 2.0, including extensions, OpenGL ES 1.1, and OpenVG 1.1                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| GPUVGv2                                                        | Vector Graphics<br>Processing Unit,<br>ver. 2 | Multimedia<br>Peripherals        | OpenVG graphics accelerator provides OpenVG 1.1 support as well as other accelerations, including Real-time hardware curve tesselation of lines, quadratic and cubic Bezier curves, 16x Line Anti-aliasing, and various Vector Drawing functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| HDMI Tx                                                        | HDMI Tx interface                             | Multimedia<br>Peripherals        | The HDMI module provides HDMI standard interface port to an HDMI 1.4 compliant display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| HSI                                                            | MIPI HSI interface                            | Connectivity<br>Peripherals      | The MIPI HSI provides a standard MIPI interface to the applications processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| I <sup>2</sup> C-1<br>I <sup>2</sup> C-2<br>I <sup>2</sup> C-3 | I <sup>2</sup> C Interface                    | Connectivity<br>Peripherals      | I <sup>2</sup> C provide serial interface for external devices. Data rates of up to 400 kbps are supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| IOMUXC                                                         | IOMUX Control                                 | System<br>Control<br>Peripherals | This module enables flexible IO multiplexing. Each IO pad has default and several alternate functions. The alternate functions are software configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| IPUv3H-1<br>IPUv3H-2                                           | Image Processing<br>Unit, ver. 3H             | Multimedia<br>Peripherals        | IPUv3H enables connectivity to displays and video sources, relevant processing and synchronization and control capabilities, allowing autonomous operation.  The IPUv3H supports concurrent output to two display ports and concurrent input from two camera ports, through the following interfaces:  Parallel Interfaces for both display and camera Single/dual channel LVDS display interface HDMI transmitter MIPI/DSI transmitter MIPI/CSI-2 receiver The processing includes: Image conversions: resizing, rotation, inversion, and color space conversion A high-quality de-interlacing filter Video/graphics combining Image enhancement: color adjustment and gamut mapping, gamma correction, and contrast enhancement |  |

| KPP                                                            | Key Pad Port                                  | Connectivity<br>Peripherals      | KPP Supports 8 x 8 external key pad matrix. KPP features are:  Open drain design Glitch suppression circuit design Multiple keys detection Standby key press detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

## **Modules List**

| Block<br>Mnemonic                | Block Name                   | Subsystem                                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------|------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDB                              | LVDS Display Bridge          | Connectivity<br>Peripherals                 | LVDS Display Bridge is used to connect the IPU (Image Processing Unit) to External LVDS Display Interface. LDB supports two channels; each channel has following signals:  • One clock pair  • Four data pairs Each signal pair contains LVDS special differential pad (PadP, PadM).                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MLB150                           | MediaLB                      | Connectivity /<br>Multimedia<br>Peripherals | The MLB interface module provides a link to a MOST <sup>®</sup> data network, using the standardized MediaLB protocol (up to 150 Mbps). The module is backward compatible to MLB-50.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MMDC                             | Multi-Mode DDR<br>Controller | Connectivity<br>Peripherals                 | DDR Controller has the following features:  • Support 16/32/64-bit DDR3-1066 (LV) or LPDDR2-1066  • Supports both dual x32 for LPDDR2 and x64 DDR3 / LPDDR2 configurations (including 2x32 interleaved mode)  • Support up to 4 GByte DDR memory space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OCOTP_CTRL                       | OTP Controller               | Security                                    | The On-Chip OTP controller (OCOTP_CTRL) provides an interface for reading, programming, and/or overriding identification and control information stored in on-chip fuse elements. The module supports electrically-programmable poly fuses (eFUSEs). The OCOTP_CTRL also provides a set of volatile software-accessible signals that can be used for software control of hardware elements, not requiring non-volatility. The OCOTP_CTRL provides the primary user-visible mechanism for interfacing with on-chip fuse elements. Among the uses for the fuses are unique chip identifiers, mask revision numbers, cryptographic keys, JTAG secure mode, boot characteristics, and various control signals, requiring permanent non-volatility. |

| OCRAM                            | On-Chip Memory<br>Controller | Data Path                                   | The On-Chip Memory controller (OCRAM) module is designed as an interface between system's AXI bus and internal (on-chip) SRAM memory module.  In i.MX 6Dual/6Quad processors, the OCRAM is used for controlling the 256 KB multimedia RAM through a 64-bit AXI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OSC 32 kHz                       | OSC 32 kHz                   | Clocking                                    | Generates 32.768 kHz clock from an external crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PCle                             | PCI Express 2.0              | Connectivity<br>Peripherals                 | The PCIe IP provides PCI Express Gen 2.0 functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PMU                              | Power-Management Functions   | Data Path                                   | Integrated power management unit. Used to provide power to various SoC domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PWM-1<br>PWM-2<br>PWM-3<br>PWM-4 | Pulse Width<br>Modulation    | Connectivity<br>Peripherals                 | The pulse-width modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images and it can also generate tones. It uses 16-bit resolution and a 4x16 data FIFO to generate sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RAM<br>16 KB                     | Secure/non-secure<br>RAM     | Secured<br>Internal<br>Memory               | Secure/non-secure Internal RAM, interfaced through the CAAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RAM<br>256 KB                    | Internal RAM                 | Internal<br>Memory                          | Internal RAM, which is accessed through OCRAM memory controllers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Block<br>Mnemonic | Block Name                                  | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|---------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROM<br>96KB       | Boot ROM                                    | Internal<br>Memory               | Supports secure and regular Boot Modes. Includes read protection on 4K region for content protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ROMCP             | ROM Controller with Patch                   | Data Path                        | ROM Controller with ROM Patch support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SATA              | Serial ATA                                  | Connectivity<br>Peripherals      | The SATA controller and PHY is a complete mixed-signal IP solution designed to implement SATA II, 3.0 Gbps HDD connectivity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SDMA              | Smart Direct Memory<br>Access               | System<br>Control<br>Peripherals | The SDMA is multi-channel flexible DMA engine. It helps in maximizing system performance by off-loading the various cores in dynamic data routing. It has the following features:  Powered by a 16-bit Instruction-Set micro-RISC engine  Multi-channel DMA supporting up to 32 time-division multiplexed DMA channels  48 events with total flexibility to trigger any combination of channels  Memory accesses including linear, FIFO, and 2D addressing  Shared peripherals between ARM and SDMA  Very fast context-switching with 2-level priority based preemptive multi-tasking  DMA units with auto-flush and prefetch capability  Flexible address management for DMA transfers (increment, decrement, and no address changes on source and destination address)  DMA ports can handle unit-directional and bi-directional flows (copy mode)  Up to 8-word buffer for configurable burst transfers  Support of byte-swapping and CRC calculations  Library of Scripts and API is available |

| SJC               | System JTAG<br>Controller                   | System<br>Control<br>Peripherals | The SJC provides JTAG interface, which complies with JTAG TAP standards, to internal logic. The i.MX 6Dual/6Quad processors use JTAG port for production, testing, and system debugging. In addition, the SJC provides BSR (Boundary Scan Register) standard support, which complies with IEEE1149.1 and IEEE1149.6 standards.  The JTAG port must be accessible during platform initial laboratory bring-up, for manufacturing tests and troubleshooting, as well as for software debugging by authorized entities. The i.MX 6Dual/6Quad SJC incorporates three security modes for protecting against unauthorized accesses. Modes are selected through eFUSE configuration.                                                                                                                                                                                                                                                                                                                      |

| SNVS              | Secure Non-Volatile<br>Storage              | Security                         | Secure Non-Volatile Storage, including Secure Real Time Clock, Security State Machine, Master Key Control, and Violation/Tamper Detection and reporting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SPDIF             | Sony Philips Digital<br>Interconnect Format | Multimedia<br>Peripherals        | A standard audio file transfer format, developed jointly by the Sony and Phillips corporations. It supports Transmitter and Receiver functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## **Modules List**

| Block<br>Mnemonic                              | Block Name                                   | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------|----------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97<br>Interface                    | Connectivity<br>Peripherals      | The SSI is a full-duplex synchronous interface, which is used on the processor to provide connectivity with off-chip audio peripherals. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock / frame sync options. The SSI has two pairs of 8x24 FIFOs and hardware support for an external DMA controller to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream that reduces CPU overhead in use cases where two time slots are being used simultaneously. |

| TEMPMON                                        | Temperature Monitor                          | System<br>Control<br>Peripherals | The temperature monitor/sensor IP module for detecting high temperature conditions. The temperature read out does not reflect case or ambient temperature. It reflects the temperature in proximity of the sensor location on the die. Temperature distribution may not be uniformly distributed; therefore, the read out value may not be the reflection of the temperature value for the entire die.                                                                                                                                                                                                                 |

| TZASC                                          | Trust-Zone Address<br>Space Controller       | Security                         | The TZASC (TZC-380 by ARM) provides security address region control functions required for intended application. It is used on the path to the DRAM controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |