Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## MCP14A0153/4/5

# 1.5A Dual MOSFET Driver with Low Threshold Input And Enable

#### **Features**

- · High Peak Output Current: 1.5A (typical)

- · Wide Input Supply Voltage Operating Range:

- 4.5V to 18V

- Low Shoot-Through/Cross-Conduction Current in Output Stage

- · High Capacitive Load Drive Capability:

- 1000 pF in 11.5 ns (typical)

- Short Delay Times: 25 ns (t<sub>D1</sub>), 24 ns (t<sub>D2</sub>) (typical)

- Low Supply Current: 750 μA (typical)

- Low-Voltage Threshold Input and Enable with Hysteresis

- Latch-Up Protected: Withstands 500 mA Reverse Current

- · Space-Saving Packages:

- 8-Lead MSOP

- 8-Lead SOIC

- 8-Lead 2x3 TDFN

#### **Applications**

- · Switch Mode Power Supplies

- · Pulse Transformer Drive

- · Line Drivers

- Level Translator

- · Motor and Solenoid Drive

#### **General Description**

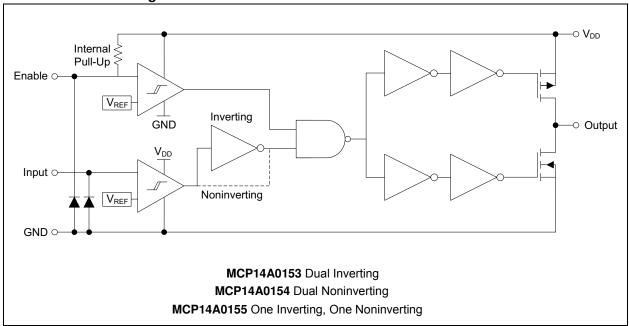

The MCP14A0153/4/5 devices are high-speed dual MOSFET drivers that are capable of providing up to 1.5A of peak current while operating from a single 4.5V to 18V supply. There are three output configurations available; dual inverting (MCP14A0153), dual noninverting (MCP14A0154) and complementary (MCP14A0155). These devices feature low shoot-through current, matched rise and fall times, and short propagation delays which make them ideal for high switching frequency applications.

The MCP14A0153/4/5 family of devices offer enhanced control with Enable functionality. The active-high Enable pins can be driven low to drive the corresponding outputs of the MCP14A0153/4/5 low, regardless of the status of the Input pin. An integrated pull-up resistor allows the user to leave the Enable pins floating for standard operation.

These devices are highly latch-up resistant under any condition within their power and voltage ratings. They can accept up to 500 mA of reverse current being forced back into their outputs without damage or logic upset. All terminals are fully protected against electrostatic discharge (ESD) up to 2 kV (HBM) and 200 V (MM).

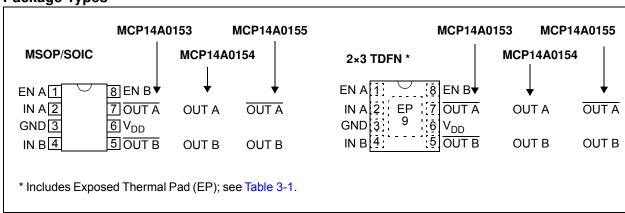

### **Package Types**

## **Functional Block Diagram**

## 1.0 ELECTRICAL CHARACTERISTICS

### **Absolute Maximum Ratings †**

| V <sub>DD</sub> , Supply Voltage                  | +20V        |

|---------------------------------------------------|-------------|

| $V_{IN}$ , Input Voltage( $V_{DD}$ + 0.3V) to (0  | GND - 0.3V) |

| $V_{EN}$ , Enable Voltage( $V_{DD}$ + 0.3V) to (0 | GND - 0.3V) |

| Package Power Dissipation ( $T_A = +50$ °C)       |             |

| 8L MSOP                                           | 0.63W       |

| 8L SOIC                                           | 1.00W       |

| 8L 2 x 3 TDFN                                     | 1.86W       |

| ESD Protection on all Pins                        | 2 kV (HBM)  |

|                                                   | .200V (MM)  |

† Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### DC CHARACTERISTICS

| <b>Electrical Specifications:</b> Unless otherwise noted, $T_A = +25^{\circ}C$ , with $4.5V \le V_{DD} \le 18V$ . |                       |                         |      |                       |       |                                                                                            |  |

|-------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|------|-----------------------|-------|--------------------------------------------------------------------------------------------|--|

| Parameters                                                                                                        | Sym.                  | Min.                    | Тур. | Max.                  | Units | Conditions                                                                                 |  |

| Input                                                                                                             |                       |                         |      |                       |       |                                                                                            |  |

| Input Voltage Range                                                                                               | V <sub>IN</sub>       | GND - 0.3               | _    | V <sub>DD</sub> + 0.3 | V     |                                                                                            |  |

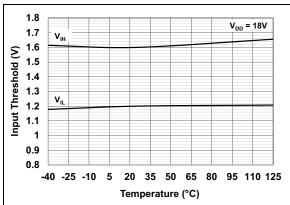

| Logic '1' High Input Voltage                                                                                      | V <sub>IH</sub>       | 2.0                     | 1.6  | _                     | V     |                                                                                            |  |

| Logic '0' Low Input Voltage                                                                                       | V <sub>IL</sub>       | _                       | 1.2  | 0.8                   | V     |                                                                                            |  |

| Input Voltage Hysteresis                                                                                          | V <sub>HYST(IN)</sub> | _                       | 0.4  | _                     | V     |                                                                                            |  |

| Input Current                                                                                                     | I <sub>IN</sub>       | -1                      | _    | +1                    | μA    | $0V \le V_{IN} \le V_{DD}$                                                                 |  |

| Enable                                                                                                            |                       |                         |      |                       |       |                                                                                            |  |

| Enable Voltage Range                                                                                              | V <sub>EN</sub>       | GND - 0.3V              | _    | V <sub>DD</sub> + 0.3 | V     |                                                                                            |  |

| Logic '1' High Enable Voltage                                                                                     | V <sub>EH</sub>       | 2                       | 1.6  | _                     | V     |                                                                                            |  |

| Logic '0' Low Enable Voltage                                                                                      | V <sub>EL</sub>       | _                       | 1.2  | 0.8                   | V     |                                                                                            |  |

| Enable Voltage Hysteresis                                                                                         | V <sub>HYST(EN)</sub> | _                       | 0.4  | _                     | V     |                                                                                            |  |

| Enable Pin Pull-Up Resistance                                                                                     | R <sub>ENBL</sub>     | _                       | 1.8  | _                     | ΜΩ    | V <sub>DD</sub> = 18V, EN = GND                                                            |  |

| Enable Input Current                                                                                              | I <sub>EN</sub>       | _                       | 10   | _                     | μA    | V <sub>DD</sub> = 18V, EN = GND                                                            |  |

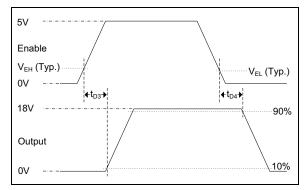

| Propagation Delay                                                                                                 | t <sub>D3</sub>       | _                       | 25   | 32                    | ns    | V <sub>DD</sub> = 18V, V <sub>EN</sub> = 5V,<br>see Figure 4-3, ( <b>Note 1</b> )          |  |

| Propagation Delay                                                                                                 | t <sub>D4</sub>       | _                       | 24   | 31                    | ns    | V <sub>DD</sub> = 18V, V <sub>EN</sub> = 5V,<br>see Figure 4-3, ( <b>Note 1</b> )          |  |

| Output                                                                                                            |                       |                         |      |                       |       |                                                                                            |  |

| High Output Voltage                                                                                               | V <sub>OH</sub>       | V <sub>DD</sub> - 0.025 | _    | _                     | V     | I <sub>OUT</sub> = 0A                                                                      |  |

| Low Output Voltage                                                                                                | V <sub>OL</sub>       | _                       | _    | 0.025                 | V     | I <sub>OUT</sub> = 0A                                                                      |  |

| Output Resistance, High                                                                                           | R <sub>OH</sub>       | _                       | 4.5  | 6.5                   | Ω     | I <sub>OUT</sub> = 10 mA, V <sub>DD</sub> = 18V                                            |  |

| Output Resistance, Low                                                                                            | R <sub>OL</sub>       | _                       | 3.0  | 4.5                   | Ω     | I <sub>OUT</sub> = 10 mA, V <sub>DD</sub> = 18V                                            |  |

| Peak Output Current                                                                                               | I <sub>PK</sub>       | _                       | 1.5  | _                     | Α     | V <sub>DD</sub> = 18V (Note 1)                                                             |  |

| Latch-Up Protection Withstand<br>Reverse Current                                                                  | I <sub>REV</sub>      | 0.5                     | _    | _                     | Α     | Duty cycle $\leq$ 2%, t $\leq$ 300 $\mu$ s (Note 1)                                        |  |

| Switching Time (Note 1)                                                                                           | •                     |                         |      |                       | •     |                                                                                            |  |

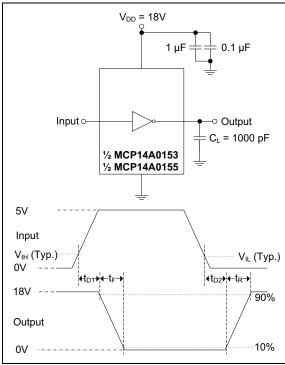

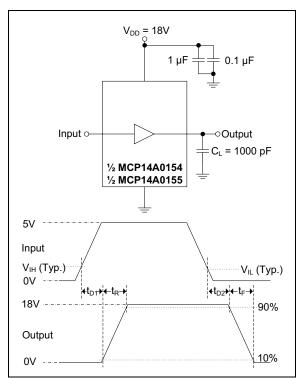

| Rise Time                                                                                                         | t <sub>R</sub>        | _                       | 11.5 | 18.5                  | ns    | V <sub>DD</sub> = 18V, C <sub>L</sub> = 1000 pF,<br>see Figure 4-1, Figure 4-2<br>(Note 1) |  |

**Note 1:** Tested during characterization, not production tested.

## **DC CHARACTERISTICS (CONTINUED)**

| <b>Electrical Specifications:</b> Unless otherwise noted, $T_A$ = +25°C, with 4.5V $\leq$ V <sub>DD</sub> $\leq$ 18V. |                 |      |      |      |       |                                                                                                 |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------|-----------------|------|------|------|-------|-------------------------------------------------------------------------------------------------|--|--|--|

| Parameters                                                                                                            | Sym.            | Min. | Тур. | Max. | Units | Conditions                                                                                      |  |  |  |

| Fall Time                                                                                                             | t <sub>F</sub>  | _    | 10   | 17   | ns    | V <sub>DD</sub> = 18V, C <sub>L</sub> = 1000 pF,<br>see Figure 4-1, Figure 4-2<br>(Note 1)      |  |  |  |

| Delay Time                                                                                                            | t <sub>D1</sub> | 1    | 25   | 32   | ns    | V <sub>DD</sub> = 18V, V <sub>IN</sub> = 5V,<br>see Figure 4-1, Figure 4-2<br>(Note 1)          |  |  |  |

|                                                                                                                       | t <sub>D2</sub> | -    | 24   | 31   | ns    | V <sub>DD</sub> = 18V, V <sub>IN</sub> = 5V,<br>see Figure 4-1, Figure 4-2<br>( <b>Note 1</b> ) |  |  |  |

| Power Supply                                                                                                          |                 |      |      |      |       |                                                                                                 |  |  |  |

| Supply Voltage                                                                                                        | $V_{DD}$        | 4.5  | _    | 18   | V     |                                                                                                 |  |  |  |

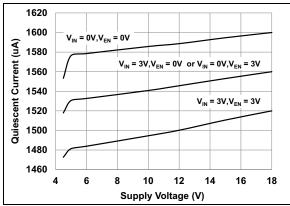

|                                                                                                                       | I <sub>DD</sub> | 1    | 675  | 1120 | μA    | $V_{INA/B} = 3V$ , $V_{ENA/B} = 3V$                                                             |  |  |  |

| Power Supply Current                                                                                                  | $I_{DD}$        | _    | 715  | 1160 | μΑ    | $V_{INA/B} = 0V$ , $V_{ENA/B} = 3V$                                                             |  |  |  |

|                                                                                                                       | $I_{DD}$        | 1    | 715  | 1160 | μΑ    | $V_{INA/B} = 3V$ , $V_{ENA/B} = 0V$                                                             |  |  |  |

|                                                                                                                       | $I_{DD}$        | _    | 750  | 1200 | μΑ    | $V_{INA/B} = 0V$ , $V_{ENA/B} = 0V$                                                             |  |  |  |

Note 1: Tested during characterization, not production tested.

## DC CHARACTERISTICS (OVER OPERATING TEMPERATURE RANGE) (Note 1)

| <b>Electrical Specifications:</b> Unless otherwise indicated, over the operating range with $4.5V \le V_{DD} \le 18V$ . |                       |                         |      |                       |       |                                                                 |  |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|------|-----------------------|-------|-----------------------------------------------------------------|--|

| Parameters                                                                                                              | Sym.                  | Min.                    | Тур. | Max.                  | Units | Conditions                                                      |  |

| Input                                                                                                                   |                       |                         |      |                       |       |                                                                 |  |

| Input Voltage Range                                                                                                     | V <sub>IN</sub>       | GND - 0.3V              | _    | $V_{DD} + 0.3$        | V     |                                                                 |  |

| Logic '1' High Input Voltage                                                                                            | V <sub>IH</sub>       | 2.0                     | 1.6  | _                     | V     |                                                                 |  |

| Logic '0' Low Input Voltage                                                                                             | $V_{IL}$              | _                       | 1.2  | 1.8                   | V     |                                                                 |  |

| Input Voltage Hysteresis                                                                                                | V <sub>HYST(IN)</sub> | _                       | 0.4  | _                     | V     |                                                                 |  |

| Input Current                                                                                                           | I <sub>IN</sub>       | -10                     | _    | +10                   | μΑ    | $0V \le V_{IN} \le V_{DD}$                                      |  |

| Enable                                                                                                                  |                       |                         |      |                       |       |                                                                 |  |

| Enable Voltage Range                                                                                                    | V <sub>EN</sub>       | GND - 0.3V              | _    | V <sub>DD</sub> + 0.3 | V     |                                                                 |  |

| Logic '1' High Enable Voltage                                                                                           | V <sub>EH</sub>       | 2.0                     | 1.6  | _                     | V     |                                                                 |  |

| Logic '0' Low Enable Voltage                                                                                            | V <sub>EL</sub>       | _                       | 1.2  | 1.8                   | V     |                                                                 |  |

| Enable Voltage Hysteresis                                                                                               | V <sub>HYST(EN)</sub> | _                       | 0.4  | _                     | V     |                                                                 |  |

| Enable Input Current                                                                                                    | I <sub>EN</sub>       |                         | 12   | _                     | μΑ    | V <sub>DD</sub> = 18V, EN = GND                                 |  |

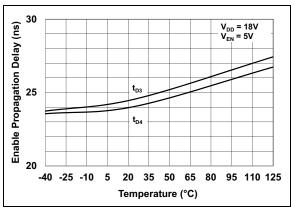

| Propagation Delay                                                                                                       | t <sub>D3</sub>       |                         | 28   | 35                    | ns    | $V_{DD}$ = 18V, $V_{EN}$ = 5V, $T_{A}$ = +125°C, see Figure 4-3 |  |

| Propagation Delay                                                                                                       | t <sub>D4</sub>       | _                       | 27   | 34                    | ns    | $V_{DD}$ = 18V, $V_{EN}$ = 5V, $T_{A}$ = +125°C, see Figure 4-3 |  |

| Output                                                                                                                  |                       |                         |      |                       |       |                                                                 |  |

| High Output Voltage                                                                                                     | V <sub>OH</sub>       | V <sub>DD</sub> - 0.025 | _    |                       | V     | DC Test                                                         |  |

| Low Output Voltage                                                                                                      | V <sub>OL</sub>       | _                       | _    | 0.025                 | V     | DC Test                                                         |  |

| Output Resistance, High                                                                                                 | R <sub>OH</sub>       | _                       | _    | 9                     | Ω     | I <sub>OUT</sub> = 10 mA, V <sub>DD</sub> = 18V                 |  |

| Output Resistance, Low                                                                                                  | R <sub>OL</sub>       | _                       | _    | 6.5                   | Ω     | I <sub>OUT</sub> = 10 mA, V <sub>DD</sub> = 18V                 |  |

**Note 1:** Tested during characterization, not production tested.

## DC CHARACTERISTICS (OVER OPERATING TEMPERATURE RANGE) (Note 1)

| <b>Electrical Specifications:</b> Unless otherwise indicated, over the operating range with $4.5 \text{V} \le \text{V}_{DD} \le 18 \text{V}$ . |                 |      |      |      |       |                                                                                   |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|------|------|-------|-----------------------------------------------------------------------------------|--|--|

| Parameters                                                                                                                                     | Sym.            | Min. | Тур. | Max. | Units | Conditions                                                                        |  |  |

| Switching Time (Note 1)                                                                                                                        |                 |      |      |      |       |                                                                                   |  |  |

| Rise Time                                                                                                                                      | t <sub>R</sub>  | _    | 14   | 21   | ns    | $V_{DD}$ = 18V, $C_L$ = 1000 pF,<br>$T_A$ = +125°C, see Figure 4-1,<br>Figure 4-2 |  |  |

| Fall Time                                                                                                                                      | t <sub>F</sub>  | _    | 13   | 20   | ns    | $V_{DD}$ = 18V, $C_L$ = 1000 pF,<br>$T_A$ = +125°C, see Figure 4-1,<br>Figure 4-2 |  |  |

| Delay Time                                                                                                                                     | t <sub>D1</sub> | _    | 28   | 35   | ns    | $V_{DD}$ = 18V, $V_{IN}$ = 5V, $T_A$ = +125°C,<br>see Figure 4-1, Figure 4-2      |  |  |

|                                                                                                                                                | t <sub>D2</sub> | _    | 27   | 34   |       | $V_{DD}$ = 18V, $V_{IN}$ = 5V, $T_A$ = +125°C, see Figure 4-1, Figure 4-2         |  |  |

| Power Supply                                                                                                                                   |                 |      |      |      |       |                                                                                   |  |  |

| Supply Voltage                                                                                                                                 | $V_{DD}$        | 4.5  | _    | 18   | V     |                                                                                   |  |  |

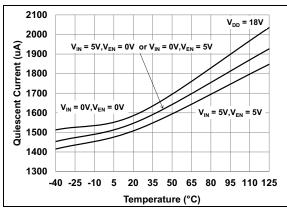

|                                                                                                                                                | $I_{DD}$        | _    | _    | 1520 | μΑ    | $V_{IN} = 3V$ , $V_{EN} = 3V$                                                     |  |  |

| Power Supply Current                                                                                                                           | $I_{DD}$        | _    | _    | 1560 | μΑ    | $V_{IN}$ = 0V, $V_{EN}$ = 3V                                                      |  |  |

|                                                                                                                                                | $I_{DD}$        | _    | _    | 1560 | μΑ    | $V_{IN} = 3V$ , $V_{EN} = 0V$                                                     |  |  |

|                                                                                                                                                | $I_{DD}$        | _    | _    | 1600 | μΑ    | $V_{IN} = 0V, V_{EN} = 0V$                                                        |  |  |

Note 1: Tested during characterization, not production tested.

### **TEMPERATURE CHARACTERISTICS**

| <b>Electrical Specifications:</b> Unless otherwise noted, all parameters apply with $4.5V \le V_{DD} \le 18V$ . |                |      |       |      |       |          |  |

|-----------------------------------------------------------------------------------------------------------------|----------------|------|-------|------|-------|----------|--|

| Parameter                                                                                                       | Sym.           | Min. | Тур.  | Max. | Units | Comments |  |

| Temperature Ranges                                                                                              |                |      |       |      |       |          |  |

| Specified Temperature Range                                                                                     | T <sub>A</sub> | -40  | _     | +125 | °C    |          |  |

| Maximum Junction Temperature                                                                                    | T <sub>J</sub> | _    | _     | +150 | °C    |          |  |

| Storage Temperature Range                                                                                       | T <sub>A</sub> | -65  | _     | +150 | °C    |          |  |

| Package Thermal Information                                                                                     |                |      |       |      |       |          |  |

| Junction-to-Ambient Thermal Resistance, 8LD MSOP                                                                | $\theta_{JA}$  | _    | 158   | _    | °C/W  | Note 1   |  |

| Junction-to-Ambient Thermal Resistance, 8LD SOIC                                                                | $\theta_{JA}$  | _    | 99.8  | _    | °C/W  | Note 1   |  |

| Junction-to-Ambient Thermal Resistance, 8LD TDFN                                                                | $\theta_{JA}$  | _    | 53.7  | _    | °C/W  | Note 1   |  |

| Junction-to-Top Characterization Parameter, 8LD MSOP                                                            | $\Psi_{JT}$    | _    | 2.4   | _    | °C/W  | Note 1   |  |

| Junction-to-Top Characterization Parameter, 8LD SOIC                                                            | $\Psi_{JT}$    | _    | 5.9   | _    | °C/W  | Note 1   |  |

| Junction-to-Top Characterization Parameter, 8LD TDFN                                                            | $\Psi_{JT}$    | _    | 0.5   | _    | °C/W  | Note 1   |  |

| Junction-to-Board Characterization Parameter, 8LD MSOP                                                          | $\Psi_{JB}$    | _    | 115.2 | _    | °C/W  | Note 1   |  |

| Junction-to-Board Characterization Parameter, 8LD SOIC                                                          | $\Psi_{JB}$    | _    | 64.8  | _    | °C/W  | Note 1   |  |

| Junction-to-Board Characterization Parameter, 8LD TDFN                                                          | $\Psi_{JB}$    | _    | 24.4  | _    | °C/W  | Note 1   |  |

**Note 1:** Parameter is determined using a High K 2S2P 4-Layer board as described in JESD 51-7, as well as JESD 51-5 for packages with exposed pads.

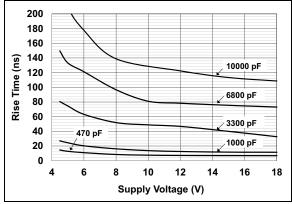

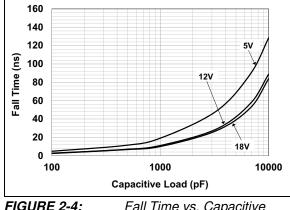

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

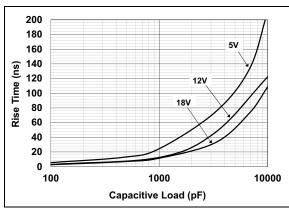

**FIGURE 2-1:** Rise Time vs. Supply Voltage.

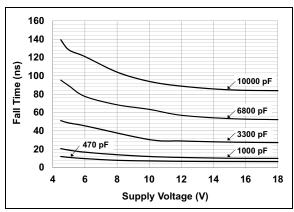

FIGURE 2-4: Fall Time vs. Capacitive Load.

FIGURE 2-2: Rise Time vs. Capacitive Load.

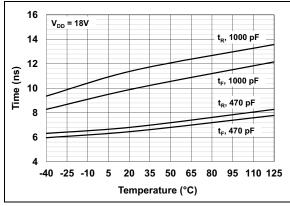

**FIGURE 2-5:** Rise and Fall Time vs. Temperature.

FIGURE 2-3: Fall Time vs. Supply Voltage.

FIGURE 2-6: Crossover Current vs. Supply Voltage.

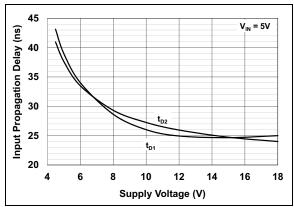

**FIGURE 2-7:** Input Propagation Delay vs. Supply Voltage.

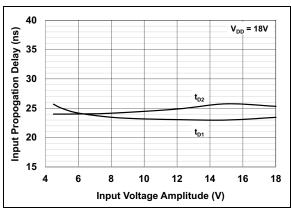

**FIGURE 2-8:** Input Propagation Delay Time vs. Input Amplitude.

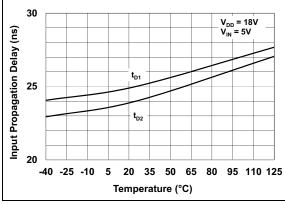

FIGURE 2-9: Input Propagation Delay vs. Temperature.

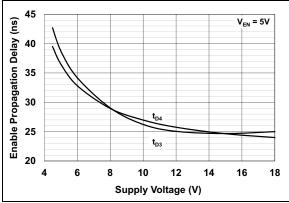

**FIGURE 2-10:** Enable Propagation Delay vs. Supply Voltage.

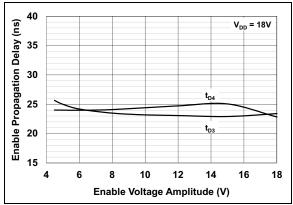

**FIGURE 2-11:** Enable Propagation Delay Time vs. Enable Voltage Amplitude.

**FIGURE 2-12:** Enable Propagation Delay vs. Temperature.

**FIGURE 2-13:** Quiescent Supply Current vs. Supply Voltage.

**FIGURE 2-14:** Quiescent Supply Current vs. Temperature.

FIGURE 2-15: Input Threshold vs. Temperature.

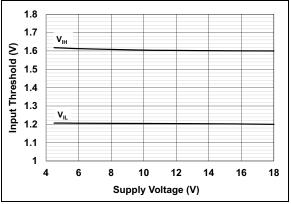

FIGURE 2-16: Input Threshold vs Supply Voltage.

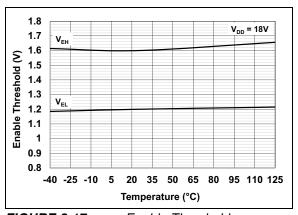

**FIGURE 2-17:** Enable Threshold vs. Temperature.

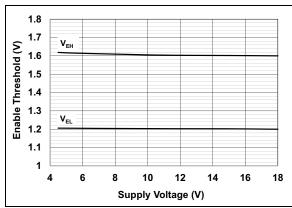

FIGURE 2-18: Enable Threshold vs Supply Voltage.

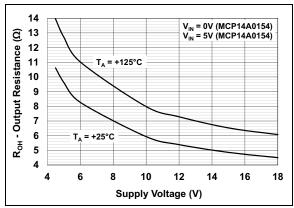

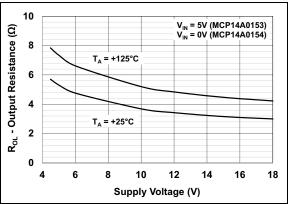

**FIGURE 2-19:** Output Resistance (Output High) vs. Supply Voltage.

**FIGURE 2-20:** Output Resistance (Output Low) vs. Supply Voltage.

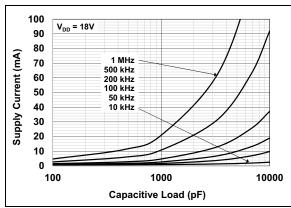

**FIGURE 2-21:** Supply Current vs. Capacitive Load ( $V_{DD} = 18V$ ).

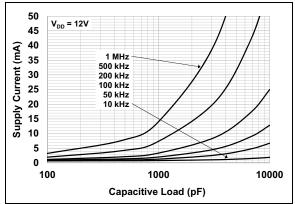

**FIGURE 2-22:** Supply Current vs. Capacitive Load ( $V_{DD} = 12V$ ).

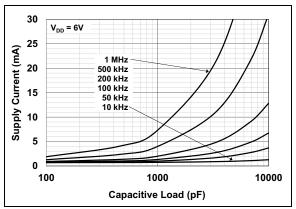

**FIGURE 2-23:** Supply Current vs. Capacitive Load  $(V_{DD} = 6V)$ .

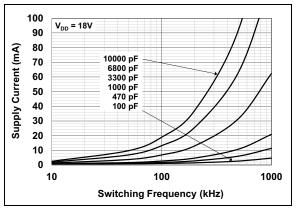

**FIGURE 2-24:** Supply Current vs. Frequency  $(V_{DD} = 18V)$ .

## MCP14A0153/4/5

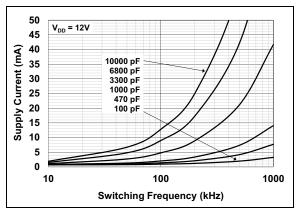

**FIGURE 2-25:** Supply Current vs. Frequency  $(V_{DD} = 12V)$ .

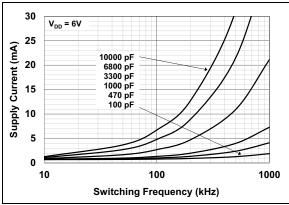

**FIGURE 2-26:** Supply Current vs. Frequency  $(V_{DD} = 6V)$ .

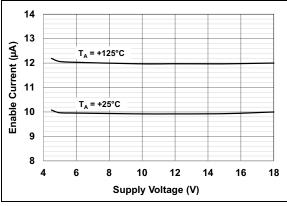

FIGURE 2-27: Enable Current vs. Supply Voltage.

#### 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| MCP14A0153, MCP1 | 4A0153, MCP14A0153 | Ob-al       | Dan animalia m            |

|------------------|--------------------|-------------|---------------------------|

| 2x3 TDFN         | MSOP/SOIC          | Symbol      | Description               |

| 1                | 1                  | EN A        | Enable - Channel A        |

| 2                | 2                  | IN A        | Input - Channel A         |

| 3                | 3                  | GND         | Device Ground             |

| 4                | 4                  | IN B        | Input - Channel B         |

| 5                | 5                  | OUT B/OUT B | Output - Channel B        |

| 6                | 6                  | $V_{DD}$    | Supply Input              |

| 7                | 7                  | OUT A/OUT A | Output - Channel A        |

| 8                | 8                  | EN B        | Enable - Channel B        |

| EP               | _                  | EP          | Exposed Thermal Pad (GND) |

## 3.1 Output Pins (OUT A/OUT A, OUT B/OUT B)

The outputs are CMOS push-pull circuits that are capable of sourcing and sinking 1.5A of peak current ( $V_{DD}$  = 18V). The low output impedance ensures the gate of the external MOSFET stays in the intended state even during large transients. This output also has a reverse current latch-up rating of 500 mA.

#### 3.2 Device Ground Pin (GND)

GND is the device return pin for the input and output stages. The GND pin should have a low-impedance connection to the bias supply source return. When the capacitive load is being discharged, high peak currents will flow through the ground pin.

#### 3.3 Device Enable Pins (EN A,EN B)

The MOSFET driver device enable pins are high-impedance inputs featuring low threshold levels. The enable inputs also have hysteresis between the high and low input levels, allowing them to be driven from slow rising and falling signals and to provide noise immunity. Driving the enable pins below the threshold will disable the corresponding output of the device, pulling OUT/OUT low, regardless of the status of the Input pin. Driving the enable pins above the threshold allows normal operation of the OUT/OUT pin based on the status of the Input pin. The enable pins utilize internal pull up resistors, allowing the pins to be left floating for standard driver operation.

#### 3.4 Control Input Pins (IN A,IN B)

The MOSFET driver control inputs are high-impedance inputs featuring low threshold levels. The Inputs also have hysteresis between the high and low input levels, allowing them to be driven from slow rising and falling signals and to provide noise immunity.

#### 3.5 Supply Input Pin (V<sub>DD</sub>)

$V_{DD}$  is the bias supply input for the MOSFET driver and has a voltage range of 4.5V to 18V. This input must be decoupled to ground with a local capacitor. This bypass capacitor provides a localized low-impedance path for the peak currents that are provided to the load.

#### 3.6 Exposed Metal Pad Pin (EP)

The exposed metal pad of the TDFN package is internally connected to GND. Therefore, this pad should be connected to a Ground plane to aid in heat removal from the package.

#### 4.0 APPLICATION INFORMATION

#### 4.1 General Information

MOSFET drivers are high-speed, high-current devices which are intended to source/sink high-peak currents to charge/discharge the gate capacitance of external MOSFETs or Insulated-Gate Bipolar Transistors (IGBTs). In high frequency switching power supplies, the Pulse-Width Modulation (PWM) controller may not have the drive capability to directly drive the power MOSFET. A MOSFET driver such as the MCP14A0153/4/5 family can be used to provide additional source/sink current capability.

### 4.2 MOSFET Driver Timing

The ability of a MOSFET driver to transition from a fully-off state to a fully-on state is characterized by the driver's rise time ( $t_R$ ), fall time ( $t_F$ ) and propagation delays ( $t_{D1}$  and  $t_{D2}$ ). Figure 4-1 and Figure 4-2 show the test circuit and timing waveform used to verify the MCP14A0153/4/5 timing.

FIGURE 4-1: Inverting Driver Timing Waveform.

**FIGURE 4-2:** Noninverting Driver Timing Waveform.

#### 4.3 Enable Function

The enable pins (EN A,EN B) provide additional control of the output pins (OUT). These pins are active high and are internally pulled up to  $V_{DD}$  so that the pins can be left floating to provide standard MOSFET driver operation.

When the enable pin input voltage's are above the enable pin high voltage threshold,  $(V_{EN\_H})$ , the corresponding output is enabled and allowed to react to the status of the Input pin. However, when the voltage applied to the Enable pins falls below the low threshold voltage  $(V_{EN\_L})$ , the driver's corresponding output is disabled and doesn't respond to changes in the status of the Input pins. When the driver is disabled, the output is pulled down to a low state. Refer to Table 4-1 for the Enable pin logic. The threshold voltage levels for the Enable pin are similar to the threshold voltage levels of the Input pin, and are TTL compatible. Hysteresis is provided to help increase the noise immunity of the enable function, avoiding false triggers of the enable signal during driver switching.

There are propagation delays associated with the driver receiving an enable signal and the output reacting. These propagation delays,  $t_{D3}$  and  $t_{D4}$ , are graphically represented in Figure 4-3.

TABLE 4-1: ENABLE PIN LOGIC

| EN | IN | OUT | OUT |

|----|----|-----|-----|

| Н  | Н  | L   | Н   |

| Н  | L  | Н   | L   |

| L  | Х  | L   | L   |

FIGURE 4-3: Enal

Enable Timing Waveform.

#### 4.4 Decoupling Capacitors

Careful PCB layout and decoupling capacitors are required when using power MOSFET drivers. Large current is required to charge and discharge capacitive loads quickly. For example, approximately 720 mA are needed to charge a 1000 pF load with 18V in 25 ns.

To operate the MOSFET driver over a wide frequency range with low supply impedance, it is recommended to place 1.0  $\mu\text{F}$  and 0.1  $\mu\text{F}$  low ESR ceramic capacitors in parallel between the driver  $V_{DD}$  and GND. These capacitors should be placed close to the driver to minimize circuit board parasitics and provide a local source for the required current.

#### 4.5 PCB Layout Considerations

Proper Printed Circuit Board (PCB) layout is important in high-current, fast switching circuits to provide proper device operation and robustness of design. Improper component placement may cause errant switching, excessive voltage ringing or circuit latch-up. The PCB trace loop length and inductance should be minimized by the use of ground planes or traces under the MOSFET gate drive signal. Separate analog and power grounds and local driver decoupling should also be used.

Placing a ground plane beneath the MCP14A0153/4/5 devices will help as a radiated noise shield, as well as providing some heat sinking for power dissipated within the device.

#### 4.6 Power Dissipation

The total internal power dissipation in a MOSFET driver is the summation of three separate power dissipation elements, as shown in Equation 4-1.

#### **EQUATION 4-1:**

$$P_T = P_L + P_Q + P_{CC}$$

Where:

$P_T$  = Total power dissipation  $P_L$  = Load power dissipation

P<sub>CC</sub> = Quiescent power dissipation P<sub>CC</sub> = Operating power dissipation

#### 4.6.1 CAPACITIVE LOAD DISSIPATION

The power dissipation caused by a capacitive load is a direct function of the frequency, total capacitive load and supply voltage. The power lost in the MOSFET driver for a complete charging and discharging cycle of a MOSFET is shown in Equation 4-2.

#### **EQUATION 4-2:**

$$P_L = f \times C_T \times V_{DD}^2$$

Where:

f = Switching frequencyC<sub>T</sub> = Total load capacitance

$V_{DD}$  = MOSFET driver supply voltage

#### 4.6.2 QUIESCENT POWER DISSIPATION

The power dissipation associated with the quiescent current draw depends on the state of the Input and Enable pins. See **Section 1.0** "**Electrical Characteristics**" for typical quiescent current draw values in different operating states. The quiescent power dissipation is shown in Equation 4-3.

#### **EQUATION 4-3:**

$$P_Q = (I_{QH} \times D + I_{QL} \times (1 - D)) \times V_{DD}$$

Where:

I<sub>OH</sub> = Quiescent current in the High state

D = Duty cycle

$I_{QL}$  = Quiescent current in the Low state

$V_{DD}$  = MOSFET driver supply voltage

## MCP14A0153/4/5

#### 4.6.3 OPERATING POWER DISSIPATION

The operating power dissipation occurs each time the MOSFET driver output transitions because, for a very short period of time, both MOSFETs in the output stage are on simultaneously. This crossover current leads to a power dissipation described in Equation 4-4.

### **EQUATION 4-4:**

$P_{CC} = V_{DD} \times I_{CO}$

Where:

$I_{CO}$  = Crossover current

$V_{DD}$  = MOSFET driver supply voltage

#### 5.0 PACKAGING INFORMATION

#### 5.1 Package Marking Information

8-Lead MSOP (3x3 mm)

| Code  |

|-------|

| A0153 |

| A0154 |

| A0155 |

|       |

Note: Applies to 8-Lead MSOP

Example

8-Lead SOIC (3.90 mm)

| Device           | Code    |

|------------------|---------|

| MCP14A0153T-E/SN | 14A0153 |

| MCP14A0154T-E/SN | 14A0154 |

| MCP14A0155T-E/SN | 14A0155 |

Note: Applies to 8-Lead SOIC

Example

8-Lead TDFN (2x3x0.75 mm)

| Device            | Code |

|-------------------|------|

| MCP14A0153T-E/MNY | ACU  |

| MCP14A0154T-E/MNY | ACM  |

| MCP14A0155T-E/MNY | ACV  |

Note: Applies to 8-Lead 2x3 TDFN

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

e3 Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

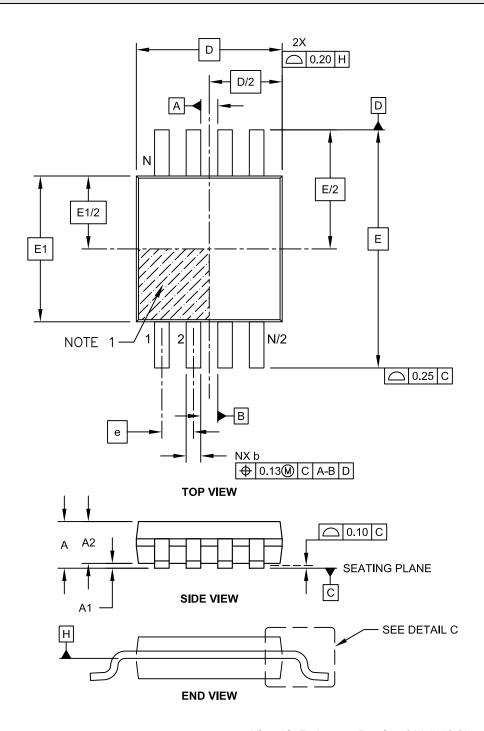

## 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-111C Sheet 1 of 2

#### 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |             |          |      |  |

|--------------------------|------------------|-------------|----------|------|--|

| Dimension                | Dimension Limits |             |          | MAX  |  |

| Number of Pins           | N                |             | 8        |      |  |

| Pitch                    | е                |             | 0.65 BSC |      |  |

| Overall Height           | Α                | ı           | -        | 1.10 |  |

| Molded Package Thickness | A2               | 0.75        | 0.85     | 0.95 |  |

| Standoff                 | A1               | 0.00        | -        | 0.15 |  |

| Overall Width            | Е                | 4.90 BSC    |          |      |  |

| Molded Package Width     | E1               | 3.00 BSC    |          |      |  |

| Overall Length           | D                |             | 3.00 BSC |      |  |

| Foot Length              | L                | 0.40        | 0.60     | 0.80 |  |

| Footprint                | L1               | 0.95 REF    |          |      |  |

| Foot Angle               | φ                | 0° - 8°     |          |      |  |

| Lead Thickness           | С                | 0.08 - 0.23 |          |      |  |

| Lead Width               | b                | 0.22        | -        | 0.40 |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-111C Sheet 2 of 2

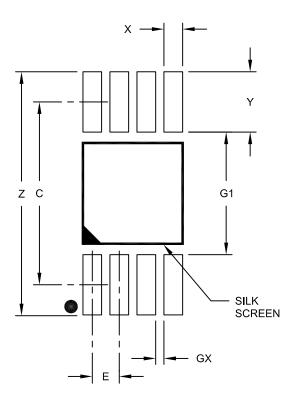

## 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | Units  |           | MILLIMETERS |      |  |

|-------------------------|--------|-----------|-------------|------|--|

| Dimension               | Limits | MIN NOM I |             | MAX  |  |

| Contact Pitch           | E      |           | 0.65 BSC    |      |  |

| Contact Pad Spacing     | С      |           | 4.40        |      |  |

| Overall Width           | Z      |           |             | 5.85 |  |

| Contact Pad Width (X8)  | X1     |           |             | 0.45 |  |

| Contact Pad Length (X8) | Y1     |           |             | 1.45 |  |

| Distance Between Pads   | G1     | 2.95      |             |      |  |

| Distance Between Pads   | GX     | 0.20      |             |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2111A

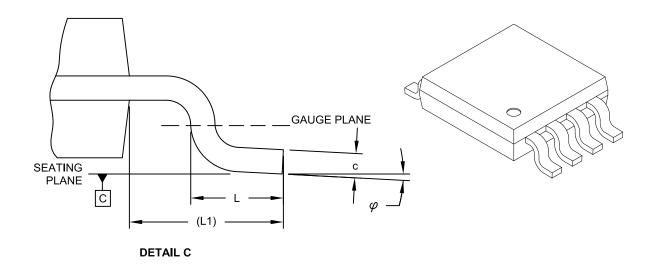

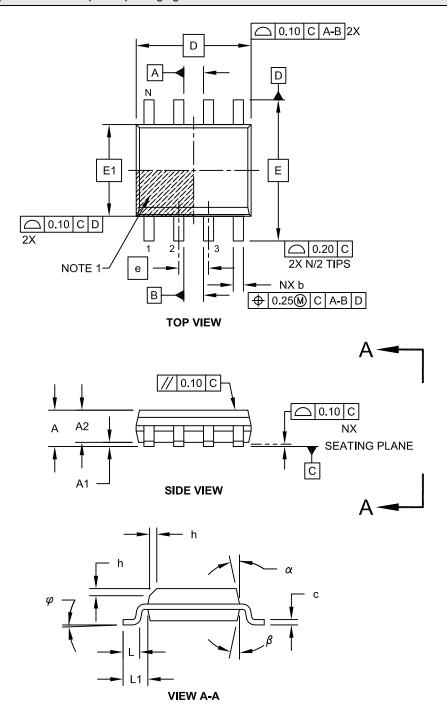

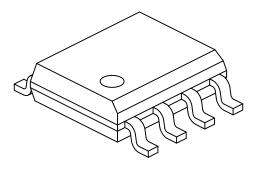

## 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-057C Sheet 1 of 2

## 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |           | MILLIMETERS |     |      |

|--------------------------|-----------|-------------|-----|------|

| Dimension Limits         |           | MIN         | NOM | MAX  |

| Number of Pins           | N         | 8           |     |      |

| Pitch                    | е         | 1.27 BSC    |     |      |

| Overall Height           | Α         | 1.75        |     |      |

| Molded Package Thickness | A2        | 1.25        |     |      |

| Standoff §               | A1        | 0.10        | ı   | 0.25 |

| Overall Width            | Е         | 6.00 BSC    |     |      |

| Molded Package Width     | E1        | 3.90 BSC    |     |      |

| Overall Length           | D         | 4.90 BSC    |     |      |

| Chamfer (Optional)       | h         | 0.25 - 0.50 |     |      |

| Foot Length              | L         | 0.40        | ı   | 1.27 |

| Footprint                | L1        | 1.04 REF    |     |      |

| Foot Angle               | $\varphi$ | 0°          | ı   | 8°   |

| Lead Thickness           | С         | 0.17        | ı   | 0.25 |

| Lead Width               | b         | 0.31        | ı   | 0.51 |

| Mold Draft Angle Top     | α         | 5°          | =   | 15°  |

| Mold Draft Angle Bottom  | β         | 5°          | -   | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-057C Sheet 2 of 2

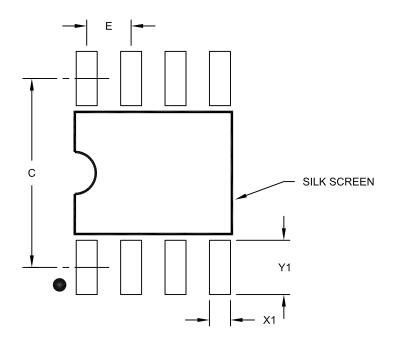

## 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | Units  | Units MILLIMETERS |      | S    |

|-------------------------|--------|-------------------|------|------|

| Dimension               | Limits | MIN NOM MA        |      | MAX  |

| Contact Pitch           | Е      | 1.27 BSC          |      |      |

| Contact Pad Spacing     | С      |                   | 5.40 |      |

| Contact Pad Width (X8)  | X1     |                   |      | 0.60 |

| Contact Pad Length (X8) | Y1     |                   |      | 1.55 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

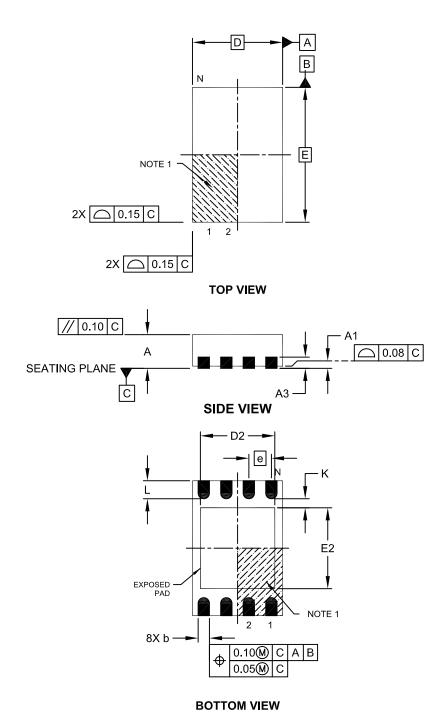

## 8-Lead Plastic Dual Flat, No Lead Package (MN) – 2x3x0.75mm Body [TDFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-129C Sheet 1 of 2

## 8-Lead Plastic Dual Flat, No Lead Package (MN) – 2x3x0.75mm Body [TDFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS |      |      |

|------------------------|------------------|-------------|------|------|

| Dimension              | Dimension Limits |             | NOM  | MAX  |

| Number of Pins         | N                | 8           |      |      |

| Pitch                  | е                | 0.50 BSC    |      |      |

| Overall Height         | Α                | 0.70        | 0.75 | 0.80 |

| Standoff               | A1               | 0.00        | 0.02 | 0.05 |

| Contact Thickness      | A3               | 0.20 REF    |      |      |

| Overall Length         | D                | 2.00 BSC    |      |      |

| Overall Width          | Е                | 3.00 BSC    |      |      |

| Exposed Pad Length     | D2               | 1.20        | ı    | 1.60 |

| Exposed Pad Width      | E2               | 1.20        | ı    | 1.60 |

| Contact Width          | b                | 0.20        | 0.25 | 0.30 |

| Contact Length         | L                | 0.25        | 0.30 | 0.45 |

| Contact-to-Exposed Pad | K                | 0.20        | =    | -    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-129C Sheet 2 of 2

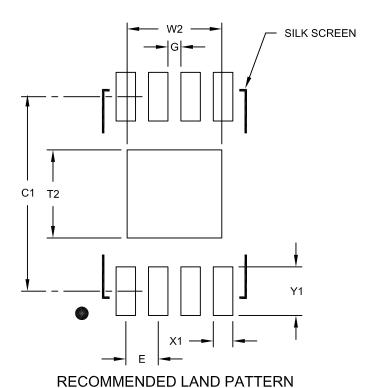

#### 8-Lead Plastic Dual Flat, No Lead Package (MN) - 2x3x0.75 mm Body [TDFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Units **MILLIMETERS Dimension Limits** MIN NOM MAX 0.50 BSC Contact Pitch Ε Optional Center Pad Width W2 1.46 Optional Center Pad Length T2 1.36 3.00 Contact Pad Spacing C1 Contact Pad Width (X8) X1 0.30 Contact Pad Length (X8) Υ1 0.75 Distance Between Pads G 0.20

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2129A

## **APPENDIX A: REVISION HISTORY**

## **Revision A (December 2015)**

· Original release of this document