Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **Obsolete Device**

For further designs, please refer to the MIC24046 or MCP16311/2 Data Sheets

# MCP16321/2

# 24V Input, 1A/2A Output, High Efficiency Synchronous Buck Regulator with Power Good Indication

#### **Features**

- Up to 95% Typical Efficiency

- Input Voltage Range: 6.0V to 24V

- 1A Output Current (MCP16321)

- · 2A Output Current (MCP16322)

- Fixed Output Voltages: 0.9V, 1.5V, 1.8V, 2.5V, 3.3V, 5V with 2% Output Voltage Accuracy

- Adjustable Version Output Voltage Range:

0.9V to 5V with 1.5% Reference Voltage Accuracy

- Integrated N-Channel High-Side Switch: 180 mΩ

- Integrated N-Channel Low-Side Switch: 120 mΩ

- 1 MHz Fixed Frequency

- · Low Device Shutdown Current

- · Peak Current Mode Control

- · Internal Compensation

- · Stable with Ceramic Capacitors

- · Internal Soft-Start

- · Cycle-by-Cycle Peak Current Limit

- Undervoltage Lockout (UVLO): 5.75V

- · Overtemperature Protection

- V<sub>OLIT</sub> Overvoltage Protection

- V<sub>OUT</sub> Voltage Supervisor Reported at the PG Pin

- Available Package: QFN-16 (3x3 mm)

#### **Applications**

- PIC®/dsPIC® Microcontroller Bias Supply

- 12V Industrial Input DC-DC Conversion

- · Set-Top Boxes

- · DSL Cable Modems

- Automotive

- · Wall Cube Regulation

- · SLA Battery Powered Devices

- · AC-DC Digital Control Power Source

- Power Meters

- Consumer

- · Medical and Health Care

- · Distributed Power Supplies

### **Description**

The MCP16321/2 is a highly integrated, high-efficiency, fixed frequency, synchronous step-down DC-DC converter in a 16-pin QFN package that operates from input voltages up to 24V. Integrated features include a high-side and low-side N-Channel switch, fixed frequency Peak Current Mode Control, internal compensation, peak current limit, V<sub>OUT</sub> overvoltage protection and overtemperature protection. Minimal external components are necessary to develop a complete synchronous step-down DC-DC converter power supply.

High converter efficiency is achieved by integrating a high-speed, current limited, low resistance, high-side N-Channel MOSFET, as well as a high-speed, low resistance, low-side N-Channel MOSFET and associated drive circuitry. High switching frequency minimizes the size of the inductor and output capacitor, resulting in a small solution size.

The MCP16321/2 device can supply 1A/2A of continuous current while regulating the output voltage from 0.9V to 5V. A high-performance peak current mode architecture keeps the output voltage tightly regulated, even during input voltage steps and output current transient conditions that are common in power supplies.

The regulator can be turned on and off with a logic level signal applied to the EN input. The EN input is internally pulled up to a 4.2V reference and is rated for a maximum of 6V. With EN low, typically 5  $\mu$ A of current is consumed from the input, making the part ideal for power shedding and load distribution applications. The PG output is an open-drain output pin used to interface with other components of the system, and can be pulled up to a maximum of 6V.

The output voltage can either be fixed at output voltages of 0.9V, 1.5V, 1.8V, 2.5V, 3.3V, 5V or adjustable using an external resistor divider. The MCP16321/2 is offered in a 3x3 QFN-16 surface mount package.

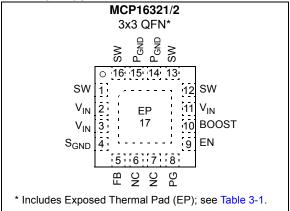

### **Package Type**

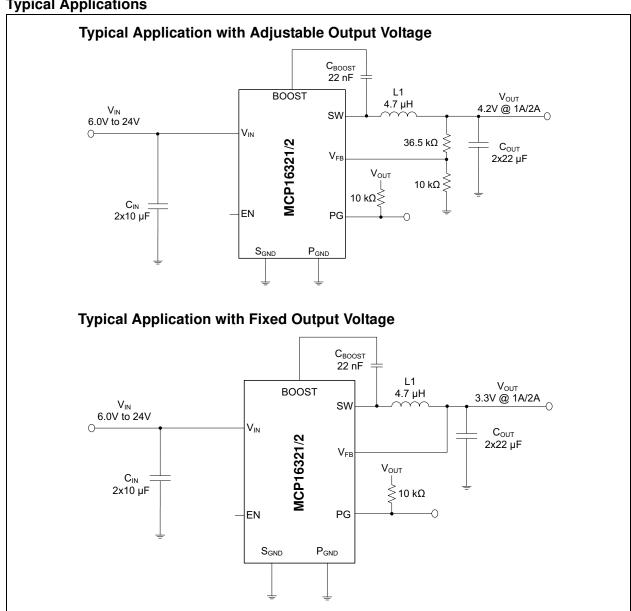

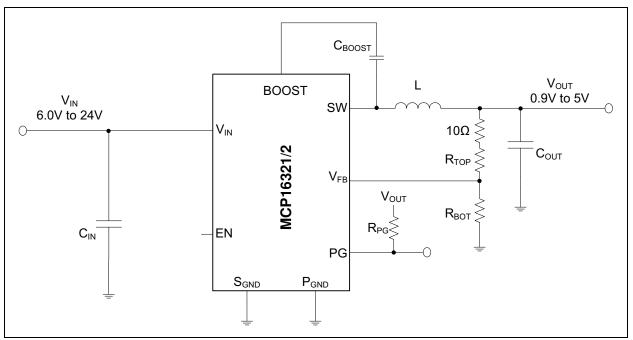

### **Typical Applications**

## 1.0 ELECTRICAL CHARACTERISTICS

### **Absolute Maximum Ratings†**

| V <sub>IN</sub>                 | 0.3V to 26.4V                 |

|---------------------------------|-------------------------------|

| SW                              | 1V to 26.4V                   |

| BOOST – GND                     | 0.3V to (V <sub>IN</sub> +6V) |

| EN,V <sub>FB</sub> , PG Voltage | 0.3V to 6V                    |

| Continuous Total Power Dissipa  | ation                         |

|                                 | See Thermal Characteristics   |

| Storage Temperature             | 65°C to +150°C                |

| Operating Junction Temperature  | e40°C to +125°C               |

| ESD Protection On All Pins:     |                               |

| НВМ                             | 3 kV                          |

| MM                              | 200V                          |

|                                 |                               |

† Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

### DC CHARACTERISTICS

**Electrical Characteristics:** Unless otherwise indicated,  $T_A$  = +25°C,  $V_{IN}$  = 12V,  $V_{OUT}$  = 3.3V,  $I_{OUT}$  = 300 mA, L = 4.7  $\mu$ H,  $C_{OUT}$  = 2x22  $\mu$ F,  $C_{IN}$  = 2x10  $\mu$ F. **Boldface** specifications apply over the  $T_J$  range of -40°C to +125°C.

| Parameters                                | Sym.                 | Min.                  | Тур.                  | Max.                    | Units | Conditions                                               |

|-------------------------------------------|----------------------|-----------------------|-----------------------|-------------------------|-------|----------------------------------------------------------|

| V <sub>IN</sub> Supply Voltage            |                      | •                     |                       |                         |       | •                                                        |

| Input Voltage                             | V <sub>IN</sub>      | 6.0                   | _                     | 24                      | V     |                                                          |

| Quiescent Current<br>(Switching)          | I <sub>Q</sub>       | _                     | 5.2                   | _                       | mA    | I <sub>OUT</sub> = 0 mA                                  |

| Quiescent Current<br>(Non-Switching)      | ΙQ                   | _                     | 2.3                   | _                       | mA    | Closed Loop in<br>Overvoltage<br>I <sub>OUT</sub> = 0 mA |

| Quiescent Current -<br>Shutdown           | IQ                   | _                     | 5                     | 10                      | μA    | EN = 0                                                   |

| V <sub>IN</sub> Undervoltage Lockout      |                      |                       |                       |                         |       |                                                          |

| Undervoltage Lockout Start                | UVLO <sub>STRT</sub> | 5.5                   | 5.75                  | 6.0                     | V     | V <sub>IN</sub> Rising                                   |

| Undervoltage Lockout<br>Hysteresis        | UVLO <sub>HYS</sub>  | _                     | 0.65                  | _                       | V     | Non-Switching                                            |

| Output Characteristics                    |                      |                       |                       |                         |       |                                                          |

| Maximum Output Current MCP16321           | I <sub>OUT</sub>     | 1                     | _                     | _                       | Α     | V <sub>IN</sub> = 6V to 24V                              |

| Maximum Output Current MCP16322           | I <sub>OUT</sub>     | 2                     | _                     | _                       | Α     | V <sub>IN</sub> = 6V to 24V                              |

| Output Voltage Adjust Range               | V <sub>OUT</sub>     | 0.9                   | _                     | 5.0                     | V     |                                                          |

| Output Voltage Tolerance in PWM Mode      | V <sub>OUT-PWM</sub> | V <sub>OUT</sub> - 2% | V <sub>OUT</sub>      | V <sub>OUT</sub> + 2%   | V     | I <sub>OUT</sub> = 1A                                    |

| Output Voltage Tolerance in PFM Mode      | V <sub>OUT-PFM</sub> | V <sub>OUT</sub> - 1% | V <sub>OUT</sub> + 1% | V <sub>OUT</sub> + 3.5% | V     | I <sub>OUT</sub> = 0A                                    |

| Feedback Voltage                          | $V_{FB}$             | 0.886                 | 0.9                   | 0.914                   | V     |                                                          |

| Feedback Reference<br>Tolerance           | V <sub>FB-TOL</sub>  | -1.5                  | _                     | 1.5                     | %     |                                                          |

| PFM Mode Feedback<br>Comparator Threshold | $V_{FB-PFM}$         | _                     | V <sub>OUT</sub> + 1% | _                       | V     |                                                          |

| Feedback Input Bias<br>Current            | I <sub>FB</sub>      | _                     | 100                   | _                       | nA    |                                                          |

Note 1: Regulator SW pin is forced off for 240 ns every eight cycles to ensure the BOOST cap is replenished.

### **DC CHARACTERISTICS (CONTINUED)**

**Electrical Characteristics:** Unless otherwise indicated, T<sub>A</sub> = +25°C, V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 3.3V, I<sub>OUT</sub> = 300 mA, L = 4.7 µH, C<sub>OUT</sub> = 2x22 µF, C<sub>IN</sub> = 2x10 µF, **Boldface** specifications apply over the T<sub>1</sub> range of -40°C to +125°C.

| L = 4.7 $\mu$ H, C <sub>OUT</sub> = 2x22 $\mu$ F, C <sub>I</sub> | <sub>N</sub> = 2x10 μF. <b>Boldfa</b> | ce specificat        | tions apply ove       | er the T <sub>J</sub> rang | e of -40 | °C to +125°C.                              |

|------------------------------------------------------------------|---------------------------------------|----------------------|-----------------------|----------------------------|----------|--------------------------------------------|

| Parameters                                                       | Sym.                                  | Min.                 | Тур.                  | Max.                       | Units    | Conditions                                 |

| PFM Mode Feedback                                                | V <sub>FB-PFM</sub>                   | _                    | V <sub>OUT</sub> + 1% | _                          | V        |                                            |

| EN Input Characteristics                                         | 1                                     | ľ                    |                       |                            |          |                                            |

| EN Input Logic High                                              | V <sub>IH</sub>                       | 2.2                  | _                     |                            | V        |                                            |

| EN Input Logic Low                                               | V <sub>IL</sub>                       | _                    | _                     | 0.8                        | V        |                                            |

| EN Input Hysteresis                                              | V <sub>EN-HYST</sub>                  | _                    | 480                   | _                          | mV       |                                            |

| EN Input Leakage Current                                         | I <sub>ENLK</sub>                     | _                    | 3.5                   | _                          | μA       | V <sub>EN</sub> = 5V                       |

|                                                                  |                                       | _                    | -1.5                  | _                          | μA       | V <sub>EN</sub> = 0V                       |

| Soft-Start Time                                                  | t <sub>SS</sub>                       | _                    | 4                     | _                          | ms       |                                            |

| Switching Characteristics                                        |                                       |                      |                       |                            |          |                                            |

| Switching Frequency                                              | f <sub>SW</sub>                       | 0.9                  | 1                     | 1.1                        | MHz      | Open Loop V <sub>FB</sub><br>Low           |

| Maximum Duty Cycle                                               | DC <sub>MAX</sub>                     | 95                   | 97                    | 99                         | %        | Open Loop V <sub>FB</sub><br>Low<br>Note 1 |

| Minimum Duty Cycle                                               |                                       | _                    | 7                     | _                          | %        |                                            |

| NMOS Low-Side<br>Switch On Resistance                            | Low-Side R <sub>DS(ON)</sub>          | _                    | 120                   | _                          | mΩ       |                                            |

| NMOS High-Side<br>Switch On Resistance                           | High-Side<br>R <sub>DS(ON)</sub>      | _                    | 180                   | _                          | mΩ       |                                            |

| NMOS High-Side                                                   | I <sub>N(MAX)</sub>                   | 1.4                  | 1.8                   | 2.4                        | Α        | MCP16321                                   |

| Switch Current Limit                                             | , ,                                   | 2.4                  | 2.8                   | 3.4                        | Α        | MCP16322                                   |

| PG Output Characteristics                                        |                                       |                      |                       |                            | •        |                                            |

| PG Low-level<br>Output Voltage                                   | PG <sub>IL</sub>                      | _                    | _                     | 0.01                       | V        | $I_{PG}$ = -0.3 mA                         |

| PG High-Level Output Leak-<br>age Current                        | I <sub>PGLK</sub>                     | _                    | 0.5                   | _                          | μA       | V <sub>PG</sub> = 5V                       |

| PG Release Timer                                                 | t <sub>PG</sub>                       | _                    | 10                    | _                          | ms       |                                            |

| V <sub>OUT</sub> Undervoltage Threshold                          | V <sub>OUT-UV</sub>                   | 91% V <sub>OUT</sub> | 93% V <sub>OUT</sub>  | 95% V <sub>OUT</sub>       |          |                                            |

| V <sub>OUT</sub> Undervoltage<br>Hysteresis                      | V <sub>OUT-UV_HYST</sub>              | _                    | 1.5% V <sub>OUT</sub> | _                          |          |                                            |

| V <sub>OUT</sub> Overvoltage<br>Threshold                        | V <sub>OUT-OV</sub>                   | _                    | 103% V <sub>OUT</sub> | _                          |          |                                            |

| V <sub>OUT</sub> Overvoltage<br>Hysteresis                       | V <sub>OUT-OV_HYST</sub>              | _                    | 1% V <sub>OUT</sub>   | _                          |          |                                            |

| Thermal Characteristics                                          | •                                     | •                    |                       |                            | •        | •                                          |

| Thermal Shutdown Die Temperature                                 | T <sub>SD</sub>                       | _                    | 170                   | _                          | °C       |                                            |

| Die Temperature<br>Hysteresis                                    | T <sub>SDHYS</sub>                    | _                    | 10                    | _                          | °C       |                                            |

|                                                                  |                                       |                      |                       |                            |          |                                            |

**Note 1:** Regulator SW pin is forced off for 240 ns every eight cycles to ensure the BOOST cap is replenished.

TABLE 1-1: TEMPERATURE CHARACTERISTICS

| Electrical Characteristics           |                   |      |      |      |       |              |

|--------------------------------------|-------------------|------|------|------|-------|--------------|

| Parameters                           | Sym.              | Min. | Тур. | Max. | Units | Conditions   |

| Temperature Ranges                   |                   |      |      |      |       |              |

| Operating Junction Temperature Range | TJ                | -40  | _    | 125  | °C    | Steady State |

| Storage Temperature Range            | T <sub>A</sub>    | -65  | _    | 150  | °C    |              |

| Maximum Junction Temperature         | TJ                | _    | _    | 150  | °C    | Transient    |

| Package Thermal Resistances          |                   |      |      |      |       |              |

| Thermal Resistance, 16L 3x3-QFN      | $\theta_{\sf JA}$ | _    | 38.5 | _    | °C/W  | Note 1       |

**Note 1:** Measured using a 4-layer FR4 Printed Circuit Board with a 13.5 in<sup>2</sup>, 1 oz internal copper ground plane.

**NOTES:**

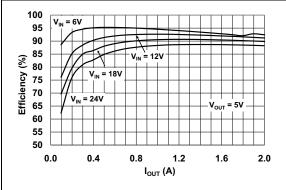

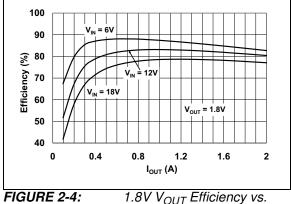

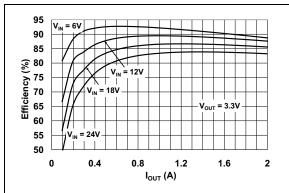

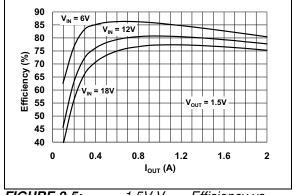

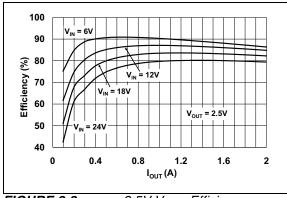

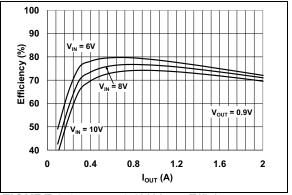

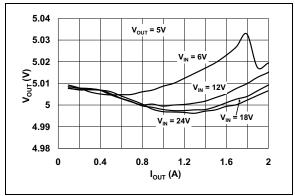

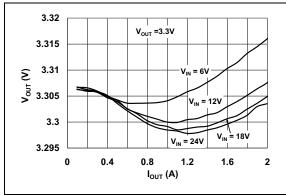

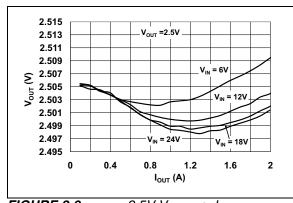

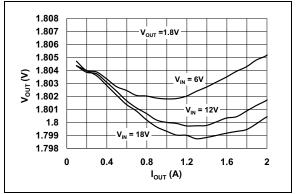

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

FIGURE 2-1: 5V V<sub>OUT</sub> Efficiency vs. I<sub>OUT</sub>.

**FIGURE 2-4:** 1.8V  $V_{OUT}$  Efficiency vs.  $I_{OUT}$ .

FIGURE 2-2: 3.3V V<sub>OUT</sub> Efficiency vs. I<sub>OUT</sub>.

**FIGURE 2-5:** 1.5V V<sub>OUT</sub> Efficiency vs. I<sub>OUT</sub>.

**FIGURE 2-3:** 2.5V V<sub>OUT</sub> Efficiency vs. I<sub>OUT</sub>.

FIGURE 2-6: 0.9V V<sub>OUT</sub> Efficiency vs. I<sub>OUT</sub>.

FIGURE 2-7:  $5V V_{OUT} vs. I_{OUT}$ .

**FIGURE 2-8:** 3.3V V<sub>OUT</sub> vs. I<sub>OUT</sub>.

**FIGURE 2-9:** 2.5V V<sub>OUT</sub> vs. I<sub>OUT</sub>.

**FIGURE 2-10:** 1.8V V<sub>OUT</sub> vs. I<sub>OUT</sub>.

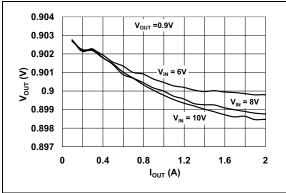

**FIGURE 2-11:** 1.5V V<sub>OUT</sub> vs. I<sub>OUT</sub>.

**FIGURE 2-12:** 0.9V V<sub>OUT</sub> vs. I<sub>OUT</sub>.

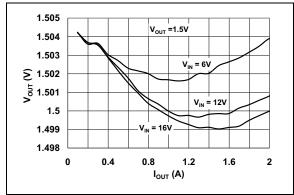

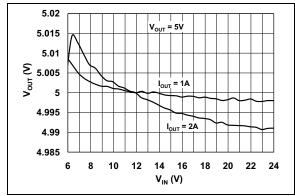

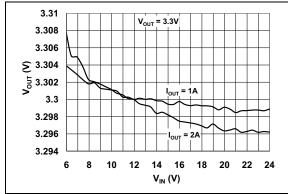

FIGURE 2-13: 5V V<sub>OUT</sub> vs V<sub>IN.</sub>

**FIGURE 2-14:** 3.3V V<sub>OUT</sub> vs V<sub>IN.</sub>

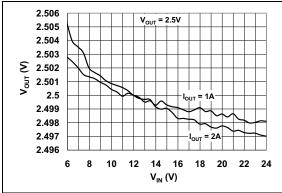

**FIGURE 2-15:** 2.5V V<sub>OUT</sub> vs V<sub>IN.</sub>

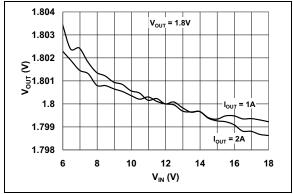

**FIGURE 2-16:** 1.8V  $V_{OUT}$  vs  $V_{IN}$ .

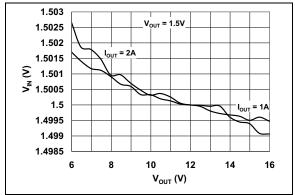

**FIGURE 2-17:** 1.5V  $V_{OUT}$  vs  $V_{IN}$ .

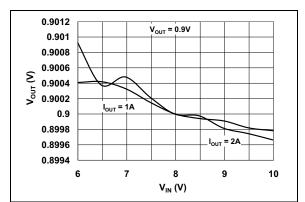

**FIGURE 2-18:** 0.9V V<sub>OUT</sub> vs V<sub>IN.</sub>

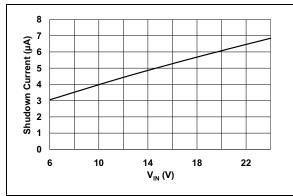

FIGURE 2-19: Shutdown Current vs. Input Voltage.

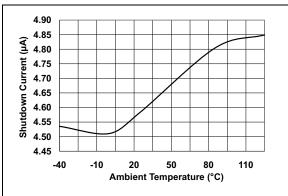

FIGURE 2-20: Shutdown Current vs. Temperature.

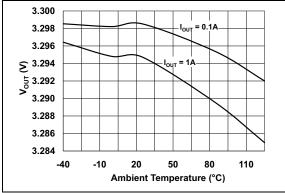

FIGURE 2-21: Output Voltage vs. Temperature.

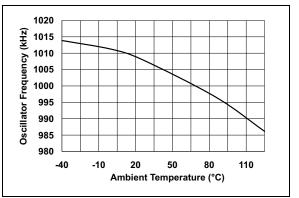

**FIGURE 2-22:** Oscillator Frequency vs. Temperature ( $I_{OUT} = 300 \text{ mA}$ ).

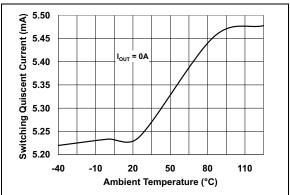

FIGURE 2-23: Input Quiescent Current vs. Temperature (No Load, Switching).

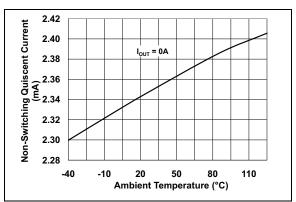

FIGURE 2-24: Input Current vs. Temperature (No Load, No Switching).

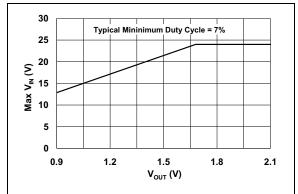

**FIGURE 2-25:** Maximum V<sub>IN</sub> to V<sub>OUT</sub> Ratio for Continuous Switching.

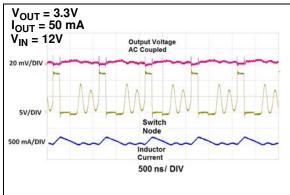

FIGURE 2-26: Light Load Switching Waveforms.

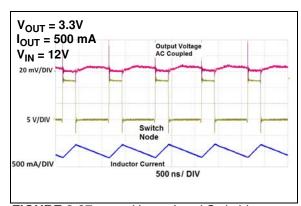

FIGURE 2-27: Heavy Load Switching Waveforms.

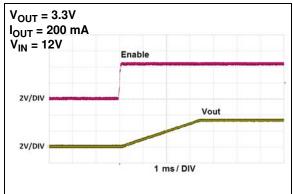

FIGURE 2-28: Start-up From Enable.

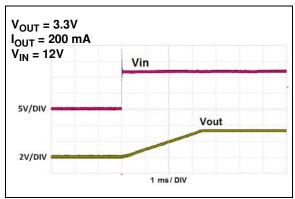

**FIGURE 2-29:** Start-up From  $V_{IN}$

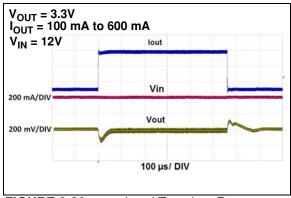

FIGURE 2-30: Load Transient Response.

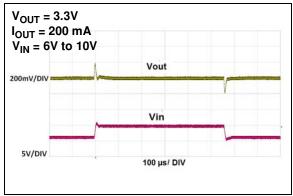

FIGURE 2-31: Line Transient Response.

#### 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| MCP16321/2<br>3x3 QFN | Symbol          | Description                                                                                                                                                 |  |  |  |

|-----------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                     | SW              | Output switch node, connects to the inductor and the bootstrap capacitor                                                                                    |  |  |  |

| 2                     | $V_{IN}$        | Input supply voltage pin for power and internal biasing                                                                                                     |  |  |  |

| 3                     | $V_{IN}$        | Input supply voltage pin for power and internal biasing                                                                                                     |  |  |  |

| 4                     | SGND            | Primary signal ground                                                                                                                                       |  |  |  |

| 5                     | $V_{FB}$        | Output voltage feedback pin. Connect $V_{\text{FB}}$ to $V_{\text{OUT}}$ for fixed version and output resistor divider for adjustable version.              |  |  |  |

| 6                     | NC              | No Connection                                                                                                                                               |  |  |  |

| 7                     | NC              | No Connection                                                                                                                                               |  |  |  |

| 8                     | PG              | Power Good open-drain output, pulled up to a maximum of 6V                                                                                                  |  |  |  |

| 9                     | EN              | Enable input pin. Logic high enables the operation. Internally pulled up, pull EN pin low to disable regulator's output. Maximum voltage on EN input is 6V. |  |  |  |

| 10                    | BOOST           | Boost voltage that drives the internal NMOS control switch. A bootstrap capacitor is connected between the BOOST and SW pins.                               |  |  |  |

| 11                    | V <sub>IN</sub> | Input supply voltage pin for power and internal biasing                                                                                                     |  |  |  |

| 12                    | SW              | Output switch node, connects to the inductor and the bootstrap capacitor                                                                                    |  |  |  |

| 13                    | SW              | Output switch node, connects to the inductor and the bootstrap capacitor                                                                                    |  |  |  |

| 14                    | PGND            | GND supply for the internal low-side NMOS/integrated diode                                                                                                  |  |  |  |

| 15                    | PGND            | GND supply for the internal low-side NMOS/integrated diode                                                                                                  |  |  |  |

| 16                    | SW              | Output switch node, connects to the inductor and the bootstrap capacitor                                                                                    |  |  |  |

| 17                    | EP              | Exposed Thermal Pad (EP); must be connected to GND                                                                                                          |  |  |  |

### 3.1 Switch Pin (SW)

The drain of the low-side N-Channel switch is connected internally to the source of the high-side N-Channel switch, and externally to the SW node, consisting of the inductor and bootstrap capacitor. The SW node can rise very fast as a result of the internal high-side switch turning on. It should be connected directly to the 4.7  $\mu H$  inductor with a wide, short trace.

## 3.2 Power Supply Input Voltage Pin (V<sub>IN</sub>)

Connect the input voltage source to  $V_{IN}$ . The input source should be decoupled to GND using 2 x 10  $\mu$ F capacitors. The amount of the capacitance depends on the impedance of the source and output current. The input capacitors provide AC current for the high-side power switch and a stable voltage source for the internal device power. This capacitor should be connected as close as possible to the  $V_{IN}$  and GND pins.

### 3.3 Signal Ground Pin (S<sub>GND</sub>)

This ground is used for the majority of the device, including the analog reference, control loop, and other circuits.

#### 3.4 Feedback Voltage Pin (V<sub>FB</sub>)

The  $V_{FB}$  input pin is used to provide output voltage regulation by either using a resistor divider or  $V_{OUT}$  directly. For the adjustable version, the  $V_{FB}$  will be 0.9V typical with the output voltage in regulation. For the fixed version, the  $V_{FB}$  will be equal to the corresponding  $V_{OUT}$  value.

#### 3.5 Power Good Pin (PG)

PG is an open-drain, active-low output. The regulator output voltage is monitored and the PG line will remain low until the output voltage reaches the  $V_{OUT-UV}$  threshold. Once the internal comparator detects that the output voltage is above the  $V_{OUT-UV}$  threshold, an internal delay timer is activated. After a 10 ms delay, the PG open-drain output pin can be pulled high, indicating that the output voltage is in regulation. The maximum voltage applied to the PG output pin should not exceed 6V.

#### 3.6 Enable Pin (EN)

The EN input pin is a logic-level input used to enable or disable the device. A logic high (> 2.2V) will enable the regulator output, while a logic low (< 0.8V) will ensure that the regulator is disabled. This pin is internally pulled up to an internal reference and will be enabled when  $V_{\text{IN}}$  > UVLO, unless the EN pin is pulled low. The maximum input voltage applied to the EN pin should not exceed 6V.

### 3.7 BOOST Pin (BOOST)

This pin will provide the bootstrap voltage required for driving the upper internal NMOS switch of the buck regulator. An external ceramic capacitor placed between the BOOST input pin and the SW pin will provide the necessary drive voltage for the upper switch. During steady state operation, the capacitor is recharged on every low-side, synchronous switching cycle. If the Switch mode approaches 100% duty cycle for the high-side MOSFET, the device will automatically reduce the duty cycle switch to a minimum off time of 240 ns on every 8<sup>th</sup> cycle to recharge the boost capacitor.

### 3.8 Power Ground Pin (P<sub>GND</sub>)

This is a separate ground connection used for the lowside synchronous switch to isolate switching noise from the rest of the device.

#### 3.9 Exposed Thermal Pad (EP)

There is no internal electrical connection between the Exposed Thermal Pad (EP) and the  $P_{GND}$  and  $S_{GND}$  pins. The EP must be connected to GND on the Printed Circuit Board (PCB).

#### 4.0 DETAILED DESCRIPTION

#### 4.1 Device Overview

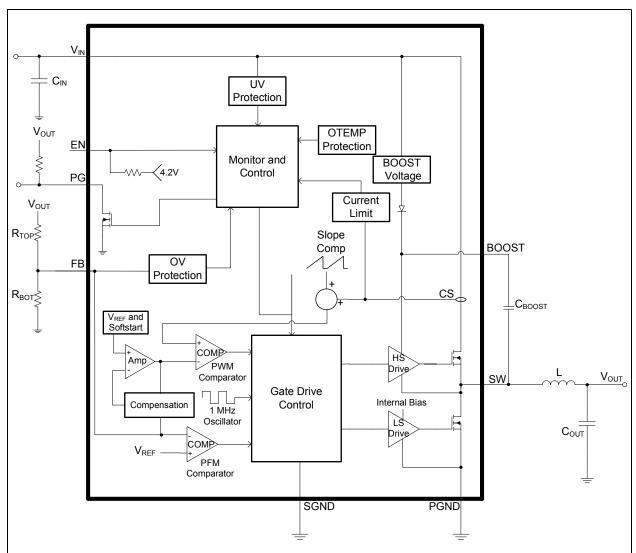

The MCP16321/2 is a high-input voltage, step-down regulator, capable of supplying 1A/2A to a regulated output voltage from 0.9V to 5V. Internally, the 1 MHz oscillator provides a fixed frequency, while the Peak Current Mode Control architecture varies the duty cycle for output voltage regulation. An internal floating driver is used to turn the high-side integrated N-Channel MOSFET on and off. The power for this driver is derived from an external boost capacitor whose energy is replenished when the low-side N-Channel MOSFET is turned on. When the maximum duty cycle approaches 100%, the boost capacitor is replenished for 240 ns after every eight cycles.

## 4.1.1 INTERNAL REFERENCE VOLTAGE $V_{RFF}$

For the adjustable version, an integrated precise 0.9V reference combined with an external resistor divider sets the desired converter output voltage. The resistor divider can vary without affecting the control system gain. High-value resistors consume less current, but are more susceptible to noise. For the fixed version, an integrated precise voltage reference is set to the desired  $V_{\rm OUT}$  value and is directly connected to  $V_{\rm OUT}$ .

#### 4.1.2 INTERNAL COMPENSATION

All control system components necessary for stable operation over the entire device operating range are integrated, including the error amplifier and inductor current slope compensation.

#### 4.1.3 EXTERNAL COMPONENTS

External components consist of:

- · Input capacitor

- · Output filter (inductor and capacitor)

- · Boost capacitor

- Resistor divider (adjustable version only)

The selection of the external inductor, output capacitor, input capacitor and boost capacitor is dependent upon the output voltage and the maximum output current.

#### 4.1.4 ENABLE INPUT

The enable input (EN) is used to disable the device. If disabled, the device consumes a minimal current from the input. Once enabled, the internal soft start controls the output voltage rate of rise, preventing high-inrush current and output voltage overshoot. The EN is internally pulled up or enabled; to disable the converter, it must be pulled low.

#### 4.1.5 SOFT START

The internal reference voltage rate of rise is controlled during start-up, minimizing the output voltage overshoot and the inrush current.

## 4.1.6 OUTPUT OVER VOLTAGE PROTECTION

If the output of the regulator exceeds 103% of the regulation voltage, the SW outputs will tri-state to protect the device from damage. This check occurs at the start of each switching cycle.

#### 4.1.7 INPUT UNDERVOLTAGE LOCKOUT

An integrated Undervoltage Lockout (UVLO) prevents the converter from starting until the input voltage is high enough for normal operation. The converter will typically start at 5.75V (typical) and operate down to 5.25V (typical). Hysteresis of 500 mV (typical) is added to prevent starting and stopping during start-up, as a result of loading the input voltage source.

#### 4.1.8 MINIMUM DUTY CYCLE

A minimum duty cycle of 70 ns typical prevents the device from constant switching for high step-down voltage ratios. Duty cycles less than this minimum will initiate pulse skipping to maintain output voltage regulation, resulting in higher output voltage ripple. Duty cycle for continuous inductor current operation is approximated by  $V_{\rm OUT}/V_{\rm IN}.$  For a 1 MHz switching frequency or 1  $\mu s$  period, this results in a 7% duty cycle minimum. Maximum  $V_{\rm IN}$  for continuous switching can be approximated dividing  $V_{\rm OUT}$  by the minimum duty cycle or 7%. For example, the maximum input voltage for continuous switching for a 1.5V output is equal to approximately 21V.

## 4.1.9 OVERTEMPERATURE PROTECTION

Overtemperature protection limits the silicon die temperature to +170°C by turning the converter off. The normal switching resumes at +160°C.

FIGURE 4-1: MCP16321/2 Block Diagram.

#### 4.2 Functional Description

## 4.2.1 STEP-DOWN OR BUCK CONVERTER

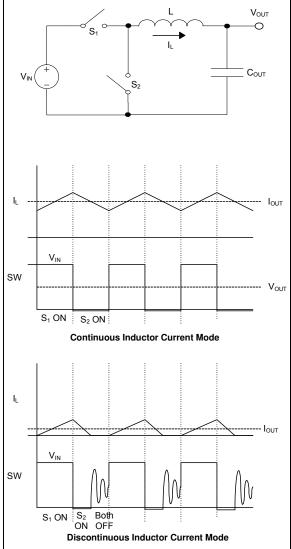

The MCP16321/2 is a synchronous, step-down or buck converter capable of stepping input voltages ranging from 6V to 24V down to 0.9V to 5V.

The integrated high-side switch is used to chop or modulate the input voltage using a controlled duty cycle for output voltage regulation. The integrated low-side switch is used to freewheel current when the high-side switch is turned off. High efficiency is achieved by using low-resistance switches and low equivalent series resistance (ESR), inductor and capacitors. When the high-side switch is turned on, a DC voltage is applied to the inductor (V<sub>IN</sub> – V<sub>OUT</sub>), resulting in a positive linear ramp of inductor current. When the high-side switch turns off and the low-side switch turns on, the applied inductor voltage is equal to -VOUT, resulting in a negative linear ramp of inductor current. In order to ensure there is no shoot-through current, a dead time where both switches are off is implemented between the high-side switch turning off and the low-side switch turning on, and the low-side switch turning off and the high-side switch turning on.

For steady-state, continuous inductor operation, the positive inductor current ramp must equal the negative current ramp in magnitude. While operating in steady state, the switch duty cycle must be equal to the relationship of V<sub>OUT</sub>/V<sub>IN</sub> for constant output voltage regulation, under the condition that the inductor current is continuous, or never reaches zero. For discontinuous inductor current operation, the steady-state duty cycle will be less than V<sub>OUT</sub>/V<sub>IN</sub> to maintain voltage regulation. When the inductor current reaches zero, the low-side switch is turned off so that current does not flow in the reverse direction, keeping the efficiency high. The average of the chopped input voltage or SW node voltage is equal to the output voltage, while the average inductor current is equal to the output current.

FIGURE 4-2: Synchronous Step-Down Converter.

#### 4.2.2 PEAK CURRENT MODE CONTROL

The MCP16321/2 integrates a Peak Current Mode Control architecture, resulting in superior AC regulation while minimizing the number of voltage loop compensation components, and their size, for integration. Peak Current Mode Control takes a small portion of the inductor current, replicates it and compares this replicated current sense signal with the output of the integrated error voltage. In practice, the inductor current and the internal switch current are equal during the switch-on time. By adding this peak current sense to the system control, the step-down power train system can be approximated by a 1<sup>st</sup> order system rather than a 2<sup>nd</sup> order system. This reduces the system complexity and increases its dynamic performance.

For Pulse-Width Modulation (PWM) duty cycles that exceed 50%, the control system can become bimodal, where a wide pulse followed by a short pulse repeats instead of the desired fixed pulse width. To prevent this mode of operation, an internal compensating ramp is summed into the current sense signal.

## 4.2.3 PULSE WIDTH MODULATION (PWM)

The internal oscillator periodically starts the switching period, which in the MCP16321/2's case occurs every 1 µs or 1 MHz. With the high-side integrated N-Channel MOSFET turned on, the inductor current ramps up until the sum of the current sense and slope compensation ramp exceeds the integrated error amplifier output. Once this occurs, the high-side switch turns off and the low-side switch turns on. The error amplifier output slews up or down to increase or decrease the inductor peak current feeding into the output LC filter. If the regulated output voltage is lower than its target, the inverting error amplifier output rises. This results in an increase in the inductor current to correct for errors in the output voltage. The fixed frequency duty cycle is terminated when the sensed inductor peak current, summed with the internal slope compensation, exceeds the output voltage of the error amplifier. The PWM latch is set by turning off the highside internal switch and preventing it from turning on until the beginning of the next cycle.

#### 4.2.4 HIGH-SIDE DRIVE

The MCP16321/2 features an integrated high-side N-Channel MOSFET for high efficiency step-down power conversion. An N-Channel MOSFET is used for its low resistance and size (instead of a P-Channel MOSFET). The N-Channel MOSFET gate must be driven above its source to fully turn on the device, resulting in a gate-drive voltage above the input to turn on the high-side N-Channel. The high-side N-Channel source is connected to the inductor and boost cap or switch node. When the high-side switch is off and the low-side is on, the inductor current flows through the low-side switch, providing a path to recharge the boost cap from the boost voltage source. An internal boostblocking diode is used to prevent current flow from the boost cap back into the output during the internal switch-on time. Prior to start-up, the boost cap has no stored charge to drive the switch. An internal regulator is used to "pre-charge" the boost cap. Once precharged, the switch is turned on and the inductor current flows. When the high-side switch turns off and the low-side turns on, current freewheels through the inductor and low-side switch, providing a path to recharge the boost cap. When the duty cycle approaches its maximum value, there is very little time for the boost cap to be recharged due to the short amount time that the low-side switch is on. Therefore, when the maximum duty cycle approaches, the switch node is forced off for 240 ns every eight cycles to ensure that the boost cap gets replenished.

### 5.0 APPLICATION INFORMATION

#### 5.0.1 TYPICAL APPLICATIONS

The MCP16321/2 synchronous step-down converter operates over a wide input range, up to 24V maximum. Typical applications include generating a bias or  $\rm V_{DD}$  voltage for  $\rm PIC^{\circledR}$  microcontrollers, digital control system bias supply for AC-DC converters and 12V industrial input and similar applications.

## 5.0.2 ADJUSTABLE OUTPUT VOLTAGE CALCULATIONS

To calculate the resistor divider values for the MCP16321/2 adjustable version, use Equation 5-1.  $R_{TOP}$  is connected to  $V_{OUT},\ R_{BOT}$  is connected to SGND, and both are connected to the  $V_{FB}$  input pin.

## EQUATION 5-1: RESISTOR DIVIDER CALCULATION

$$V_{OUT} = V_{FB} \times \left(1 + \frac{R_{TOP}}{R_{BOT}}\right)$$

### **EXAMPLE 5-1: 2.0V RESISTOR DIVIDER**

$V_{OUT} = 2.0V$

$V_{FB} = 0.9V$

$R_{BOT} = 10 k\Omega$

$R_{TOP} = 12.2 \text{ k}\Omega \text{ (standard value = } 12.3 \text{ k}\Omega)$

$V_{OUT}$  = 2.007V (using standard values)

### **EXAMPLE 5-2:** 4.2V RESISTOR DIVIDER

$V_{OLIT} = 4.2V$

$V_{FB} = 0.9V$

$R_{BOT} = 10 k\Omega$

$R_{TOP} = 36.7 \text{ k}\Omega \text{ (standard value = } 36.5 \text{ k}\Omega)$

$V_{OUT}$  = 4.185V (using standard values)

The error amplifier is internally compensated to ensure loop stability. External resistor dividers, inductance and output capacitance, all have an impact on the control system and should be selected carefully and evaluated for stability. A 10  $k\Omega$  resistor is recommended as a good trade-off for quiescent current and noise immunity.

#### 5.0.3 GENERAL DESIGN EQUATIONS

The step-down converter duty cycle can be estimated using Equation 5-2 while operating in Continuous Inductor Current Mode. This equation accounts for the forward drop of two internal N-Channel MOSFETS. As load current increases, the voltage drop in both internal switches will increase, requiring a larger PWM duty cycle to maintain the output voltage regulation. Switch voltage drop is estimated by multiplying the switch current times the switch resistance or R<sub>DSON</sub>.

## EQUATION 5-2: CONTINUOUS INDUCTOR CURRENT DUTY CYCLE

$$D = \frac{V_{OUT} + (I_{LSW} \times R_{DSONL})}{V_{IN} - (I_{HSW} \times R_{DSONH})}$$

#### 5.0.4 INPUT CAPACITOR SELECTION

The step-down converter input capacitor must filter the high-input ripple current, as a result of pulsing or chopping the input voltage. The MCP16321/2 input voltage pin is used to supply voltage for the power train and as a source for internal bias. A low equivalent series resistance (ESR), preferably a ceramic capacitor, is recommended. The necessarv capacitance is dependent upon the maximum load current and source impedance. Three capacitor parameters to keep in mind are the voltage rating, equivalent series resistance and the temperature rating. For wide temperature range applications, a multilayer X7R dielectric is recommended, while for applications with limited temperature range, a multilayer X5R dielectric is acceptable. The input capacitor voltage rating must be V<sub>IN</sub> plus margin.

#### 5.0.5 OUTPUT CAPACITOR SELECTION

The output capacitor provides a stable output voltage during sudden load transients, and reduces the output voltage ripple. As with the input capacitor, X5R and X7R ceramic capacitors are well suited for this application.

The MCP16321/2 is internally compensated, so the output capacitance range is limited. See **TABLE 5-1:** "Capacitor Value Range" for the recommended output capacitor range.

The amount and type of output capacitance and equivalent series resistance will have a significant effect on the output ripple voltage and system stability. The range of the output capacitance is limited due to the integrated compensation of the MCP16321/2.

The output voltage capacitor rating should be a minimum of  $V_{\mbox{\scriptsize OUT}}$  plus margin.

TABLE 5-1: CAPACITOR VALUE RANGE

| Parameter       | Min  | Max  |

|-----------------|------|------|

| C <sub>IN</sub> | 8 µF | None |

TABLE 5-1: CAPACITOR VALUE RANGE

| Parameter        | Min   | Max  |

|------------------|-------|------|

| C <sub>OUT</sub> | 33 µF | None |

#### 5.0.6 INDUCTOR SELECTION

The MCP16321/2 is designed to be used with small surface mount inductors. Several specifications should be considered prior to selecting an inductor. To optimize system performance, low ESR inductors should be used.

EQUATION 5-3: INDUCTOR CURRENT RIPPLE

$$\Delta I_L = \frac{V_L}{L} \times t_{ON}$$

## EXAMPLE 5-3: MCP16321 PEAK INDUCTOR CURRENT – 1A

$$V_{IN} = 12V$$

$$V_{OUT} = 3.3V$$

$$I_{OUT} = 1A$$

$$L = 4.7 \mu H$$

$$I_{LPK} = \frac{\Delta I_L}{2} + I_{OUT}$$

Inductor ripple current = 509 mA Inductor peak current = 1.255A

An inductor saturation rating minimum of 1.255A is recommended. A trade-off between size, cost and efficiency is made to achieve the desired results.

## EXAMPLE 5-4: MCP16322 PEAK INDUCTOR CURRENT – 2A

$$V_{IN}$$

= 12V

$V_{OUT}$  = 3.3V

$I_{OUT}$  = 2A

$L$  = 4.7  $\mu$ H

$$I_{LPK} = \frac{\Delta I_L}{2} + I_{OUT}$$

Inductor ripple current = 509 mA Inductor peak current = 2.255A

An inductor saturation rating minimum of 2.255A is recommended. A trade-off between size, cost and efficiency is made to achieve the desired results.

TABLE 5-2: MCP16321 RECOMMENDED INDUCTORS

| Part<br>Number         | Value<br>(μΗ)      | DCR<br>(Ω) | I <sub>SAT</sub> (A) | Size<br>WxLxH<br>(mm) |

|------------------------|--------------------|------------|----------------------|-----------------------|

| Coilcraft <sup>®</sup> |                    |            |                      |                       |

| 1008PS                 | 4.7                | 0.35       | 1.7                  | 3.81x3.78x2.74        |

| LPS4012                | 4.7                | 0.175      | 1.8                  | 4.1x4.1x1.2           |

| LPS4018                | 4.7                | 0.125      | 1.9                  | 4.1x4.1x1.8           |

| LPS5015                | 4.7                | 0.15       | 1.8                  | 5x5x1.5               |

| MSS5121                | 4.7                | 0.095      | 1.66                 | 5.1x5.1x2.2           |

| LPS5030                | 4.7                | 0.083      | 2                    | 5x5x3                 |

| MSS6122                | 4.7                | 0.065      | 1.82                 | 6.1x6.1x2.2           |

| MOS6020                | 4.7                | 0.05       | 1.94                 | 6.8x6x2.4             |

| Wurth Elekti           | ronik <sup>®</sup> |            |                      |                       |

| 744042                 | 4.7                | 0.07       | 1.65                 | 4.8x4.8x1.8           |

| 744068                 | 4.7                | 0.072      | 1.55                 | 8x8x1.1               |

| 7448944                | 4.7                | 0.0545     | 4.2                  | 8x8x3.8               |

| EPCOS <sup>®</sup>     |                    |            |                      |                       |

| LTF5022T               | 4.7                | 0.073      | 2                    | 5.2x5x2.2             |

| VLC5020T               | 4.7                | 0.097      | 2                    | 5x5x2                 |

| VLC6020T               | 4.7                | 0.079      | 1.8                  | 6x6x2                 |

| VLCF5020T              | 4.7                | 0.122      | 1.7                  | 5x5x2                 |

| VLF5014ST              | 4.7                | 0.12       | 1.7                  | 4.8x4.6x1.4           |

TABLE 5-3: MCP16322 RECOMMENDED INDUCTORS

| Part Number            | Value<br>(µH)                 | DCR<br>(Ω) | I <sub>SAT</sub> (A) | Size<br>WxLxH<br>(mm) |  |  |

|------------------------|-------------------------------|------------|----------------------|-----------------------|--|--|

| Coilcraft <sup>®</sup> |                               |            |                      |                       |  |  |

| MSS6132-472            | 4.7                           | 0.056      | 2.84                 | 6.1x6.1x3.2           |  |  |

| LPS6225-472            | 4.7                           | 0.065      | 3.2                  | 6.2x6.2x2.5           |  |  |

| MSS7341-502            | 4.7                           | 0.024      | 3.16                 | 7.3x7.3x4.1           |  |  |

| DO1813H-472            | 4.7                           | 0.054      | 2.6                  | 8.89x6.1x5.0          |  |  |

| Wurth Elektron         | Wurth Elektronik <sup>®</sup> |            |                      |                       |  |  |

| 7447785004             | 4.7                           | 0.06       | 2.5                  | 5.9x6.2x3.3           |  |  |

| 7447786004             | 4.7                           | 0.057      | 2.8                  | 5.9x6.2x5.1           |  |  |

| 7447789004             | 4.7                           | 0.033      | 3.9                  | 7.3x3.2x1.5           |  |  |

| EPCOS <sup>®</sup>     |                               |            |                      |                       |  |  |

| B82464G2               | 4.7                           | 0.033      | 3.1                  | 10.4x10.4x3.0         |  |  |

| B82464A2               | 4.7                           | 0.03       | 4.5                  | 10.4x10.4x3.0         |  |  |

#### 5.0.7 BOOST CAPACITOR

The boost capacitor is used to supply current for the internal high-side drive circuitry that is above the input voltage. The boost capacitor must store enough energy to completely drive the high-side switch on and off. A 22 nF X5R or X7R capacitor is recommended for all applications. The boost capacitor maximum voltage is 5.5V, so a 6.3V or 10V rated capacitor is recommended.

#### 5.0.8 THERMAL CALCULATIONS

The MCP16321/2 is available in a 3x3 QFN-16 package. By calculating the power dissipation and applying the package thermal resistance ( $\theta_{JA}$ ), the junction temperature is estimated. The maximum continuous junction temperature rating for the MCP16321/2 is +125°C.

To quickly estimate the internal power dissipation for the switching step-down regulator, an empirical calculation using measured efficiency can be used. Given the measured efficiency, the internal power dissipation is estimated in Equation 5-4. This power dissipation includes all internal and external component losses. For a quick internal estimate, subtract the estimated inductor ESR loss from the P<sub>DIS</sub> calculation in Equation 5-4.

## EQUATION 5-4: TOTAL POWER DISSIPATION ESTIMATE

$$P_{DIS} = \frac{V_{OUT} \times I_{OUT}}{Efficency} - (V_{OUT} \times I_{OUT})$$

The difference between the first term, input power, and the second term, power delivered, is the total system power dissipation. The inductor losses are estimated by  $P_L = I_{OUT}^2 x L_{ESR}$ .

## EXAMPLE 5-5: POWER DISSIPATION – MCP16321

$V_{IN} = 12V$

$V_{OUT} = 5.0V$

$I_{OUT} = 1A$

Efficiency = 92.5%

Total System Dissipation = 405 mW

$L_{ESR} = 0.04 \Omega$

$P_L = 40 \text{ mW}$

MCP16321 internal power dissipation estimate:

$P_{DIS} - P_{L} = 365 \text{ mW}$

$\theta_{JA} = 38.5^{\circ}C/W$

Estimated Junction = +14.052°C

Note 1:  $\theta_{JA} = 38.5^{\circ}$ C/W for a 4-layer FR4 Printed Circuit Board with a 13.5 in<sup>2</sup>, 1 oz internal copper ground plane.

**2:** A smaller ground plane will result in a larger  $\theta_{\text{JA}}$  temperature rise.

## EXAMPLE 5-6: POWER DISSIPATION – MCP16322

$V_{IN} = 12V$

$V_{OUT} = 3.3V$

$I_{OUT} = 2A$

Efficiency = 87.5%

Total System Dissipation = 943 mW

$L_{ESR} = 0.04 \Omega$

$P_1 = 160 \text{ mW}$

MCP16322 internal power dissipation estimate:

$P_{DIS} - P_{I} = 783 \text{ mW}$

$\theta_{JA} = 38.5^{\circ}C/W$

Estimated Junction = +30.14°C

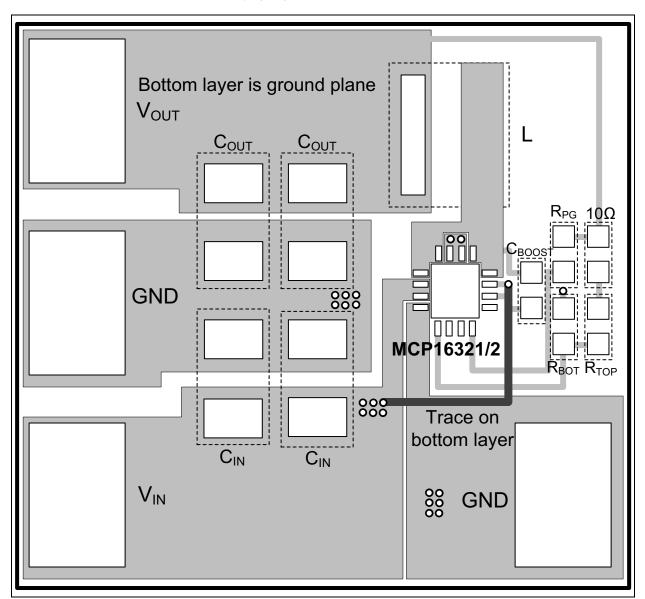

#### 5.0.9 PCB LAYOUT INFORMATION

Good printed circuit board layout techniques are important to any switching circuitry, and switching power supplies are no different. When wiring the switching high-current paths, short and wide traces should be used. Therefore, it is important that the input and output capacitors be placed as close as possible to the MCP16321/2 to minimize the loop area.

The feedback resistors and feedback signal should be routed away from the switching node and the switching current loop. When possible, ground planes and traces should be used to help shield the feedback signal and minimize noise and magnetic interference.

A good MCP16321/2 layout starts with  $C_{IN}$  placement.  $C_{IN}$  supplies current to the input of the circuit when the switch is turned on. In addition to supplying high-

frequency switch current, C<sub>IN</sub> also provides a stable voltage source for the internal MCP16321/2 circuitry. Unstable PWM operation can result if there are excessive transients or ringing on the V<sub>IN</sub> pin of the MCP16321/2 device. In Figure 5-1, C<sub>IN</sub> is placed close to the  $V_{\mbox{\scriptsize IN}}$  pins. A ground plane on the bottom of the board provides a low resistive and low inductive path for the return current. The next priority in placement is the freewheeling current loop formed by COUT and L while strategically placing the  $C_{OUT}$  return close to  $C_{IN}$ return. Next, CBOOST should be placed between the boost pin and the switch node pin. This leaves space close to the MCP16321/2  $V_{FB}$  pin to place  $R_{TOP}$  and R<sub>BOT</sub>. R<sub>TOP</sub> and R<sub>BOT</sub> are routed away from the switch node so noise is not coupled into the high-impedance V<sub>FB</sub> input.

FIGURE 5-1: Recommended Layout.

FIGURE 5-2: Recommended Layout – Schematic.

TABLE 5-4: RECOMMENDED LAYOUT COMPONENTS

| Component          | Value     |  |  |  |

|--------------------|-----------|--|--|--|

| C <sub>IN</sub>    | 2 x 10 μF |  |  |  |

| C <sub>OUT</sub>   | 2 x 22 μF |  |  |  |

| L                  | 4.7 µH    |  |  |  |

| R <sub>TOP</sub>   | 36.5 kΩ   |  |  |  |

| R <sub>BOT</sub>   | 10 kΩ     |  |  |  |

| $R_{PG}$           | 10 kΩ     |  |  |  |

| C <sub>BOOST</sub> | 22 nF     |  |  |  |

**NOTES:**

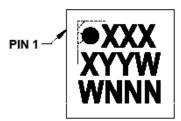

### 6.0 PACKAGING INFORMATION

### 6.1 Package Marking Information

16-Lead QFN (3x3x0.9 mm)

| Part Number       | Code |

|-------------------|------|

| MCP16321T-150E/NG | AAA  |

| MCP16321T-180E/NG | AAB  |

| MCP16321T-250E/NG | AAC  |

| MCP16321T-330E/NG | AAD  |

| MCP16321T-500E/NG | AAE  |

| MCP16321T-ADJE/NG | AAF  |

| MCP16322T-150E/NG | ABA  |

| MCP16322T-180E/NG | ABB  |

| MCP16322T-250E/NG | ABC  |

| MCP16322T-330E/NG | ABD  |

| MCP16322T-500E/NG | ABE  |

| MCP16322T-ADJE/NG | ABF  |

AAA E114 5256

Example

**Legend:** XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3) can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.