Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Digitally Enhanced Power Analog Synchronous Low-Side PWM Controller with Improved 8k Word Core

#### **Features**

- · Input Voltage: +4.5V to +42V

- Can be configured with multiple topologies including but not limited to:

- Flyback

- Ćuk

- Boost

- SEPIC (Single-Ended Primary-Inductor Converter)

- Capable of Quasi-Resonant or Fixed-Frequency Operation

- · Low Quiescent Current: 5 mA Typical

- Low Sleep Current: 50 μA Typical

- · Low-Side Gate Drivers:

- +5V gate drive with 0.5A sink/source current

- +10V gate drive with 1A sink/source current

- · Peak Current Mode Control

- · Differential Remote Output Sense

- · Multiple Output Systems:

- Master or Slave

- · AEC-Q100 Qualified

- · Configurable Parameters:

- V<sub>REF</sub>, Precision I<sub>OUT</sub>/V<sub>OUT</sub> Set Point (DAC)

- ADC Reference Switch (V<sub>DD</sub> or AV<sub>DD</sub>)

- Input Undervoltage Lockout (UVLO)

- Input Overvoltage Lockout (OVLO)

- Detection and protection

- Primary current leading edge blanking (0 ns, 50 ns, 100 ns and 200 ns)

- Gate drive dead time (16 ns to 256 ns)

- Fixed switching frequency range: 31.25 kHz to 2.0 MHz

- Slope compensation

- Quasi-Resonant configuration with built-in comparator and programmable offset voltage adjustment

- Primary current offset adjustment

- GPIO pin options

- Integrated Low-Side Differential Current-Sense Amplifier

- · Better than 5% Current Regulation

- · Thermal Shutdown

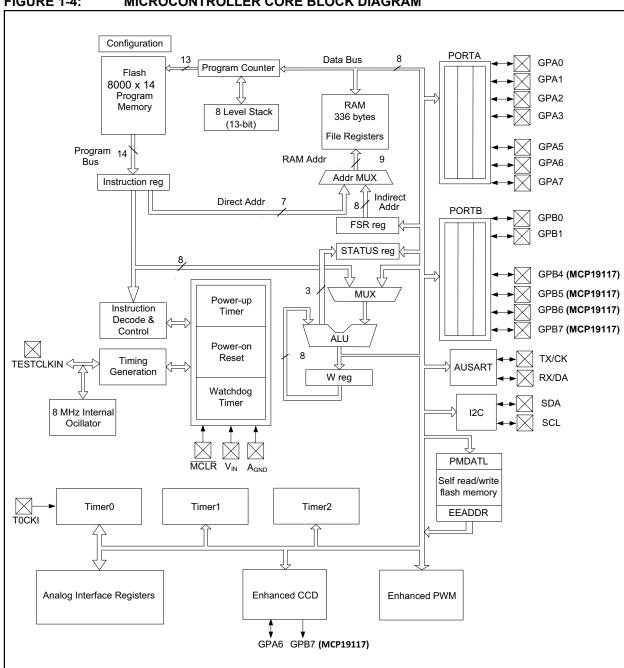

#### **Microcontroller Features**

- · Precision 8 MHz Internal Oscillator Block:

- Factory-calibrated to ±1%, typical

- Interrupt-Capable:

- Firmware

- Interrupt-on-change pins

- · Only 35 Instructions to Learn

- 8192 Words On-Chip Program Memory

- · High-Endurance Flash:

- 100,000 write Flash endurance

- Flash retention: > 40 years

- Watchdog Timer (WDT) with Independent Oscillator for Reliable Operation

- · Programmable Code Protection

- In-Circuit Serial Programming™ (ICSP™) via Two Pins

- Eight I/O Pins and One Input-Only Pin:

- Two open-drain pins

- · Analog-to-Digital Converter (ADC):

- 10-bit resolution

- Five external channels

- · Timer0: 8-bit Timer/Counter with 8-bit Prescaler

- Enhanced Timer1:

- 16-bit timer with prescaler

- Two selectable clock sources

- Timer2: 8-Bit Timer with Prescaler:

- 8-bit period register

- I<sup>2</sup>C Communication:

- 7-bit address masking

- Two dedicated address registers

- Addressable Universal Synchronous Receiver Transmitter (AUSART) Modes

- Asynchronous (Full Duplex)

- Synchronous Master (Half Duplex)

- Synchronous Slave (Half Duplex)

# Pin Diagram - 24-Pin QFN (MCP19116) GPB1/AN4/VREF2/TX/CK COMP $V_{DD}$ $\stackrel{\mathbb{Z}}{>}$ s<sup>s</sup> 24 22 21 20 23 19 GPA0/AN0/TEST\_OUT 1 18 $V_{\text{DR}}$ GPA1/AN1/CLKPIN 2 17 **PDRV** GPA2/AN2/T0CKI/INT 16 **SDRV** 3 MCP19116 GPA3/AN3 15 $P_{\text{GND}}$ GPA7/SCL/ICSPCLK 5 14 $A_{\text{GND}} \\$ EXP-25 GPA6/CCD/ICSPDAT/RX/DT 13 $I_P$ 6 9 10 11 12 7 8 NS NS $\mathsf{DESAT}_{\mathsf{N}}$ SP GPB0/SDA GPA5/MCLR/TEST\_EN DESAT<sub>P</sub>/ISOUT

TABLE 1: 24-PIN QFN (MCP19116) SUMMARY

| O/I                  | 24-Pin QFN | ANSEL | A/D | Timers | MSSP/AUSART | Interrupt  | Pull-Up | Basic            | Additional                                                          |

|----------------------|------------|-------|-----|--------|-------------|------------|---------|------------------|---------------------------------------------------------------------|

| GPA0                 | 1          | Y     | AN0 | _      |             | IOC        | Y       | _                | Analog/Digital Debug Output (1)                                     |

| GPA1                 | 2          | Υ     | AN1 | _      | _           | IOC        | Υ       | _                | Sync Signal In/Out (2)                                              |

| GPA2                 | 3          | Y     | AN2 | T0CKI  | _           | IOC<br>INT | Υ       | _                | _                                                                   |

| GPA3                 | 4          | Υ     | AN3 |        | _           | IOC        | Υ       | _                | _                                                                   |

| GPA5                 | 7          | N     | _   | _      | _           | IOC (3)    | Y (4)   | MCLR             | Test Enable Input                                                   |

| GPA6                 | 6          | N     | _   | _      | RX/DT       | IOC        | Y       | ICSPDAT          | Dual Capture / Single Compare1<br>Input                             |

| GPA7                 | 5          | N     | _   | _      | SCL         | IOC        | N       | ICSPCLK          | _                                                                   |

| GPB0                 | 8          | N     | _   | _      | SDA         | IOC        | N       | _                | _                                                                   |

| GPB1                 | 24         | Υ     | AN4 | _      | TX/CK       | IOC        | Υ       | _                | V <sub>REF2</sub> (5)                                               |

| DESAT <sub>N</sub>   | 9          | N     | _   | _      | _           | _          | _       | _                | DESAT Negative Input                                                |

| DESAT <sub>P</sub> / | 10         | N     | _   | _      | _           | _          | _       | _                | DESAT <sub>P</sub> Input or I <sub>SOUT</sub> Output <sup>(6)</sup> |

| I <sub>SP</sub>      | 11         | N     | _   | _      | _           | _          | Y       | _                | Current Sense Amplifier Positive Input                              |

| I <sub>SN</sub>      | 12         | N     | _   | _      | _           | _          | _       | _                | Current Sense Amplifier<br>Negative Input                           |

| Ι <sub>Ρ</sub>       | 13         | Ν     | _   |        | _           | _          | _       | _                | Primary Input Current Sense                                         |

| $A_{GND}$            | 14         | N     | _   | _      | _           | _          |         | A <sub>GND</sub> | Small Signal Ground                                                 |

| $P_{GND}$            | 15         | N     | _   | _      | _           | _          |         | $P_{GND}$        | Large Signal Ground                                                 |

| SDRV                 | 16         | Ν     | _   |        | _           | _          |         | _                | Secondary LS Gate Drive<br>Output                                   |

| PDRV                 | 17         | Z     | _   |        | _           | _          | _       | _                | Primary LS Gate Drive<br>Output                                     |

| $V_{DR}$             | 18         | Ν     | _   |        | _           | _          | _       | $V_{DR}$         | Gate Drive Supply Voltage                                           |

| $V_{\mathrm{DD}}$    | 19         | N     | _   |        | _           | _          | _       | $V_{DD}$         | V <sub>DD</sub> Output                                              |

| V <sub>IN</sub>      | 20         | Ν     | _   | _      | _           | _          | _       | V <sub>IN</sub>  | Input Supply Voltage                                                |

| V <sub>S</sub>       | 21         | N     | _   | _      | _           | _          | _       | _                | Output Voltage Sense                                                |

| I <sub>FB</sub>      | 22         | N     | _   | _      | _           | _          | _       | _                | Error Amplifier Feedback Input                                      |

| I <sub>COMP</sub>    | 23         | N     | _   | _      | _           | _          | _       | _                | Error Amplifier Output                                              |

- Note 1: The Analog/Digital Debug Output is selected through the control of the ABECON register.

- 2: Selected when functioning as master or slave by proper configuration of the MSC<1:0> bits in the MODECON register.

- **3:** The IOC is disabled when  $\overline{MCLR}$  is enabled.

- **4:** Weak pull-up always enabled when  $\overline{MCLR}$  is enabled, otherwise the pull-up is under user control.

- **5:** V<sub>REF2</sub> output selected when configured as master by proper configuration of the MSC<1:0> bits in the MODECON register.

- **6:** When RFB of MODECON<5> = 0, the internal feedback resistor and DESAT<sub>P</sub> input are enabled. When RFB = 1, I<sub>SOUT</sub> is enabled.

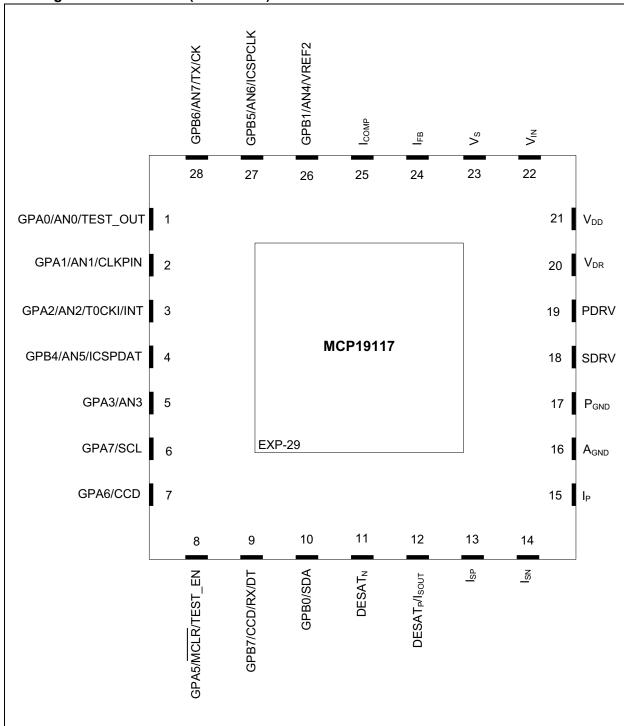

# Pin Diagram - 28-Pin QFN (MCP19117)

TABLE 2: 28-PIN QFN (MCP19117) SUMMARY

| 0/1                  | 28-Pin QFN | ANSEL | A/D | Timers | MSSP/AUSART | Interrupt  | Pull-Up | Basic     | Additional                                                          |

|----------------------|------------|-------|-----|--------|-------------|------------|---------|-----------|---------------------------------------------------------------------|

| GPA0                 | 1          | Y     | AN0 | _      |             | IOC        | Y       | ı         | Analog/Digital Debug Output (1)                                     |

| GPA1                 | 2          | Υ     | AN1 | _      | _           | IOC        | Υ       | _         | Sync Signal In/Out (2)                                              |

| GPA2                 | 3          | Y     | AN2 | T0CKI  | _           | IOC<br>INT | Υ       | _         | _                                                                   |

| GPA3                 | 5          | Υ     | AN3 | _      | _           | IOC        | Υ       | _         | _                                                                   |

| GPA5                 | 8          | N     | 1   | _      | 1           | IOC (3)    | Y (4)   | MCLR      | Test Enable Input                                                   |

| GPA6                 | 7          | N     |     | _      | 1           | IOC        | Y       | ı         | Dual Capture / Single<br>Compare1 Input                             |

| GPA7                 | 6          | N     | _   | _      | SCL         | IOC        | N       | _         | _                                                                   |

| GPB0                 | 10         | N     | _   | _      | SDA         | IOC        | N       | _         | _                                                                   |

| GPB1                 | 26         | Y     | AN4 |        | _           | IOC        | Υ       | _         | V <sub>REF2</sub> (5)                                               |

| GPB4                 | 4          | Υ     | AN5 | _      | _           | IOC        | Υ       | ICSPDAT   | _                                                                   |

| GPB5                 | 27         | Υ     | AN6 | _      | _           | IOC        | Υ       | ICSPCLK   | _                                                                   |

| GPB6                 | 28         | Υ     | AN7 | _      | TX/CK       | IOC        | Υ       | _         | _                                                                   |

| GPB7                 | 9          | Υ     | _   | _      | RX/DT       | IOC        | Υ       | _         | Single Compare2 Input                                               |

| DESAT <sub>P</sub> / | 12         | N     | _   | _      | _           | _          | _       | _         | DESAT <sub>P</sub> Input or I <sub>SOUT</sub> Output <sup>(6)</sup> |

| DESAT <sub>N</sub>   | 11         | N     | _   | _      | _           | _          | _       | _         | DESAT Negative Input                                                |

| I <sub>SP</sub>      | 13         | N     | 1   | _      | ı           | _          | Υ       |           | Current Sense Amplifier<br>Non-inverting Input                      |

| I <sub>SN</sub>      | 14         | N     |     | _      | _           | _          | _       | -         | Current Sense Amplifier Inverting Input                             |

| Ι <sub>Ρ</sub>       | 15         | N     | _   | _      |             | _          | _       | _         | Primary Input Current Sense                                         |

| $A_{GND}$            | 16         | N     |     | —      | _           | _          | _       | $A_{GND}$ | Small Signal Ground                                                 |

| $P_{GND}$            | 17         | N     |     | _      | _           | _          |         | $P_{GND}$ | Large Signal Ground                                                 |

| SDRV                 | 18         | N     | _   | _      | _           | _          | _       | _         | Secondary LS Gate Drive Output                                      |

| PDRV                 | 19         | N     | _   | _      | _           | _          |         | _         | Primary LS Gate Drive Output                                        |

| $V_{DR}$             | 20         | N     | _   | _      | _           | _          | _       | $V_{DR}$  | Gate Drive Supply Voltage                                           |

| $V_{DD}$             | 21         | N     | _   | _      |             | _          | _       | $V_{DD}$  | V <sub>DD</sub> Output                                              |

| V <sub>IN</sub>      | 22         | N     | _   | _      | _           | _          | _       | $V_{IN}$  | Input Supply Voltage                                                |

| V <sub>S</sub>       | 23         | N     | _   | _      |             | _          |         | _         | Output Voltage Sense                                                |

| I <sub>FB</sub>      | 24         | N     | —   | —      |             | _          |         | _         | Error Amplifier Feedback input                                      |

| I <sub>COMP</sub>    | 25         | N     | _   | _      | _           | _          | _       | <u> </u>  | Error Amplifier Output                                              |

- Note 1: The Analog/Digital Debug Output is selected through the control of the ABECON register.

- 2: Selected when functioning as master or slave by proper configuration of the MSC<1:0> bits in the MODECON register.

- **3:** The IOC is disabled when  $\overline{MCLR}$  is enabled.

- **4:** Weak pull-up always enabled when  $\overline{MCLR}$  is enabled, otherwise the pull-up is under user control.

- **5:** V<sub>REF2</sub> output selected when configured as master by proper configuration of the MSC<1:0> bits in the MODECON register.

- **6:** When RFB of MODECON<6> = 0, the internal feedback resistor is enabled allow with DESAT<sub>P</sub> input. When RFB = 1, I<sub>SOUT</sub> is enabled.

# **Table of Contents**

| Feat  | ures                                         | 1   |

|-------|----------------------------------------------|-----|

| 1.0   | Device Overview                              | 9   |

| 2.0   | Pin Description                              | 13  |

| 3.0   | Functional Description                       | 19  |

| 4.0   | Electrical Characteristics                   | 22  |

| 5.0   | Digital Electrical Characteristics           | 31  |

| 5.0   | Digital Electrical Characteristics           |     |

| 6.0   | Configuring the MCP19116/7                   | 39  |

| 7.0   | Typical Performance Curves                   |     |

| 8.0   | System Bench Testing                         | 57  |

| 9.0   | Device Calibration                           | 59  |

| 10.0  | Addressable USART Module                     |     |

| 11.0  | Memory Organization                          | 81  |

| 12.0  | Device Configuration                         | 93  |

| 13.0  | Oscillator Modes                             | 95  |

| 14.0  | Resets                                       | 97  |

|       | Interrupts                                   |     |

|       | Power-Down Mode (Sleep)                      |     |

|       | Watchdog Timer (WDT)                         |     |

|       | Flash Program Memory Control                 |     |

|       | I/O Ports                                    |     |

| 20.0  | Interrupt-On-Change                          |     |

| 21.0  |                                              | 137 |

| 22.0  | Analog-to-Digital Converter (ADC) Module     | 139 |

|       | Timer0 Module                                |     |

| 24.0  | Timer1 Module with Gate Control              |     |

| 25.0  | Timer2 Module                                |     |

|       | Enhanced PWM Module                          |     |

| 27.0  | Dual Capture/Compare (CCD) Module            | 161 |

| 28.0  | PWM Control Logic                            | 165 |

|       | Master Synchronous Serial Port (MSSP) Module |     |

|       | Instruction Set Summary                      |     |

| 31.0  | In-Circuit Serial Programming™ (ICSP™)       |     |

| 32.0  |                                              |     |

|       | Packaging Information                        |     |

|       | ndix A: Revision History                     |     |

| INDE  | X                                            | 235 |

|       | Microchip Web Site                           |     |

|       | omer Change Notification Service             |     |

|       | omer Support                                 |     |

|       | uct Identification System                    |     |

|       | emarks                                       |     |

| World | twide Sales and Service                      | 246 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| M   | Ρ1 | 91 | 11 | 6 | 17 |

|-----|----|----|----|---|----|

| IVI |    | •  |    | V |    |

NOTES:

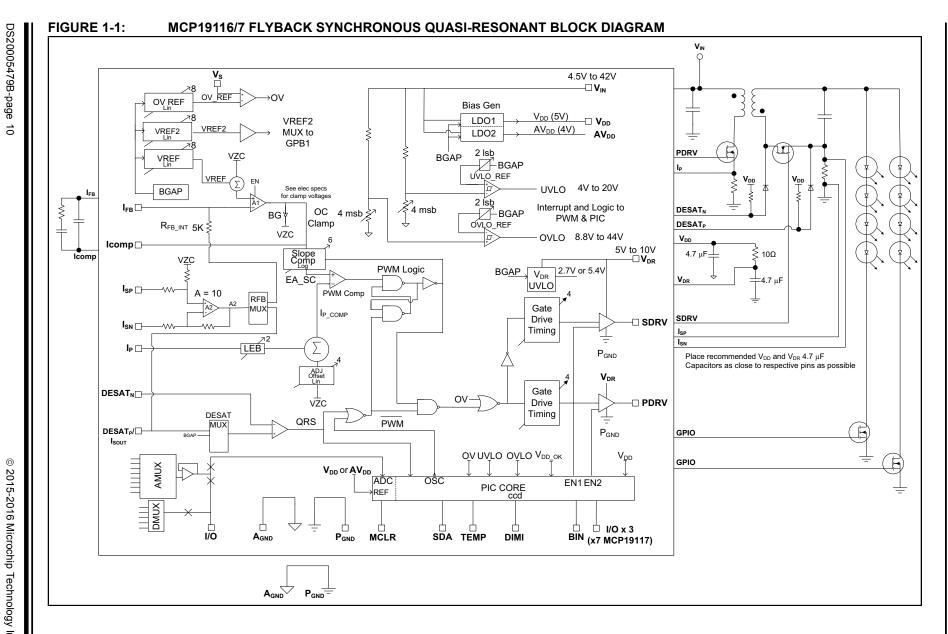

# 1.0 DEVICE OVERVIEW

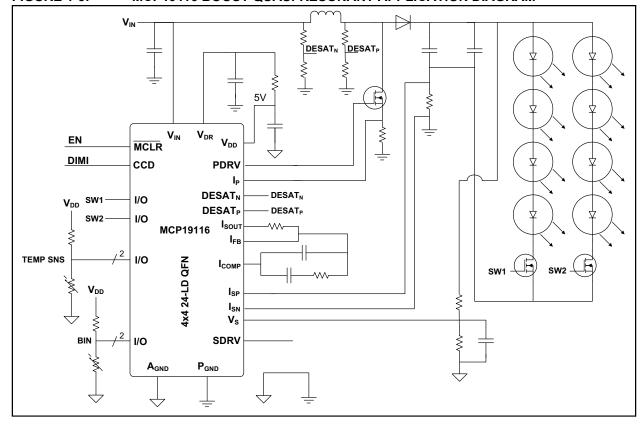

The MCP19116/7 devices are highly integrated, mixed-signal low-side synchronous controllers that operate from +4.5V to +42V. The family features an PWM controller with an integrated microcontroller core used for LED lighting systems, battery chargers and other low-side switch PWM applications. The MCP19116/7 devices are derived from the MCP19114/5 which share the same features and characteristics except for the addition of larger program memory (8k words vs 4k words) and several design enhancements. These enhancements were added to the MCP19116/7 devices to improve calibration, increase accuracy and provide greater flexibility. The devices feature an analog internal PWM controller similar to the MCP1631, and a standard PIC® microcontroller similar to the PIC12F617.

Complete customization of device operating parameters, start-up or shutdown profiles, protection levels and fault handling procedures are accomplished by setting digital registers using Microchip's MPLAB® X Integrated Development Environment software and one of Microchip's many in-circuit debugger and device programmers.

The MCP19116/7 mixed-signal low-side synchronous controllers feature integrated programmable input UVLO/OVLO, programmable output overvoltage (OV), two low-side gate drive outputs with independent programmable dead time, programmable leading edge blanking (four steps), programmable 6-bit slope compensation and an integrated internal fixed-frequency programmable oscillator for applications.

An integrated 8-bit reference voltage ( $V_{REF}$ ) is used for setting output current or voltage. An internal comparator supports quasi-resonant applications. Additional Capture and Compare modules are integrated for increased control, including enhanced dimming capability.

The MCP19116/7 devices contain two internal LDOs. A 5V LDO ( $V_{DD}$ ) is used to power the internal processor and provide 5V externally. A 4V LDO ( $AV_{DD}$ ) is used to power the internal analog circuitry. Either  $V_{DD}$  or  $AV_{DD}$  can be connected internally to the 10-bit Analog-to-Digital Converter reference input. The 5V external output can be used to supply the gate drive. An analog filter between the  $V_{DD}$  output and the  $V_{DR}$  input is recommended when implementing a 5V gate drive supplied from  $V_{DD}$ . Two 4.7  $\mu F$  capacitors are recommended with one placed as close as possible to  $V_{DD}$  and one as close as possible to  $V_{DR}$ , separated by a  $10\Omega$  isolation resistor. DO NOT exceed 10  $\mu F$  on the  $V_{DD}$ . An external supply is required to implement higher gate drive voltages.

By utilizing a Microchip Technology Incorporated TC1240A voltage doubler supplied from  $V_{DD}$  to provide  $V_{DR}$ , a 10V gate drive can be achieved.

A 4V LDO is used to power the internal analog circuitry. The two low-side drivers can be used to operate the power converter in bidirectional mode, enabling the "shaping" of LED dimming current in LED applications or developing bidirectional power converters for battery-powered applications.

The MCP19116 is packaged in a 24-lead 4 mm x 4 mm QFN. The MCP19117 is packaged in a 28-lead 5 mm x 5 mm QFN.

The ability for system designers to configure application-specific features allows users of the MCP19116/7 devices to save costly board real estate and additional component costs.

The General Purpose Input/Output (GPIO) of the MCP19116/7 can be configured to offer a status output:

- · a device enable, to control an external switch

- a switching frequency synchronization output or input

- · and even a device status or "heartbeat" indicator

With integrated features like output current adjustment and dynamic output voltage positioning, the MCP19116/7 family has the best in-class performance and highest integration level currently available.

Power trains supported by this architecture include but are not limited to boost, flyback, quasi-resonant flyback, SEPIC, Ćuk, etc.

Two low-side gate drivers are capable of sinking and sourcing 1A at 10V  $V_{DR}$ . With a 5V gate drive, the driver is capable of 0.5A sink and source. The user has the option to allow the  $V_{IN}$  UVLO to shut down the drivers by setting the UVLOEN bit. When this bit is not set, the device drivers will ride through the UVLO condition and continue to operate until  $V_{DR}$  reaches the gate drive UVLO value. This value is selectable at 2.7V or 5.4V and is always enabled. An internal reset for the microcontroller core is set to 2.0V. An internal comparator module is used to sense the desaturation of the flyback transformer to synchronize switching for quasi-resonant applications.

The operating input voltage for normal device operation ranges from +4.5V to +42V with an absolute maximum of 44V. The maximum transient voltage is 48V for 500 ms. An  $I^2C$  serial bus is used for device communications from the PWM controller to the system.

$\mathbf{V}_{\text{IN}}$ TC1240 VOLTAGE DOUBLER 5V 10V  $\textbf{V}_{\text{DR}}$ ΕN MCLR DIMI CCD **PDRV**  $I_P$ MCP19116 I/O  $\mathbf{V}_{\text{DD}}$ **DESAT<sub>N</sub> DESAT<sub>P</sub>** 4x4 24-LD QFN **SDRV** I<sub>SN</sub> TEMP SNS 2 I/O  $I_{SP}$  $I_{FB}$  $V_{\text{DD}}$ ICOMP ٧s BIN 2 I/O I/O I/O  $\boldsymbol{P}_{\text{GND}}$  $\mathbf{A}_{\text{GND}}$

FIGURE 1-2: MCP19116 ĆUK SYNCHRONOUS POSITIVE OUTPUT APPLICATION DIAGRAM

FIGURE 1-4: MICROCONTROLLER CORE BLOCK DIAGRAM

# 2.0 PIN DESCRIPTION

The 24-lead MCP19116 and 28-lead MCP19117 devices feature pins that have multiple functions associated with each pin. Table 2-1 provides a description of the different functions. Refer to Section 2.1 "Detailed Pin Functional Description" for detailed information.

TABLE 2-1: MCP19116/7 PINOUT DESCRIPTION

| Name                          | Function | Input<br>Type    | Output<br>Type | Description                                           |

|-------------------------------|----------|------------------|----------------|-------------------------------------------------------|

| GPA0/AN0/TEST_OUT             | GPA0     | TTL              | CMOS           | General purpose I/O                                   |

|                               | AN0      | AN               | _              | A/D Channel 0 input                                   |

|                               | TEST_OUT | _                | _              | Internal analog/digital signal multiplexer output (1) |

| GPA1/AN1/CLKPIN               | GPA1     | TTL              | CMOS           | General purpose I/O                                   |

|                               | AN1      | AN               | _              | A/D Channel 1 input                                   |

|                               | CLKPIN   | ST               | CMOS           | Switching-frequency clock input or output (2)         |

| GPA2/AN2/T0CKI/INT            | GPA2     | ST               | CMOS           | General purpose I/O                                   |

|                               | AN2      | AN               | _              | A/D Channel 2 input                                   |

|                               | T0CKI    | ST               | _              | Timer0 clock input                                    |

|                               | INT      | ST               | _              | External interrupt                                    |

| GPA3/AN3                      | GPA3     | TTL              | CMOS           | General purpose I/O                                   |

|                               | AN3      | AN               | _              | A/D Channel 3 input                                   |

| GPA5/MCLR                     | GPA5     | TTL              | _              | General purpose input only                            |

|                               | MCLR     | ST               | _              | Master Clear with internal pull-up                    |

| GPA6/CCD/ICSPDAT/RX/DT        | GPA6     | ST               | CMOS           | General purpose I/O                                   |

| ICSPDAT/RX/DT                 | ICSPDAT  | ST               | CMOS           | Serial Programming Data I/O (MCP19116 only)           |

| (MCP19116 Only)               | CCD      | ST               | CMOS           | Dual Capture Input. CCD1 Single Compare output        |

| ,                             | RX       | ST               | _              | USART asynchronous serial receive (MCP19116 only)     |

|                               | DT       | ST               | CMOS           | USART synchronous serial data (MCP19116 only)         |

| GPA7/SCL/ICSPCLK              | GPA7     | ST               | OD             | General purpose open drain I/O                        |

| ICSPCLK (MCP19116 only)       | SCL      | I <sup>2</sup> C | OD             | I <sup>2</sup> C clock                                |

| TOOL OLIK (MOT TOTTO OTHY)    | ICSPCLK  | ST               | _              | Serial Programming Clock (MCP19116 only)              |

| GPB0/SDA                      | GPB0     | TTL              | OD             | General purpose I/O                                   |

|                               | SDA      | I <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output                    |

| GPB1/AN4/VREF2/TX/CK          | GPB1     | TTL              | CMOS           | General-purpose I/O                                   |

| TX/CK ( <b>MCP19116</b> Only) | AN4      | AN               | _              | A/D Channel 4 input                                   |

| TA/CK (WCP 19116 Offig)       | VREF2    | _                | AN             | VREF2 DAC Output (3)                                  |

|                               | TX       | _                | CMOS           | USART asynchronous serial transmit (MCP19116 only)    |

|                               | CK       | ST               | CMOS           | USART synchronous serial clock (MCP19116 only)        |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

Note 1: The Analog/Digital Debug Output is selected through the control of the ABECON register.

<sup>2:</sup> Selected when functioning as master or slave by proper configuration of the MSC<1:0> bits in the MODECON register.

<sup>3:</sup> VREF2 output selected when configured as master by proper configuration of the MSC<1:0> bits in the MODECON register.

TABLE 2-1: MCP19116/7 PINOUT DESCRIPTION (CONTINUED)

| Name                                  | Function                              | Input<br>Type | Output<br>Type | Description                                                  |

|---------------------------------------|---------------------------------------|---------------|----------------|--------------------------------------------------------------|

| GPB4/AN5/ICSPDAT                      | GPB4                                  | TTL           | CMOS           | General purpose I/O                                          |

| (MCP19117 Only)                       | AN5                                   | AN            | _              | A/D Channel 5 input                                          |

|                                       | ICSPDAT                               | ST            | CMOS           | Primary Serial Programming Data I/O                          |

| GPB5/AN6/ICSPCLK                      | GPB5                                  | TTL           | CMOS           | General purpose I/O                                          |

| (MCP19117 Only)                       | AN6                                   | AN            | _              | A/D Channel 6 input                                          |

|                                       | ISCPCLK                               | ST            | _              | Primary Serial Programming Clock                             |

| GPB6/AN7/TX/CK                        | GPB6                                  | TTL           | CMOS           | General purpose I/O                                          |

| ( <b>MCP19117</b> Only)               | AN7                                   | AN            | _              | A/D Channel 7 input                                          |

|                                       | TX                                    |               | CMOS           | USART asynchronous serial transmit                           |

|                                       | CK                                    | ST            | CMOS           | USART synchronous serial clock                               |

| GPB7/CCD/RX/DT                        | GPB7                                  | TTL           | CMOS           | General purpose I/O                                          |

| (MCP19117 Only)                       | CCD                                   | ST            | CMOS           | CCD2 Single Compare output.                                  |

|                                       | RX                                    | ST            | _              | USART asynchronous serial receive                            |

|                                       | DT                                    | ST            | CMOS           | USART synchronous serial data                                |

| V <sub>IN</sub>                       | V <sub>IN</sub>                       | _             | _              | Device input supply voltage                                  |

| $V_{DD}$                              | $V_{DD}$                              |               | _              | Internal +5V LDO output pin                                  |

| $V_{DR}$                              | $V_{DR}$                              |               | _              | Gate drive supply voltage                                    |

| A <sub>GND</sub>                      | A <sub>GND</sub>                      | _             | _              | Small signal quiet ground                                    |

| P <sub>GND</sub>                      | P <sub>GND</sub>                      |               | _              | Large signal power ground                                    |

| PDRV                                  | PDRV                                  | _             | _              | Primary low-side MOSFET gate drive                           |

| SDRV                                  | SDRV                                  | _             | _              | Secondary low-side MOSFET gate drive                         |

| I <sub>P</sub>                        | l <sub>P</sub>                        |               | _              | Primary input current sense                                  |

| I <sub>SN</sub>                       | I <sub>SN</sub>                       |               | _              | Secondary-current sense-amplifier negative input             |

| I <sub>SP</sub>                       | I <sub>SP</sub>                       | _             | _              | Secondary-current sense-amplifier positive input             |

| $V_S$                                 | V <sub>S</sub>                        |               | _              | Sense voltage compared to overvoltage DAC                    |

| I <sub>FB</sub>                       | I <sub>FB</sub>                       |               | _              | Error amplifier feedback input                               |

| I <sub>COMP</sub>                     | I <sub>COMP</sub>                     | _             | _              | Error amplifier output                                       |

| DESAT <sub>P</sub> /I <sub>SOUT</sub> | DESAT <sub>P</sub> /I <sub>SOUT</sub> | _             | _              | DESAT <sub>P</sub> : DESAT detect comparator positive input  |

|                                       |                                       |               |                | I <sub>SOUT</sub> : Secondary-current sense-amplifier output |

| DESAT <sub>N</sub>                    | DESAT <sub>N</sub>                    | _             | _              | DESAT <sub>N</sub> : DESAT detect comparator negative        |

|                                       |                                       |               |                | input                                                        |

Legend:

AN

= Analog input or output

CMOS

= CMOS compatible input or output

OD

= Open-Drain

TTL

= TTL compatible input

ST

= Schmitt Trigger input with CMOS levels

I²C

= Schmitt Trigger input with I²C

**Note 1:** The Analog/Digital Debug Output is selected through the control of the ABECON register.

<sup>2:</sup> Selected when functioning as master or slave by proper configuration of the MSC<1:0> bits in the MODECON register.

<sup>3:</sup> VREF2 output selected when configured as master by proper configuration of the MSC<1:0> bits in the MODECON register.

# 2.1 Detailed Pin Functional Description

#### 2.1.1 GPA0 PIN

GPA0 is a general purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN0 is an input to the A/D. To configure this pin to be read by the A/D on channel 0, bits TRISA0 and ANSA0 must be set.

The ABECON register can be configured to set this pin to the TEST\_OUT function. It is a buffered output of the internal analog or digital signal multiplexers. Analog signals present on this pin are controlled by the ADCON0 register. Digital signals present on this pin are controlled by the ABECON register.

#### 2.1.2 GPA1 PIN

GPA1 is a general purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available

AN1 is an input to the A/D. To configure this pin to be read by the A/D on channel 1, bits TRISA1 and ANSA1 must be set.

When the MCP19116/7 are configured as a master or slave, this pin is configured to be the switching-frequency synchronization input or output (CLKPIN).

#### 2.1.3 GPA2 PIN

GPA2 is a general purpose ST input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN2 is an input to the A/D. To configure this pin to be read by the A/D on channel 2, bits TRISA2 and ANSA2 must be set.

When bit T0CS is set in the OPTION\_REG register, the T0CKI function is enabled. Refer to **Section 23.0** "Timer0 Module" for more information.

GPA2 can also be configured as an external interrupt by setting the INTE bit. Refer to **Section 15.2** "GPA2/INT Interrupt" for more information.

#### 2.1.4 GPA3 PIN

GPA3 is a general purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN3 is an input to the A/D. To configure this pin to be read by the A/D on channel 3, bits TRISA3 and ANSA3 must be set.

#### 2.1.5 GPA5 PIN

GPA5 is a general purpose TTL input only pin. An internal weak pull-up and interrupt-on-change are also available.

For programming purposes, this pin is to be connected to the MCLR pin of the serial programmer. Refer to **Section 31.0** "In-Circuit Serial Programming™ (ICSP™)" for more information.

This pin is MCLR when the MCLRE bit is set in the CONFIG register.

#### 2.1.6 GPA6 PIN

GPA6 is a general purpose CMOS output ST input pin whose data direction is controlled in TRISGPA.

ICSPDAT is a serial programming data I/O function. This can be used in conjunction with ICSPCLK to serial-program the device.

**MCP19116 Only**: RX is the USART Asynchronous serial receive.

**MCP19116 Only**: DT is the USART Synchronous serial clock.

GPA6 is the Dual Capture input and CCD1 output compare. For more information, refer to Section 27.0 "Dual Capture/Compare (CCD) Module".

#### 2.1.7 GPA7 PIN

GPA7 is a true open-drain general purpose pin whose data direction is controlled in TRISGPA. There is no internal connection between this pin and device  $V_{DD}$ . This pin does not have a weak pull-up, but interrupt-on-change is available.

This pin is the primary ICSPCLK input. This can be used in conjunction with ICSPDAT to serial program the device.

When the MCP19116/7 is configured for I<sup>2</sup>C communication, GPA7 functions as the I<sup>2</sup>C clock (SCL). This pin must be configured as an input to allow proper operation. For more information, refer to Section 29.2 "I<sup>2</sup>C Mode Overview"

#### 2.1.8 GPB0 PIN

GPB0 is a true open-drain general purpose pin whose data direction is controlled in TRISGPB. There is no internal connection between this pin and device  $V_{DD}$ . This pin does not have a weak pull-up, but interrupt-on-change is available. When the MCP19116/7 are configured for  $I^2C$  communication, GPB0 functions as the  $I^2C$  clock (SDA). This pin must be configured as an input to allow proper operation. For more information, refer to Section 29.2 " $I^2C$  Mode Overview".

#### 2.1.9 GPB1 PIN

GPB1 is a general purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN4 is an input to the A/D. To configure this pin to be read by the A/D on channel 4, bits TRISB1 and ANSB1 must be set.

**MCP19116 Only**: TX is the USART Asynchronous serial transmit.

MCP19116 Only: CK is the USART Synchronous serial clock.

When the MCP19116/7 are configured as a master, this pin is configured to be the  $V_{REF2}$  DAC output.

#### 2.1.10 GPB4 PIN (MCP19117 ONLY)

GPB4 is a general purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN5 is an input to the A/D. To configure this pin to be read by the A/D on channel 5, bits TRISB4 and ANSB4 must be set.

ICSPDAT is the primary serial-programming data I/O function. This is used in conjunction with ICSPCLK to serial program the device.

## 2.1.11 GPB5 PIN (MCP19117 ONLY)

GPB5 is a general purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN6 is an input to the A/D. To configure this pin to be read by the A/D on channel 6, bits TRISB5 and ANSB5 must be set.

ICSPCLK is the primary serial-programming clock function. This is used in conjunction with ICSPDAT to serial program the device.

### 2.1.12 GPB6 PIN (MCP19117 ONLY)

GPB6 is a general purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available

AN7 is an input to the A/D. To configure this pin to be read by the A/D on channel 7, bits TRISB6 and ANSB6 must be set.

**MCP19117 Only**: TX is the USART Asynchronous serial transmit.

**MCP19117 Only**: CK is the USART Synchronous serial clock.

## 2.1.13 GPB7 PIN (MCP19117 ONLY)

GPB7 is a general purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

RX is the USART Asynchronous serial receive.

DT is the USART Synchronous serial clock.

For more information, refer to Section 10.0 "Addressable USART Module"

GPB7 is the CCD2 output Compare. For more information, refer to Section 27.0 "Dual Capture/Compare (CCD) Module".

# 2.1.14 DESAT<sub>N</sub> PIN

Internal comparator inverting input. Used during Quasi-Resonant operation for desaturation detection.

#### 2.1.15 DESAT<sub>P</sub>/I<sub>SOUT</sub> PIN

When using the internal comparator for desaturation detection during Quasi-Resonant operation, this pin connects to the comparator's non-inverting input. The output of the remote sense current-sense amplifier gets configured to utilize the  $5~k\Omega$  internal feedback resistor. When not utilizing the internal comparator and not configured to use the  $5~k\Omega$  internal feedback resistor, the current sense amplifier gets connected to this pin and is  $I_{SOLIT}$ .

# 2.1.16 I<sub>SP</sub> PIN

The non-inverting input to internal current-sense amplifier, typically used to differentially remote-sense secondary current. This pin can be internally pulled-up to  $V_{DD}$  by setting the <ISPUEN> bit in the PE1 register.

# 2.1.17 I<sub>SN</sub> PIN

The inverting input to internal current-sense amplifier, typically used to differentially remote-sense secondary current.

### 2.1.18 I<sub>P</sub> PIN

Primary input current-sense for current mode control and peak current limit. For voltage mode control, this pin can be connected to an artificial ramp.

## 2.1.19 A<sub>GND</sub> PIN

$A_{GND}$  is the small signal ground connection pin. This pin should be connected to the exposed pad on the bottom of the package.

# 2.1.20 P<sub>GND</sub> PIN

Connect all large-signal level ground returns to P<sub>GND</sub>. These large-signal level ground traces should have a small loop area and minimal length to prevent coupling of switching noise to sensitive traces.

### 2.1.21 SDRV PIN

The gate of the low-side secondary MOSFET is connected to SDRV. The PCB trace connecting SDRV to the gate must be of minimal length and appropriate width to handle the high-peak drive current and fast voltage transitions.

#### 2.1.22 PDRV PIN

The gate of the low-side primary MOSFET is connected to PDRV. The PCB tracing connecting PDRV to the gate must be of minimal length and appropriate width to handle the high-peak drive currents and fast voltage transitions.

# 2.1.23 V<sub>DR</sub> PIN

The supply for the low-side drivers is connected to this pin and has an absolute maximum rating of +13.5V. This pin can be connected by an RC filter to the  $V_{DD}$  pin.

# 2.1.24 V<sub>DD</sub> PIN

The output of the internal +5.0V regulator is connected to this pin. It is recommended that a 1.0  $\mu F$  minimum/ 10  $\mu F$  maximum bypass capacitor be connected between this pin and the GND pin of the device. The bypass capacitor should be physically placed close to the device.

### 2.1.25 $V_{IN}$ PIN

Input power connection pin of the device. It is recommended that capacitance be placed between this pin and the GND pin of the device.

# 2.1.26 V<sub>S</sub> PIN

Analog input connected to the non-inverting input of the overvoltage comparator. Typically used as output-voltage overvoltage protection. The inverting input of the overvoltage comparator is controlled by the OV REF DAC.

# 2.1.27 I<sub>FB</sub> PIN

Error-amplifier inverting feedback connection.

#### 2.1.28 I<sub>COMP</sub> PIN

Error-amplifier output signal.

## 2.1.29 EXPOSED PAD (EP)

It is recommended to connect the exposed pad to  $\ensuremath{A_{GND}}.$

NOTES:

# 3.0 FUNCTIONAL DESCRIPTION

# 3.1 Linear Regulators

The operating input voltage for the MCP19116/7 ranges from 4.5V to 42V. There are two internal Low Dropout (LDO) voltage regulators. A 5V LDO is used to power the internal processor and provide a 5V output for external usage. A second LDO (AV $_{DD}$ ) is a 4V regulator and is used to power the remaining analog internal circuitry. AV $_{DD}$  is factory calibrated and is the default ADC reference voltage. The ADC reference is switchable between AV $_{DD}$  and V $_{DD}$ . Using an LDO to power the MCP19116/7, the input voltage is monitored using a resistor divider. The MCP19116/7 also incorporate brown-out protection. Refer to Section 14.3 "Brown-out Reset (BOR)" for details. The PIC core will reset at 2.0V V $_{DD}$ .

# 3.2 Output Drive Circuitry

The MCP19116/7 integrate two low-side drivers used to drive the external low-side N-Channel power MOSFETs for synchronous applications, such as synchronous flyback and synchronous Ćuk converters. Both converter types can be configured for non-synchronous control by replacing the synchronous FET with a diode. The flyback is also capable of quasi-resonant operation. The MCP19116/7 can also be configured as a Boost or SEPIC switch-mode power supply (SMPS). In Boost mode, non-synchronous fixed-frequency or non-synchronous quasi-resonant control can be utilized. This device can also be used as a SEPIC SMPS in fixed-frequency non-synchronous mode. The low-side drive is capable of switching the MOSFET at high frequency in typical SMPS applications. The gate drive (VDR) can be supplied from 5V to 10V. The drive strength is capable of up to 1A sink/source with 10V gate drive and down to 0.5A sink/source with 5V gate drive. A programmable delay is used to set the gate turn-on dead time. This prevents overlap and shoot-through currents that can decrease the converter efficiency. Each driver has its own EN input controlled by the microcontroller core.

#### 3.3 Current Sense

The output current is differentially sensed by the MCP19116/7. In low-current applications, this helps maintain high system efficiency by minimizing power dissipation in current-sense resistors. Differential current sensing also minimizes external ground-shift errors. The internal differential amplifier has a typical gain of 10 V/V and is factory trimmed.

#### 3.4 Peak Current Mode

The MCP19116/7 is a peak current mode controlled device with the current-sensing element in series with the primary side MOSFET. Programmable leading edge blanking can be implemented to blank current spikes resulting from turn on. The blank time is controlled from the ICLEBCON register.

Primary-input current-offset adjust is also available via user programmability, thus limiting peak primary input current. This offset adjustment is controlled by the ICO-ACON register.

# 3.5 Magnetic Desaturation Detection

An internal comparator module is used to detect power train magnetic desaturation for quasi-resonant applications. The comparator output is used as a signal to synchronize the start of the next switching cycle. This operation differs from the traditional fixed-frequency application. The DESAT comparator output can be enabled and routed into the PWM circuitry or disabled for fixed-frequency applications. During Quasi-Resonant (QR) operation, the DESAT comparator output is enabled and combined with a pair of one-shot timers and a flip-flop to sustain PWM operation. Timer2 (TMR2) must be initialized and set to run at a frequency lower than the minimum QR operating frequency. When the CDSWDE bit is set in the DESATCON register, TMR2 serves as a watchdog.

An example of the order of events for a Flyback SMPS in synchronous QR operation is as follows:

- · the primary gate drive (PDRV) goes high

- · the output of the DESAT comparator is high

- the primary current increases until I<sub>P</sub> reaches the level of the Error Amp and causes PWM comparator output to go low

- the PDRV goes low and the secondary gate drive (SDRV) goes high (after programmed dead time).

This triggers the first one-shot to send a 200 ns pulse that resets the flip-flop and TMR2 (WDM\_RESET)

- the 200 ns one-shot pulse design is implemented to mask any spurious transitions at the DESAT comparator output caused by switching noise

- the SDRV stays high until the secondary winding completely runs out of energy, at which time the output capacitance begins to source current back through the winding and secondary MOSFET

- the DESAT comparator detects this and its output goes low. This sets the flip-flop and triggers the second one-shot to send a 33 ns pulse to the control logic, causing the SDRV to go low and the PDRV to go high (after programmed dead time)

- the cycle then repeats. If, for any reason, the reset one-shot does not fire, the WDM\_RESET signal stays low and TMR2 is allowed to run until the PWM signal kicks off a new cycle

The desaturation comparator module is controlled by the DESATCON register.

## 3.6 Start-Up

To control the output current during start-up, the MCP19116/7 devices have the capability to monotonically increase system current at the user's discretion. This is accomplished through the control of the reference voltage DAC ( $V_{REF}$ ). Users also have firmware control over the switching frequency through Timer2 and the PR2 register. Maximum duty-cycle control is established through the PWMRL register. Refer to Section 26.0, Enhanced PWM Module for details. The entire start-up profile is under user control via software.

# 3.7 Driver Control Circuitry

The internal driver control circuitry of the MCP19116/7 is comprised of an error amplifier (EA), a high-speed comparator and a latch similar to the MCP1631.

The error amplifier generates the control voltage used by the high-speed PWM comparator. There is an internally generated reference voltage, V<sub>RFF</sub>. The difference or error between this internal reference voltage and the actual feedback voltage is the control voltage. Some applications will implement parked times where the gate drives are not active. For example, when changing between LED strings and after voltage repositioning, the user can disable the gate drives and park the error amplifier output low. During the time when the EA is parked, its output will be clamped low (1 \* BG) such that it is in a known state when reactivated. Before the output switches are re-enabled, it may be necessary to re-enable the EA some time prior to enabling the output drivers. This prior-EA enable time will allow the EA to slew towards the intended target and prevent the secondary switch from turning on for an extensive period of time, unintentionally discharging the output capacitance and the output voltage down. External compensation is used to stabilize the control system.

Since the MCP19116/7 devices are peak current mode controlled, the comparator compares the primary peak current waveform (IP) that is based upon the current flowing in the primary side with the error amplifier control output voltage. This error amplifier control output voltage also has user-programmable slope compensation subtracted from it. In fixed-frequency applications, the slope compensation signal is generated to be greater than 1/2 the down slope of the inductor current waveform and is controlled by the SLPCRCON register. Offset adjust ability is also available to set the peak current limit of the primary switch for overcurrent protection. The range of the slope compensation ramp is specified. When the current sense signal reaches the level of the control voltage minus slope compensation, the ON cycle is terminated and the external PDRV switch is latched off until the beginning of the next cycle which begins at the next clock cycle.

To improve current regulation at low levels, a pedestal voltage (VZC) set to the BG (1.23V) is implemented. This virtual ground serves as the reference for the error amplifier (A1), slope compensation, current sense amplifier (A2) and the  $I_P$  offset adjustment.

An S-R latch (Set-Rest-Flip-Flop) is used to prevent the PWM circuitry from turning the external switch on until the beginning of the next clock cycle.

## 3.8 Fixed PWM Frequency

The switching frequency of the MCP19116/7 while not controlled by the DESAT comparator output is generated by using a single edge of the 8 MHz internal clock. The user sets the MCP19116/7 switching frequency by configuring the PR2 register. The maximum allowable PDRV duty cycle is adjustable and is controlled by the PWMRL register. The programmable range of the switching frequency will be 31.25 kHz to 2 MHz. The available switching frequency below 2 MHz is defined as  $F_{SW}$  = 8 MHz/N, where N is a whole number between  $4 \le N \le 256$ . Refer to Section 26.0 "Enhanced PWM Module" for details.

# 3.9 V<sub>REF</sub>

This reference is used to generate the voltage connected to the non-inverting input of the error amplifier. The entire analog control loop is raised to a virtual ground pedestal equal to the Band Gap voltage (1.23V).

## 3.10 OV REF

This reference is used to set the output overvoltage set point. It is compared to the  $V_{\rm S}$  input pin, which is typically proportional to the output voltage based on a resistor divider. OV protection, when enabled, can be set to a value for the protection of system circuitry, or it can be used to "ripple" regulate the converter output voltage for repositioning purposes. For details, refer to Register 6-4.

# 3.11 Independent Gate Drive with Programmable Delay

Two independent low-side gate drives are integrated for synchronous applications. Programmable delay has been implemented to improve efficiency and prevent shoot-through currents. Each gate drive has an independent enable input controlled by the PE1 register and programmable dead time controlled by the DEADCON register.

# 3.12 Temperature Management

### 3.12.1 THERMAL SHUTDOWN

To protect the MCP19116/7 from overtemperature conditions, a 150°C junction temperature thermal shutdown has been implemented. When the junction temperature reaches this limit, the device disables the output drivers. In Shutdown mode, both PDRV and SDRV outputs are disabled and the overtemperature flag (OTIF) is set in the PIR2 register. When the junction temperature is reduced by 20°C to 130°C, the MCP19116/7 can resume normal output drive switching.

#### 3.12.2 TEMPERATURE REPORTING

The MCP19116/7 devices have a second on-chip temperature monitoring circuit that can be read by the ADC through the analog test MUX. Refer to Section 21.0 "Internal Temperature Indicator Module" for details on this internal temperature monitoring circuit.

# 4.0 ELECTRICAL CHARACTERISTICS

# 4.1 ABSOLUTE MAXIMUM RATINGS †

| V <sub>IN</sub> - V <sub>GND</sub> (DC)                                         | 0.3V to +44V                             |

|---------------------------------------------------------------------------------|------------------------------------------|

| V <sub>IN</sub> - V <sub>GND</sub> (DC)<br>V <sub>IN</sub> (transient < 500 ms) | +48V                                     |

| PDRV                                                                            | (GND - $0.3V$ ) to ( $V_{DR} + 0.3V$ )   |

| SDRV                                                                            | (GND - 0.3V) to (V <sub>DR</sub> + 0.3V) |

| V <sub>DD</sub> Internally Generated                                            | +6.5V                                    |

| V <sub>DR</sub> Externally Generated                                            | +13.5V                                   |

| Voltage on MCLR with respect to GND                                             |                                          |

| Maximum voltage: any other pin                                                  |                                          |

| Maximum output current sunk by any single I/O pin                               | 25 mA                                    |

| Maximum output current sourced by any single I/O pin                            | 25 mA                                    |

| Maximum current sunk by all GPIO                                                |                                          |

| Maximum current sourced by all GPIO                                             | 35 mA                                    |

| Storage Temperature                                                             | 65°C to +150°C                           |

| Maximum Junction Temperature                                                    | +150°C                                   |

| Operating Junction Temperature                                                  | 40°C to +125°C                           |

| ESD protection on all pins (HBM)                                                |                                          |

| ESD protection on all pins (MM)                                                 | 200V                                     |

**† Notice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### 4.2 Electrical Characteristics

| Electrical Specificatio apply over the T <sub>A</sub> range                  |                           |      | = 12V, F <sub>SW</sub> | = 150 kHz, | $T_A = +25$ | °C. <b>Boldface</b> specifications                         |

|------------------------------------------------------------------------------|---------------------------|------|------------------------|------------|-------------|------------------------------------------------------------|

| Parameters                                                                   | Sym.                      | Min. | Тур.                   | Max.       | Units       | Conditions                                                 |

| Input                                                                        |                           |      |                        |            |             |                                                            |

| Input Voltage                                                                | V <sub>IN</sub>           | 4.5  | _                      | 42         | V           |                                                            |

| Input Quiescent                                                              | ΙQ                        | _    | 6                      | 7.5        | mA          | V <sub>IN</sub> = 12V, Not switching                       |

| Current                                                                      |                           | _    | 6                      | 7.5        |             | V <sub>IN</sub> = 20V, Not switching                       |

| Shutdown Current                                                             | I <sub>SHDN</sub>         | _    | 50                     | 80         | μA          | V <sub>IN</sub> = 12V<br>(Note 1)                          |

| Linear Regulator V <sub>DD</sub>                                             |                           |      |                        |            |             |                                                            |

| Internal Circuitry Bias<br>Voltage                                           | V <sub>DD</sub>           | 4.75 | 5.1                    | 5.5        | V           | V <sub>IN</sub> = 6.0V to 42V                              |

| Maximum External V <sub>DD</sub> Output Current                              | I <sub>DD_OUT</sub>       | 35   | _                      | _          | mA          | V <sub>IN</sub> = 6.0V to 42V<br>(Note 2)                  |

| Internal Circuitry Bias<br>Voltage during SLEEP                              | V <sub>DD_SLEEP</sub>     | 2.4  | _                      | 4          | V           | V <sub>IN</sub> = 4.5V to 42V<br>I <sub>DD_OUT</sub> = 1mA |

| Maximum Available<br>External V <sub>DD</sub> Output<br>Current During SLEEP | I <sub>DD_OUT_SLEEP</sub> | 1    | _                      | _          | mA          | $V_{IN}$ = 6.0V to 42V<br>$V_{DD}$ = $V_{DD\_SLEEP}$       |

- Note 1: Refer to Section 16.0, Power-Down Mode (Sleep).

- 2:  $V_{DD}$  is the voltage present at the  $V_{DD}$  pin.

- 3: Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value measured at a 1V differential between V<sub>IN</sub> and V<sub>DD</sub>.

- 4: Ensured by design, not production tested.

- **5:** These parameters are characterized, but not production tested.

- **6:** The V<sub>DD</sub> LDO will limit the total source current to a maximum of 35 mA. Individually each pin can source a maximum of 15 mA.

# 4.2 Electrical Characteristics (Continued)

**Electrical Specifications:** Unless otherwise noted,  $V_{IN}$  = 12V,  $F_{SW}$  = 150 kHz,  $T_A$  = +25°C. **Boldface** specifications apply over the  $T_A$  range of -40°C to +125°C.

| Parameters                           | Sym.                                                | Min. | Тур.  | Max. | Units | Conditions                                                                                                   |

|--------------------------------------|-----------------------------------------------------|------|-------|------|-------|--------------------------------------------------------------------------------------------------------------|

| Line Regulation                      | $\Delta V_{DD-OUT}/$ $(V_{DD-OUT} * \Delta V_{IN})$ | -0.1 | 0.002 | 0.1  | %/V   | $(V_{DD} + 1.0V) \le V_{IN} \le 20V$ (Note 2)                                                                |

| Load Regulation                      | $\Delta V_{DD	ext{-}OUT}/V_{DD	ext{-}OUT}$          | -1.0 | 0.1   | 1.0  | %     | I <sub>DD_OUT</sub> = 1 mA to 20 mA (Note 2)                                                                 |

| Output Short-Circuit Current         | I <sub>DD_SC</sub>                                  | _    | 50    | _    | mA    | V <sub>IN</sub> = (V <sub>DD</sub> + 1.0V)<br>(Note 2)                                                       |

| Dropout Voltage                      | $V_{IN} - V_{DD}$                                   | _    | 0.3   | 0.5  | V     | I <sub>DD_OUT</sub> = 20 mA<br>(Notes 2 and 3)                                                               |

| Power Supply<br>Rejection Ratio      | PSRR <sub>LDO</sub>                                 | _    | 60    | _    | dB    | $f \le 1000 \text{ Hz}$<br>$I_{DD\_OUT} = 25 \text{ mA}$<br>$C_{IN} = 0 \mu\text{F}, C_{DD} = 1 \mu\text{F}$ |

| Linear Regulator AVD                 | D                                                   |      |       |      |       |                                                                                                              |

| Internal Analog<br>Supply Voltage    | AV <sub>DD</sub>                                    | _    | 4.096 | _    | V     |                                                                                                              |

| AV <sub>DD</sub> Tolerance           | AV <sub>DD_TOL</sub>                                | -2.5 | ±0.5  | 2.5  | %     | Trimmed at 25°C,<br>0°C to 125°C                                                                             |

|                                      |                                                     | -3.3 | _     | 3.3  | %     | -40°C to 0°C                                                                                                 |

| Band Gap Voltage                     | BG                                                  | _    | 1.23  | _    | V     | Trimmed at 1.0% tolerance                                                                                    |

| Band Gap Tolerance                   | BG <sub>TOL</sub>                                   | -2.5 | _     | 2.5  | %     |                                                                                                              |

| Input UVLO Voltage                   |                                                     |      |       |      |       |                                                                                                              |

| UVLO Range                           | UVLO <sub>ON</sub>                                  | 4    | _     | 20   | V     | V <sub>IN</sub> Falling                                                                                      |

| UVLO <sub>ON</sub> Trip<br>Tolerance | UVLO <sub>TOL</sub>                                 | -14  | _     | 14   | %     | V <sub>IN</sub> Falling<br>UVLO trip set to 9V<br>VINUVLO = 0x21h                                            |

| UVLO Hysteresis                      | UVLO <sub>HYS</sub>                                 | 1    | 4     | 8    | %     | Hysteresis is based upon<br>the UVLO <sub>ON</sub> setting<br>UVLO trip set to 9V<br>VINUVLO = 0x21h         |

| Resolution                           | nbits                                               | _    | 6     | _    | bits  | Logarithmic Steps                                                                                            |

| UVLO Comparator                      | <u></u>                                             |      |       |      |       |                                                                                                              |

| Input-to-Output Delay                | TD                                                  | _    | 5     | _    | μs    | 100 ns rise time to 1V overdrive on V <sub>IN</sub> V <sub>IN</sub> > UVLO to flag set                       |

| Input OVLO Voltage                   |                                                     |      |       |      |       |                                                                                                              |

| OVLO Range                           | OVLO <sub>ON</sub>                                  | 8.8  | _     | 44   | V     | V <sub>IN</sub> Rising                                                                                       |

| OVLO <sub>ON</sub> Trip<br>Tolerance | OVLO <sub>TOL</sub>                                 | -14  | _     | 14   | %     | V <sub>IN</sub> Rising<br>OVLO trip set to 18V<br>VINOVLO = 0x1Fh                                            |

- Note 1: Refer to Section 16.0, Power-Down Mode (Sleep).

- **2:**  $V_{DD}$  is the voltage present at the  $V_{DD}$  pin.

- 3: Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value measured at a 1V differential between  $V_{IN}$  and  $V_{DD}$ .

- **4:** Ensured by design, not production tested.

- **5**: These parameters are characterized, but not production tested.

- **6:** The V<sub>DD</sub> LDO will limit the total source current to a maximum of 35 mA. Individually each pin can source a maximum of 15 mA.

# 4.2 Electrical Characteristics (Continued)

**Electrical Specifications:** Unless otherwise noted,  $V_{IN}$  = 12V,  $F_{SW}$  = 150 kHz,  $T_A$  = +25°C. **Boldface** specifications apply over the  $T_A$  range of -40°C to +125°C.

| Parameters                         | Sym.                  | Min. | Тур. | Max.   | Units | Conditions                                                                                   |

|------------------------------------|-----------------------|------|------|--------|-------|----------------------------------------------------------------------------------------------|

| OVLO Hysteresis                    | OVLO <sub>HYS</sub>   | 1    | 5    | 8      | %     | Hysteresis is based upon the OVLO <sub>ON</sub> setting OVLO trip set to 18V VINOVLO = 0x1Fh |

| Resolution                         | nbits                 | _    | 6    | _      | bits  | Logarithmic Steps                                                                            |

| OVLO Comparator                    |                       |      |      |        |       |                                                                                              |

| Input-to-Output Delay              | TD                    | _    | 5    | _      | μs    | 100 ns rise time to 1V overdrive on V <sub>IN</sub> V <sub>IN</sub> > OVLO to flag set       |

| Output OV DAC                      |                       |      |      |        |       |                                                                                              |

| Resolution                         | nbits                 | _    | 8    | _      | bits  | Linear DAC                                                                                   |

| Full-Scale Range                   | FSR                   | 0    | _    | 2 * BG | V     |                                                                                              |

| Tolerance                          | OVREF <sub>TOL</sub>  | -2.0 | ±0.3 | 2.0    | %     | Trimmed @ code = 0xCC at 25°C, 0°C to 125°C                                                  |

|                                    |                       | -3.3 | _    | 3.3    | %     | -40°C to 0°C                                                                                 |

| <b>Output OV Comparato</b>         | r                     |      |      | •      |       |                                                                                              |

| OV Hysteresis                      | OV <sub>HYS</sub>     | _    | 50   | _      | mV    |                                                                                              |

| Input Bias Current                 | I <sub>BIAS</sub>     | _    | ±1   | _      | μA    |                                                                                              |

| Common-Mode Input<br>Voltage Range | $V_{CMR}$             | 0    | _    | 3.0    | V     | Note 4                                                                                       |

| Input-to-Output Delay              | TD                    | _    | 200  | _      | ns    | 100 ns rise time to 1V overdrive on V <sub>S</sub> V <sub>S</sub> > OV to flag set (Note 4)  |

| Voltage Reference DAG              | C (V <sub>REF</sub> ) |      |      |        |       |                                                                                              |

| Resolution                         | nbits                 | _    | 8    |        | bits  | Linear DAC                                                                                   |

| Full-Scale Range                   | FSR                   | BG   |      | 2 * BG | V     | Pedestal set to BG                                                                           |

| Tolerance                          | V <sub>REF_TOL</sub>  | -2.0 | ±0.2 | 2.0    | %     | Trimmed @ code = 0xCC at 25°C, 0°C to 125°C                                                  |

|                                    |                       | -3.3 | _    | 3.3    | %     | -40°C to 0°C                                                                                 |

- Note 1: Refer to Section 16.0, Power-Down Mode (Sleep).

- 2:  $V_{DD}$  is the voltage present at the  $V_{DD}$  pin.

- 3: Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value measured at a 1V differential between  $V_{IN}$  and  $V_{DD}$ .

- **4:** Ensured by design, not production tested.

- **5:** These parameters are characterized, but not production tested.

- **6:** The V<sub>DD</sub> LDO will limit the total source current to a maximum of 35 mA. Individually each pin can source a maximum of 15 mA.

# 4.2 Electrical Characteristics (Continued)

**Electrical Specifications:** Unless otherwise noted,  $V_{IN}$  = 12V,  $F_{SW}$  = 150 kHz,  $T_A$  = +25°C. **Boldface** specifications apply over the  $T_A$  range of -40°C to +125°C.

| Parameters                              | Sym.                    | Min.    | Тур. | Max.                 | Units | Conditions                                                                                                               |

|-----------------------------------------|-------------------------|---------|------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------|

| Voltage Reference DA                    | C (V <sub>REF2</sub> )  |         |      | 1                    |       |                                                                                                                          |

| Resolution                              | nbits                   | _       | 8    | _                    | bits  | Linear DAC                                                                                                               |