# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

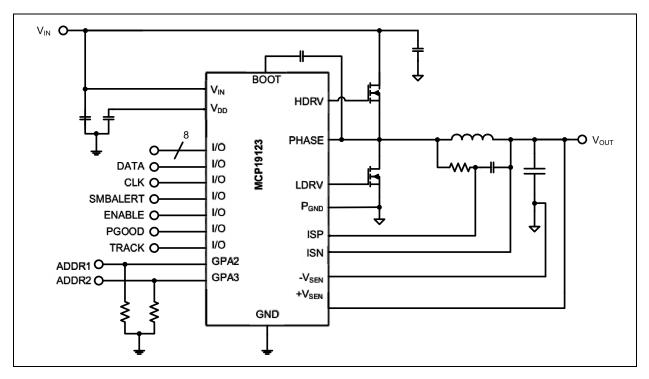

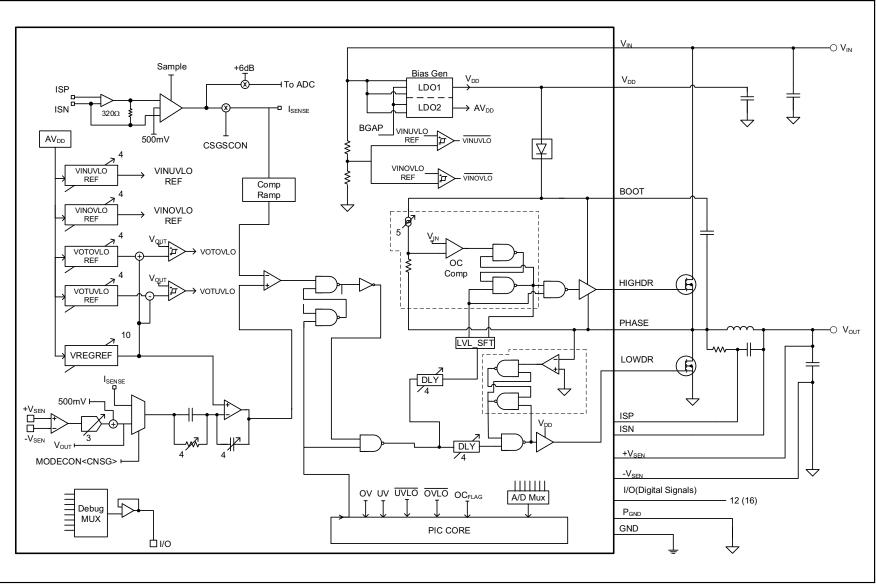

# MCP19122/3

# Digitally Enhanced Power Analog Controller with Integrated Synchronous Driver

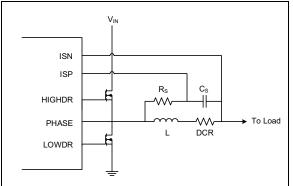

# Synchronous Buck Features

- Input Voltage: 4.5V to 40V (operating), 48V (non-operating)

- Output Voltage: 0.3V to 16V

- 0.1% typical output voltage accuracy

- Greater than 16V requires external divider

- Switching Frequency: 100 kHz to 1.6 MHz

- Shutdown Quiescent Current: 50 µA Typical

- · High-Drive:

- +5V Gate Drive

- 2A Source Current

- 2A Sink Current

- Low-Drive:

- +5V Gate Drive

- 2A Source Current

- 4A Sink Current

- Emulated Average Current Mode Control

- Differential Remote Output Sense

- Multi-Phase Systems:

- Master or Slave

- Frequency Synchronized

- Common Current Sense Signal

- Multiple Output Systems:

- Master or Slave

- Frequency Synchronized

- AEC-Q100 Qualified

- Configureable Parameters:

- Overcurrent Limit

- Input Undervoltage Lockout

- Input Overvoltage

- Output Overvoltage

- Output Undervoltage

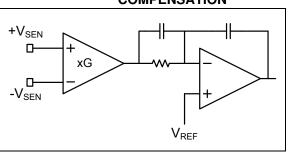

- Internal Analog Compensation

- Soft Start Profile

- Synchronous Driver Dead Time

- Switching Frequency

- Thermal Shutdown

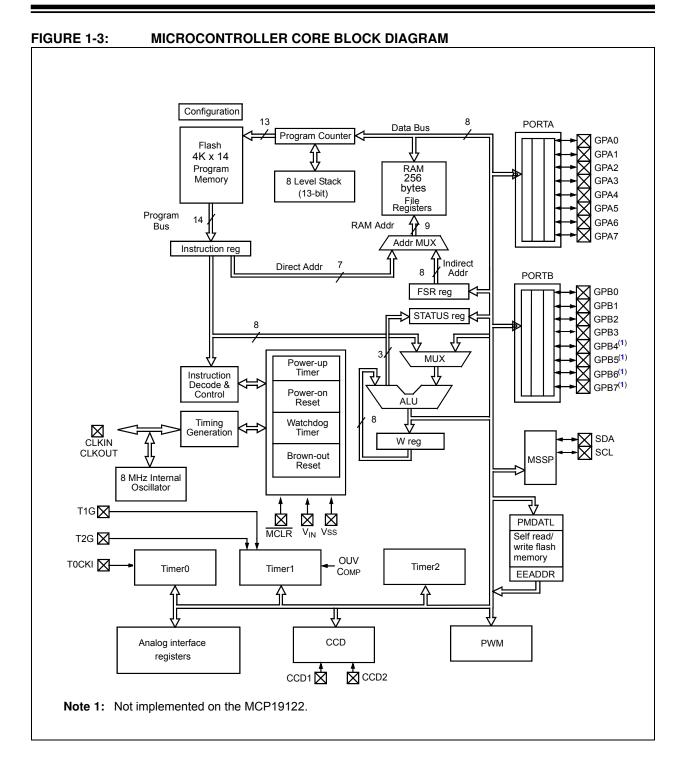

## **Microcontroller Features**

- Precision 8 MHz Internal Oscillator Block:

- Factory Calibrated

- Interrupt Capable

- Firmware

- Interrupt-on-Change Pins

- Only 35 Instructions to Learn

- · 4096 Words On-Chip Program Memory

- High Endurance Flash:

- 100,000 Write Flash Endurance

- Flash Retention: >40 years

- Watchdog Timer (WDT) with Independent Oscillator for Reliable Operation

- Programmable Code Protection

- In-Circuit Debug (ICD) via Two Pins (MCP19123)

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- 12 I/O Pins and One Input-Only Pin (MCP19122)

- 3 Open Drain Pins

- 2 Weak Current Source Pins

- 16 I/O Pins and One Input-Only Pin (MCP19123)

- 3 Open Drain Pins

- 2 Weak Current Source Pins

- Analog-to-Digital Converter (ADC):

- 10-bit Resolution

- 24 Internal Channels

- 8 External Channels

- Timer0: 8-bit Timer/Counter with 8-Bit Prescaler

- Enhanced Timer1:

- 16-bit Timer/Counter with Prescaler

- 2 Selectable Clock Sources

- External Gate Input Mode

- Timer2: 8-Bit Timer/Counter with Prescaler

- 8-bit Period Register

- Capture, Compare Module

- I<sup>2</sup>C<sup>™</sup> Communication:

- 7-bit Address Masking

- 2 Dedicated Address Registers

- SMBus/PMBus<sup>™</sup> Compatibility

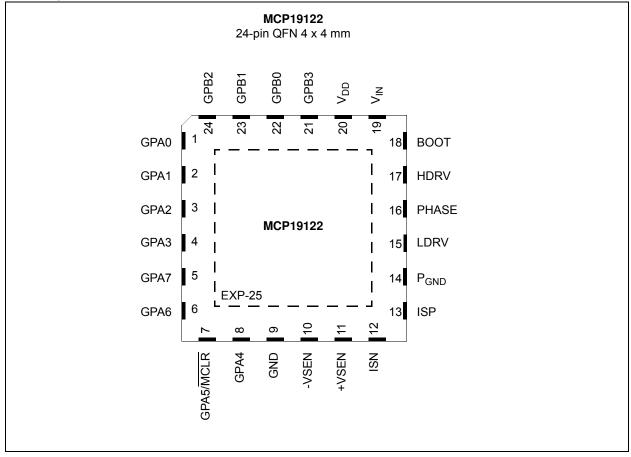

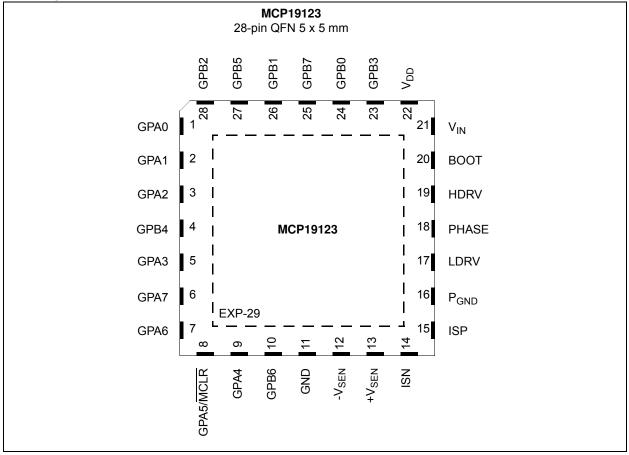

# Pin Diagram – 24-Pin 4X4 QFN (MCP19122)

| 24-PIN QFN (MCP19122) SUMMARY |                                                                                                                                                                                                |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 24-Pin QFN                    | ANSEL                                                                                                                                                                                          | A/D                                                                                                                                                                                                                                                           | Timers                                                                                                                                                                                                                                                                                                                                                  | MSSP                                                                                                                                                                                                                                                                                                                                                                                                  | Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dn-IIn4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Basic                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Additional                                                                       |

| 1                             | Y                                                                                                                                                                                              | AN0                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                     | IOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Analog Debug Output <sup>(1)</sup>                                               |

| 2                             | Y                                                                                                                                                                                              | AN1                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                     | IOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Sync Signal In/Out <sup>(2, 3)</sup>                                             |

| 3                             | Y                                                                                                                                                                                              | AN2                                                                                                                                                                                                                                                           | TOCKI                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                       | IOC<br>INT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Weak Current Source                                                              |

| 4                             | Y                                                                                                                                                                                              | AN3                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                     | IOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Weak Current Source<br>Timer1 Gate Input 1                                       |

| 8                             | Ν                                                                                                                                                                                              | —                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                       | IOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —                                                                                |

| 7                             | Ν                                                                                                                                                                                              | —                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                       | IOC <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Y <sup>(5)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                |

| 6                             | Ν                                                                                                                                                                                              | _                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                     | IOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ICSPDAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | —                                                                                |

| 5                             | Ν                                                                                                                                                                                              | —                                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                       | SCL                                                                                                                                                                                                                                                                                                                                                                                                   | IOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ICSPCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | —                                                                                |

| 22                            | Ν                                                                                                                                                                                              | _                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                       | SDA                                                                                                                                                                                                                                                                                                                                                                                                   | IOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —                                                                                |

| 23                            | Y                                                                                                                                                                                              | AN4                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                     | IOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Current Sense Output<br>Current Reference Input <sup>(3)</sup>                   |

| 24                            | Y                                                                                                                                                                                              | AN5                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                       | IOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Timer1 Gate Input 2                                                              |

| 21                            | Ν                                                                                                                                                                                              |                                                                                                                                                                                                                                                               | _                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                       | IOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Clock Signal In/Out <sup>(2, 3)</sup>                                            |

| 19                            | Ν                                                                                                                                                                                              | —                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Device Input Voltage                                                             |

| 20                            | Ν                                                                                                                                                                                              | —                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Internal Regulator Output                                                        |

| 9                             | Ν                                                                                                                                                                                              | —                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Small Signal Ground                                                              |

| 14                            | Ν                                                                                                                                                                                              | —                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Large Signal Ground                                                              |

| 15                            | Ν                                                                                                                                                                                              | _                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Low-Side MOSFET<br>Connection                                                    |

| 17                            | Ν                                                                                                                                                                                              | —                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | High-Side MOSFET<br>Connection                                                   |

| 16                            | Ν                                                                                                                                                                                              | _                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Switch Node                                                                      |