# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# MCP19214/5

# Digitally Enhanced Power Analog, Dual Channel, Low-Side PWM Controller

# Features

- AEC Q100 Qualified and PPAP Capable

- Input Voltage Range: 4.5V-42V

- Two Independent High-Performance PWM Controllers

- Two Independent Control Loops per Channel allowing the User to Simultaneously Control the Output Voltage and Current

- Can Be Configured to Control Multiple Topologies including but Not Limited To:

- Boost

- Flyback

- Ćuk

- Single-Ended Primary-Inductor Converter (SEPIC)

- Peak Current Mode Control

- Master/Slave Operation of the PWM Controllers with Adjustable Phase Shift

- Differential Output Current Sense Capability

- Integrated Low-Side Current Sense Differential Amplifier (10X)

- Integrated Low-Side Gate Drivers:

- 0.5A Sink/Source Current Capability at 5V Supply Voltage

- 1A Sink/Source Current Capability at 10V Supply Voltage

- Special Events Generator (the state of regulating loops can be monitored without firmware overhead)

- Configurable Parameters:

- Reference Voltages for Regulating Loops (four internal DACs)

- Input Undervoltage Lockout (UVLO)

- Input Overvoltage Lockout (OVLO)

- Primary Current Leading Edge Blanking: 0 ns, 50 ns, 100 ns and 200 ns

- Fixed Switching Frequency Range: 31.25 kHz-2.0 MHz

- Slope Compensation

- Primary Current Sense Offset Adjustment

- Configurable GPIO Pin Options

- Low Quiescent Current: 10 mA Typical

- Low Sleep Current: 120 µA Typical

- · Thermal Shutdown

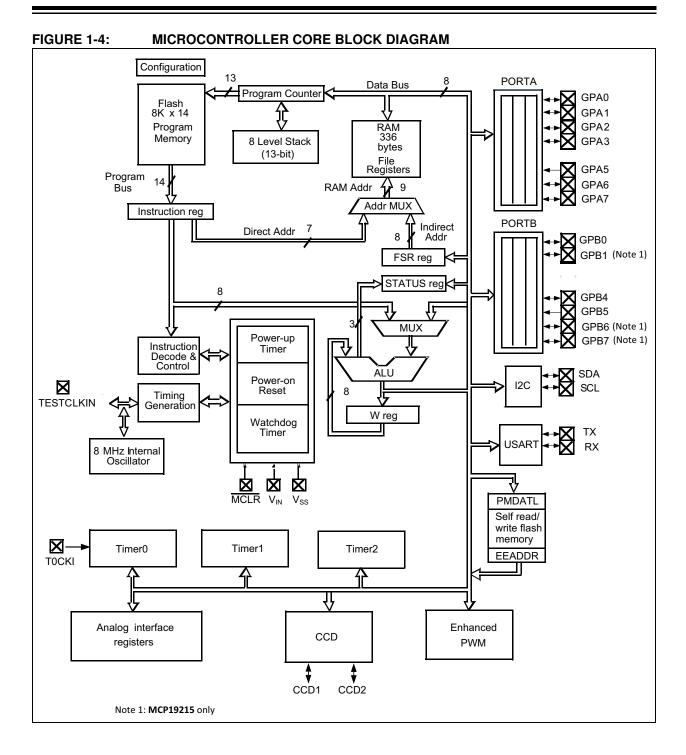

#### **Microcontroller Features**

- Precision 8 MHz Internal Oscillator Block:

- Factory-Calibrated to ±1%, Typical

- Interrupt-Capable

- Firmware

- Interrupt-on-Change Pins

- Only 35 Instructions to Learn

- 8192 Words On-Chip Program Memory

- 336 bytes of Internal RAM

- High-Endurance Flash:

- 100,000 Write Flash Endurance

- Flash Retention: > 40 Years

- Watchdog Timer (WDT) with Independent Oscillator for Reliable Operation

- Programmable Code Protection

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- Up to 12 I/O Pins and One Input-Only Pin

- Analog-to-Digital Converter (ADC):

- 10-Bit Resolution

- Internal 4096 mV Precision Reference Generator

- Up to 8 External Channels

- Timer0: 8-Bit Timer/Counter with 8-Bit Prescaler

- Enhanced Timer1:

- 16-bit Timer with Prescaler

- Two Selectable Clock Sources

- Timer2: 8-Bit Timer with Prescaler

- 8-Bit Period Register

- I<sup>2</sup>C Communication:

- 7-bit Address Masking

- Two Dedicated Address Registers

- Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) (only MCP19215):

- 8 and 9-Bit Data Operations

- Address Detect

- Asynchronous and Synchronous Operating Modes

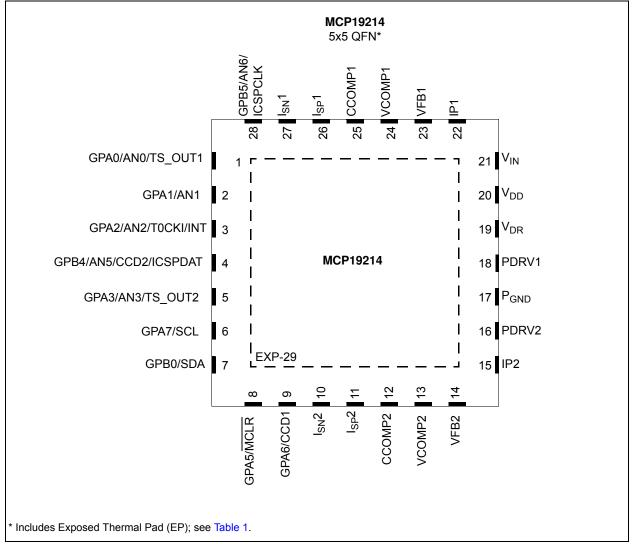

# Pin Diagram – 28-Pin 5x5 QFN (MCP19214)

| I/O<br>28-Din OEN                | Pin QFN | EL    |     |        |      |        |                    |                  |                  |                                                                        |

|----------------------------------|---------|-------|-----|--------|------|--------|--------------------|------------------|------------------|------------------------------------------------------------------------|

| Õ                                | 28-     | ANSEL | A/D | Timers | dSSM | AUSART | Interrupt          | dU-IInq          | Basic            | Additional                                                             |

| GPA0 1                           | 1       | Υ     | AN0 |        | _    |        | IOC                | Y                | _                | Analog Circuitry Debug Out <sup>(1)</sup>                              |

| GPA1 2                           | 2       | Υ     | AN1 | _      |      |        | IOC                | Y                | _                |                                                                        |

| GPA2 3                           | 3       | Y     | AN2 | T0CKI  | —    | _      | IOC<br>INT         | Y                | —                | _                                                                      |

| GPB4 4                           | 4       | Υ     | AN5 |        |      |        | IOC                | Y                | _                | Dual Capture/Compare Input 2                                           |

| GPA3 5                           | 5       | Υ     | AN3 | _      | _    | _      | IOC                | Y                |                  | Digital Circuitry Debug Out <sup>(1)</sup>                             |

| GPA7 6                           | 6       | Ν     | _   | _      | SCL  | _      | IOC                | Y                | ICSPDAT          | —                                                                      |

| GPB0 7                           | 7       | Ν     | _   | _      | SDA  | _      | IOC                | Y                |                  | _                                                                      |

| GPA5 8                           | 8       | Ν     | _   | _      | _    |        | IOC <sup>(2)</sup> | Y <sup>(3)</sup> | MCLR             | Test Enable Input                                                      |

| GPA6 9                           | 9       | Ν     | _   |        | _    | _      | IOC                | Y                | _                | Dual Capture/Compare Input 1                                           |

| I <sub>SN</sub> 2 1              | 10      | -     | —   | -      | —    |        |                    |                  | _                | Current Sense Amplifier Negative<br>Input for PWM Channel 2            |

| I <sub>SP</sub> 2 1 <sup>-</sup> | 11      | —     | —   | —      | —    | —      | _                  | _                |                  | Current Sense Amplifier Positive<br>Input for PWM Channel 2            |

| CCOMP2 1                         | 12      | —     | —   |        | —    |        |                    |                  | _                | The Output of the Error Amplifier of the Current Loop of PWM Channel 2 |

| VCOMP2 1                         | 13      | _     | —   |        | —    | _      |                    |                  | —                | The Output of the Error Amplifier of the Voltage Loop of PWM Channel 2 |

| VFB2 14                          | 14      | —     | —   | _      | _    |        |                    |                  | —                | Feedback Input of the Voltage Loop<br>of PWM Channel 2                 |

| IP2 1                            | 15      | _     | —   |        | _    |        |                    |                  | _                | Primary Input Current Sense<br>of PWM Channel 2                        |

| PDRV2 1                          | 16      | —     | —   | _      | —    | _      | _                  | _                | —                | Gate Drive Output of PWM Channel 2                                     |

| P <sub>GND</sub> 1               | 17      | —     | —   | _      | —    | —      | _                  | _                | —                | Power Ground                                                           |

| PDRV1 1                          | 18      | —     | —   |        | —    | _      | _                  | _                | —                | Gate Drive Output of PWM Channel 1                                     |

| V <sub>DR</sub> 1                | 19      | —     | —   | _      | —    | _      | _                  | _                | —                | Gate Drive Supply Voltage                                              |

| V <sub>DD</sub> 20               | 20      | —     | —   | _      | —    | _      | _                  | _                | —                | V <sub>DD</sub> Output (+5V)                                           |

| V <sub>IN</sub> 2                | 21      | —     | —   |        | —    | _      | _                  | _                | _                | Input Supply Voltage                                                   |

| IP1 22                           | 22      | —     | —   | —      | —    |        |                    |                  | _                | Primary Input Current Sense<br>of PWM Channel 1                        |

| VFB1 2                           | 23      | —     | —   | _      |      | —      |                    | _                | —                | Feedback Input of the Voltage Loop<br>of PWM Channel 1                 |

| VCOMP1 24                        | 24      | —     | _   | _      | —    |        |                    |                  |                  | The Output of the Error Amplifier of the Voltage Loop of PWM Channel 1 |

| CCOMP1 2                         | 25      | —     | —   |        | —    |        |                    |                  | —                | The Output of the Error Amplifier of the Current Loop of PWM Channel 1 |

| I <sub>SP</sub> 1 2              | 26      | —     | —   | —      | —    | _      | —                  | —                | —                | Current Sense Amplifier Positive<br>Input for PWM Channel 1            |

| I <sub>SN</sub> 1 2 <sup>-</sup> | 27      | —     | —   | —      | —    | —      | —                  | —                | —                | Current Sense Amplifier Negative<br>Input for PWM Channel 1            |

| GPB5 2                           | 28      | Υ     | AN6 |        |      | _      | IOC                | Y                | ICSPCLK          |                                                                        |

| EP 29                            | 29      | —     | —   |        | —    |        |                    |                  | A <sub>GND</sub> | Small Signal Ground and Digital Ground                                 |

**Note 1:** The Analog/Digital Debug Output is selected through the control of the ABECON1 register.

**2:** The IOC is disabled when  $\overline{\text{MCLR}}$  is enabled.

3: Weak pull-up always enabled when MCLR is enabled, otherwise the pull-up is under user control.

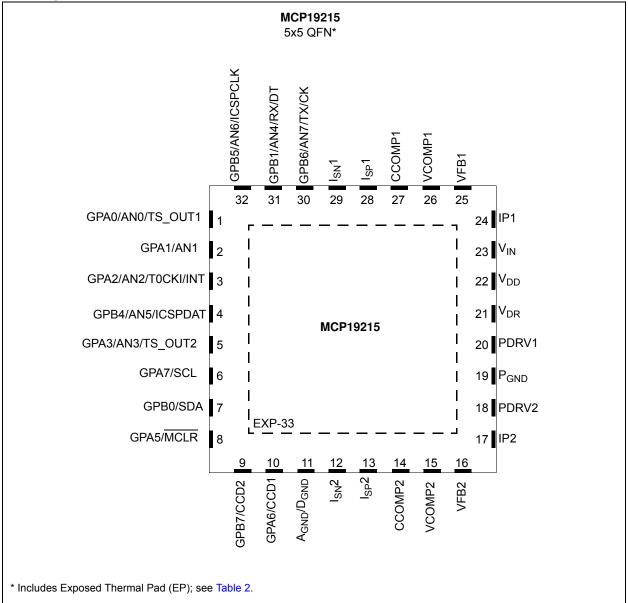

# Pin Diagram - 32-PIN 5X5 QFN (MCP19215)

| TABLE 2:                           | BLE 2: 32-PIN QFN (MCP19215) SUMMARY |       |     |        |      |        |                    |                  |         |                                                                              |

|------------------------------------|--------------------------------------|-------|-----|--------|------|--------|--------------------|------------------|---------|------------------------------------------------------------------------------|

| 0/1                                | 32-Pin QFN                           | ANSEL | A/D | Timers | MSSP | AUSART | Interrupt          | Pull-Up          | Basic   | Additional                                                                   |

| GPA0                               | 1                                    | Υ     | AN0 | _      | _    | _      | IOC                | Y                | _       | Analog Circuitry Debug Out <sup>(1)</sup>                                    |

| GPA1                               | 2                                    | Υ     | AN1 |        | _    | _      | IOC                | Y                | _       | —                                                                            |

| GPA2                               | 3                                    | Y     | AN2 | TOCKI  | —    |        | IOC<br>INT         | Y                | —       | -                                                                            |

| GPB4                               | 4                                    | Y     | AN5 |        |      | _      | IOC                | Y                | ICSPDAT | —                                                                            |

| GPA3                               | 5                                    | Υ     | AN3 | _      |      | _      | IOC                | Y                |         | Digital Circuitry Debug Out <sup>(1)</sup>                                   |

| GPA7                               | 6                                    | Ν     | -   | _      | SCL  |        | IOC                | Y                | _       | Dual Capture/Single<br>Compare1 Input                                        |

| GPB0                               | 7                                    | Ν     | —   | —      | SDA  | _      | IOC                | Y                | _       | —                                                                            |

| GPA5                               | 8                                    | Ν     | _   | —      | _    |        | IOC <sup>(2)</sup> | Y <sup>(3)</sup> | MCLR    |                                                                              |

| GPB7                               | 9                                    | Ν     | _   |        | _    |        | IOC                | Y                |         | —                                                                            |

| GPA6                               | 10                                   | Ν     |     |        |      |        | IOC                | Y                | _       | —                                                                            |

| A <sub>GND</sub> /D <sub>GND</sub> | 11                                   | _     | _   | —      | _    | _      | —                  | —                | _       | —                                                                            |

| I <sub>SN</sub> 2                  | 12                                   | _     | —   | —      | _    | _      | —                  | _                | _       | Current Sense Amplifier<br>Negative Input for PWM Channel<br>2               |

| I <sub>SP</sub> 2                  | 13                                   | —     | _   | —      | —    |        | —                  |                  | -       | Current Sense Amplifier<br>Positive Input for PWM Channel 2                  |

| CCOMP2                             | 14                                   | —     | _   | —      | -    | _      | —                  | _                | -       | The Output of the Error Amplifier<br>of the Current Loop of PWM<br>Channel 2 |

| VCOMP2                             | 15                                   |       | _   | —      | _    | _      | —                  | —                | -       | The Output of the Error Amplifier<br>of the Voltage Loop of PWM<br>Channel 2 |

| VFB2                               | 16                                   | —     |     | —      | _    |        | —                  |                  | —       | Feedback Input of the Voltage<br>Loop of PWM Channel 2                       |

| IP2                                | 17                                   |       |     | —      | _    |        | —                  | —                | -       | Primary Input Current Sense of<br>PWM Channel 2                              |

| PDRV2                              | 18                                   | _     |     | —      | _    | _      | —                  | _                | -       | Gate Drive Output of<br>PWM Channel 2                                        |

| P <sub>GND</sub>                   | 19                                   |       | _   | _      | _    |        | —                  |                  | —       | Power Ground                                                                 |

| PDRV1                              | 20                                   | _     |     | —      | _    | _      | —                  | _                | -       | Gate Drive Output of<br>PWM Channel 1                                        |

| V <sub>DR</sub>                    | 21                                   | _     | _   |        |      |        |                    |                  |         | Gate Drives Supply Voltage                                                   |

| V <sub>DD</sub>                    | 22                                   | —     | _   |        | _    |        | —                  | _                | _       | V <sub>DD</sub> Output (+5V)                                                 |

| V <sub>IN</sub>                    | 23                                   | _     | _   | _      | _    |        | _                  |                  |         | Input Supply Voltage                                                         |

| IP1                                | 24                                   | —     | -   | —      | _    |        | —                  |                  | _       | Primary Input Current Sense of<br>PWM Channel 1                              |

| VFB1                               | 25                                   |       | _   | —      | _    |        | —                  | _                | —       | Feedback Input of the Voltage<br>Loop of PWM Channel 1                       |

TABLE 2: 32-PIN QFN (MCP19215) SUMMARY

Note 1: The Analog/Digital Debug Output is selected through the control of the ABECON1 register.

**2:** The IOC is disabled when  $\overline{\text{MCLR}}$  is enabled.

**3:** Weak pull-up always enabled when  $\overline{MCLR}$  is enabled, otherwise the pull-up is under user control.

# MCP19214/5

| TADLE 2.          | 32-FIN QIN (WEF 19213) SOMMANT (CONTINOED) |       |     |        |      |        |           |         |         |                                                                              |

|-------------------|--------------------------------------------|-------|-----|--------|------|--------|-----------|---------|---------|------------------------------------------------------------------------------|

| 0/1               | 32-Pin QFN                                 | ANSEL | A/D | Timers | MSSP | AUSART | Interrupt | Pull-Up | Basic   | Additional                                                                   |

| VCOMP1            | 26                                         |       | _   | —      | —    | —      | _         | _       | _       | The Output of the Error Amplifier<br>of the Voltage Loop of PWM<br>Channel 1 |

| CCOMP1            | 27                                         | _     |     | —      | _    |        | —         | —       | _       | The Output of the Error Amplifier<br>of the Current Loop of PWM<br>Channel 1 |

| I <sub>SP</sub> 1 | 28                                         | _     |     | _      |      |        | _         | —       | —       | Current Sense Amplifier Positive<br>Input for PWM Channel 1                  |

| I <sub>SN</sub> 1 | 29                                         |       |     | _      |      | _      | _         | —       | —       | Current Sense Amplifier Negative<br>Input for PWM Channel 1                  |

| GPB6              | 30                                         | Υ     | AN7 | _      | _    | TX/CK  | IOC       | Y       | —       | —                                                                            |

| GPB1              | 31                                         | Y     | AN4 | _      | —    | RX/DT  | IOC       | Y       | —       | —                                                                            |

| GPB5              | 32                                         | Y     | AN6 |        |      | —      | IOC       | Y       | ICSPCLK | —                                                                            |

| EP                | 33                                         | _     | _   | _      | _    | —      | _         | _       | —       | —                                                                            |

# TABLE 2: 32-PIN QFN (MCP19215) SUMMARY (CONTINUED)

Note 1: The Analog/Digital Debug Output is selected through the control of the ABECON1 register.

**2:** The IOC is disabled when  $\overline{\text{MCLR}}$  is enabled.

**3:** Weak pull-up always enabled when  $\overline{MCLR}$  is enabled, otherwise the pull-up is under user control.

#### **Table of Contents**

| 1.0   | Device Overview                                                              | 0   |

|-------|------------------------------------------------------------------------------|-----|

| 2.0   | Pin Description                                                              |     |

| 3.0   | Functional Description                                                       |     |

| 4.0   | Electrical Characteristics                                                   |     |

| 5.0   | Digital Electrical Characteristics                                           |     |

| 6.0   | Configuring the MCP19214/5                                                   |     |

| 7.0   | Typical Performance Curves                                                   |     |

| 8.0   | System Bench Testing                                                         |     |

| 9.0   | Device Calibration                                                           |     |

| 10.0  | Memory Organization                                                          |     |

| 11.0  | Device Configuration                                                         |     |

| 12.0  | Resets                                                                       |     |

| 13.0  | Interrupts                                                                   |     |

| 14.0  | Watchdog Timer (WDT)                                                         |     |

| 15.0  | Interrupt-On-Change                                                          |     |

| 16.0  | Oscillator Modes                                                             |     |

| 17.0  | Flash Program Memory Control                                                 |     |

| 18.0  | I/O Ports                                                                    | 125 |

| 19.0  | Power-Down Mode (Sleep)                                                      | 133 |

|       | Analog-to-Digital Converter (ADC) Module                                     |     |

| 21.0  | Timer0 Module                                                                |     |

| 22.0  | Timer1 Module                                                                | 147 |

|       | Timer2 Module                                                                |     |

|       | Enhanced PWM Module                                                          |     |

|       | Internal Temperature Indicator Module                                        |     |

|       | PWM Control Logic                                                            |     |

|       | Master Synchronous Serial Port (MSSP) Module                                 |     |

|       | Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) |     |

|       | Application Hints                                                            |     |

| 30.0  | Instruction Set Summary                                                      |     |

| 31.0  | Dual Capture/Compare (CCD) Module                                            |     |

|       | In-Circuit Serial Programming™ (ICSP™)                                       |     |

| 33.0  |                                                                              |     |

|       | Packaging Information                                                        |     |

|       | ndix A: Revision History                                                     |     |

|       |                                                                              |     |

|       | Microchip Web Site                                                           |     |

|       | omer Change Notification Service                                             |     |

|       | omer Support                                                                 |     |

|       | uct Identification System                                                    |     |

|       | emarks                                                                       |     |

| World | dwide Sales and Service                                                      |     |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via e-mail at docerrors@microchip.com. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our web site at:

#### www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's web site; www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

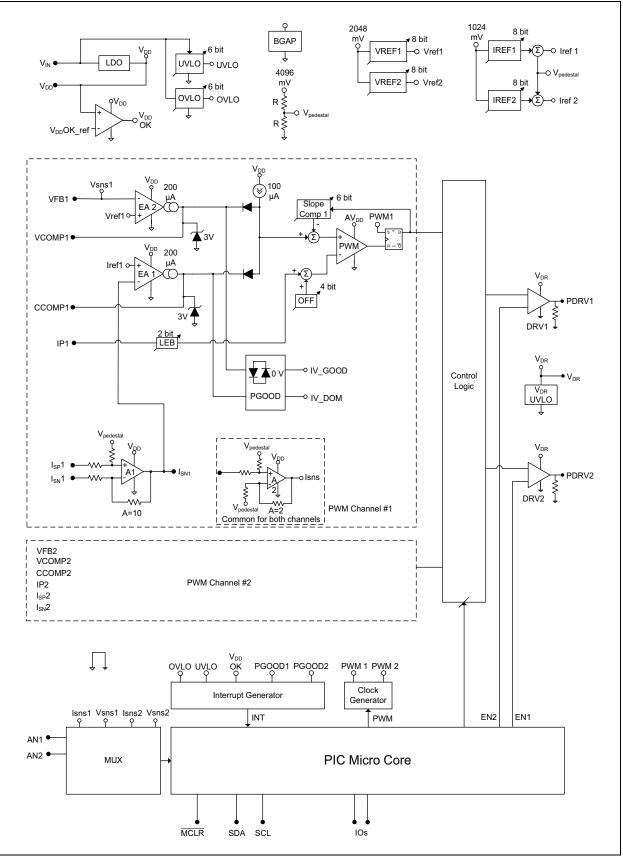

# 1.0 DEVICE OVERVIEW

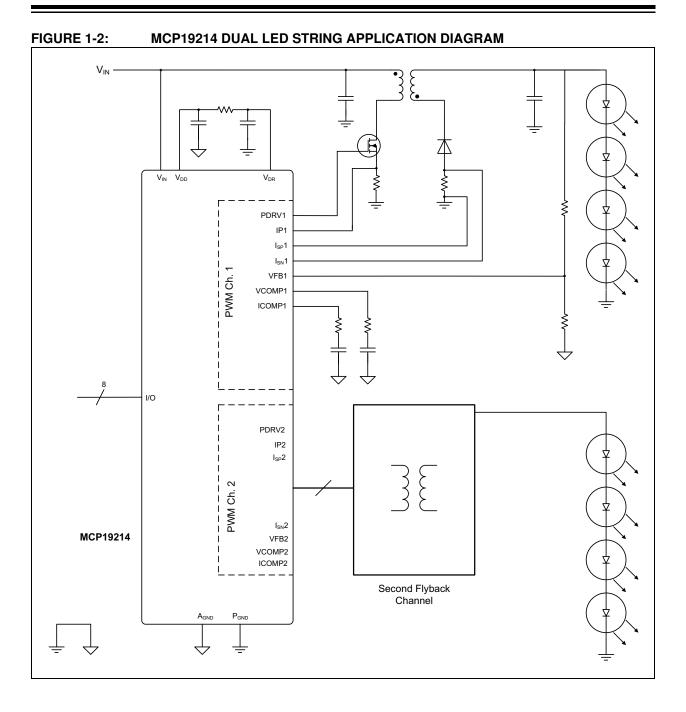

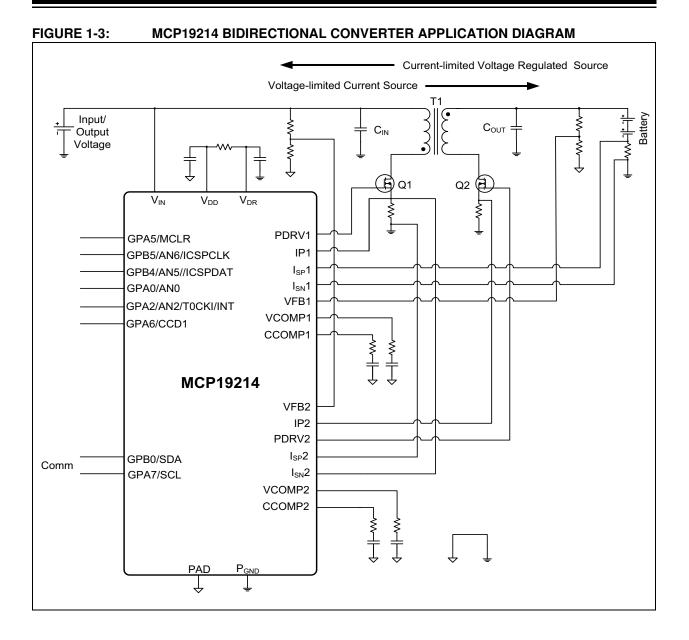

The MCP19214/5 devices are highly integrated, digitally enhanced PWM controllers, used for battery chargers, bidirectional converters, LED lighting systems and other low-side switch PWM applications.

These devices feature two independent analog PWM controllers, and the internal architecture is optimized for applications that require precise control of the output parameters. Like the other members of the digitally enhanced PWM controllers family, MCP19214/5 includes a fully programmable microcontroller core and a 10-bit analog-to-digital converter.

Each PWM channel includes two error amplifiers with independent adjustable reference voltage generators, current sense input with programmable leading edge blanking, programmable slope compensation ramp generator, integrated internal programmable oscillator, current sense differential amplifier and an integrated MOSFET driver.

An internal LDO (+5V) is used to power the PIC core, the analog circuitry and to provide 5V externally. This 5V external output can also be used to supply the internal MOSFET drivers. The internal MOSFET drivers have the option to be powered from an external voltage source (up to 10V) in order to accommodate applications that require higher voltages for gate driving.

The MCP19214/5 controllers offer a very high degree of integration, allowing the user to develop complex applications without additional circuitry. Some unique features, like simultaneous control of the converter's output current and voltage, make MCP19214/5 devices ideally suited for battery chargers, LED drivers and bidirectional converters. Additionally, the General Purpose Inputs/Outputs (GPIOs) can be used to drive various switches, to enable/disable additional circuitry, or to indicate a typical state. The MCP19214 is packaged in a 28-lead 5 mm x 5 mm QFN, and the MCP19215 in a 32-lead 5 mm x 5 mm QFN. The operating input voltage for normal device operation is 4.5V-42V, with an absolute maximum of 44V. The maximum transient voltage is 48V for 500 mS.

Power trains supported by this architecture include, but are not limited to, Boost, Buck-Boost, Flyback, SEPIC and Cuk.

MCP19214/5 integrates an I<sup>2</sup>C controller and an Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) module (only for MCP19215). The user can develop specific communication protocols using the internal interfaces. A PMBus compatible protocol, specific for power converters, can be implemented using the provided I<sup>2</sup>C serial bus.

Complete customization of the device operating parameters, start-up or shutdown profiles, protection levels and fault handling procedures are accomplished by firmware that can be developed using Microchip's MPLAB<sup>®</sup> X Integrated Development Environment. Programming the MCP19214/5 is done using one of Microchip's many in-circuit debugger and device programmers.

# MCP19214/5

# MCP19214/5

# 2.0 PIN DESCRIPTION

The 28-lead MCP19214 and 32-lead MCP19215 devices feature pins that have multiple functions associated with each pin. Table 2-1 provides a description of the different functions. Refer to **Section 2.1 "Detailed Pin Functional Description"** for more detailed information.

| Name                    | Function | Input<br>Type    | Output<br>Type | Description                                                                     |

|-------------------------|----------|------------------|----------------|---------------------------------------------------------------------------------|

| GPA0/AN0/TS_OUT1        | GPA0     | TTL              | CMOS           | General-purpose I/O                                                             |

|                         | AN0      | AN               |                | A/D Channel 0 input                                                             |

|                         | TS_OUT1  |                  |                | Internal analog signal multiplexer output <sup>(1)</sup>                        |

| GPA1/AN1                | GPA1     | TTL              | CMOS           | General-purpose I/O                                                             |

|                         | AN1      | AN               | _              | A/D Channel 1 input                                                             |

| GPA2/AN2/T0CKI/INT      | GPA2     | ST               | CMOS           | General-purpose I/O                                                             |

|                         | AN2      | AN               | _              | A/D Channel 2 input                                                             |

|                         | TOCKI    | ST               |                | Timer0 clock input                                                              |

|                         | INT      | ST               | _              | External interrupt                                                              |

| GPA3/AN3/TS_OUT2        | GPA3     | TTL              | CMOS           | General-purpose I/O                                                             |

|                         | AN3      | AN               | _              | A/D Channel 3 input                                                             |

|                         | TS_OUT2  |                  |                | Internal digital signals multiplexer output <sup>(1)</sup>                      |

| GPA5/MCLR               | GPA5     | TTL              | _              | General-purpose input only                                                      |

|                         | MCLR     | ST               | _              | Master Clear with internal pull-up                                              |

| GPA6/CCD1               | GPA6     | ST               | CMOS           | General-purpose I/O                                                             |

|                         | CCD1     | ST               | CMOS           | Single Compare output of PWM channel 1.<br>Dual Capture input of PWM channel 1. |

| GPA7/SCL                | GPA7     | ST               | CMOS           | General-purpose open drain I/O                                                  |

|                         | SCL      | l <sup>2</sup> C | OD             | I <sup>2</sup> C clock                                                          |

| GPB0/SDA                | GPB0     | TTL              | CMOS           | General-purpose I/O                                                             |

|                         | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output                                              |

| GPB1/AN4/RX/DT          | GPB1     | TTL              | CMOS           | General-purpose I/O                                                             |

| ( <b>MCP19215</b> Only) | AN4      | AN               | _              | A/D Channel 4 input                                                             |

|                         | RX       | ST               |                | AUSART asynchronous receive input                                               |

|                         | DT       | TTL              | CMOS           | AUSART synchronous data input/output                                            |

| GPB4/AN5/ICSPDAT        | GPB4     | TTL              | CMOS           | General-purpose I/O                                                             |

|                         | AN5      | AN               |                | A/D Channel 5 input                                                             |

|                         | ICSPDAT  | ST               | CMOS           | In-Circuit Debugger and ICSP programming data                                   |

| GPB5/AN6/ICSPCLK        | GPB5     | TTL              | CMOS           | General-purpose I/O                                                             |

|                         | AN6      | AN               | —              | A/D Channel 6 input                                                             |

|                         | ISCPCLK  | ST               |                | In-Circuit Debugger and ICSP programming clock                                  |

TABLE 2-1: MCP19214/5 PINOUT DESCRIPTION

Legend:AN= Analog input or outputCMOS= CMOS compatible input or outputOD= Open-DrainTTL= TTL compatible inputST= Schmitt Trigger input with CMOS levels $l^2C$ = Schmitt Trigger input with  $l^2C$

**Note 1:** The Analog/Digital Debug Output is selected through the control of the ABECON1 register.

| Name                               | Function          | Input<br>Type | Output<br>Type | Description                                                                                                                    |  |  |

|------------------------------------|-------------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| GPB6/AN7/TX/CK                     | GPB6              | TTL           | CMOS           | General-purpose I/O                                                                                                            |  |  |

| (MCP19215 Only)                    | AN7               | AN            | _              | A/D Channel 7 input                                                                                                            |  |  |

|                                    | ТХ                | _             | CMOS           | AUSART asynchronous transmit output                                                                                            |  |  |

|                                    | СК                | TTL           | CMOS           | AUSART synchronous clock input/output                                                                                          |  |  |

| GPB7/CCD2                          | GPB7              | TTL           | CMOS           | General-purpose I/O                                                                                                            |  |  |

| (MCP19215 Only)                    | CCD2              | ST            | CMOS           | Single Compare output of PWM channel 2<br>Dual Capture input of PWM channel 2                                                  |  |  |

| V <sub>IN</sub>                    | V <sub>IN</sub>   | _             | _              | Device input supply voltage                                                                                                    |  |  |

| V <sub>DD</sub>                    | V <sub>DD</sub>   | —             |                | Internal +5V LDO output pin                                                                                                    |  |  |

| V <sub>DR</sub>                    | V <sub>DR</sub>   | —             |                | Gate drivers supply voltage                                                                                                    |  |  |

| A <sub>GND</sub> /D <sub>GND</sub> | A <sub>GND</sub>  | _             |                | Small signal quiet ground                                                                                                      |  |  |

| P <sub>GND</sub>                   | P <sub>GND</sub>  | _             | _              | Large signal power ground                                                                                                      |  |  |

| PDRV1                              | PDRV1             | _             | _              | Primary PWM channel MOSFET gate drive                                                                                          |  |  |

| PDRV2                              | PDRV2             | _             | _              | Secondary PWM channel MOSFET gate drive                                                                                        |  |  |

| IP1                                | IP1               | _             | _              | Primary input current sense for PWM channel 1                                                                                  |  |  |

| IP2                                | IP2               | _             | _              | Primary input current sense for PWM channel 2                                                                                  |  |  |

| I <sub>SN</sub> 1                  | I <sub>SN</sub> 1 | —             | —              | Differential current sense amplifier negative input of PWM channel 1                                                           |  |  |

| I <sub>SN</sub> 2                  | I <sub>SN</sub> 2 | —             | —              | Differential current sense amplifier negative input of PWM channel 2                                                           |  |  |

| I <sub>SP</sub> 1                  | I <sub>SP</sub> 1 | —             | —              | Differential current sense amplifier positive input of PWM channel 1                                                           |  |  |

| I <sub>SP</sub> 2                  | I <sub>SP</sub> 2 | —             | —              | Differential current sense amplifier positive input of PWM channel 2                                                           |  |  |

| CCOMP1                             | CCOMP1            | —             | —              | Output of the current loop error amplifier of PWM channel 1                                                                    |  |  |

| CCOMP2                             | CCOMP2            | —             | —              | Output of the current loop error amplifier of PWM channel 2                                                                    |  |  |

| VCOMP1                             | VCOMP1            | —             | —              | Output of the voltage loop error amplifier of PWM channel 1                                                                    |  |  |

| VCOMP2                             | VCOMP2            | -             | —              | Output of the voltage loop error amplifier of PWM channel 2                                                                    |  |  |

| VFB1                               | VFB1              | -             | —              | Feedback input of the voltage loop of PWM channel 1                                                                            |  |  |

| VFB2                               | VFB2              | -             | —              | Feedback input of the voltage loop of PWM channel 2                                                                            |  |  |

| EP                                 |                   |               |                | Exposed Pad. The $A_{GND}$ and $D_{GND}$ internal nodes close here. Connect this to the PCBs ground plane using multiple vias. |  |  |

Legend:

AN

= Analog input or output

CMOS

= CMOS compatible input or output

OD

= Open-Drain

TTL

= TTL compatible input

ST

= Schmitt Trigger input with CMOS levels

I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

**Note 1:** The Analog/Digital Debug Output is selected through the control of the ABECON1 register.

#### 2.1 Detailed Pin Functional Description

#### 2.1.1 GPA0 PIN

GPA0 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN0 is an input to the A/D. To configure this pin to be read by the A/D on channel 0, bits TRISA0 and ANSA0 must be set.

The ABECON1/2 registers can be configured to set this pin to the TS\_OUT1 function. It is a buffered output of the internal analog signals multiplexer. Analog signals present on this pin are controlled by the ADCON0 register.

#### 2.1.2 GPA1 PIN

GPA1 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN1 is an input to the A/D. To configure this pin to be read by the A/D on channel 1, bits TRISA1 and ANSA1 must be set.

#### 2.1.3 GPA2 PIN

GPA2 is a general-purpose ST input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN2 is an input to the A/D. To configure this pin to be read by the A/D on channel 2, bits TRISA2 and ANSA2 must be set.

When bit TOCS is set in the OPTION\_REG register, the TOCKI function is enabled. Refer to **Section 21.0** "Timer0 Module" for more information.

GPA2 can also be configured as an external interrupt by setting the INTE bit. Refer to **Section 13.2 "GPA2/INT Interrupt**" for more information.

#### 2.1.4 GPA3 PIN

GPA3 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN3 is an input to the A/D. To configure this pin to be read by the A/D on channel 3, bits TRISA3 and ANSA3 must be set.

The ABECON1/2 registers can be configured to set this pin to the TS\_OUT2 function. It is a buffered output of the internal digital signals multiplexer. Digital signals present on this pin are controlled by the ABECON2 register.

#### 2.1.5 GPA5 PIN

GPA5 is a general-purpose TTL input only pin. An internal weak pull-up and interrupt-on-change are also available.

For programming purposes, this pin is to be connected to the MCLR pin of the serial programmer. Refer to Section 32.0 "In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)" for more information.

This pin is  $\overline{\text{MCLR}}$  when the MCLRE bit is set in the CONFIG register. When the  $\overline{\text{MCLR}}$  is active, the interrupt-on-change is disabled and the weak pull-up is always enabled.

#### 2.1.6 GPA6 PIN

GPA6 is a general-purpose CMOS output ST input pin whose data direction is controlled in TRISGPA.

GPA6 is part of the CCD Module. For more information, refer to Section 31.0 "Dual Capture/Compare (CCD) Module".

#### 2.1.7 GPA7 PIN

GPA7 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

When the MCP19214/5 is configured for  $I^2C$  communication, Section 27.2 " $I^2C$  Mode Overview", GPA7 functions as the  $I^2C$  clock (SCL). This pin must be configured as an input to allow proper operation.

#### 2.1.8 GPB0 PIN

GPB0 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

When the MCP19214/5 are configured for  $I^2C$  communication, Section 27.2 " $I^2C$  Mode Overview", GPB0 functions as the  $I^2C$  clock (SDA). This pin must be configured as an input to allow proper operation.

#### 2.1.9 GPB1 PIN (MCP19215 ONLY)

GPB1 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN4 is an input to the A/D. To configure this pin to be read by the A/D on channel 4, bits TRISB1 and ANSB1 must be set.

RX is the receiver's input of the AUSART block for asynchronous operation.

DT is the input/output pin of the AUSART block for synchronous operation

#### 2.1.10 GPB4 PIN

GPB4 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN5 is an input to the A/D. To configure this pin to be read by the A/D on channel 5, bits TRISB4 and ANSB4 must be set.

ICSPDAT is the serial programming data I/O function. This is used in conjunction with ICSPCLK to serial program the device. Refer to **Section 32.0 "In-Circuit Serial Programming™ (ICSP™)**" for more information.

#### 2.1.11 GPB5 PIN

GPB5 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN6 is an input to the A/D. To configure this pin to be read by the A/D on channel 6, bits TRISB5 and ANSB5 must be set.

ICSPCLK is the serial programming/debugging clock function. This is used in conjunction with ICSPDAT to serial program the device. Refer to **Section 32.0** "**In-Circuit Serial Programming™** (**ICSP™**)" for more information.

#### 2.1.12 GPB6 PIN (MCP19215 ONLY)

GPB6 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN7 is an input to the A/D. To configure this pin to be read by the A/D on channel 7, bits TRISB6 and ANSB6 must be set.

TX is the transmitter's output of the AUSART block during asynchronous operation.

CK is the input/output clock of the AUSART block during synchronous operation.

#### 2.1.13 GPB7 PIN (MCP19215 ONLY)

GPB7 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

GPB7 is part of the CCD Module. For more information, refer to Section 31.0 "Dual Capture/Compare (CCD) Module".

#### 2.1.14 V<sub>IN</sub> PIN

$V_{\rm IN}$  is the input voltage pin of the MCP19214/5 controller. This pin is connected to the input of the +5V internal voltage regulator. A bypass capacitor of minimum 100 nF must be connected between this pin and GND. This capacitor should be physically placed close to the device.

#### 2.1.15 V<sub>DD</sub> PIN

The output of the internal +5.0V regulator is connected to this pin. It is recommended that a minimum 4.7  $\mu F$  ceramic bypass capacitor be connected between this pin and the GND pin of the device. The bypass capacitor should be physically placed close to the device.

#### 2.1.16 V<sub>DR</sub> PIN

The supply for the MOSFET drivers is connected to this pin and has an absolute maximum rating of +13.5V. A decoupling capacitor of 1.0  $\mu$ F should be placed between this pin and P<sub>GND</sub> pin. This pin can be connected by an RC filter to the V<sub>DD</sub> pin.

# 2.1.17 A<sub>GND</sub>/D<sub>GND</sub> PIN (MCP19215 ONLY)

$A_{GND}/D_{GND}$  is the small signal ground connection pin. This pin should be connected to a low noise ground.

# 2.1.18 P<sub>GND</sub> PIN

This is the large signal ground pin.  $P_{GND}$  is the return path for the internal MOSFET drivers. This pin should be connected to the power train ground using short, low impedance connection.

#### 2.1.19 PDRV1 PIN

The output of the internal MOSFET driver of PWM channel 1. Connect this pin to the gate of the power MOSFET using short, low-impedance trace.

#### 2.1.20 PDRV2 PIN

The output of the internal MOSFET driver of PWM channel 2. Connect this pin to the gate of the power MOSFET using short, low-impedance trace.

#### 2.1.21 IP1 PIN

This pin is the primary current sense input of the PWM channel 1. IP1 is connected to the main PWM comparator via a blanking circuit. This input is sensitive to high-frequency noise. Keep the associated trace away from noise sources like the main switch node of the converter or the MOSFET's gate drive signals. It is recommended to insert an RC low-pass filter between this input and the shunt resistor used to sense the inductor's current.

#### 2.1.22 IP2 PIN

This pin is the primary current sense input of the PWM channel 2. IP2 is connected to the main PWM comparator via a blanking circuit. This input is sensitive to high-frequency noise. Keep the associated trace away from noise sources like the main switch node of the converter or the MOSFETs gate drive signals. It is recommended to insert an RC low-pass filter between this input and the shunt resistor used to sense the inductor's current.

#### 2.1.23 I<sub>SN</sub>1 PIN

This pin is the inverting input of the internal differential current sense amplifier of PWM channel 1.

#### 2.1.24 I<sub>SN</sub>2 PIN

This pin is the inverting input of the internal differential current sense amplifier of PWM channel 2.

#### 2.1.25 I<sub>SP</sub>1 PIN

This pin is the noninverting input of the internal differential current sense amplifier of PWM channel 1.

#### 2.1.26 I<sub>SP</sub>2 PIN

This pin is the noninverting input of the internal differential current sense amplifier of PWM channel 2.

#### 2.1.27 CCOMP1

The CCOMP1 pin is the output of the current loop error amplifier of PWM channel 1. The loop's compensation network is connected between this pin and GND. This is a high-impedance node, and the traces associated with this pin must be kept far from the noise sources like the main switch node of the converter or the MOSFET's gate drive signals.

#### 2.1.28 CCOMP2

The CCOMP2 pin is the output of the current loop error amplifier of PWM channel 2. The loop's compensation network is connected between this pin and GND. This is a high-impedance node, and the traces associated with this pin must be kept far from the noise sources like the main switch node of the converter or the MOSFETs gate drive signals.

#### 2.1.29 VCOMP1

The VCOMP1 pin is the output of the voltage loop error amplifier of PWM channel 1. The compensation network is connected between this pin and GND. This is a high-impedance node, and the traces associated with this pin must be kept far from the noise sources like the main switch node of the converter or the MOSFET's gate drive signals.

#### 2.1.30 VCOMP2

The VCOMP2 pin is the output of the voltage loop error amplifier of PWM channel 2. The compensation network is connected between this pin and GND. This is a high-impedance node, and the traces associated with this pin must be kept far from the noise sources like the main switch node of the converter or the MOSFET's gate drive signals.

#### 2.1.31 VFB1 PIN

The inverting input of the error amplifier of the voltage loop for PWM channel 1. This is a high-impedance input and is sensitive to noise. Keep the trace associated with this pin far from noise sources like the main switch node of the converter or MOSFETs gate drive signals.

#### 2.1.32 VFB2 PIN

The inverting input of the error amplifier of the voltage loop for PWM channel 2. This is a high-impedance input and is sensitive to noise. Keep the trace associated with this pin far from noise sources like the main switch node of the converter or MOSFET's gate drive signals.

#### 2.1.33 EXPOSED PAD (EP)

This pad should be connected to a solid ground plane using multiple vias. The connection must provide low thermal impedance as well as low electrical noise. In case of MCP19214, this pad is associated with analog and digital internal grounds ( $A_{GND}/D_{GND}$ ).

# 3.0 FUNCTIONAL DESCRIPTION

# 3.1 Linear Regulator

The operating input voltage for the MCP19214/5 devices ranges from 4.5V-42V. The internal 5V LDO provides bias voltage for the microcontroller core and for the analog circuitry. The output of this LDO can be used for bias additional external low-power circuitry, as well as for the integrated MOSFET drivers. Care should be exercised to avoid an overload of the LDO. The output of this LDO is monitored using a comparator and a specific interrupt is generated in case of malfunction. The thresholds of this comparator are adjustable. Bits that control the functionality of the V<sub>DD</sub> UVLO comparator are located in the VDDCON register.

In order to minimize the current consumption during Sleep mode, the output voltage of the LDO can be adjusted in two steps: 3V and 5V (typical). There are also two operating modes during sleep: Normal mode and Low-Power mode. Bits that control the functionality of the LDO during Sleep mode are located in PE1 register.

The MCP19214/5 also incorporate a brown-out protection. Refer to **Section 12.3** "**Brown-out Reset** (**BOR**)" for details. The PIC core will reset at 2.0V V<sub>DD</sub>.

# 3.2 Output Drive Circuitry

The MCP19214/5 integrates two low-side drivers, one per PWM channel used to drive the external low-side N-Channel power MOSFETs. MCP19214/5 directly controls only topologies that involve low-side MOSFET drivers like boost, buck-boost, flyback, SEPIC or Cuk. For topologies that require high-side MOSFET drive (e.g., buck or synchronous buck) an external, specialized MOSFET driver can be used.

The gate drive ( $V_{DR}$ ) can be supplied from 5V-10V. The drive strength is capable of up to 1A sink/source with 10V gate drive and down to 0.5A sink/source with 5V gate drive. The supply voltage of the MOSFET drivers is monitored by a UVLO circuit in order to prevent damage to the external power switches. The MOSFET driver's UVLO circuit has two thresholds: 2.7V and 5.4V (typical).

Each driver has its own enable bit, controlled by the microcontroller core. These bits are located in PE1 register.

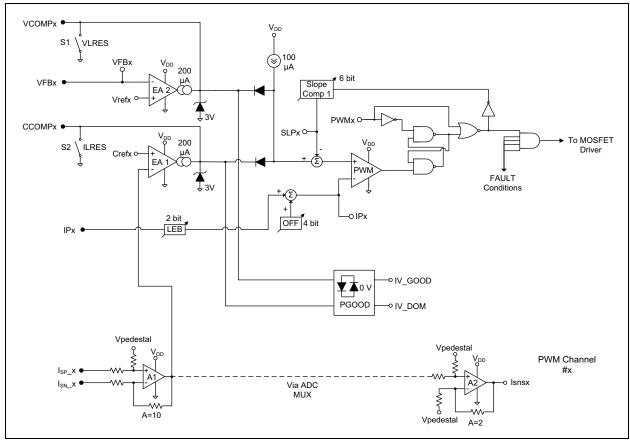

# 3.3 PWM Controller

MCP19214/5 integrates two independent PWM controllers. Each PWM channel comprises a set of two error amplifiers with independent reference voltage generators, a PWM comparator with latched output, a current sense input with adjustable leading-edge blanking time, and a ramp generator for slope compensation. See Figure 3-1 for details. The error amplifiers are of transconductance type (OTA) with separate, external compensation network connected between the output and the ground ( $A_{GND}$ ). The outputs of the OTAs are tied together through diodes in order to allow the simultaneous control of the output voltage and current. The typical sink current is 200 uA. This type of amplifier makes possible the usage of high-valued resistors for the feedback divider without affecting the frequency response of the amplifier, as these resistors are out of the compensation loop. Only one inverting input is accessible outside the chip (VFBx), the other being internally connected to the output of the 10X differential amplifier. The error signal is clamped at a certain level (3V, typical) in order to prevent overcurrent in the main switching MOSFET of the converter.

The output of the error amplifiers (CCOMP and VCOMP) are equipped with switches (S1 and S2 in Figure 3-1) in order to reset the compensation networks before the soft start or before the activation of a certain loop. These switches are under the software control (VLRES and CLRES bits), and it is the responsibility of the user to ensure proper operation.

The internal 10X differential amplifier is used to improve the accuracy of the current regulated loops and reduce the power dissipation in the external current sensing element (shunt).

A second amplifier (common for both PWM channels) with a gain of 2X is connected between the ADC input and the output of the 10X amplifier. This second amplifier increases the dynamic range of the current measurement circuitry.

In order to prevent any inherent errors that may occur when the output of the amplifier goes near ground or input rail, a special circuit centers the common mode voltage at a specified level (pedestal voltage, typical 2.048V). This technique allows the microcontroller core to read the current in both directions (as with the bidirectional converters): the forward direction when the converter charges the battery, and the reverse direction when the converter delivers constant output voltage from the battery. The output of the 10X differential amplifier as well as the output of the second 2X amplifier will be at the pedestal voltage if the sensed current is zero. The same pedestal voltage is added to the value of the reference voltage generator of the current loop in order to compensate the DC offset introduced by the pedestal voltage. The 2X amplifier output can be connected via the analog multiplexer to the ADC input for current monitoring purposes (Isnsx signal). The pedestal voltage is fixed at 2.048V.

The loop implements the Peak Current mode control. The IPx input is used to sense the inductor's current. A leading-edge blanking circuit (LEB) is used to prevent false reset of the PWM circuitry. The LEB can be set to four steps (0 ns, 50 ns, 100 ns and 200 ns). The blank time is controlled from the ICLEBCON register. External resistor capacitor filtering techniques can still be used to filter the leading edge if desired. An adjustable offset voltage generator is used to add a certain amount of DC offset (programmable) on top of the IPx signal. This offset prevents the effects of the nonlinearities associated with the error amplifiers outputs at very low-voltage levels, and can also be protection used for overcurrent purposes (cycle-by-cycle current limit). This offset adjustment is controlled by the ICOACON register.

The Peak Current mode control requires slope compensation in order to avoid subharmonic oscillations. A programmable (6-bit) ramp generator is provided and its output is subtracted from the error signal. When the current sense signal reaches the level of the control voltage minus slope compensation, the on cycle is terminated and the external switch is latched off until the beginning of the next cycle, which begins at the next clock cycle.

A S-R Latch (Set-Reset Latch) is used to prevent the PWM circuitry from turning the external switch on until the beginning of the next clock cycle.

In order to avoid severe overshoots of the controlled parameter (current or voltage) when the loop switches between operating modes (constant current or constant voltage), the outputs of the error amplifiers are clamped together.

#### FIGURE 3-1: THE PWM CONTROLLER BLOCK DIAGRAM

# 3.4 Current Sense

The output current is differentially sensed by the MCP19214/5. In high-current applications, this helps to maintain high-system efficiency by minimizing power dissipation in current sense resistors. Differential current sensing also minimizes external ground shift errors. The internal differential amplifier has a typical gain of 10 V/V (typical).

# 3.5 Power Good Circuitry

The Power Good circuitry monitors the outputs of the error amplifiers to detect an open-loop condition. The IV\_GOOD signal will generate an interrupt and the PIC core will read the status of the IV\_GOOD and IV\_DOM bits. The IV\_GOOD signal indicates if one of the loops is active, and IV\_DOM indicates which loop is dominant. The associated bits are located in LOOPCON1 and LOOPCON2.

# 3.6 **PWM Frequency**

The MCP19214/5 device uses a fixed frequency PWM control strategy. Both PWM channels will have the same switching frequency, but the phase difference between them is adjustable. The first PWM channel is considered the master channel, while the second is the slave channel. The user sets the MCP19214/5 switching frequency by configuring the PR2 register. The maximum allowable PDRVx duty cycle is adjustable and is controlled by the PWMRL register. The programmable range of the switching frequency will be 31.25 kHz to 2 MHz. The available switching frequency below 2 MHz is defined as  $F_{SW}$  = 8 MHz/N, where N is a whole number between  $4 \le N \le 256$ . Refer to Section 24.0 "Enhanced PWM Module" for details.

# 3.7 Reference Voltage Generators

There are four internal reference generators, two for each PWM channel. The digital-to-analog converters that control these reference have 8-bit resolution and are controlled by firmware.

The output voltage range of the DACs that set the reference voltage for the voltage loops is 0 mV to 2.048 mV (typical). Thus, the reference voltage of the voltage loops can be adjusted with a step of 8 mV. The associated registers that hold the DAC value are VREFCON1 and VREFCON2.

The output voltage range of the DACs that set the reference voltage for the current loops is 0 mV to 1.024 mV (typical). Thus, the reference voltage of the current loops can be adjusted with a step of 4 mV. The associated registers that hold the DAC value are CREFCON1 and CREFCON2.

# 3.8 Start-Up

To control the output current during start-up, the MCP19214/5 has the capability to monotonically increase system voltage or current at the user's discretion. This is accomplished through the control of the reference voltage DACs for each control loop. The entire start-up profile is under user control via software.

### 3.9 Temperature Management

#### 3.9.1 THERMAL SHUTDOWN

To protect the MCP19214/5 from overtemperature conditions, a 150°C (typical) junction temperature thermal shutdown has been implemented. When the junction temperature reaches this limit, the device disables the output drivers. In Shutdown mode, both PDRV1 and PDRV1 outputs are disabled and the overtemperature flag (OTIF) is set in the PIR2 register. The internal LDO is also disabled during thermal shutdown phase. When the junction temperature is reduced by 20°C to 130°C (typical), the MCP19214/5 can resume normal output drive switching.

#### 3.9.2 TEMPERATURE REPORTING

The MCP19214/5 has a second on-chip temperature monitoring circuit that can be read by the ADC through the analog test MUX. Refer to Section 25.0 "Internal Temperature Indicator Module" for details on this internal temperature monitoring circuit.

# 4.0 ELECTRICAL CHARACTERISTICS

# 4.1 ABSOLUTE MAXIMUM RATINGS †

| V <sub>IN</sub> - V <sub>GND</sub> (operating)<br>V <sub>IN</sub> (transient < 500 ms) | –0.3V to +44V<br>+48V |

|----------------------------------------------------------------------------------------|-----------------------|

| PDRVx                                                                                  |                       |

| V <sub>DD</sub> Internally Generated                                                   | +6.5V                 |

| V <sub>DR</sub> Externally Generated                                                   | +13.5V                |

| Voltage on MCLR with respect to GND                                                    |                       |

| Maximum voltage: any other pin                                                         |                       |

| Maximum output current sunk by any single I/O pin                                      |                       |

| Maximum output current sourced by any single I/O pin                                   |                       |

| Maximum current sunk by all GPIO                                                       |                       |

| Maximum current sourced by all GPIO                                                    | 35 mA                 |

| Storage Temperature                                                                    | –65°C to +150°C       |

| Maximum Junction Temperature                                                           | +150°C                |

| Operating Junction Temperature                                                         | –40°C to +125°C       |

| ESD protection on all pins (CDM)                                                       |                       |

| ESD protection on all pins (HBM)                                                       |                       |

| ESD protection on all pins (MM)                                                        |                       |

**† Notice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 4.2 Electrical Characteristics

| Electrical Specifications: Unless  | otherwise noted, V | V <sub>IN</sub> = 12V, I | = <sub>SW</sub> = 300 | kHz, $T_A = +$ | -25°C, <b>E</b> | Boldface specifications apply |

|------------------------------------|--------------------|--------------------------|-----------------------|----------------|-----------------|-------------------------------|

| over the $T_A$ range of –40°C to + | 125°C              |                          | -                     |                |                 |                               |

|                                    |                    |                          |                       |                |                 |                               |

| Parameters                                         | Sym.                                                               | Min. | Тур. | Max. | Units | Conditions                                                                        |

|----------------------------------------------------|--------------------------------------------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------|

| Input                                              | · · · · · · · · · · · · · · · · · · ·                              |      |      |      |       | ·                                                                                 |

| Input Voltage                                      | V <sub>IN</sub>                                                    | 4.5  |      | 42   | V     | Steady State                                                                      |

| Input Quiescent Current                            | ۱ <sub>Q</sub>                                                     | _    | 6    | 10   | mA    | Not Switching,<br>Analog circuitry disabled                                       |

| Shutdown Current                                   | I <sub>SHDN</sub>                                                  |      | 110  | 400  | μA    | Depends on the selected<br>mode; see Section 19.0<br>"Power-Down Mode<br>(Sleep)" |

| Linear Regulator V <sub>DD</sub>                   |                                                                    |      |      |      |       |                                                                                   |

| Internal Circuitry Bias Voltage                    | V <sub>DD</sub>                                                    | 4.75 | 5.0  | 5.25 | V     | V <sub>IN</sub> = 6.0V to 42V                                                     |

| Maximum External V <sub>DD</sub><br>Output Current | I <sub>DD_OUT</sub>                                                | 35   | _    |      | mA    | V <sub>IN</sub> = 6.0V to 42V,<br>V <sub>DD</sub> = 5.0V,<br>(Note 1)             |

| Line Regulation                                    | ΔV <sub>DD-OUT</sub> /<br>(V <sub>DD-OUT</sub> *ΔV <sub>IN</sub> ) | _    | 0.02 | 0.1  | %/V   | $(V_{DD} + 1.0V) \le V_{IN} \le 20V$ (Note 1)                                     |

| Load Regulation                                    | ΔV <sub>DD-OUT</sub> /<br>V <sub>DD-OUT</sub>                      | -1   | ±0.1 | +1   | %     | I <sub>DD_OUT</sub> = 1 mA to 35 mA<br>( <b>Note 1</b> )                          |

| Output Short Circuit Current                       | I <sub>DD_SC</sub>                                                 | —    | 60   | 90   | mA    | V <sub>IN</sub> = (V <sub>DD</sub> + 1.0V)<br>(Note 1)                            |

Note 1:  $V_{DD}$  is the voltage present at the  $V_{DD}$  pin.

2: Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value measured at a 1V differential between V<sub>IN</sub> and V<sub>DD</sub>.

- 3: Characterized during validation phase, not production tested.

- 4: The V<sub>DD</sub> LDO will limit the total source current to less than 90 mA. Each pin individually can source a maximum of 15 mA.

# 4.2 Electrical Characteristics (Continued)

Electrical Specifications: Unless otherwise noted,  $V_{IN}$  = 12V,  $F_{SW}$  = 300 kHz,  $T_A$  = +25°C, **Boldface** specifications apply over the  $T_A$  range of -40°C to +125°C

| over the T <sub>A</sub> range of –40°C to +              |                                   |       |       |       |       | -                                                                                                                                                                        |

|----------------------------------------------------------|-----------------------------------|-------|-------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters                                               | Sym.                              | Min.  | Тур.  | Max.  | Units | Conditions                                                                                                                                                               |

| Dropout Voltage                                          | V <sub>IN</sub> - V <sub>DD</sub> | —     | 0.3   | 0.6   | V     | I <sub>DD_OUT</sub> = 35 mA,<br>(Notes 1 and 2)                                                                                                                          |

| Power Supply Rejection Ratio                             | PSRR <sub>LDO</sub>               | 40    | 60    |       | dB    | $\label{eq:states} \begin{array}{l} f \leq 1000 \text{ Hz}, \\ I_{DD\_OUT} = 25 \text{ mA} \\ C_{\text{IN}} = 0 \ \mu\text{F}, \ C_{DD} = 4.7 \ \mu\text{F} \end{array}$ |

| Band Gap Voltage                                         | BG                                | 1.215 | 1.23  | 1.245 | V     | Trimmed at 1.0% tolerance                                                                                                                                                |

| Input UVLO Voltage DAC                                   |                                   |       |       |       |       |                                                                                                                                                                          |

| UVLO Range (VIN_ON)                                      | UVLO <sub>ON</sub>                | 4.0   | —     | 20    | V     | V <sub>IN</sub> Falling                                                                                                                                                  |

| UVLO Hysteresis ( <i>VIN_OFF</i> )                       | UVLO <sub>HYS</sub>               | _     | 5     | —     | %     | Hysteresis is based upon<br>UVLO <sub>ON</sub> setting                                                                                                                   |

| Resolution                                               | nbits                             | _     | 6     | _     | Bits  | Logarithmic DAC                                                                                                                                                          |

| Input UVLO Comparator                                    |                                   |       |       |       |       |                                                                                                                                                                          |

| Input Offset Voltage                                     | V <sub>OS</sub>                   | —     | +/-10 | 20    | mV    | Ensure by design                                                                                                                                                         |

| Input-to-Output Delay                                    | TD                                | _     | 5     |       | μs    | 100 ns rise time to<br>1V overdrive on V <sub>IN</sub> .<br>V <sub>IN</sub> > UVLO to flag set.                                                                          |

| Input OVLO Voltage DAC                                   | 1                                 | 1     |       |       |       | 1                                                                                                                                                                        |

| OVLO (V <sub>IN</sub> Rising) Range<br>( <i>VIN_ON</i> ) | OVLO <sub>ON</sub>                | 8.8   | —     | 44    | V     | V <sub>IN</sub> Rising                                                                                                                                                   |

| OVLO Hysteresis ( <i>VIN_OFF</i> )                       | OVLO <sub>HYS</sub>               | _     | 5     |       | %     | Hysteresis is based upon<br>OVLO <sub>ON</sub> setting                                                                                                                   |

| Resolution                                               | nbits                             | _     | 6     |       | Bits  | Logarithmic DAC                                                                                                                                                          |

| Input OVLO Comparator                                    |                                   |       |       |       |       |                                                                                                                                                                          |

| Input Offset Voltage                                     | V <sub>OS</sub>                   | —     | +/-10 | 20    | mV    |                                                                                                                                                                          |

| Input-to-Output Delay                                    | TD                                | _     | 5     | _     | μs    | 100 nS rise time to<br>1V overdrive on V <sub>IN</sub><br>V <sub>IN</sub> > OVLO to flag set                                                                             |

| V <sub>DD</sub> UVLO Comparator                          |                                   |       |       |       | -     |                                                                                                                                                                          |