# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **Three-Channel Analog Front-End Device**

#### **Device Features:**

- Three input pins for analog input signals

- High input detection sensitivity (3 mV<sub>PP</sub>, typical)

- High modulation depth sensitivity (as low as 8%)

- Three output selections:

- Demodulated data

- Carrier clock

- RSSI

- Input carrier frequency: 125 kHz, typical

- Input data rate: 10 Kbps, maximum

- 8 internal Configuration registers

- Bidirectional transponder communication (LF talk back)

- Programmable antenna tuning capacitance (up to 63 pF, 1 pF/step)

- · Programmable output enable filter

- Low standby current: 4 µA (with 3 channels enabled), typical

- Low operating current: 13 µA (with 3 channels enabled), typical

- Serial Peripheral Interface (SPI™) with external devices

- Supports Battery Back-Up mode and batteryless

operation with external circuits

- Industrial and Extended Temperature Range: -40°C to +85°C (industrial)

#### **Typical Applications:**

- Automotive industry applications:

- Passive Keyless Entry (PKE) transponder

- Remote door locks and gate openers

- Engine immobilizer

- LF initiator sensor for tire pressure monitoring systems

- Security Industry applications:

- Long range access control transponder

- Parking lot entry transponder

- Hands-free apartment door access

- Asset control and management

#### **Description:**

The MCP2030 is a stand-alone Analog Front-End (AFE) device for Low-Frequency (LF) sensing and bidirectional communication applications. The device has eight internal Configuration registers which are readable and programmable, except the read-only STATUS register, by an external device.

The device has three low-frequency input channels. Each input channel can be individually enabled or disabled. The device can detect an input signal with amplitude as low as ~1 mV\_{PP} and can demodulate an amplitude-modulated input signal with as low as 8% modulation depth. The device can also transmit data by clamping and unclamping the input LC antenna voltage.

The device can output demodulated data, carrier clock or RSSI current depending on the register setting. The demodulated data and carrier clock outputs are available on the LFDATA pin, while the RSSI output is available on the RSSI pin. The RSSI current output is linearly proportional to the input signal strength.

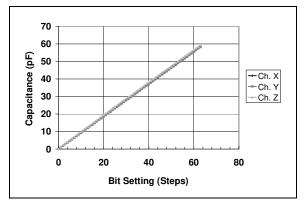

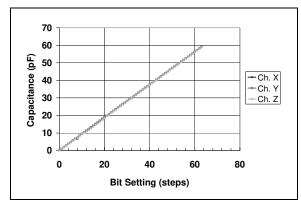

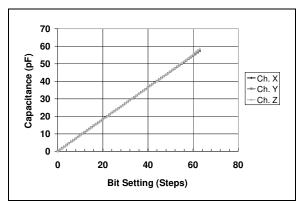

The device has programmable internal tuning capacitors for each input channel. The user can program these capacitors up to 63 pF, 1 pF per step. These internal tuning capacitors can be used effectively for fine-tuning of the external LC resonant circuit.

The device is optimized for very low current consumption and has various battery-saving low-power modes (Sleep, Standby, Active). The device can also be operated in Battery Back-up and Batteryless modes using a few external components.

This device is available in 14-pin PDIP, SOIC, and TSSOP packages. This device is also used as the AFE in the PIC16F639.

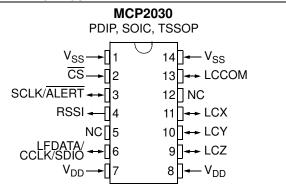

#### Package Types:

NOTES:

### 1.0 ELECTRICAL SPECIFICATIONS

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias40°C to +125°C                                 |

|------------------------------------------------------------------------------|

| Storage temperature65°C to +150°C                                            |

| Voltage on $V_{DD}$ with respect to $V_{SS}$ 0.3V to +6.5V                   |

| Voltage on all other pins with respect to $V_{SS}$ 0.3V to $(V_{DD} + 0.3V)$ |

|                                                                              |

| Maximum current out of V <sub>SS</sub> pin                                   |

| Maximum current into V <sub>DD</sub> pin250 mA                               |

| Maximum LC Input Voltage<br>(LCX, LCY, LCZ) loaded, with device              |

| Maximum LC Input Voltage<br>(LCX, LCY, LCZ) unloaded, without device         |

| Maximum Input Current (rms) into device<br>per LC Channel10 mA               |

| Human Body ESD rating2000 (min.) V                                           |

| Machine Model ESD rating200 (min.) V                                         |

**†** Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **DC Characteristics**

| Electrical Specifications: Standard Operating Conditions (unless otherwise stated)         Operating temperature $-40^{\circ}C \le T_A \le +85^{\circ}C$ LC Signal Input       Sinusoidal 300 mV_{PP}         Carrier Frequency       125 kHz         LCCOM connected to V <sub>SS</sub> |                    |                       |             |                       |                |                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|-------------|-----------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters                                                                                                                                                                                                                                                                               | Sym.               | Min.                  | Тур†        | Max.                  | Units          | Conditions                                                                                                                                                         |

| Supply Voltage                                                                                                                                                                                                                                                                           | $V_{DD}$           | 2.0                   | 3.0         | 3.6                   | ٧              |                                                                                                                                                                    |

| V <sub>DD</sub> Start Voltage to ensure internal<br>Power-on Reset signal                                                                                                                                                                                                                | V <sub>POR</sub>   | _                     |             | 1.8                   | V              |                                                                                                                                                                    |

| Modulation Transistor-on Resistance                                                                                                                                                                                                                                                      | R <sub>M</sub>     | _                     | 50          | 100                   | Ω              | $V_{DD} = 3.0V$                                                                                                                                                    |

| Active Current (detecting signal)<br>1 LC Input Channel Receiving Signal<br>3 LC Input Channel Receiving Signals                                                                                                                                                                         | I <sub>ACT</sub>   |                       | 10<br>13    | —<br>18               | μΑ<br>μΑ       | $\label{eq:constraint} \begin{split} \overline{CS} &= V_{DD} \\ Input &= Continuous Wave (CW); \\ Amplitude &= 300 \ mV_{PP} \\ All channels enabled. \end{split}$ |

| Standby Current (wait to detect signal)<br>1 LC Input Channel Enabled<br>2 LC Input Channels Enabled<br>3 LC Input Channels Enabled                                                                                                                                                      | I <sub>STDBY</sub> |                       | 2<br>3<br>4 | 5<br>6<br>7           | μΑ<br>μΑ<br>μΑ | $\overline{\text{CS}} = \text{V}_{\text{DD}}; \overline{\text{ALERT}} = \text{V}_{\text{DD}}$                                                                      |

| Sleep Current                                                                                                                                                                                                                                                                            | I <sub>SLEEP</sub> | _                     | 0.2         | 1                     | μΑ             | $\overline{\text{CS}} = \text{V}_{\text{DD}}; \overline{\text{ALERT}} = \text{V}_{\text{DD}}$                                                                      |

| Analog Input Leakage Current<br>LCX, LCY, LCZ<br>LCCOM                                                                                                                                                                                                                                   | I <sub>AIL</sub>   |                       |             | ± 1<br>± 1            | μΑ<br>μΑ       | $V_{DD}$ = 3.6V, $V_{SS} \leq V_{IN} \leq 1V$ with respect to ground. Internal tuning capacitors are switched off, tested in Sleep mode.                           |

| Digital Input Low Voltage                                                                                                                                                                                                                                                                | V <sub>IL</sub>    | V <sub>SS</sub>       | -           | 0.3 V <sub>DD</sub>   | V              | SCLK, SDI, CS                                                                                                                                                      |

| Digital Input High Voltage                                                                                                                                                                                                                                                               | V <sub>IH</sub>    | 0.8 V <sub>DD</sub>   | _           | V <sub>DD</sub>       | V              | SCLK, SDI, CS                                                                                                                                                      |

| Digital Input Leakage Current <b>(Note 1)</b><br>SDI<br>SCLK, CS                                                                                                                                                                                                                         | ١                  |                       |             | ± 1<br>± 1            | μΑ<br>μΑ       | $\begin{array}{l} V_{DD} = 3.6V \\ V_{SS} \leq V_{PIN} \leq V_{DD} \\ V_{PIN} \leq V_{DD} \end{array}$                                                             |

| Digital Output Low Voltage<br>ALERT, LFDATA/SDIO                                                                                                                                                                                                                                         | V <sub>OL</sub>    | _                     | _           | V <sub>SS</sub> + 0.4 | V              | Analog Front-End section<br>$I_{OL} = 1.0$ mA, $V_{DD} = 2.0V$                                                                                                     |

| Digital Output High Voltage<br>ALERT, LFDATA/SDIO                                                                                                                                                                                                                                        | V <sub>OH</sub>    | V <sub>DD</sub> - 0.5 | _           | _                     | V              | I <sub>OH</sub> = -400 μA, V <sub>DD</sub> = 2.0V                                                                                                                  |

| Digital Input Pull-Up Resistor<br>CS, SCLK                                                                                                                                                                                                                                               | R <sub>PU</sub>    | 50                    | 200         | 350                   | kΩ             | V <sub>DD</sub> = 3.6V                                                                                                                                             |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Negative current is defined as current sourced by the pin.

#### **AC Characteristics**

$\label{eq:constraint} \begin{array}{|c|c|c|} \hline \textbf{Electrical Specifications:} Standard Operating Conditions (unless otherwise stated) \\ Supply Voltage & 2.0V \leq V_{DD} \leq 3.6V \\ Operating temperature & -40^\circ\text{C} \leq T_A \leq +85^\circ\text{C} \\ LCCOM connected to V_{SS} \\ LC Signal Input & Sinusoidal 300 \ mV_{PP} \\ Carrier Frequency & 125 \ \text{kHz} \\ LCCOM connected to V_{SS} \\ \hline \end{array}$

| Parameters                                                                  | Sym.                 | Min. | Typ†                | Max.           | Units            | Conditions                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------|----------------------|------|---------------------|----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Sensitivity                                                           | V <sub>SENSE</sub>   | 1    | 3.0                 | 6              | mV <sub>PP</sub> | $\label{eq:VDD} \begin{array}{l} V_{DD} = 3.0V \\ Output enable filter disabled \\ AGCSIG = 0; MODMIN = 00 \\ (33\% modulation depth setting) \\ Input = Continuous Wave (CW) \\ Output = Logic level transition from \\ Iow-to-high at sensitivity level for CW input. \end{array}$ |

| Coil de-Q'ing Voltage -<br>RF Limiter (R <sub>FLM</sub> ) must be active    | V <sub>DE_Q</sub>    | 3    | -                   | 5              | V                | $V_{DD}$ = 3.0V, Force I <sub>IN</sub> = 5 $\mu\text{A}$ (worst case)                                                                                                                                                                                                                |

| RF Limiter Turn-on Resistance<br>(LCX, LCY, LCZ)                            | R <sub>FLM</sub>     | —    | 300                 | 700            | Ω                | $V_{DD}$ = 2.0V, $V_{IN}$ = 8 $V_{DC}$                                                                                                                                                                                                                                               |

| Sensitivity Reduction                                                       | S <sub>ADJ</sub>     | _    | 0<br>-30            |                | dB<br>dB         | V <sub>DD</sub> = 3.0V<br>No sensitivity reduction selected<br>Max. reduction selected<br>Monotonic increment in attenuation value<br>from setting = 0000 to 1111 by design                                                                                                          |

| Minimum Modulation Depth<br>60% setting<br>33% setting<br>14% setting<br>8% | V <sub>IN_MOD</sub>  |      | 60<br>33<br>14<br>8 | 84<br>49<br>26 | %<br>%<br>%      | V <sub>DD</sub> = 3.0V<br>See <b>Section 5.21 "Minimum Modulation</b><br><b>Depth Requirement for Input Signal</b> ".<br>See Modulation Depth Definition in<br>Figure 5-5.                                                                                                           |

| Carrier frequency                                                           | F <sub>CARRIER</sub> | _    | 125                 | _              | kHz              |                                                                                                                                                                                                                                                                                      |

| Input modulation frequency                                                  | F <sub>MOD</sub>     | _    | _                   | 10             | kHz              | Input data rate with NRZ data format.<br>$V_{DD} = 3.0V$<br>Minimum modulation depth setting = 33%<br>Input conditions:<br>Amplitude = 300 mV_{PP}<br>Modulation depth = 100%                                                                                                        |

| LCX Tuning Capacitor                                                        | C <sub>TUNX</sub>    | _    | 0                   | _              | pF               | V <sub>DD</sub> = 3.0V,<br>Config. Reg. 1, bits <6:1> Setting = 000000                                                                                                                                                                                                               |

|                                                                             |                      | 44   | 59                  | 82             | pF               | 63 pF ±30%<br>Config. Reg. 1, bits <6:1> Setting = 111111<br>63 steps, approx. 1 pF/step<br>Monotonic increment in capacitor value from<br>setting = 000000 to 111111 by design                                                                                                      |

| LCY Tuning Capacitor                                                        | C <sub>TUNY</sub>    | _    | 0                   | _              | pF               | V <sub>DD</sub> = 3.0V,<br>Config. Reg. 2, bits <6:1> Setting = 000000                                                                                                                                                                                                               |

|                                                                             |                      | 44   | 59                  | 82             | pF               | 63 pF ±30%<br>Config. Reg. 2, bits <6:1> Setting = 111111<br>63 steps, approx. 1 pF/step<br>Monotonic increment in capacitor value from<br>setting = 000000 to 111111 by design                                                                                                      |

| LCZ Tuning Capacitor                                                        | C <sub>TUNZ</sub>    | _    | 0                   | _              | pF               | V <sub>DD</sub> = 3.0V,<br>Config. Reg. 3, bits<6:1> Setting = 000000                                                                                                                                                                                                                |

|                                                                             |                      | 44   | 59                  | 82             | pF               | 63 pF ±30%<br>Config. Reg. 3, bits<6:1> Setting = 111111<br>63 steps, approx. 1 pF/step<br>Monotonic increment in capacitor value from<br>setting = 000000 to 111111 by design                                                                                                       |

| Q of Internal Tuning Capacitors                                             | Q_C                  | 50 * | —                   | _              |                  |                                                                                                                                                                                                                                                                                      |

| Demodulator Charge Time<br>(delay time of demodulated output to rise)       | T <sub>DR</sub>      |      | 50                  | _              | μs               | $V_{DD}$ = 3.0V<br>Minimum modulation depth setting = 33%<br>Input conditions:<br>Amplitude = 300 mV <sub>PP</sub><br>Modulation depth = 100%                                                                                                                                        |

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. †

Required output enable filter high time must account for input path analog delays (=  $T_{OEH} - T_{DR} + T_{DF}$ ). Required output enable filter low time must account for input path analog delays (=  $T_{OEL} + T_{DR} - T_{DF}$ ). Note 1:

2:

#### AC Characteristics (Continued)

Electrical Specifications:Standard Operating Conditions (unless otherwise stated)Supply Voltage $2.0V \le V_{DD} \le 3.6V$ Operating temperature $-40^\circ C \le T_A \le +85^\circ C$ LCCOM connected to V<sub>SS</sub> LC Signal Input Sinusoidal 300 mV\_{PP} Carrier Frequency 125 kHz

| Parameters                                                                                                                                    | Sym.                 | Min.                                                  | Typ† | Max.                                                                                                                                                                            | Units          | Conditions                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------|

| Demodulator Discharge Time (delay time<br>of demodulated output to fall)                                                                      | T <sub>DF</sub>      | _                                                     | 50   | _                                                                                                                                                                               | μs             | $V_{DD}$ = 3.0V<br>MOD depth setting = 33%<br>Input conditions:<br>Amplitude = 300 mV <sub>PP</sub><br>Modulation depth = 100% |

| Rise time of LFDATA                                                                                                                           | TR <sub>LFDATA</sub> | _                                                     | 0.5  | _                                                                                                                                                                               | μs             | $V_{DD}{=}3.0V.$ Time is measured from 10% to 90% of amplitude                                                                 |

| Fall time of LFDATA                                                                                                                           | TF <sub>LFDATA</sub> | _                                                     | 0.5  |                                                                                                                                                                                 | μs             | $V_{DD} = 3.0V$<br>Time is measured from 10% to 90% of amplitude                                                               |

| AGC stabilization time<br>(T <sub>AGC +</sub> T <sub>PAGC</sub> )                                                                             | T <sub>STAB</sub>    | 4                                                     |      | _                                                                                                                                                                               | ms             |                                                                                                                                |

| AGC initialization time                                                                                                                       | T <sub>AGC</sub>     |                                                       | 3.5  | _                                                                                                                                                                               | ms             |                                                                                                                                |

| High time after AGC initialization time                                                                                                       | T <sub>PAGC</sub>    |                                                       | 62.5 | _                                                                                                                                                                               | μs             |                                                                                                                                |

| Gap time after AGC stabilization time                                                                                                         | T <sub>GAP</sub>     | 200                                                   | _    | _                                                                                                                                                                               | μs             |                                                                                                                                |

| Time element of pulse                                                                                                                         | T <sub>E</sub>       | 100                                                   | _    | _                                                                                                                                                                               | μs             | Minimum pulse width                                                                                                            |

| Time from exiting Sleep or POR to being ready to receive signal                                                                               | T <sub>RDY</sub>     | _                                                     |      | 50*                                                                                                                                                                             | ms             |                                                                                                                                |

| Minimum time AGC level must be held after receiving AGC Preserve command                                                                      | T <sub>PRES</sub>    | 5*                                                    |      | -                                                                                                                                                                               | ms             | AGC level must not change more than 10% during $T_{\mbox{\scriptsize PRES}}.$                                                  |

| Internal RC oscillator frequency                                                                                                              | F <sub>OSC</sub>     | 27                                                    | 32   | 35.5                                                                                                                                                                            | kHz            | Internal clock trimmed at 32 kHz during test                                                                                   |

| Inactivity timer time-out                                                                                                                     | TINACT               | 13.5                                                  | 16   | 17.75                                                                                                                                                                           | ms             | 512 cycles of RC oscillator @ F <sub>OSC</sub>                                                                                 |

| Alarm timer time-out                                                                                                                          | T <sub>ALARM</sub>   | 27                                                    | 32   | 35.5                                                                                                                                                                            | ms             | 1024 cycles of RC oscillator @ F <sub>OSC</sub>                                                                                |

| LC Pin Input Resistance for<br>LCX, LCY, LCZ pins                                                                                             | R <sub>IN</sub>      | _                                                     | 800* | _                                                                                                                                                                               | kΩ             | LCCOM grounded, V <sub>DD</sub> = 3V,<br>F <sub>CARRIER</sub> = 125 kHz.                                                       |

| LC Pin Input Parasitic Capacitance for LCX, LCY, LCZ pins                                                                                     | C <sub>IN</sub>      | I                                                     | 24*  |                                                                                                                                                                                 | pF             | LCCOM grounded, $V_{DD} = 3V$ ,<br>F <sub>CARRIER</sub> = 125 kHz.                                                             |

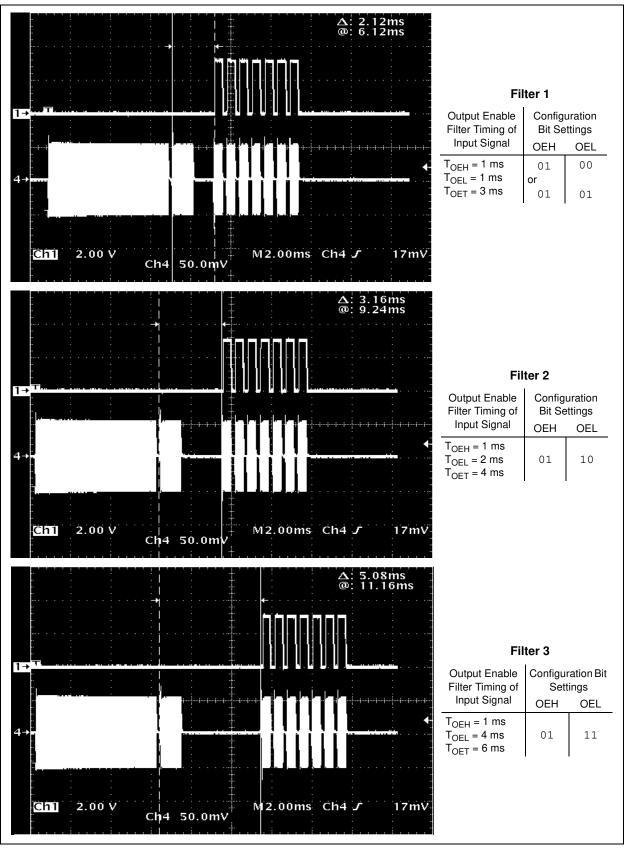

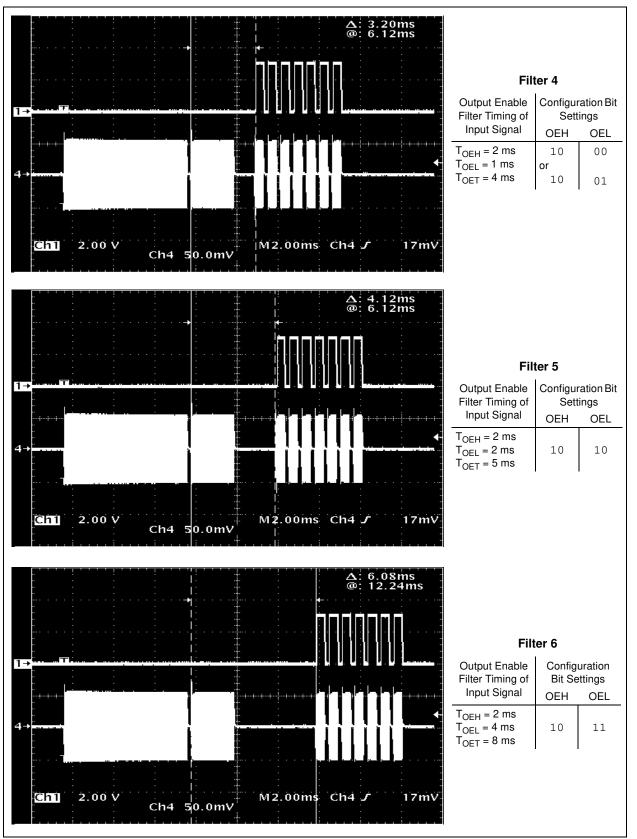

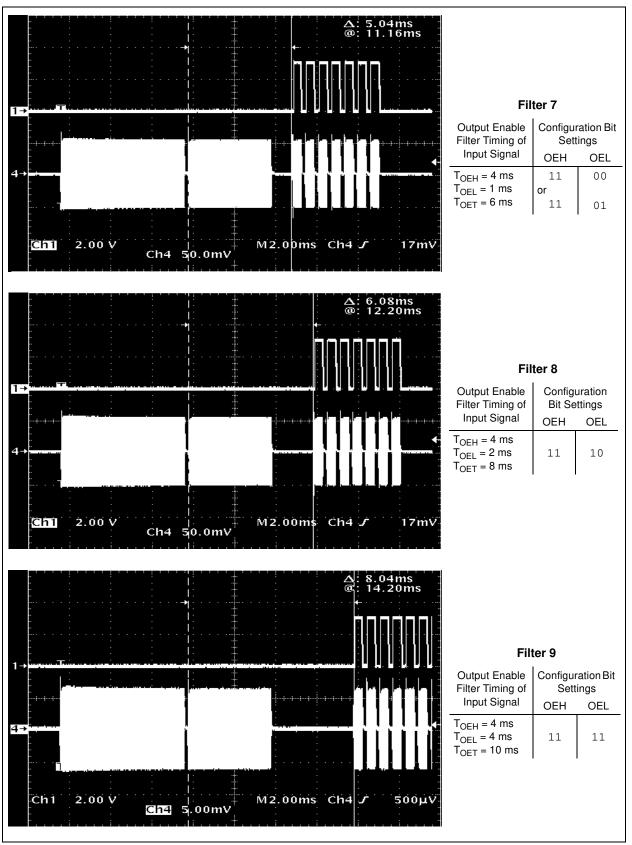

| Minimum output enable filter high time<br><b>OEH (Bits Config0&lt;8:7&gt;)</b><br>01 = 1 ms<br>10 = 2 ms<br>11 = 4 ms<br>00 = Filter Disabled | Т <sub>ОЕН</sub>     | 32 (~1 ms)<br>64 (~2 ms)<br>128 (~4 ms)<br>—          |      |                                                                                                                                                                                 | clock<br>count | RC oscillator = $F_{OSC}$ (see $F_{OSC}$ specification<br>for variations).<br>Viewed from the pin input:<br>(Note 1)           |

| Minimum output enable filter low time<br><b>OEL (Bits Config0&lt;6:5&gt;)</b><br>00 = 1 ms<br>01 = 1 ms<br>10 = 2 ms<br>11 = 4 ms             | T <sub>OEL</sub>     | 32 (~1 ms)<br>32 (~1 ms)<br>64 (~2 ms)<br>128 (~4 ms) |      |                                                                                                                                                                                 | clock<br>count | RC oscillator = F <sub>OSC</sub><br>Viewed from the pin input:<br>(Note 2)                                                     |

| Maximum output enable filter period                                                                                                           | T <sub>OET</sub>     |                                                       |      |                                                                                                                                                                                 |                | RC oscillator = F <sub>OSC</sub>                                                                                               |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                        |                      |                                                       |      | 96 (~3 ms)<br>96 (~3 ms)<br>128 (~4 ms)<br>192 (~6 ms)<br>128 (~4 ms)<br>128 (~4 ms)<br>128 (~4 ms)<br>160 (~5 ms)<br>250 (~8 ms)<br>192 (~6 ms)<br>192 (~6 ms)<br>320 (~10 ms) | clock<br>count |                                                                                                                                |

| 00 XX = Filter Disabled                                                                                                                       |                      | —                                                     | _    | —                                                                                                                                                                               |                | LFDATA output appears as long as input signal level is greater than V <sub>SENSE</sub> .                                       |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Required output enable filter high time must account for input path analog delays (=  $T_{OEH} - T_{DR} + T_{DF}$ ). Required output enable filter low time must account for input path analog delays (=  $T_{OEL} + T_{DR} - T_{DF}$ ). Note 1:

2:

#### **AC Characteristics (Continued)**

| Parameters             | Sym.                | Min. | Тур†              | Max.           | Units          | Conditions                                                                                                                                                                                                                                                           |

|------------------------|---------------------|------|-------------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

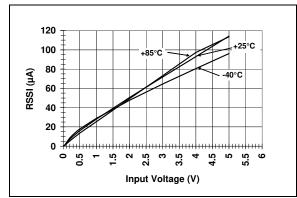

| RSSI current output    | I <sub>RSSI</sub>   | 6    | 0.65<br>12<br>100 | 2<br>20.3<br>— | μΑ<br>μΑ<br>μΑ | $ \begin{array}{l} V_{IN}=37\ mV_{PP} \\ V_{IN}=370\ mV_{PP} \\ V_{DD}=3.0V,\ V_{IN}=0\ to\ 4\ V_{PP} \\ Linearly\ increases\ with\ input\ signal\ amplitude. \\ Tested\ at\ V_{IN}=37\ mV_{PP},\ 100\ mV_{PP},\ and \ 370\ mV_{PP}\ at\ +25^{\circ}C. \end{array} $ |

| RSSI current linearity | ILR <sub>RSSI</sub> | -15  | _                 | 15             | %              | Tested at room temperature only (see<br>Equation 5-1 and Figure 5-7 for test method).                                                                                                                                                                                |

\* Parameter is characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Required output enable filter high time must account for input path analog delays (=  $T_{OEH} - T_{DR} + T_{DF}$ ).

2: Required output enable filter low time must account for input path analog delays (= T<sub>OEL</sub> + T<sub>DR</sub> - T<sub>DF</sub>).

#### **SPI** Timing

| Electrical Specifications: Standard Operating Conditions (unless otherwise stated)         Supply Voltage $2.0V \le V_{DD} \le 3.6V$ Operating temperature $-40^{\circ}C \le T_A \le +85^{\circ}C$ LC Signal Input       Sinusoidal 300 mV <sub>PP</sub> Carrier Frequency       125 kHz         LCCOM connected to V <sub>SS</sub> |                   |      |      |      |       |                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|------|-------|----------------------------------------------------------------|

| Parameters                                                                                                                                                                                                                                                                                                                          | Sym.              | Min. | Typ† | Max. | Units | Conditions                                                     |

| SCLK Frequency                                                                                                                                                                                                                                                                                                                      | F <sub>SCLK</sub> | _    | —    | 3    | MHz   |                                                                |

| CS fall to first SCLK edge setup time                                                                                                                                                                                                                                                                                               | T <sub>CSSC</sub> | 100  | —    | —    | ns    |                                                                |

| SDI setup time                                                                                                                                                                                                                                                                                                                      | T <sub>SU</sub>   | 30   | —    | _    | ns    |                                                                |

| SDI hold time                                                                                                                                                                                                                                                                                                                       | T <sub>HD</sub>   | 50   | —    | _    | ns    |                                                                |

| SCLK high time                                                                                                                                                                                                                                                                                                                      | T <sub>HI</sub>   | 150  | —    | _    | ns    |                                                                |

| SCLK low time                                                                                                                                                                                                                                                                                                                       | T <sub>LO</sub>   | 150  | _    | _    | ns    |                                                                |

| SDO setup time                                                                                                                                                                                                                                                                                                                      | T <sub>DO</sub>   | _    | _    | 150  | ns    |                                                                |

| SCLK last edge to $\overline{CS}$ rise setup time                                                                                                                                                                                                                                                                                   | T <sub>SCCS</sub> | 100  | _    | _    | ns    |                                                                |

| CS high time                                                                                                                                                                                                                                                                                                                        | T <sub>CSH</sub>  | 500  |      | _    | ns    |                                                                |

| CS rise to SCLK edge setup time                                                                                                                                                                                                                                                                                                     | T <sub>CS1</sub>  | 50   | _    | _    | ns    |                                                                |

| SCLK edge to $\overline{CS}$ fall setup time                                                                                                                                                                                                                                                                                        | T <sub>CS0</sub>  | 50   | —    | _    | ns    | SCLK edge when $\overline{CS}$ is high                         |

| Rise time of SPI data<br>(SPI Read command)                                                                                                                                                                                                                                                                                         | TR <sub>SPI</sub> | _    | 10   | -    | ns    | $V_{DD}{=}3.0V.$ Time is measured from 10% to 90% of amplitude |

| Fall time of SPI data<br>(SPI Read command)                                                                                                                                                                                                                                                                                         | TF <sub>SPI</sub> | _    | 10   | -    | ns    | $V_{DD}{=}3.0V.$ Time is measured from 90% to 10% of amplitude |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

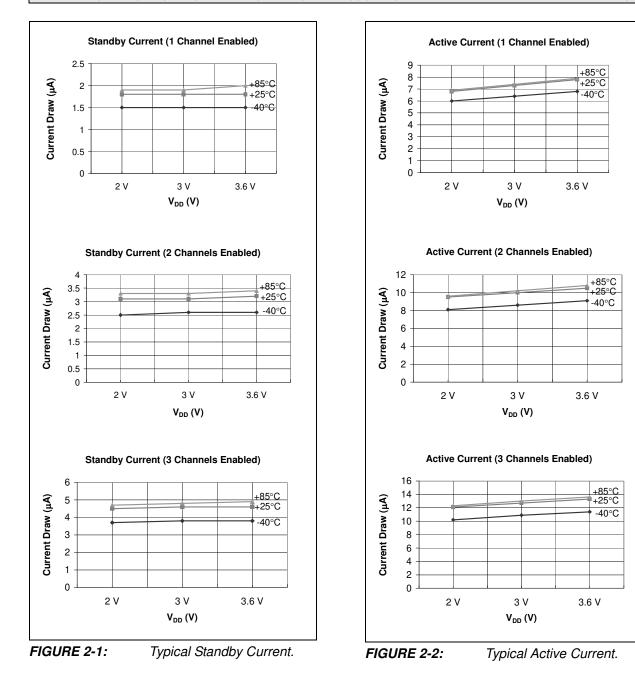

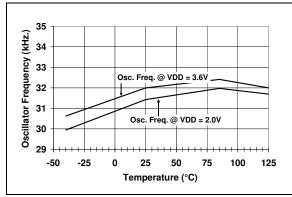

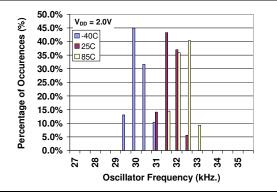

### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**FIGURE 2-3:** Oscillator Frequency vs. Temperature,  $V_{DD} = 3.6V$  and 2.0V.

**FIGURE 2-4:** Oscillator Frequency Histograms vs. Temperature,  $V_{DD} = 2V$ .

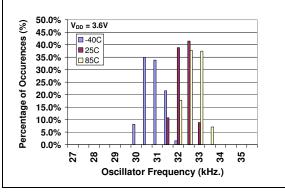

**FIGURE 2-5:** Oscillator Frequency Histograms vs. Temperature at  $V_{DD} = 3V$ .

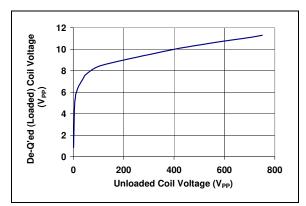

FIGURE 2-6: De-Q'ed Voltage vs. Unloaded Coil Voltage.

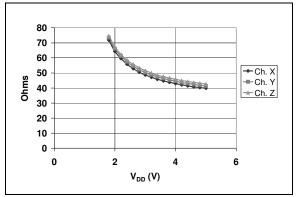

**FIGURE 2-7:** Modulation Transistor-on Resistance (+25°C).

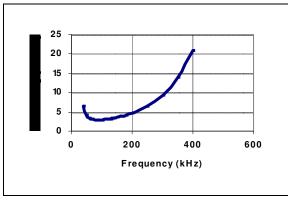

FIGURE 2-8: Bandwidth.

Channel Sensitivity vs.

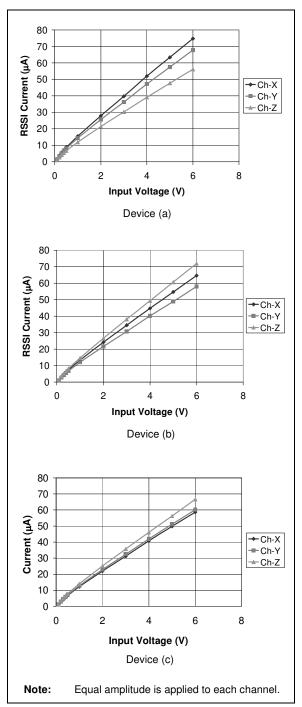

**FIGURE 2-9:** Typical RSSI Output Current vs. Input Signal Strength.

**FIGURE 2-10:** Typical Tuned Capacitance Value vs. Configuration Register Bit Setting  $(V_{DD} = 3V, Temperature = +25^{\circ}C.$

**FIGURE 2-11:** Typical Tuned Capacitance Value vs. Configuration Register Bit Setting  $(V_{DD} = 3V, Temperature = -40 \,^{\circ}C.$

**FIGURE 2-12:** Typical Tuned Capacitance Value vs. Configuration Register Bit Setting  $(V_{DD} = 3V, Temperature = +85 ^{\circ}C.$

**FIGURE 2-13:** Examples of RSSI Output Current Variations Between Channel to Channel and Device to Device at Room Temperature.

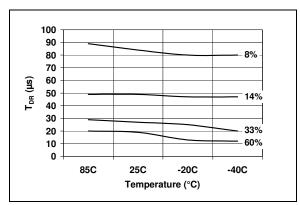

**FIGURE 2-14:** Example of Typical  $T_{DR}$ Changes over Temperature. Input Signal Condition: Amplitude = 300 mV<sub>PR</sub> Modulation Depth = 100 %.

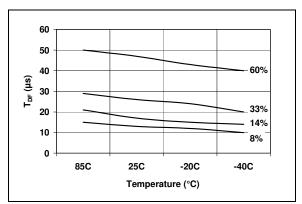

**FIGURE 2-15:** Example of Typical  $T_{DF}$ Changes over Temperature. Input Signal Condition: Amplitude = 300 mV<sub>PP</sub> Modulation Depth = 100 %.

#### 2.1 Performance Plots

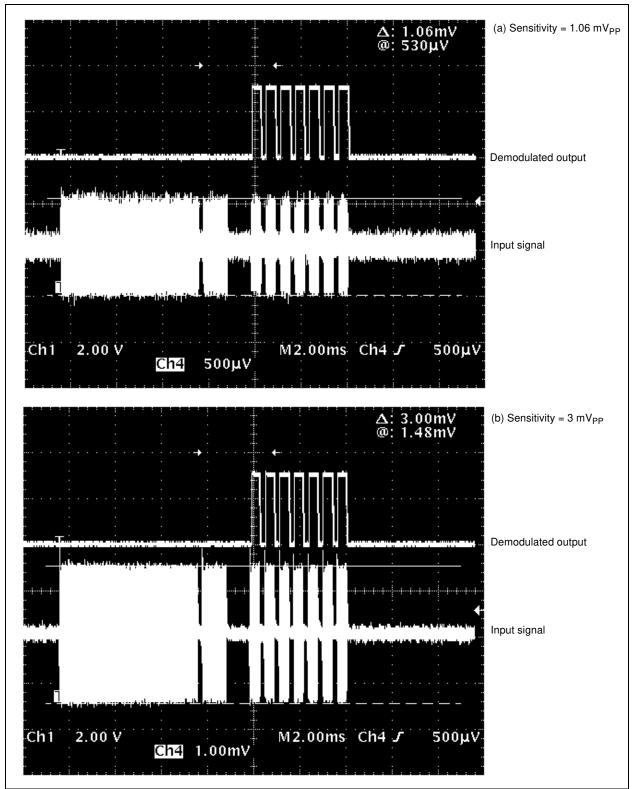

FIGURE 2-16: Input Sensitivity Example.

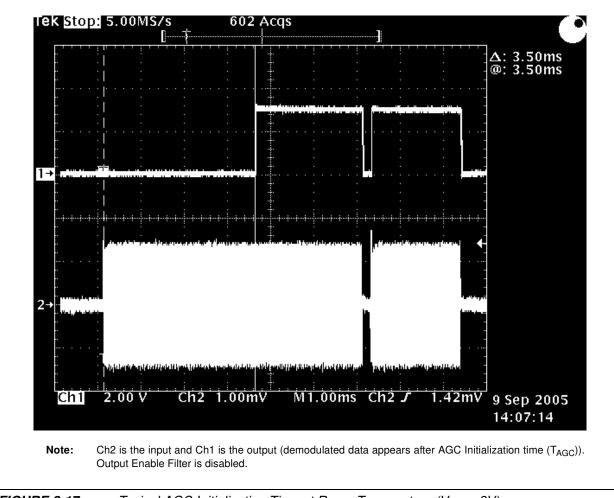

**FIGURE 2-17:** Typical AGC Initialization Time at Room Temperature ( $V_{DD} = 3V$ ).

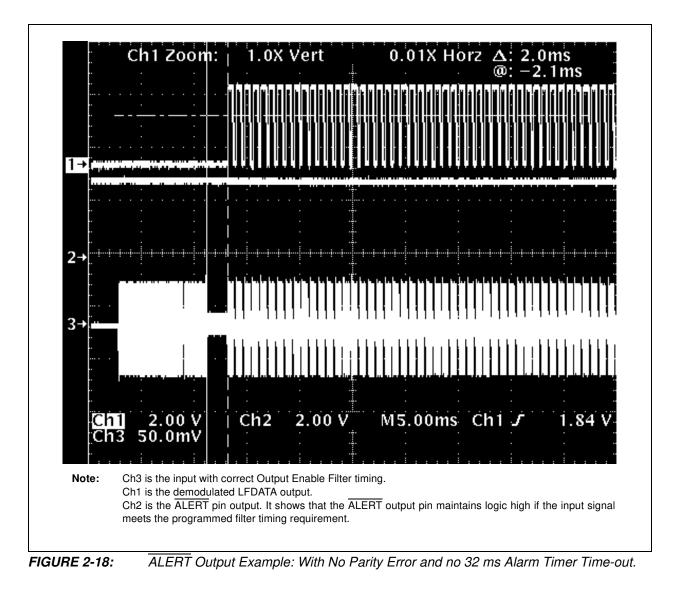

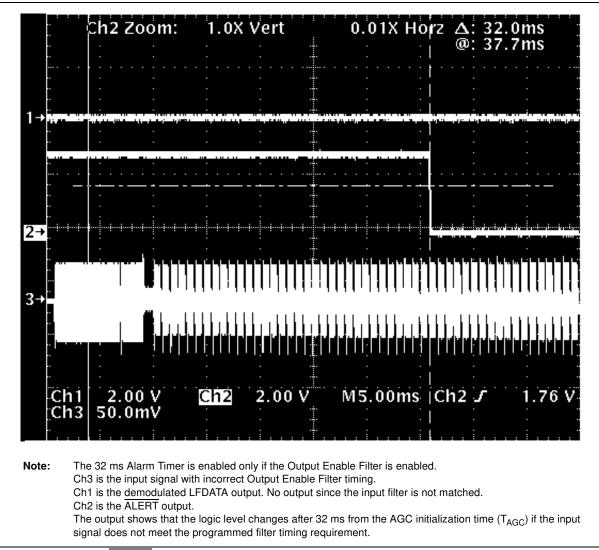

FIGURE 2-19: ALERT Output Example: With 32 ms Alarm Timer Timed out.

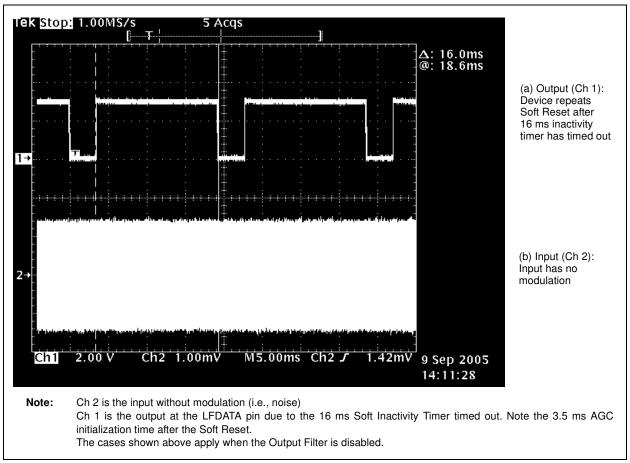

**FIGURE 2-20:** Examples of Soft Inactivity Timer Timed out: This output is available only if the Output Enable Filter is disabled.

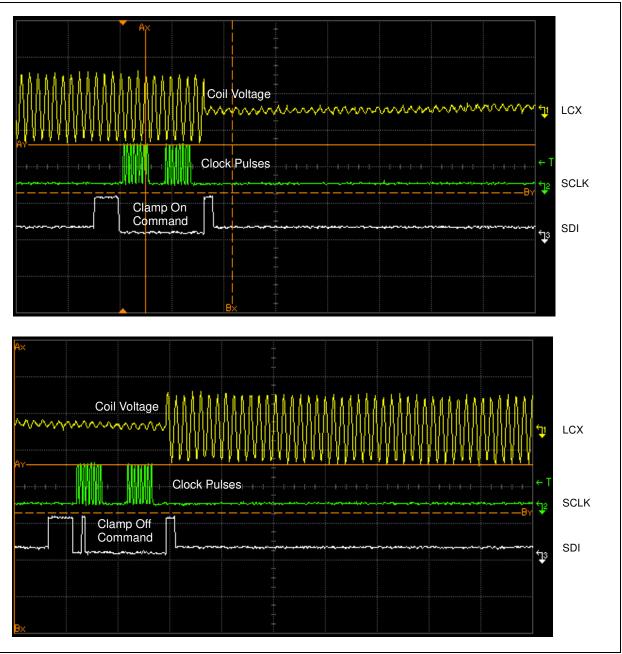

FIGURE 2-21: Examples of Clamp-On and Clamp-Off Commands and Changes in Coil Voltage.

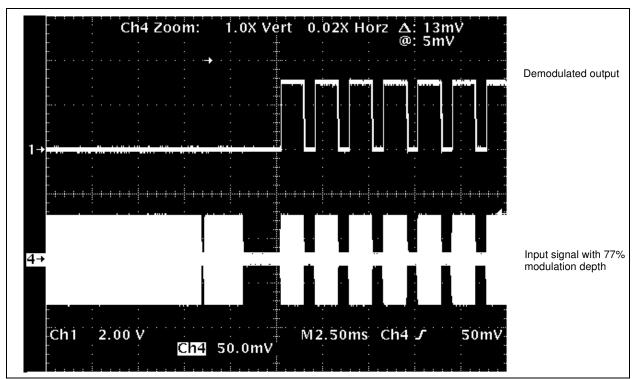

**FIGURE 2-22:** Example of Minimum Modulation Depth Setting: Modulation Depth of Input Signal = 77%, Minimum Modulation Depth (MODMIN) Setting = 60%.

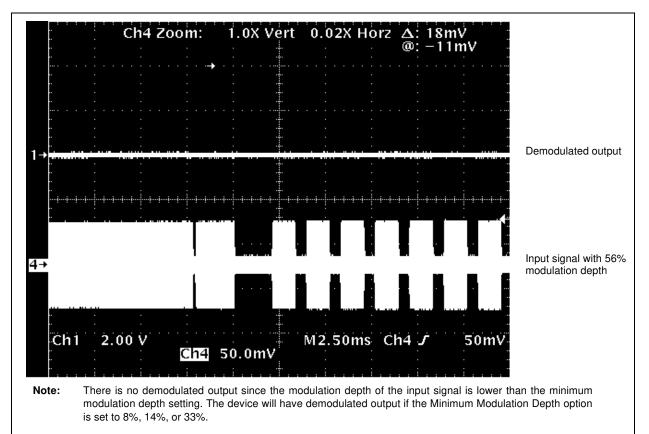

**FIGURE 2-23:** Example of Minimum Modulation Depth Setting: Modulation Depth of Input Signal = 56%, Minimum Modulation Depth (MODMIN) Setting = 60%.

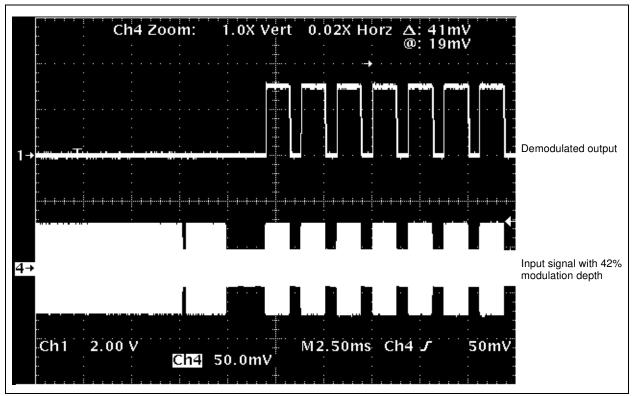

**FIGURE 2-24:** Example of Minimum Modulation Depth Setting: Modulation Depth of Input Signal = 42%, Minimum Modulation Depth (MODMIN) Setting = 33%.

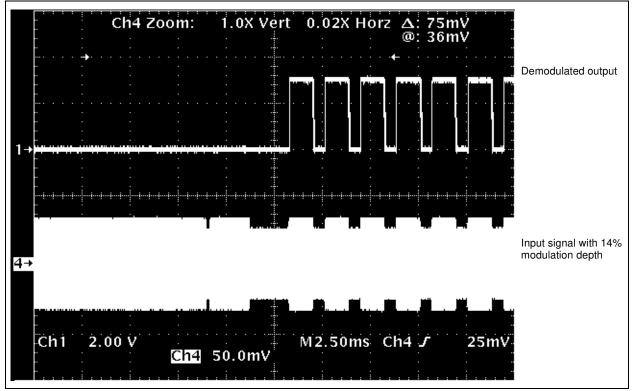

**FIGURE 2-25:** Example of Minimum Modulation Depth Setting: Modulation Depth of Input Signal = 14%, Minimum Modulation Depth (MODMIN) Setting = 14%.

*FIGURE 2-26:* Examples of Output Enable Filters 1 through 3 (Wake-up Filters) and Demodulated Outputs.

*FIGURE 2-27:* Examples of Output Enable Filters 4 through 6 (Wake-up Filters) and Demodulated Outputs.

*FIGURE 2-28:* Examples of Output Enable Filters 7 through 9 (Wake-up Filters) and Demodulated Outputs.

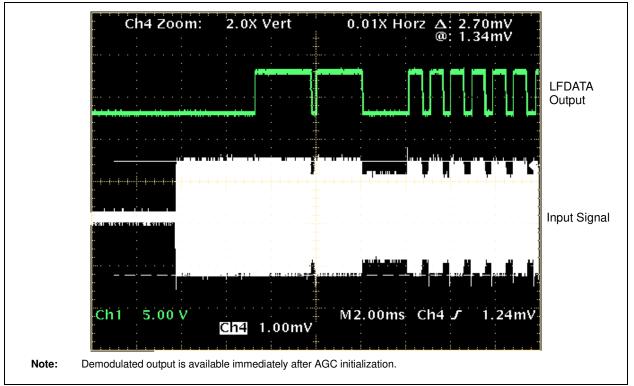

FIGURE 2-29: Input Signal and Demodulated Output When the Output Enable Filter is Disabled.

FIGURE 2-30: Input Signal and Demodulator Output When Output Enable Filter is Enabled and Input

Meets Filter Timing Requirements.

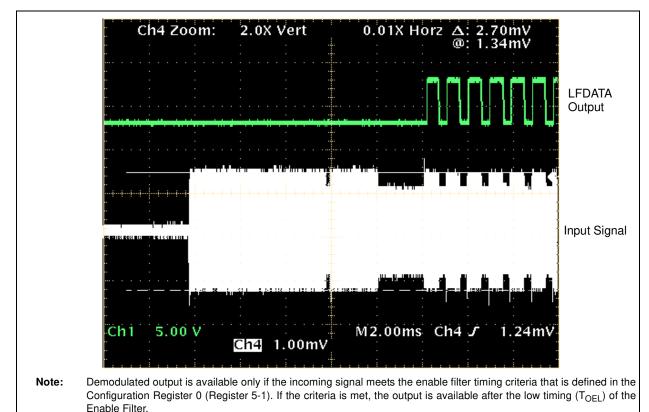

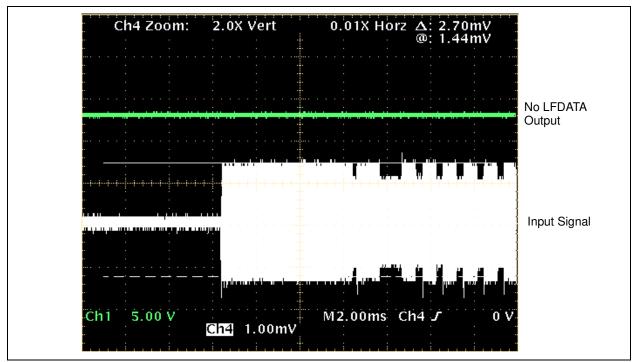

**FIGURE 2-31:** No Demodulator Output When Output Enable Filter is Enabled But Input Does Not Meet Filter Timing Requirements.

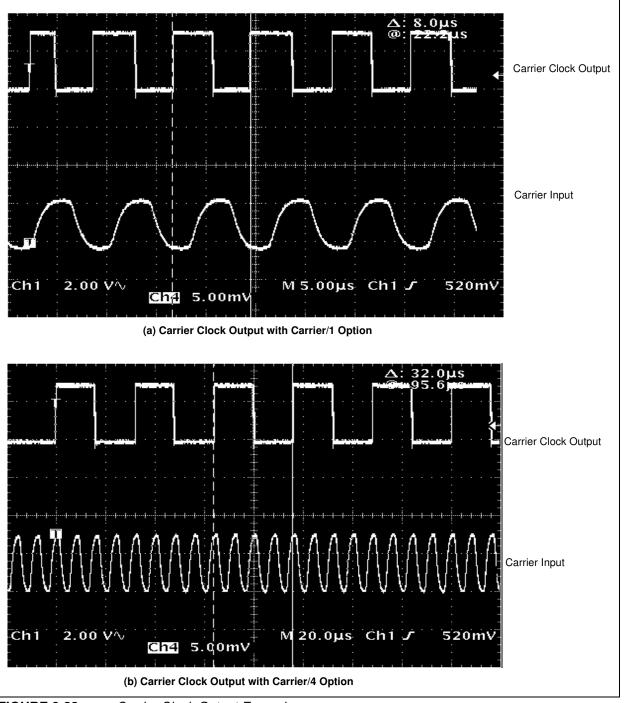

FIGURE 2-32: Carrier Clock Output Examples.

### 3.0 **PIN DESCRIPTIONS**

| Pin No. | Symbol           | I/O/P | Function                                                                                                                                                                                 |

|---------|------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>SS</sub>  | Р     | Ground Pin.                                                                                                                                                                              |

| 2       | CS               | I     | Chip Select Digital Input Pin.                                                                                                                                                           |

| 3       | SCLK/ALERT       | I/O   | Clock input for the modified 3-wire SPI interface.<br>ALERT output: This pin goes low if there is a parity error in the<br>Configuration register or the 32 ms alarm timer is timed out. |

| 4       | RSSI             | 0     | Received Signal Strength Indicator (RSSI) current output.                                                                                                                                |

| 5       | NC               | N/A   | No Connect.                                                                                                                                                                              |

| 6       | LFDATA/CCLK/SDIO | I/O   | Demodulated data output.<br>Carrier clock output.<br>Serial input or output data for the modified 3-wire SPI interface.                                                                  |

| 7       | V <sub>DD</sub>  | Р     | Positive Supply Voltage Pin.                                                                                                                                                             |

| 8       | V <sub>DD</sub>  | Р     | Positive Supply Voltage Pin.                                                                                                                                                             |

| 9       | LCZ              | I     | Input pin for external LC antennas.                                                                                                                                                      |

| 10      | LCY              | I     | Input pin for external LC antennas.                                                                                                                                                      |

| 11      | LCX              | I     | Input pin for external LC antennas.                                                                                                                                                      |

| 12      | NC               | N/A   | No Connect.                                                                                                                                                                              |

| 13      | LCCOM            | I     | Common reference input for the external LC antennas.                                                                                                                                     |

| 14      | V <sub>SS</sub>  | Р     | Ground Pin.                                                                                                                                                                              |

Type Identification: I = Input; O = Output; P = Power

#### 3.1 Supply Voltage (V<sub>DD</sub>, V<sub>SS</sub>)

The  $V_{DD}$  pin is the power supply pin for the analog and digital circuitry within the MCP2030. This pin requires an appropriate bypass capacitor of 0.1  $\mu$ F. The voltage on this pin should be maintained in the 2.0V-3.6V range for specified operation.

The  $V_{SS}$  pin is the ground pin and the current return path for both analog and digital circuitry of the MCP2030. If an analog ground plane is available, it is recommended that this device be tied to the analog ground plane of the PCB.

### 3.2 Chip Select (CS)

The  $\overline{CS}$  pin needs to stay high when the device is receiving input signals. Leaving the  $\overline{CS}$  pin low will place the device in the SPI Programming mode.

The  $\overline{\text{CS}}$  pin is an open collector output. This pin has an internal pull-up resistor to ensure that no spurious SPI communication occurs between power-up and pin configuration of the MCU.

### 3.3 SPI Clock Input (SCLK/ALERT)

This pin becomes the SPI clock input (SCLK) when  $\overline{CS}$  is low, and becomes the ALERT output when  $\overline{CS}$  is high.

The ALERT pin is an open collector output. This pin has an internal pull-up resistor to ensure that no spurious SPI communication occurs between power-up and pin configuration of the MCU.

#### 3.4 Received Signal Strength Indicator (RSSI)

This pin becomes the Received Signal Strength Indicator (RSSI) output current sink when the RSSI output option is selected.