# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# MCP23017/MCP23S17

### **16-Bit I/O Expander with Serial Interface**

#### Features

- 16-Bit Remote Bidirectional I/O Port:

- I/O pins default to input

- High-Speed I<sup>2</sup>C Interface (MCP23017):

- 100 kHz

- 400 kHz

- 1.7 MHz

- High-Speed SPI Interface (MCP23S17):

- 10 MHz (maximum)

- Three Hardware Address Pins to Allow Up to Eight Devices On the Bus

- · Configurable Interrupt Output Pins:

- Configurable as active-high, active-low or open-drain

- INTA and INTB Can Be Configured to Operate Independently or Together

- Configurable Interrupt Source:

- Interrupt-on-change from configured register defaults or pin changes

- Polarity Inversion Register to Configure the Polarity of the Input Port Data

- · External Reset Input

- Low Standby Current: 1 μA (max.)

- · Operating Voltage:

- 1.8V to 5.5V @ -40°C to +85°C

- 2.7V to 5.5V @ -40°C to +85°C

- 4.5V to 5.5V @ -40°C to +125°C

#### Packages

- 28-pin QFN, 6 x 6 mm Body

- · 28-pin SOIC, Wide, 7.50 mm Body

- · 28-pin SPDIP, 300 mil Body

- · 28-pin SSOP, 5.30 mm Body

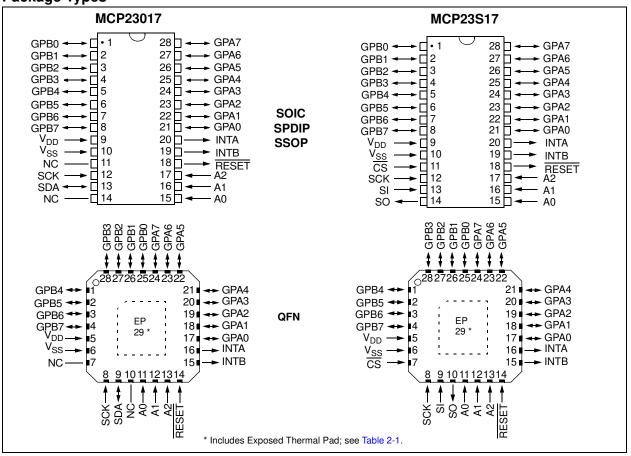

#### **Package Types**

## MCP23017/MCP23S17

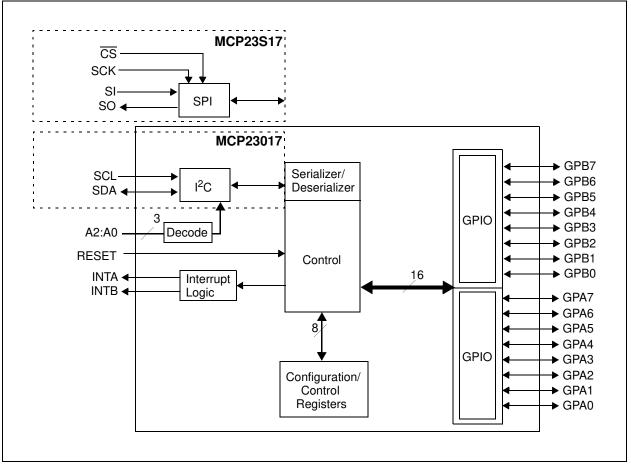

#### **Functional Block Diagram**

### 1.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                          | 40°C to +125°C                   |

|-----------------------------------------------------------------------------------------|----------------------------------|

| Storage temperature                                                                     | 65°C to +150°C                   |

| Voltage on $V_{\text{DD}}$ with respect to $V_{\text{SS}}$                              | 0.3V to +5.5V                    |

| Voltage on all other pins with respect to $V_{\mbox{SS}}$ (except $V_{\mbox{DD}})$      | 0.6V to (V <sub>DD</sub> + 0.6V) |

| Total power dissipation                                                                 | 700 mW                           |

| Maximum current out of V <sub>SS</sub> pin                                              | 150 mA                           |

| Maximum current into V <sub>DD</sub> pin                                                |                                  |

| Input clamp current, $I_{IK}$ (V <sub>I</sub> < 0 or V <sub>I</sub> > V <sub>DD</sub> ) | ±20 mA                           |

| Output clamp current, Iok ( $V_O < 0$ or $V_O > V_{DD}$ )                               | ±20 mA                           |

| Maximum output current sunk by any output pin                                           | 25 mA                            |

| Maximum output current sourced by any output pin                                        | 25 mA                            |

| ESD protection on all pins (HBM:MM)                                                     | 4 kV:400V                        |

**† Notice**: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 1.1 DC Characteristics

#### TABLE 1-1: DC CHARACTERISTICS

| Param.<br>No. | Characteristic                                            | Sym.                                         | Min.                  | Тур. <sup>(1)</sup> | Max.                 | Units | Conditions                                                                                                               |

|---------------|-----------------------------------------------------------|----------------------------------------------|-----------------------|---------------------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------|

| D001          | Supply Voltage                                            | V <sub>DD</sub>                              | 1.8                   |                     | 5.5                  | V     |                                                                                                                          |

| D002          | V <sub>DD</sub> Start Voltage to<br>ensure Power-on Reset | V <sub>POR</sub>                             | —                     | $V_{SS}$            | —                    | V     |                                                                                                                          |

| D003          | V <sub>DD</sub> Rise Rate to ensure<br>Power-on Reset     | SV <sub>DD</sub>                             | 0.05                  | _                   | —                    | V/ms  | Design guidance only.<br>Not tested.                                                                                     |

| D004          | Supply Current                                            | I <sub>DD</sub>                              | —                     | _                   | 1                    | mA    | SCL/SCK = 1 MHz                                                                                                          |

| D005          | Standby current                                           | I <sub>DDS8</sub>                            | —                     | _                   | 1                    | μA    | $-40^{\circ}C \leq T_A \leq +85^{\circ}C$                                                                                |

|               |                                                           |                                              | _                     | _                   | 3                    | μA    | $\begin{array}{l} 4.5V \leq V_{DD} \leq 5.5V \\ +85^\circ C \leq T_A \leq +125^\circ C \\ \textbf{(Note 1)} \end{array}$ |

| Input Lo      | ow Voltage                                                |                                              |                       |                     |                      |       |                                                                                                                          |

| D030          | A0, A1, A2 (TTL buffer)                                   | V <sub>IL</sub>                              | V <sub>SS</sub>       |                     | 0.15 V <sub>DD</sub> | V     |                                                                                                                          |

| D031          | CS, GPIO, SCL/SCK,<br>SDA, RESET<br>(Schmitt Trigger)     | V <sub>IL</sub>                              | V <sub>SS</sub>       | _                   | 0.2 V <sub>DD</sub>  | V     |                                                                                                                          |

| Input Hi      | gh Voltage                                                |                                              |                       |                     |                      |       |                                                                                                                          |

| D040          | A0, A1, A2 (TTL buffer)                                   | V <sub>IH</sub>                              | 0.25 VDD + 0.8        |                     | V <sub>DD</sub>      | V     |                                                                                                                          |

| D041          | CS, GPIO, SCL/SCK,<br>SDA, RESET<br>(Schmitt Trigger)     | V <sub>IH</sub>                              | 0.8 Vdd               |                     | V <sub>DD</sub>      | V     | For entire V <sub>DD</sub> range                                                                                         |

| Input Le      | akage Current                                             | <u>.                                    </u> |                       |                     | <u> </u>             |       |                                                                                                                          |

| D060          | I/O port pins                                             | ١ <sub>IL</sub>                              | —                     |                     | ±1                   | μA    | $V_{SS} \le V_{PIN} \le V_{DD}$                                                                                          |

| Output        | Leakage Current                                           |                                              |                       |                     | <u> </u>             |       | · ··· ··· ·                                                                                                              |

| D065          | I/O port pins                                             | I <sub>LO</sub>                              |                       |                     | ±1                   | μA    | $V_{SS} \le V_{PIN} \le V_{DD}$                                                                                          |

| D070          | GPIO weak pull-up<br>current                              | I <sub>PU</sub>                              | 40                    | 75                  | 115                  | μA    | $V_{DD} = 5V$<br>GP pins = V <sub>SS</sub>                                                                               |

| Output        | Low-Voltage                                               |                                              |                       |                     | 11                   |       |                                                                                                                          |

| D080          | GPIO                                                      | V <sub>OL</sub>                              | _                     | -                   | 0.6                  | V     | I <sub>OL</sub> = 8.0 mA<br>V <sub>DD</sub> = 4.5V                                                                       |

|               | INT                                                       | V <sub>OL</sub>                              | _                     | _                   | 0.6                  | V     | I <sub>OL</sub> = 1.6 mA<br>V <sub>DD</sub> = 4.5V                                                                       |

|               | SO, SDA                                                   | V <sub>OL</sub>                              | —                     |                     | 0.6                  | V     | I <sub>OL</sub> = 3.0 mA<br>V <sub>DD</sub> = 1.8V                                                                       |

|               | SDA                                                       | V <sub>OL</sub>                              | —                     |                     | 0.8                  | V     | I <sub>OL</sub> = 3.0 mA<br>V <sub>DD</sub> = 4.5V                                                                       |

| Output I      | High-Voltage                                              |                                              |                       |                     |                      |       |                                                                                                                          |

| D090          | GPIO, INT, SO                                             | V <sub>OH</sub>                              | V <sub>DD</sub> – 0.7 |                     | —                    | V     | I <sub>OH</sub> = -3.0 mA<br>V <sub>DD</sub> = 4.5V                                                                      |

|               |                                                           |                                              | V <sub>DD</sub> – 0.7 | —                   | -                    |       | I <sub>OH</sub> = -400 μA<br>V <sub>DD</sub> = 1.8V                                                                      |

| <b>^</b>      | ve Loading Specs on Out                                   | put Pins                                     | •                     |                     |                      |       |                                                                                                                          |

| Capacit       | <b>v</b> .                                                |                                              |                       |                     |                      |       |                                                                                                                          |

| D101          | GPIO, SO, INT                                             | C <sub>IO</sub>                              | _                     |                     | 50                   | pF    |                                                                                                                          |

**Note 1:** This parameter is characterized, not 100% tested.

#### 1.2 AC Characteristics

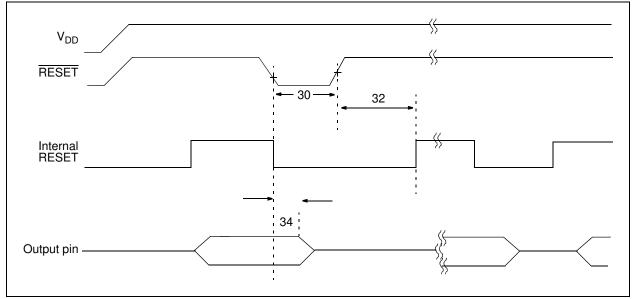

#### FIGURE 1-2: RESET AND DEVICE RESET TIMER TIMING

#### TABLE 1-2: DEVICE RESET SPECIFICATIONS

| AC Cha        | AC Characteristics: Unless otherwise noted, $1.8V \le V_{DD} \le 5.5V$ at $-40^{\circ}C \le T_A \le +125^{\circ}C$ |                   |      |                     |      |       |                        |

|---------------|--------------------------------------------------------------------------------------------------------------------|-------------------|------|---------------------|------|-------|------------------------|

| Param.<br>No. | Characteristic                                                                                                     | Sym.              | Min. | Typ. <sup>(1)</sup> | Max. | Units | Conditions             |

| 30            | RESET Pulse Width<br>(Low)                                                                                         | T <sub>RSTL</sub> | 1    | —                   | _    | μs    |                        |

| 32            | Device Active After Reset<br>high                                                                                  | T <sub>HLD</sub>  | _    | 0                   | _    | ns    | V <sub>DD</sub> = 5.0V |

| 34            | Output High-Impedance<br>From RESET Low                                                                            | Τ <sub>ΙΟΖ</sub>  | _    | —                   | 1    | μs    |                        |

**Note 1:** This parameter is characterized, not 100% tested.

# MCP23017/MCP23S17

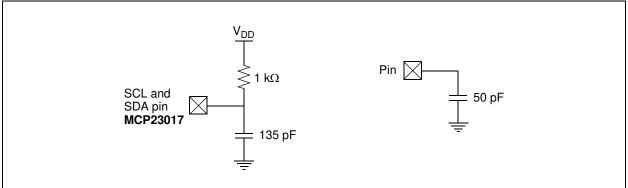

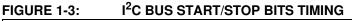

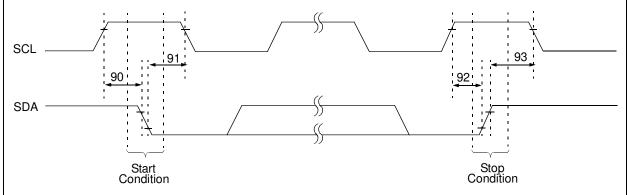

#### FIGURE 1-4: I<sup>2</sup>C BUS DATA TIMING

#### TABLE 1-3: I<sup>2</sup>C BUS DATA REQUIREMENTS

|               | rface AC Characteristics: Unles<br>1 kΩ, C <sub>L</sub> (SCL, SDA) = 135 pF | s otherwis                    | e noted, $1.8V \le V$                  | ′ <sub>DD</sub> ≤ 5. | 5V at -4 | 40°C ≤ <sup>·</sup> | $T_A \le +125^{\circ}C$ , $R_{PU}$ (SCL, |

|---------------|-----------------------------------------------------------------------------|-------------------------------|----------------------------------------|----------------------|----------|---------------------|------------------------------------------|

| Param.<br>No. | Characteristic                                                              | Sym.                          | Min.                                   | Тур.                 | Max.     | Units               | Conditions                               |

| 100           | Clock High Time:                                                            | T <sub>HIGH</sub>             |                                        |                      |          |                     |                                          |

|               | 100 kHz mode                                                                |                               | 4.0                                    | _                    | _        | μs                  | 1.8V – 5.5V                              |

|               | 400 kHz mode                                                                |                               | 0.6                                    | —                    |          | μs                  | 2.7V – 5.5V                              |

|               | 1.7 MHz mode                                                                |                               | 0.12                                   | _                    |          | μs                  | 4.5V – 5.5V                              |

| 101           | Clock Low Time:                                                             | T <sub>LOW</sub>              |                                        |                      |          |                     |                                          |

|               | 100 kHz mode                                                                |                               | 4.7                                    | _                    | _        | μs                  | 1.8V – 5.5V                              |

|               | 400 kHz mode                                                                |                               | 1.3                                    | _                    |          | μs                  | 2.7V – 5.5V                              |

|               | 1.7 MHz mode                                                                |                               | 0.32                                   | _                    | _        | μs                  | 4.5V – 5.5V                              |

| 102           | SDA and SCL Rise Time:                                                      | T <sub>R</sub> (1)            |                                        |                      |          |                     |                                          |

|               | 100 kHz mode                                                                |                               | —                                      | —                    | 1000     | ns                  | 1.8V – 5.5V                              |

|               | 400 kHz mode                                                                |                               | 20 + 0.1 C <sub>B</sub> <sup>(2)</sup> | _                    | 300      | ns                  | 2.7V – 5.5V                              |

|               | 1.7 MHz mode                                                                |                               | 20                                     | _                    | 160      | ns                  | 4.5V – 5.5V                              |

| 103           | SDA and SCL Fall Time:                                                      | T <sub>F</sub> <sup>(1)</sup> |                                        |                      |          |                     |                                          |

|               | 100 kHz mode                                                                |                               | —                                      | _                    | 300      | ns                  | 1.8V – 5.5V                              |

|               | 400 kHz mode                                                                |                               | 20 + 0.1 C <sub>B</sub> <sup>(2)</sup> | _                    | 300      | ns                  | 2.7V – 5.5V                              |

|               | 1.7 MHz mode                                                                |                               | 20                                     | _                    | 80       | ns                  | 4.5V – 5.5V                              |

Note 1: This parameter is characterized, not 100% tested.

**2:** C<sub>B</sub> is specified to be from 10 to 400 pF.

#### TABLE 1-3: I<sup>2</sup>C BUS DATA REQUIREMENTS (CONTINUED)

$\hline \textbf{I^2C Interface AC Characteristics: } Unless otherwise noted, 1.8V \leq V_{DD} \leq 5.5V \text{ at } -40^\circ\text{C} \leq T_A \leq +125^\circ\text{C}, \text{ R}_{PU} (SCL, SDA) = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ k}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ c}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ c}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ c}\Omega, \text{ C}_L (SCL, SDA) = 135 \text{ pF} \\ \hline \textbf{SDA} = 1 \text{ c}\Omega, \text{ C} =$

| -             | 1 kΩ, C <sub>L</sub> (SCL, SDA) = 135 pF      | <u>г                                    </u> |      |      |      | r     | Γ                     |

|---------------|-----------------------------------------------|----------------------------------------------|------|------|------|-------|-----------------------|

| Param.<br>No. | Characteristic                                | Sym.                                         | Min. | Тур. | Max. | Units | Conditions            |

| 90            | START Condition Setup Time:                   | T <sub>SU:STA</sub>                          |      |      |      |       |                       |

|               | 100 kHz mode                                  |                                              | 4.7  | —    | _    | μs    | 1.8V – 5.5V           |

|               | 400 kHz mode                                  |                                              | 0.6  | —    | _    | μs    | 2.7V – 5.5V           |

|               | 1.7 MHz mode                                  |                                              | 0.16 | —    | _    | μs    | 4.5V – 5.5V           |

| 91            | START Condition Hold Time:                    | T <sub>HD:STA</sub>                          |      |      |      |       |                       |

|               | 100 kHz mode                                  |                                              | 4.0  | -    |      | μs    | 1.8V – 5.5V           |

|               | 400 kHz mode                                  |                                              | 0.6  | —    | _    | μs    | 2.7V – 5.5V           |

|               | 1.7 MHz mode                                  |                                              | 0.16 | _    | _    | μs    | 4.5V – 5.5V           |

| 106           | Data Input Hold Time:                         | T <sub>HD:DAT</sub>                          |      |      |      |       |                       |

|               | 100 kHz mode                                  |                                              | 0    | —    | 3.45 | μs    | 1.8V – 5.5V           |

|               | 400 kHz mode                                  |                                              | 0    | _    | 0.9  | μs    | 2.7V – 5.5V           |

|               | 1.7 MHz mode                                  |                                              | 0    | —    | 0.15 | μs    | 4.5V – 5.5V           |

| 107           | Data Input Setup Time:                        | T <sub>SU:DAT</sub>                          |      |      |      |       |                       |

|               | 100 kHz mode                                  |                                              | 250  | —    | _    | ns    | 1.8V – 5.5V           |

|               | 400 kHz mode                                  |                                              | 100  | _    | _    | ns    | 2.7V – 5.5V           |

|               | 1.7 MHz mode                                  |                                              | 0.01 | —    |      | μs    | 4.5V – 5.5V           |

| 92            | Stop Condition Setup Time:                    | T <sub>SU:STO</sub>                          |      |      |      |       |                       |

|               | 100 kHz mode                                  |                                              | 4.0  | _    | _    | μs    | 1.8V – 5.5V           |

|               | 400 kHz mode                                  |                                              | 0.6  | —    | _    | μs    | 2.7V – 5.5V           |

|               | 1.7 MHz mode                                  |                                              | 0.16 | _    |      | μs    | 4.5V–5.5V             |

| 109           | Output Valid From Clock:                      | T <sub>AA</sub>                              |      |      |      |       |                       |

|               | 100 kHz mode                                  |                                              |      | _    | 3.45 | μs    | 1.8V – 5.5V           |

|               | 400 kHz mode                                  |                                              |      | _    | 0.9  | μs    | 2.7V – 5.5V           |

|               | 1.7 MHz mode                                  |                                              | _    | —    | 0.18 | μs    | 4.5V – 5.5V           |

| 110           | Bus Free Time:                                | T <sub>BUF</sub>                             |      | •    |      |       |                       |

|               | 100 kHz mode                                  |                                              | 4.7  | _    | _    | μs    | 1.8V – 5.5V           |

|               | 400 kHz mode                                  |                                              | 1.3  | —    | _    | μs    | 2.7V – 5.5V           |

|               | 1.7 MHz mode                                  |                                              | N/A  | —    | N/A  | μs    | 4.5V – 5.5V           |

| 111           | Bus Capacitive Loading:                       | CB                                           |      | •    |      |       |                       |

|               | 100 kHz and 400 kHz                           |                                              | _    | —    | 400  | pF    | Note 1                |

|               | 1.7 MHz                                       |                                              | _    | —    | 100  | pF    | Note 1                |

| 112           | Input Filter Spike Suppression (SDA and SCL): | T <sub>SP</sub>                              |      |      |      |       |                       |

|               | 100 kHz and 400 kHz                           |                                              | _    | —    | 50   | ns    |                       |

|               | 1.7 MHz                                       |                                              |      | —    | 10   | ns    | Spike suppression off |

**Note 1:** This parameter is characterized, not 100% tested.

2: C<sub>B</sub> is specified to be from 10 to 400 pF.

### MCP23017/MCP23S17

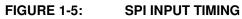

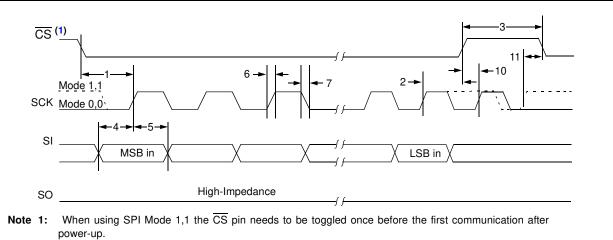

#### TABLE 1-4: SPI INTERFACE REQUIREMENTS

| SPI Inter     | SPI Interface AC Characteristics: Unless otherwise noted, $1.8V \le V_{DD} \le 5.5V$ at $-40^{\circ}C \le T_A \le +125^{\circ}C$ |                  |      |      |      |       |             |

|---------------|----------------------------------------------------------------------------------------------------------------------------------|------------------|------|------|------|-------|-------------|

| Param.<br>No. | Characteristic                                                                                                                   | Sym.             | Min. | Тур. | Max. | Units | Conditions  |

| _             | Clock Frequency                                                                                                                  | F <sub>CLK</sub> |      | _    | 5    | MHz   | 1.8V – 5.5V |

|               |                                                                                                                                  |                  | —    | _    | 10   | MHz   | 2.7V – 5.5V |

|               |                                                                                                                                  |                  | —    | _    | 10   | MHz   | 4.5V – 5.5V |

| 1             | CS Setup Time                                                                                                                    | T <sub>CSS</sub> | 50   | _    |      | ns    |             |

| 2             | CS Hold Time                                                                                                                     | T <sub>CSH</sub> | 100  |      |      | ns    | 1.8V – 5.5V |

|               |                                                                                                                                  |                  | 50   |      | —    | ns    | 2.7V – 5.5V |

| 3             | CS Disable Time                                                                                                                  | T <sub>CSD</sub> | 100  | —    |      | ns    | 1.8V – 5.5V |

|               |                                                                                                                                  |                  | 50   | _    |      | ns    | 2.7V – 5.5V |

| 4             | Data Setup Time                                                                                                                  | Τ <sub>SU</sub>  | 20   | _    |      | ns    | 1.8V – 5.5V |

|               |                                                                                                                                  |                  | 10   | _    |      | ns    | 2.7V – 5.5V |

**Note 1:** This parameter is characterized, not 100% tested.

| PI Inter      | face AC Characteristics: Unle | ess otherwis     | se noted | , 1.8V ≤ | $V_{DD} \le 5$ | .5V at -4 | $0^{\circ}C \leq T_A \leq +125^{\circ}C$ |

|---------------|-------------------------------|------------------|----------|----------|----------------|-----------|------------------------------------------|

| Param.<br>No. | Characteristic                | Sym.             | Min.     | Тур.     | Max.           | Units     | Conditions                               |

| 5             | Data Hold Time                | T <sub>HD</sub>  | 20       |          |                | ns        | 1.8V – 5.5V                              |

|               |                               |                  | 10       | _        |                | ns        | 2.7V – 5.5V                              |

| 6             | CLK Rise Time                 | Τ <sub>R</sub>   | —        | _        | 2              | μs        | Note 1                                   |

| 7             | CLK Fall Time                 | Τ <sub>F</sub>   | —        | _        | 2              | μs        | Note 1                                   |

| 8             | Clock High Time               | T <sub>HI</sub>  | 90       | _        | _              | ns        | 1.8V – 5.5V                              |

|               |                               |                  | 45       | _        | _              | ns        | 2.7V – 5.5V                              |

| 9             | Clock Low Time                | T <sub>LO</sub>  | 90       | _        | —              | ns        | 1.8V – 5.5V                              |

|               |                               |                  | 45       | _        | _              | ns        | 2.7V – 5.5V                              |

| 10            | Clock Delay Time              | T <sub>CLD</sub> | 50       | _        |                | ns        |                                          |

| 11            | Clock Enable Time             | T <sub>CLE</sub> | 50       | _        |                | ns        |                                          |

| 12            | Output Valid from Clock Low   | Τv               | —        | _        | 90             | ns        | 1.8V – 5.5V                              |

|               |                               |                  | —        | _        | 45             | ns        | 2.7V – 5.5V                              |

| 13            | Output Hold Time              | Т <sub>НО</sub>  | 0        | _        | —              | ns        |                                          |

| 14            | Output Disable Time           | T <sub>DIS</sub> |          | _        | 100            | ns        |                                          |

**Note 1:** This parameter is characterized, not 100% tested.

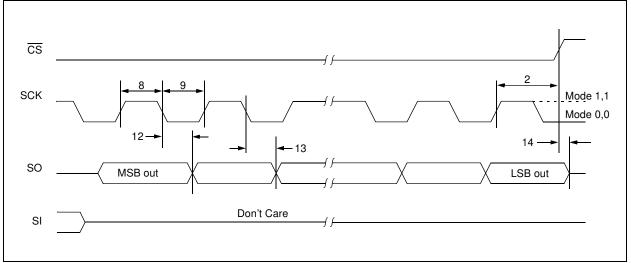

#### FIGURE 1-7: GPIO AND INT TIMING

#### TABLE 1-5: GP AND INT PINS REQUIREMENTS

| Param.<br>No. | Characteristic                       | Sym.                | Min. | Тур. | Max. | Units | Conditions |

|---------------|--------------------------------------|---------------------|------|------|------|-------|------------|

| 50            | Serial Data to Output Valid          | T <sub>GPOV</sub>   | _    |      | 500  | ns    |            |

| 51            | Interrupt Pin Disable Time           | T <sub>INTD</sub>   | —    | —    | 600  | ns    |            |

| 52            | GP Input Change to<br>Register Valid | T <sub>GPIV</sub>   | _    | _    | 450  | ns    |            |

| 53            | IOC Event to INT Active              | T <sub>GPINT</sub>  | _    | _    | 600  | ns    |            |

|               | Glitch Filter on GP Pins             | T <sub>GLITCH</sub> | _    | —    | 150  | ns    | Note 1     |

**Note 1:** This parameter is characterized, not 100% tested.

#### 2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

| IADLE       |     |                       |             |                                                                                                      |

|-------------|-----|-----------------------|-------------|------------------------------------------------------------------------------------------------------|

| Pin<br>Name | QFN | SOIC<br>SPDIP<br>SSOP | Pin<br>Type | Function                                                                                             |

| GPB0        | 25  | 1                     | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPB1        | 26  | 2                     | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPB2        | 27  | 3                     | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPB3        | 28  | 4                     | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPB4        | 1   | 5                     | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPB5        | 2   | 6                     | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPB6        | 3   | 7                     | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPB7        | 4   | 8                     | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| $V_{DD}$    | 5   | 9                     | Р           | Power                                                                                                |

| $V_{SS}$    | 6   | 10                    | Р           | Ground                                                                                               |

| NC/CS       | 7   | 11                    | Ι           | NC (MCP23017)/Chip Select (MCP23S17)                                                                 |

| SCK         | 8   | 12                    | Ι           | Serial clock input                                                                                   |

| SDA/SI      | 9   | 13                    | I/O         | Serial data I/O (MCP23017)/Serial data input (MCP23S17)                                              |

| NC/SO       | 10  | 14                    | 0           | NC (MCP23017)/Serial data out (MCP23S17)                                                             |

| A0          | 11  | 15                    | Ι           | Hardware address pin. Must be externally biased.                                                     |

| A1          | 12  | 16                    | Ι           | Hardware address pin. Must be externally biased.                                                     |

| A2          | 13  | 17                    | Ι           | Hardware address pin. Must be externally biased.                                                     |

| RESET       | 14  | 18                    | -           | Hardware reset. Must be externally biased.                                                           |

| INTB        | 15  | 19                    | 0           | Interrupt output for PORTB. Can be configured as active-high, active-low or open-drain.              |

| INTA        | 16  | 20                    | 0           | Interrupt output for PORTA. Can be configured as active-high, active-low or open-drain.              |

| GPA0        | 17  | 21                    | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPA1        | 18  | 22                    | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPA2        | 19  | 23                    | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPA3        | 20  | 24                    | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPA4        | 21  | 25                    | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPA5        | 22  | 26                    | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPA6        | 23  | 27                    | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| GPA7        | 24  | 28                    | I/O         | Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor. |

| EP          | 29  | _                     | _           | Exposed Thermal Pad. Either connect to V <sub>SS</sub> , or leave unconnected.                       |

#### TABLE 2-1: PINOUT DESCRIPTION

#### 3.0 DEVICE OVERVIEW

The MCP23017/MCP23S17 (MCP23X17) device family provides 16-bit, general purpose parallel I/O expansion for  $I^2C$  bus or SPI applications. The two devices differ only in the serial interface:

- MCP23017 I<sup>2</sup>C interface

- MCP23S17 SPI interface

The MCP23X17 consists of multiple 8-bit configuration registers for input, output and polarity selection. The system master can enable the I/Os as either inputs or outputs by writing the I/O configuration bits (IODIRA/B). The data for each input or output is kept in the corresponding input or output register. The polarity of the Input Port register can be inverted with the Polarity Inversion register. All registers can be read by the system master.

The 16-bit I/O port functionally consists of two 8-bit ports (PORTA and PORTB). The MCP23X17 can be configured to operate in the 8-bit or 16-bit modes via IOCON.BANK.

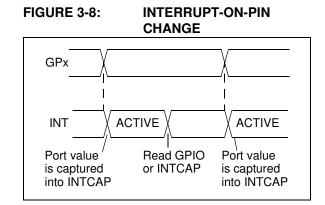

There are two interrupt pins, INTA and INTB, that can be associated with their respective ports, or can be logically OR'ed together so that both pins will activate if either port causes an interrupt.

The interrupt output can be configured to activate under two conditions (mutually exclusive):

- 1. When any input state differs from its corresponding Input Port register state. This is used to indicate to the system master that an input state has changed.

- 2. When an input state differs from a preconfigured register value (DEFVAL register).

The Interrupt Capture register captures port values at the time of the interrupt, thereby saving the condition that caused the interrupt.

The Power-on Reset (POR) sets the registers to their default values and initializes the device state machine.

The hardware address pins are used to determine the device address.

#### 3.1 Power-on Reset (POR)

The on-chip POR circuit holds the device in reset until  $V_{DD}$  has reached a high enough voltage to deactivate the POR circuit (i.e., release the device from reset). The maximum  $V_{DD}$  rise time is specified in Section 1.0 "Electrical Characteristics".

When the device exits the POR condition (releases reset), device operating parameters (i.e., voltage, temperature, serial bus frequency, etc.) must be met to ensure proper operation.

#### 3.2 Serial Interface

This block handles the functionality of the  $I^2C$  (**MCP23017**) or SPI (**MCP23S17**) interface protocol. The MCP23X17 contains 22 individual registers (11 register pairs) that can be addressed through the Serial Interface block, as shown in Table 3-1.

TABLE 3-1: REGISTER ADDRESSES

| Address<br>IOCON.BANK = 1 | Address<br>IOCON.BANK = 0 | Access to: |

|---------------------------|---------------------------|------------|

| 00h                       | 00h                       | IODIRA     |

| 10h                       | 01h                       | IODIRB     |

| 01h                       | 02h                       | IPOLA      |

| 11h                       | 03h                       | IPOLB      |

| 02h                       | 04h                       | GPINTENA   |

| 12h                       | 05h                       | GPINTENB   |

| 03h                       | 06h                       | DEFVALA    |

| 13h                       | 07h                       | DEFVALB    |

| 04h                       | 08h                       | INTCONA    |

| 14h                       | 09h                       | INTCONB    |

| 05h                       | 0Ah                       | IOCON      |

| 15h                       | 0Bh                       | IOCON      |

| 06h                       | 0Ch                       | GPPUA      |

| 16h                       | 0Dh                       | GPPUB      |

| 07h                       | 0Eh                       | INTFA      |

| 17h                       | 0Fh                       | INTFB      |

| 08h                       | 10h                       | INTCAPA    |

| 18h                       | 11h                       | INTCAPB    |

| 09h                       | 12h                       | GPIOA      |

| 19h                       | 13h                       | GPIOB      |

| 0Ah                       | 14h                       | OLATA      |

| 1Ah                       | 15h                       | OLATB      |

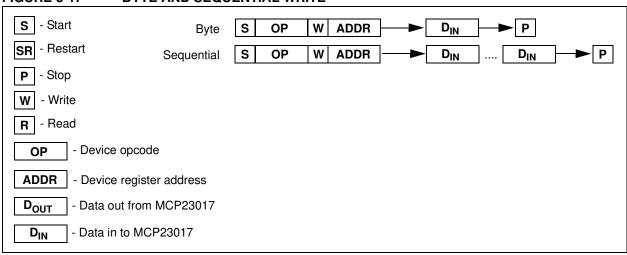

### 3.2.1 BYTE MODE AND SEQUENTIAL MODE

The MCP23X17 family has the ability to operate in Byte mode or Sequential mode (IOCON.SEQOP).

**Byte mode** disables automatic Address Pointer incrementing. When operating in Byte mode, the MCP23X17 family does not increment its internal address counter after each byte during the data transfer. This gives the ability to continually access the same address by providing extra clocks (without additional control bytes). This is useful for polling the GPIO register for data changes or for continually writing to the output latches.

A special mode (Byte mode with IOCON.BANK = 0) causes the address pointer to toggle between associated A/B register pairs. For example, if the BANK bit is cleared and the Address Pointer is initially set to address 12h (GPIOA) or 13h (GPIOB), the pointer will toggle between GPIOA and GPIOB. Note that the Address Pointer can initially point to either address in the register pair.

**Sequential mode** enables automatic address pointer incrementing. When operating in Sequential mode, the MCP23X17 family increments its address counter after each byte during the data transfer. The Address Pointer automatically rolls over to address 00h after accessing the last register.

These two modes are not to be confused with single writes/reads and continuous writes/reads that are serial protocol sequences. For example, the device may be configured for Byte mode and the master may perform a continuous read. In this case, the MCP23X17 would not increment the Address Pointer and would repeatedly drive data from the same location.

#### 3.2.2 I<sup>2</sup>C INTERFACE

#### 3.2.2.1 I<sup>2</sup>C Write Operation

The  $I^2C$  write operation includes the control byte and register address sequence, as shown in Figure 3-1. This sequence is followed by eight bits of data from the master and an Acknowledge (ACK) from the MCP23017. The operation is ended with a Stop (P) or Restart (SR) condition being generated by the master.

Data is written to the MCP23017 after every byte transfer. If a Stop or Restart condition is generated during a data transfer, the data will not be written to the MCP23017.

Both "byte writes" and "sequential writes" are supported by the MCP23017. If Sequential mode is enabled (IOCON, SEQOP = 0) (default), the MCP23017 increments its address counter after each ACK during the data transfer.

#### FIGURE 3-1: BYTE AND SEQUENTIAL WRITE

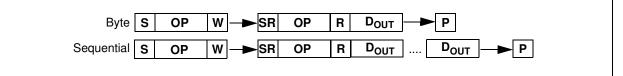

#### 3.2.2.2 I<sup>2</sup>C Read Operation

$I^2C$  Read operations include the control byte sequence, as shown in Figure 3-2. This sequence is followed by another control byte (including the Start condition and ACK) with the R/W bit set (R/W = 1). The MCP23017 then transmits the data contained in the addressed register. The sequence is ended with the master generating a Stop or Restart condition.

#### FIGURE 3-2: BYTE AND SEQUENTIAL READ

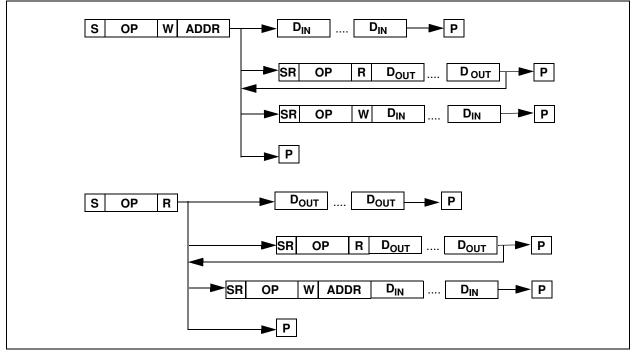

#### 3.2.2.3 I<sup>2</sup>C Sequential Write/Read

For sequential operations (Write or Read), instead of transmitting a Stop or Restart condition after the data transfer, the master clocks the next byte pointed to by the address pointer (see Section 3.2.1 "Byte Mode and Sequential Mode" for details regarding sequential operation control).

The sequence ends with the master sending a Stop or Restart condition.

The MCP23017 Address Pointer will roll over to address zero after reaching the last register address. Refer to Figure 3-3.

#### FIGURE 3-3: MCP23017 I<sup>2</sup>C DEVICE PROTOCOL

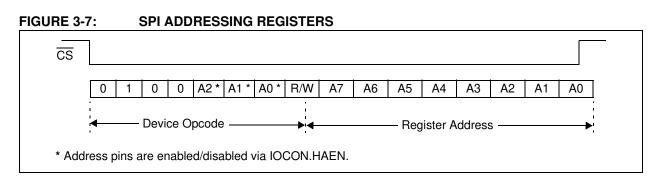

#### 3.2.3 SPI INTERFACE

#### 3.2.3.1 SPI Write Operation

The SPI write operation is started by lowering  $\overline{CS}$ . The Write command (slave address with R/W bit cleared) is then clocked into the device. The opcode is followed by an address and at least one data byte.

#### 3.2.3.2 SPI Read Operation

The SPI read operation is started by lowering  $\overline{CS}$ . The SPI read command (slave address with R/W bit set) is then clocked into the device. The opcode is followed by an address, with at least one data byte being clocked out of the device.

#### 3.2.3.3 SPI Sequential Write/Read

For sequential operations, instead of deselecting the device by raising  $\overline{CS}$ , the master clocks the next byte pointed to by the Address Pointer. (see Section 3.2.1 "Byte Mode and Sequential Mode" for details regarding sequential operation control).

The sequence ends by the raising of  $\overline{CS}$ .

The MCP23S17 Address Pointer will roll over to address zero after reaching the last register address.

#### 3.3 Hardware Address Decoder

The hardware address pins are used to determine the device address. To address a device, the corresponding address bits in the control byte must match the pin state. The pins must be biased externally.

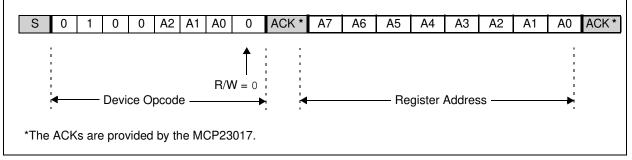

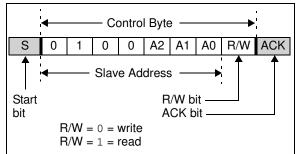

### 3.3.1 ADDRESSING I<sup>2</sup>C DEVICES (MCP23017)

The MCP23017 is a slave  $I^2C$  interface device that supports 7-bit slave addressing, with the read/write bit filling out the control byte. The slave address contains

#### I<sup>2</sup>C ADDRESSING REGISTERS

four fixed bits and three user-defined hardware address bits (pins A2, A1 and A0). Figure 3-4 shows the control byte format.

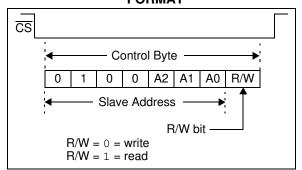

### 3.3.2 ADDRESSING SPI DEVICES (MCP23S17)

The MCP23S17 is a slave SPI device. The slave address contains four fixed bits and three user-defined hardware address bits (if enabled via IOCON.HAEN) (pins A2, A1 and A0) with the read/write bit filling out the control byte. Figure 3-5 shows the control byte format. The address pins should be externally biased even if disabled (IOCON.HAEN = 0).

SPI CONTROL BYTE FORMAT

## MCP23017/MCP23S17

#### 3.4 GPIO Port

The GPIO module is a general purpose, 16-bit wide, bidirectional port that is functionally split into two 8-bit wide ports.

The GPIO module contains the data ports (GPIOn), internal pull-up resistors and the output latches (OLATn).

Reading the GPIOn register reads the value on the port. Reading the OLATn register only reads the latches, not the actual value on the port.

Writing to the GPIOn register actually causes a write to the latches (OLATn). Writing to the OLATn register forces the associated output drivers to drive to the level in OLATn. Pins configured as inputs turn off the associated output driver and put it in high-impedance.

| <b>TABLE 3-2:</b> | SUMMARY OF REGISTERS ASSOCIATED WITH THE GPIO PORTS (BANK = 1) |

|-------------------|----------------------------------------------------------------|

|-------------------|----------------------------------------------------------------|

| Register<br>Name | Address<br>(hex) | bit 7  | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  | POR/RST<br>value |

|------------------|------------------|--------|--------|--------|--------|--------|--------|--------|--------|------------------|

| IODIRA           | 00               | 107    | IO6    | 105    | IO4    | IO3    | IO2    | IO1    | IO0    | 1111 1111        |

| IPOLA            | 01               | IP7    | IP6    | IP5    | IP4    | IP3    | IP2    | IP1    | IP0    | 0000 0000        |

| GPINTENA         | 02               | GPINT7 | GPINT6 | GPINT5 | GPINT4 | GPINT3 | GPINT2 | GPINT1 | GPINT0 | 0000 0000        |

| GPPUA            | 06               | PU7    | PU6    | PU5    | PU4    | PU3    | PU2    | PU1    | PU0    | 0000 0000        |

| GPIOA            | 09               | GP7    | GP6    | GP5    | GP4    | GP3    | GP2    | GP1    | GP0    | 0000 0000        |

| OLATA            | 0A               | OL7    | OL6    | OL5    | OL4    | OL3    | OL2    | OL1    | OL0    | 0000 0000        |

| IODIRB           | 10               | 107    | IO6    | IO5    | IO4    | IO3    | IO2    | IO1    | IO0    | 1111 1111        |

| IPOLB            | 11               | IP7    | IP6    | IP5    | IP4    | IP3    | IP2    | IP1    | IP0    | 0000 0000        |

| GPINTENB         | 12               | GPINT7 | GPINT6 | GPINT5 | GPINT4 | GPINT3 | GPINT2 | GPINT1 | GPINT0 | 0000 0000        |

| GPPUB            | 16               | PU7    | PU6    | PU5    | PU4    | PU3    | PU2    | PU1    | PU0    | 0000 0000        |

| GPIOB            | 19               | GP7    | GP6    | GP5    | GP4    | GP3    | GP2    | GP1    | GP0    | 0000 0000        |

| OLATB            | 1A               | OL7    | OL6    | OL5    | OL4    | OL3    | OL2    | OL1    | OL0    | 0000 0000        |

#### TABLE 3-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE GPIO PORTS (BANK = 0)

| Register<br>Name | Address<br>(hex) | bit 7  | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  | POR/RST<br>value |

|------------------|------------------|--------|--------|--------|--------|--------|--------|--------|--------|------------------|

| IODIRA           | 00               | 107    | IO6    | 105    | IO4    | IO3    | IO2    | IO1    | IO0    | 1111 1111        |

| IODIRB           | 01               | 107    | IO6    | IO5    | 104    | IO3    | IO2    | IO1    | IO0    | 1111 1111        |

| IPOLA            | 02               | IP7    | IP6    | IP5    | IP4    | IP3    | IP2    | IP1    | IP0    | 0000 0000        |

| IPOLB            | 03               | IP7    | IP6    | IP5    | IP4    | IP3    | IP2    | IP1    | IP0    | 0000 0000        |

| GPINTENA         | 04               | GPINT7 | GPINT6 | GPINT5 | GPINT4 | GPINT3 | GPINT2 | GPINT1 | GPINT0 | 0000 0000        |

| GPINTENB         | 05               | GPINT7 | GPINT6 | GPINT5 | GPINT4 | GPINT3 | GPINT2 | GPINT1 | GPINT0 | 0000 0000        |

| GPPUA            | 0C               | PU7    | PU6    | PU5    | PU4    | PU3    | PU2    | PU1    | PU0    | 0000 0000        |

| GPPUB            | 0D               | PU7    | PU6    | PU5    | PU4    | PU3    | PU2    | PU1    | PU0    | 0000 0000        |

| GPIOA            | 12               | GP7    | GP6    | GP5    | GP4    | GP3    | GP2    | GP1    | GP0    | 0000 0000        |

| GPIOB            | 13               | GP7    | GP6    | GP5    | GP4    | GP3    | GP2    | GP1    | GP0    | 0000 0000        |

| OLATA            | 14               | OL7    | OL6    | OL5    | OL4    | OL3    | OL2    | OL1    | OL0    | 0000 0000        |

| OLATB            | 15               | OL7    | OL6    | OL5    | OL4    | OL3    | OL2    | OL1    | OL0    | 0000 0000        |

#### 3.5 Configuration and Control Registers

There are 21 registers associated with the MCP23X17, as shown in Tables 3-4 and 3-5. The two tables show the register mapping with the two BANK bit values. Ten registers are associated with PORTA and ten are

associated with PORTB. One register (IOCON) is shared between the two ports. The PORTA registers are identical to the PORTB registers, therefore, they will be referred to without differentiating between the port designation (i.e., they will not have the "A" or "B" designator assigned) in the register tables.

| Register<br>Name | Address<br>(hex) | bit 7  | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  | POR/RST<br>value |

|------------------|------------------|--------|--------|--------|--------|--------|--------|--------|--------|------------------|

| IODIRA           | 00               | 107    | IO6    | IO5    | IO4    | IO3    | IO2    | IO1    | IO0    | 1111 1111        |

| IPOLA            | 01               | IP7    | IP6    | IP5    | IP4    | IP3    | IP2    | IP1    | IP0    | 0000 0000        |

| GPINTENA         | 02               | GPINT7 | GPINT6 | GPINT5 | GPINT4 | GPINT3 | GPINT2 | GPINT1 | GPINT0 | 0000 0000        |

| DEFVALA          | 03               | DEF7   | DEF6   | DEF5   | DEF4   | DEF3   | DEF2   | DEF1   | DEF0   | 0000 0000        |

| INTCONA          | 04               | IOC7   | IOC6   | IOC5   | IOC4   | IOC3   | IOC2   | IOC1   | IOC0   | 0000 0000        |

| IOCON            | 05               | BANK   | MIRROR | SEQOP  | DISSLW | HAEN   | ODR    | INTPOL |        | 0000 0000        |

| GPPUA            | 06               | PU7    | PU6    | PU5    | PU4    | PU3    | PU2    | PU1    | PU0    | 0000 0000        |

| INTFA            | 07               | INT7   | INT6   | INT5   | INT4   | INT3   | INT2   | INT1   | INTO   | 0000 0000        |

| INTCAPA          | 08               | ICP7   | ICP6   | ICP5   | ICP4   | ICP3   | ICP2   | ICP1   | ICP0   | 0000 0000        |

| GPIOA            | 09               | GP7    | GP6    | GP5    | GP4    | GP3    | GP2    | GP1    | GP0    | 0000 0000        |

| OLATA            | 0A               | OL7    | OL6    | OL5    | OL4    | OL3    | OL2    | OL1    | OL0    | 0000 0000        |

| IODIRB           | 10               | 107    | IO6    | IO5    | IO4    | IO3    | IO2    | IO1    | IO0    | 1111 1111        |

| IPOLB            | 11               | IP7    | IP6    | IP5    | IP4    | IP3    | IP2    | IP1    | IP0    | 0000 0000        |

| GPINTENB         | 12               | GPINT7 | GPINT6 | GPINT5 | GPINT4 | GPINT3 | GPINT2 | GPINT1 | GPINT0 | 0000 0000        |

| DEFVALB          | 13               | DEF7   | DEF6   | DEF5   | DEF4   | DEF3   | DEF2   | DEF1   | DEF0   | 0000 0000        |

| INTCONB          | 14               | IOC7   | IOC6   | IOC5   | IOC4   | IOC3   | IOC2   | IOC1   | IOC0   | 0000 0000        |

| IOCON            | 15               | BANK   | MIRROR | SEQOP  | DISSLW | HAEN   | ODR    | INTPOL | —      | 0000 0000        |

| GPPUB            | 16               | PU7    | PU6    | PU5    | PU4    | PU3    | PU2    | PU1    | PU0    | 0000 0000        |

| INTFB            | 17               | INT7   | INT6   | INT5   | INT4   | INT3   | INT2   | INT1   | INTO   | 0000 0000        |

| INTCAPB          | 18               | ICP7   | ICP6   | ICP5   | ICP4   | ICP3   | ICP2   | ICP1   | ICP0   | 0000 0000        |

| GPIOB            | 19               | GP7    | GP6    | GP5    | GP4    | GP3    | GP2    | GP1    | GP0    | 0000 0000        |

| OLATB            | 1A               | OL7    | OL6    | OL5    | OL4    | OL3    | OL2    | OL1    | OL0    | 0000 0000        |

TABLE 3-4:CONTROL REGISTER SUMMARY (IOCON.BANK = 1)

#### TABLE 3-5: CONTROL REGISTER SUMMARY (IOCON.BANK = 0)

| Register<br>Name | Address<br>(hex) | bit 7  | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  | POR/RST<br>value |

|------------------|------------------|--------|--------|--------|--------|--------|--------|--------|--------|------------------|

| IODIRA           | 00               | 107    | IO6    | IO5    | IO4    | IO3    | 102    | IO1    | IO0    | 1111 1111        |

| IODIRB           | 01               | 107    | IO6    | IO5    | IO4    | IO3    | IO2    | IO1    | IO0    | 1111 1111        |

| IPOLA            | 02               | IP7    | IP6    | IP5    | IP4    | IP3    | IP2    | IP1    | IP0    | 0000 0000        |

| IPOLB            | 03               | IP7    | IP6    | IP5    | IP4    | IP3    | IP2    | IP1    | IP0    | 0000 0000        |

| GPINTENA         | 04               | GPINT7 | GPINT6 | GPINT5 | GPINT4 | GPINT3 | GPINT2 | GPINT1 | GPINT0 | 0000 0000        |

| GPINTENB         | 05               | GPINT7 | GPINT6 | GPINT5 | GPINT4 | GPINT3 | GPINT2 | GPINT1 | GPINT0 | 0000 0000        |

| DEFVALA          | 06               | DEF7   | DEF6   | DEF5   | DEF4   | DEF3   | DEF2   | DEF1   | DEF0   | 0000 0000        |

| DEFVALB          | 07               | DEF7   | DEF6   | DEF5   | DEF4   | DEF3   | DEF2   | DEF1   | DEF0   | 0000 0000        |

| INTCONA          | 08               | IOC7   | IOC6   | IOC5   | IOC4   | IOC3   | IOC2   | IOC1   | IOC0   | 0000 0000        |

| INTCONB          | 09               | IOC7   | IOC6   | IOC5   | IOC4   | IOC3   | IOC2   | IOC1   | IOC0   | 0000 0000        |

| IOCON            | 0A               | BANK   | MIRROR | SEQOP  | DISSLW | HAEN   | ODR    | INTPOL | —      | 0000 0000        |

| IOCON            | 0B               | BANK   | MIRROR | SEQOP  | DISSLW | HAEN   | ODR    | INTPOL | —      | 0000 0000        |

| GPPUA            | 0C               | PU7    | PU6    | PU5    | PU4    | PU3    | PU2    | PU1    | PU0    | 0000 0000        |

| GPPUB            | 0D               | PU7    | PU6    | PU5    | PU4    | PU3    | PU2    | PU1    | PU0    | 0000 0000        |

© 2005-2016 Microchip Technology Inc.

|                  |                  |       |       |       | •     |       | , ,   |       | ,     |                  |

|------------------|------------------|-------|-------|-------|-------|-------|-------|-------|-------|------------------|

| Register<br>Name | Address<br>(hex) | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | POR/RST<br>value |

| INTFA            | 0E               | INT7  | INT6  | INT5  | INT4  | INT3  | INT2  | INT1  | INTO  | 0000 0000        |

| INTFB            | 0F               | INT7  | INT6  | INT5  | INT4  | INT3  | INT2  | INT1  | INTO  | 0000 0000        |

| INTCAPA          | 10               | ICP7  | ICP6  | ICP5  | ICP4  | ICP3  | ICP2  | ICP1  | ICP0  | 0000 0000        |

| INTCAPB          | 11               | ICP7  | ICP6  | ICP5  | ICP4  | ICP3  | ICP2  | ICP1  | ICP0  | 0000 0000        |

| GPIOA            | 12               | GP7   | GP6   | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | 0000 0000        |

| GPIOB            | 13               | GP7   | GP6   | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | 0000 0000        |

| OLATA            | 14               | OL7   | OL6   | OL5   | OL4   | OL3   | OL2   | OL1   | OL0   | 0000 0000        |

| OLATB            | 15               | OL7   | OL6   | OL5   | OL4   | OL3   | OL2   | OL1   | OL0   | 0000 0000        |

#### TABLE 3-5: CONTROL REGISTER SUMMARY (IOCON.BANK = 0) (CONTINUED)

#### 3.5.1 I/O DIRECTION REGISTER

Controls the direction of the data I/O.

When a bit is set, the corresponding pin becomes an input. When a bit is clear, the corresponding pin becomes an output.

#### REGISTER 3-1: IODIR: I/O DIRECTION REGISTER (ADDR 0x00)

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 107   | IO6   | IO5   | IO4   | IO3   | IO2   | IO1   | IO0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 IO<7:0>: Controls the direction of data I/O <7:0>

1 = Pin is configured as an input.

0 = Pin is configured as an output.

#### 3.5.2 INPUT POLARITY REGISTER

This register allows the user to configure the polarity on the corresponding GPIO port bits.

If a bit is set, the corresponding GPIO register bit will reflect the inverted value on the pin.

#### REGISTER 3-2: IPOL: INPUT POLARITY PORT REGISTER (ADDR 0x01)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IP7   | IP6   | IP5   | IP4   | IP3   | IP2   | IP1   | IP0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0

IP<7:0>: Controls the polarity inversion of the input pins <7:0>

1 = GPIO register bit reflects the opposite logic state of the input pin.

0 = GPIO register bit reflects the same logic state of the input pin.

#### 3.5.3 INTERRUPT-ON-CHANGE CONTROL REGISTER

The GPINTEN register controls the interrupt-on-change feature for each pin.

If a bit is set, the corresponding pin is enabled for interrupt-on-change. The DEFVAL and INTCON registers must also be configured if any pins are enabled for interrupt-on-change.

#### **REGISTER 3-3:** GPINTEN: INTERRUPT-ON-CHANGE PINS (ADDR 0x02) (Note 1)

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| GPINT7 | GPINT6 | GPINT5 | GPINT4 | GPINT3 | GPINT2 | GPINT1 | GPINT0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 **GPINT<7:0>:** General purpose I/O interrupt-on-change bits <7:0>

- 1 = Enables GPIO input pin for interrupt-on-change event.

- 0 = Disables GPIO input pin for interrupt-on-change event.

#### Note 1: Refer to INTCON.

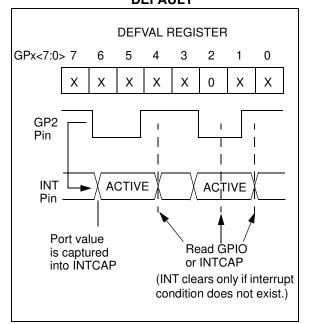

#### 3.5.4 DEFAULT COMPARE REGISTER FOR INTERRUPT-ON-CHANGE

The default comparison value is configured in the DEFVAL register. If enabled (via GPINTEN and INTCON) to compare against the DEFVAL register, an opposite value on the associated pin will cause an interrupt to occur.

#### REGISTER 3-4: DEFVAL: DEFAULT VALUE REGISTER (ADDR 0x03)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DEF7  | DEF6  | DEF5  | DEF4  | DEF3  | DEF2  | DEF1  | DEF0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

### bit 7-0 DEF<7:0>: Sets the compare value for pins configured for interrupt-on-change from defaults <7:0> (Note 1)

If the associated pin level is the opposite from the register bit, an interrupt occurs. (Note 2)

#### **Note 1:** Refer to INTCON.

2: Refer to INTCON and GPINTEN.

#### 3.5.5 INTERRUPT CONTROL REGISTER

The INTCON register controls how the associated pin value is compared for the interrupt-on-change feature. If a bit is set, the corresponding I/O pin is compared against the associated bit in the DEFVAL register. If a bit value is clear, the corresponding I/O pin is compared against the previous value.

#### REGISTER 3-5: INTCON: INTERRUPT-ON-CHANGE CONTROL REGISTER (ADDR 0x04) (Note 1)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOC7  | IOC6  | IOC5  | IOC4  | IOC3  | IOC2  | IOC1  | IOC0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-0 **IOC<7:0>:** Controls how the associated pin value is compared for interrupt-on-change <7:0>1 = Pin value is compared against the associated bit in the DEFVAL register.

0 = Pin value is compared against the previous pin value.

Note 1: Refer to INTCON and GPINTEN.

#### 3.5.6 CONFIGURATION REGISTER

The IOCON register contains several bits for configuring the device:

The BANK bit changes how the registers are mapped (see Tables 3-4 and 3-5 for more details).

- If BANK = 1, the registers associated with each port are segregated. Registers associated with PORTA are mapped from address 00h - 0Ah and registers associated with PORTB are mapped from 10h - 1Ah.

- If BANK = 0, the A/B registers are paired. For example, IODIRA is mapped to address 00h and IODIRB is mapped to the next address (address 01h). The mapping for all registers is from 00h -15h.

It is important to take care when changing the BANK bit as the address mapping changes after the byte is clocked into the device. The address pointer may point to an invalid location after the bit is modified.

For example, if the device is configured to automatically increment its internal Address Pointer, the following scenario would occur:

- BANK = 0

- Write 80h to address 0Ah (IOCON) to set the BANK bit

- Once the write completes, the internal address now points to 0Bh which is an invalid address when the BANK bit is set.

For this reason, when changing the BANK bit, it is advised to only perform byte writes to this register.

The **MIRROR** bit controls how the INTA and INTB pins function with respect to each other.

- When MIRROR = 1, the INTn pins are functionally OR'ed so that an interrupt on either port will cause both pins to activate.

- When MIRROR = 0, the INT pins are separated. Interrupt conditions on a port will cause its respective INT pin to activate.

The Sequential Operation (SEQOP) controls the incrementing function of the Address Pointer. If the address pointer is disabled, the Address Pointer does not automatically increment after each byte is clocked during a serial transfer. This feature is useful when it is desired to continuously poll (read) or modify (write) a register.

The Slew Rate (**DISSLW**) bit controls the slew rate function on the SDA pin. If enabled, the SDA slew rate will be controlled when driving from a high to low.

The Hardware Address Enable (**HAEN**) bit enables/disables hardware addressing on the MCP23S17 only. The address pins (A2, A1 and A0) must be externally biased, regardless of the HAEN bit value.

If enabled (HAEN = 1), the device's hardware address matches the address pins.

If disabled (HAEN = 0), the device's hardware address is A2 = A1 = A0 = 0.

The Open-Drain (**ODR**) control bit enables/disables the INT pin for open-drain configuration. Setting this bit overrides the INTPOL bit.

The Interrupt Polarity (**INTPOL**) sets the polarity of the INT pin. This bit is functional only when the ODR bit is cleared, configuring the INT pin as active push-pull.

#### REGISTER 3-6: IOCON: I/O EXPANDER CONFIGURATION REGISTER (ADDR 0x05)

| R/W-0 | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0  | U-0   |

|-------|--------|-------|--------|-------|-------|--------|-------|

| BANK  | MIRROR | SEQOP | DISSLW | HAEN  | ODR   | INTPOL | —     |

| bit 7 |        |       |        |       |       |        | bit 0 |

| Legend:      |                                            |                                                                                                |                                                |                    |

|--------------|--------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------|

| R = Readab   | ole bit                                    | W = Writable bit                                                                               | U = Unimplemented bit,                         | , read as '0'      |

| -n = Value a | at POR                                     | '1' = Bit is set                                                                               | '0' = Bit is cleared                           | x = Bit is unknown |

| bit 7        |                                            | ontrols how the registers are                                                                  | e addressed<br>h port are separated into diffe | erent banks.       |

| bit 6        | 0 = The re<br><b>MIRROR:</b><br>1 = The IN | egisters are in the same ban<br>INT Pins Mirror bit<br>NT pins are internally connect          | k (addresses are sequential).<br>cted          |                    |

| bit 5        | SEQOP: Sequ                                | Sequential Operation mode<br>ential operation disabled, ac<br>ential operation enabled, ad     | Idress pointer does not increr                 | ment.              |

| bit 4        | 1 = Slew                                   | Slew Rate control bit for SD<br>rate disabled<br>rate enabled                                  | A output                                       |                    |

| bit 3        | 1 = Enab                                   | ardware Address Enable bit<br>les the MCP23S17 address<br>bles the MCP23S17 address            | pins.                                          |                    |

| bit 2        | 1 = Open                                   | nfigures the INT pin as an op<br>-drain output (overrides the<br>e driver output (INTPOL bit s | INTPOL bit.)                                   |                    |

| bit 1        | <b>INTPOL:</b><br>1 = Active<br>0 = Active |                                                                                                | ne INT output pin                              |                    |

| bit 0        | Unimpler                                   | nented: Read as '0'                                                                            |                                                |                    |

Note 1: Address pins are always enabled on the MCP23017.

#### 3.5.7 PULL-UP RESISTOR CONFIGURATION REGISTER

The GPPU register controls the pull-up resistors for the port pins. If a bit is set and the corresponding pin is configured as an input, the corresponding port pin is internally pulled up with a 100 k $\Omega$  resistor.

#### REGISTER 3-7: GPPU: GPIO PULL-UP RESISTOR REGISTER (ADDR 0x06)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PU7   | PU6   | PU5   | PU4   | PU3   | PU2   | PU1   | PU0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### Legend:

| =ogona:           |                                  |                      |                       |  |  |

|-------------------|----------------------------------|----------------------|-----------------------|--|--|

| R = Readable bit  | W = Writable bit U = Unimplement |                      | nted bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set                 | '0' = Bit is cleared | x = Bit is unknown    |  |  |

bit 7-0

- **PU<7:0>** Controls the weak pull-up resistors on each pin (when configured as an input)

- 1 = Pull-up enabled

- 0 = Pull-up disabled

#### 3.5.8 INTERRUPT FLAG REGISTER

The INTF register reflects the interrupt condition on the port pins of any pin that is enabled for interrupts via the GPINTEN register. A set bit indicates that the associated pin caused the interrupt.

This register is read-only. Writes to this register will be ignored.