Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 2.7V 4-Channel/8-Channel 10-Bit A/D Converters with SPI Serial Interface

#### **Features**

- · 10-bit resolution

- ± 1 LSB max DNL

- ± 1 LSB max INL

- · 4 (MCP3004) or 8 (MCP3008) input channels

- Analog inputs programmable as single-ended or pseudo-differential pairs

- · On-chip sample and hold

- · SPI serial interface (modes 0,0 and 1,1)

- Single supply operation: 2.7V 5.5V

- 200 ksps max. sampling rate at V<sub>DD</sub> = 5V

- 75 ksps max. sampling rate at V<sub>DD</sub> = 2.7V

- · Low power CMOS technology

- 5 nA typical standby current, 2 μA max.

- 500 µA max. active current at 5V

- Industrial temp range: -40°C to +85°C

- · Available in PDIP, SOIC and TSSOP packages

#### **Applications**

- · Sensor Interface

- · Process Control

- · Data Acquisition

- · Battery Operated Systems

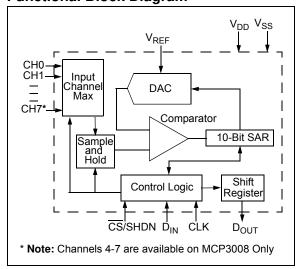

#### **Functional Block Diagram**

#### **Description**

The Microchip Technology Inc. MCP3004/3008 devices are successive approximation 10-bit Analogto-Digital (A/D) converters with on-board sample and hold circuitry. The MCP3004 is programmable to provide two pseudo-differential input pairs or four single-ended inputs. The MCP3008 is programmable to provide four pseudo-differential input pairs or eight single-ended inputs. Differential Nonlinearity (DNL) and Integral Nonlinearity (INL) are specified at ±1 LSB. Communication with the devices is accomplished using a simple serial interface compatible with the SPI protocol. The devices are capable of conversion rates of up to 200 ksps. The MCP3004/3008 devices operate over a broad voltage range (2.7V - 5.5V). Low-current design permits operation with typical standby currents of only 5 nA and typical active currents of 320 µA. The MCP3004 is offered in 14-pin PDIP. 150 mil SOIC and TSSOP packages, while the MCP3008 is offered in 16pin PDIP and SOIC packages.

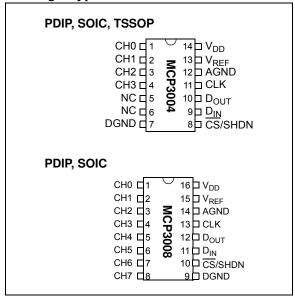

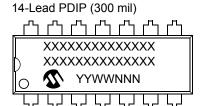

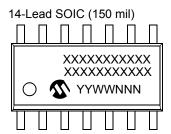

#### **Package Types**

**NOTES:**

### 1.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| V <sub>DD</sub> 7.0V                                             |

|------------------------------------------------------------------|

| All Inputs and Outputs w.r.t. $V_{SS}$ – 0.6V to $V_{DD}$ + 0.6V |

| Storage Temperature65°C to +150°C                                |

| Ambient temperature with power applied65°C to +150°C             |

| Soldering temperature of leads (10 seconds)+300°C                |

| ESD Protection On All Pins (HBM)≥ 4 kV                           |

† Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL SPECIFICATIONS**

**Electrical Characteristics:** Unless otherwise noted, all parameters apply at  $V_{DD}$  = 5V,  $V_{REF}$  = 5V,  $V_{AEF}$  = 5V,  $V_{AEF}$  = 200 ksps and  $V_{AEF}$  = 18\* $V_{A$

| Parameter                                               | Sym                 | Min                  | Тур          | Max                   | Units           | Conditions                                           |  |

|---------------------------------------------------------|---------------------|----------------------|--------------|-----------------------|-----------------|------------------------------------------------------|--|

| Conversion Rate                                         |                     |                      |              |                       |                 |                                                      |  |

| Conversion Time                                         | t <sub>CONV</sub>   | _                    | _            | 10                    | clock<br>cycles |                                                      |  |

| Analog Input Sample Time                                | t <sub>SAMPLE</sub> |                      | 1.5          |                       | clock<br>cycles |                                                      |  |

| Throughput Rate                                         | f <sub>SAMPLE</sub> |                      |              | 200<br>75             | ksps<br>ksps    | $V_{DD} = V_{REF} = 5V$<br>$V_{DD} = V_{REF} = 2.7V$ |  |

| DC Accuracy                                             |                     |                      |              |                       |                 |                                                      |  |

| Resolution                                              |                     |                      | 10           |                       | bits            |                                                      |  |

| Integral Nonlinearity                                   | INL                 | _                    | ±0.5         | ±1                    | LSB             |                                                      |  |

| Differential Nonlinearity                               | DNL                 | _                    | ±0.25        | ±1                    | LSB             | No missing codes over temperature                    |  |

| Offset Error                                            |                     | _                    | _            | ±1.5                  | LSB             |                                                      |  |

| Gain Error                                              |                     | _                    |              | ±1.0                  | LSB             |                                                      |  |

| Dynamic Performance                                     |                     |                      |              |                       |                 |                                                      |  |

| Total Harmonic Distortion                               |                     | _                    | -76          |                       | dB              | V <sub>IN</sub> = 0.1V to 4.9V@1 kHz                 |  |

| Signal-to-Noise and Distortion (SINAD)                  |                     | _                    | 61           |                       | dB              | V <sub>IN</sub> = 0.1V to 4.9V@1 kHz                 |  |

| Spurious Free Dynamic Range                             |                     | _                    | 78           |                       | dB              | V <sub>IN</sub> = 0.1V to 4.9V@1 kHz                 |  |

| Reference Input                                         |                     |                      |              |                       |                 |                                                      |  |

| Voltage Range                                           |                     | 0.25                 |              | $V_{DD}$              | >               | Note 2                                               |  |

| Current Drain                                           |                     | _                    | 100<br>0.001 | 150<br>3              | μA<br>μA        | $\overline{\text{CS}} = V_{\text{DD}} = 5V$          |  |

| Analog Inputs                                           |                     |                      |              |                       |                 |                                                      |  |

| Input Voltage Range for CH0 or CH1 in Single-Ended Mode |                     | V <sub>SS</sub>      | _            | V <sub>REF</sub>      | V               |                                                      |  |

| Input Voltage Range for IN+ in pseudo-differential mode |                     | IN-                  | _            | V <sub>REF</sub> +IN- |                 |                                                      |  |

| Input Voltage Range for IN- in pseudo-differential mode |                     | V <sub>SS</sub> -100 | _            | V <sub>SS</sub> +100  | mV              |                                                      |  |

- Note 1: This parameter is established by characterization and not 100% tested.

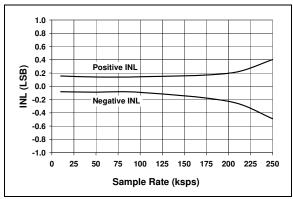

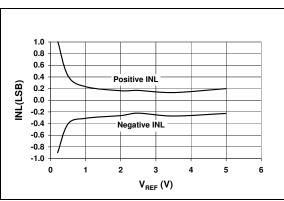

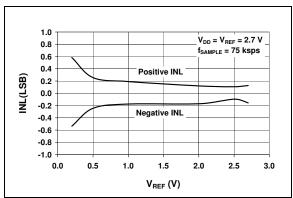

- **2:** See graphs that relate linearity performance to V<sub>REF</sub> levels.

- 3: Because the sample cap will eventually lose charge, effective clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures. See **Section 6.2 "Maintaining Minimum Clock Speed"**, "Maintaining Minimum Clock Speed", for more information.

#### **ELECTRICAL SPECIFICATIONS (CONTINUED)**

**Electrical Characteristics:** Unless otherwise noted, all parameters apply at  $V_{DD}$  = 5V,  $V_{REF}$  = 5V,  $V_{AEF}$  = 5V,  $V_{AEF}$  = 200 ksps and  $V_{AEF}$  = 18\* $V_{AEF}$  = 18\* $V_{AEF}$  = 18. Unless otherwise noted, typical values apply for  $V_{AEF}$  = 5V,  $V_{AEF}$  = 425°C.

| $V_{DD} = 5V$ , $I_A = +25$ °C.         |                                       |                     |             |                     |            |                                                                                    |  |

|-----------------------------------------|---------------------------------------|---------------------|-------------|---------------------|------------|------------------------------------------------------------------------------------|--|

| Parameter                               | Sym                                   | Min                 | Тур         | Max                 | Units      | Conditions                                                                         |  |

| Leakage Current                         |                                       | _                   | 0.001       | ±1                  | μA         |                                                                                    |  |

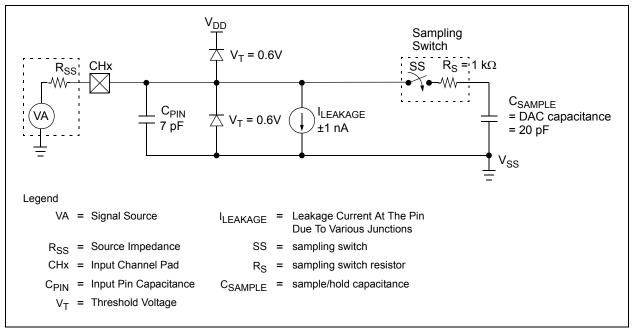

| Switch Resistance                       |                                       | _                   | 1000        | _                   | Ω          | See Figure 4-1                                                                     |  |

| Sample Capacitor                        |                                       | _                   | 20          | _                   | pF         | See Figure 4-1                                                                     |  |

| Digital Input/Output                    |                                       |                     |             |                     |            |                                                                                    |  |

| Data Coding Format                      |                                       | St                  | traight Bin | ary                 |            |                                                                                    |  |

| High Level Input Voltage                | $V_{IH}$                              | 0.7 V <sub>DD</sub> | _           | _                   | V          |                                                                                    |  |

| Low Level Input Voltage                 | $V_{IL}$                              |                     | _           | 0.3 V <sub>DD</sub> | V          |                                                                                    |  |

| High Level Output Voltage               | V <sub>OH</sub>                       | 4.1                 | _           | _                   | V          | I <sub>OH</sub> = -1 mA, V <sub>DD</sub> = 4.5V                                    |  |

| Low Level Output Voltage                | V <sub>OL</sub>                       | _                   | _           | 0.4                 | V          | I <sub>OL</sub> = 1 mA, V <sub>DD</sub> = 4.5V                                     |  |

| Input Leakage Current                   | ILI                                   | -10                 | _           | 10                  | μA         | $V_{IN} = V_{SS}$ or $V_{DD}$                                                      |  |

| Output Leakage Current                  | $I_{LO}$                              | -10                 |             | 10                  | μA         | $V_{OUT} = V_{SS}$ or $V_{DD}$                                                     |  |

| Pin Capacitance<br>(All Inputs/Outputs) | C <sub>IN</sub> ,<br>C <sub>OUT</sub> |                     | 1           | 10                  | pF         | V <sub>DD</sub> = 5.0V ( <b>Note 1</b> )<br>T <sub>A</sub> = 25°C, f = 1 MHz       |  |

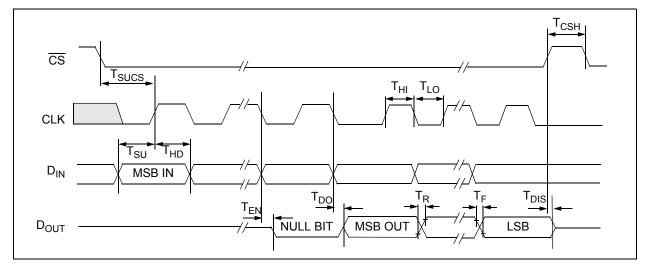

| Timing Parameters                       | 9001                                  |                     |             |                     |            | A 20 0,1 1 mile                                                                    |  |

| Clock Frequency                         | f <sub>CLK</sub>                      | _                   | _           | 3.6<br>1.35         | MHz<br>MHz | V <sub>DD</sub> = 5V ( <b>Note 3</b> )<br>V <sub>DD</sub> = 2.7V ( <b>Note 3</b> ) |  |

| Clock High Time                         | t <sub>HI</sub>                       | 125                 | _           | _                   | ns         |                                                                                    |  |

| Clock Low Time                          | t <sub>LO</sub>                       | 125                 | _           | _                   | ns         |                                                                                    |  |

| CS Fall To First Rising CLK Edge        | t <sub>SUCS</sub>                     | 100                 | _           | _                   | ns         |                                                                                    |  |

| CS Fall To Falling CLK Edge             | t <sub>CSD</sub>                      | _                   | _           | 0                   | ns         |                                                                                    |  |

| Data Input Setup Time                   | t <sub>SU</sub>                       | 50                  | _           | _                   | ns         |                                                                                    |  |

| Data Input Hold Time                    | t <sub>HD</sub>                       | 50                  | _           | _                   | ns         |                                                                                    |  |

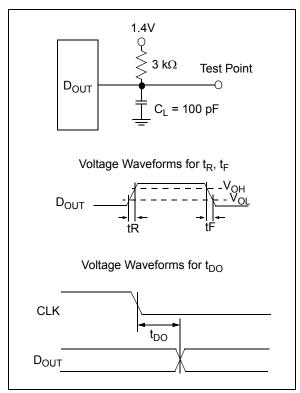

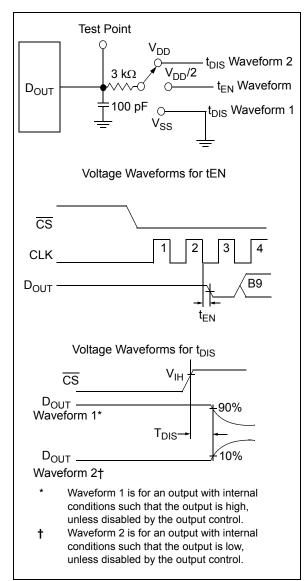

| CLK Fall To Output Data Valid           | t <sub>DO</sub>                       | _                   | _           | 125<br>200          | ns<br>ns   | V <sub>DD</sub> = 5V, See Figure 1-2<br>V <sub>DD</sub> = 2.7V, See Figure 1-2     |  |

| CLK Fall To Output Enable               | t <sub>EN</sub>                       | _                   | _           | 125<br>200          | ns<br>ns   | V <sub>DD</sub> = 5V, See Figure 1-2<br>V <sub>DD</sub> = 2.7V, See Figure 1-2     |  |

| CS Rise To Output Disable               | t <sub>DIS</sub>                      | _                   | _           | 100                 | ns         | See Test Circuits, Figure 1-2                                                      |  |

| CS Disable Time                         | t <sub>CSH</sub>                      | 270                 | _           | _                   | ns         | -                                                                                  |  |

| D <sub>OUT</sub> Rise Time              | t <sub>R</sub>                        | _                   | _           | 100                 | ns         | See Test Circuits, Figure 1-2 (Note 1)                                             |  |

| D <sub>OUT</sub> Fall Time              | t <sub>F</sub>                        | _                   |             | 100                 | ns         | See Test Circuits, Figure 1-2 (Note 1)                                             |  |

Note 1: This parameter is established by characterization and not 100% tested.

**<sup>2:</sup>** See graphs that relate linearity performance to  $V_{\mbox{\scriptsize REF}}$  levels.

<sup>3:</sup> Because the sample cap will eventually lose charge, effective clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures. See **Section 6.2 "Maintaining Minimum Clock Speed"**, "Maintaining Minimum Clock Speed", for more information.

#### **ELECTRICAL SPECIFICATIONS (CONTINUED)**

**Electrical Characteristics:** Unless otherwise noted, all parameters apply at  $V_{DD}$  = 5V,  $V_{REF}$  = 5V,  $T_A$  = -40°C to +85°C,  $f_{SAMPLE}$  = 200 ksps and  $f_{CLK}$  = 18\* $f_{SAMPLE}$ . Unless otherwise noted, typical values apply for  $V_{DD}$  = 5V,  $T_A$  = +25°C.

| Parameter          | Sym              | Min | Тур        | Max | Units | Conditions                                                                                |

|--------------------|------------------|-----|------------|-----|-------|-------------------------------------------------------------------------------------------|

| Power Requirements |                  |     |            |     |       |                                                                                           |

| Operating Voltage  | $V_{DD}$         | 2.7 | _          | 5.5 | V     |                                                                                           |

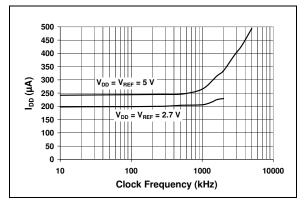

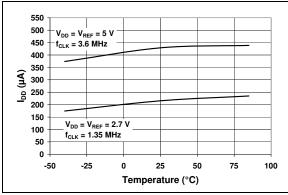

| Operating Current  | I <sub>DD</sub>  | _   | 425<br>225 | 550 | μΑ    | $V_{DD} = V_{REF} = 5V,$ $D_{OUT}$ unloaded $V_{DD} = V_{REF} = 2.7V,$ $D_{OUT}$ unloaded |

| Standby Current    | I <sub>DDS</sub> | _   | 0.005      | 2   | μΑ    | <u>CS</u> = V <sub>DD</sub> = 5.0V                                                        |

- **Note 1:** This parameter is established by characterization and not 100% tested.

- **2:** See graphs that relate linearity performance to  $V_{REF}$  levels.

- 3: Because the sample cap will eventually lose charge, effective clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures. See Section 6.2 "Maintaining Minimum Clock Speed", "Maintaining Minimum Clock Speed", for more information.

#### **TEMPERATURE CHARACTERISTICS**

| Electrical Specifications: Unless otherwise indicated, V <sub>DD</sub> = +2.7V to +5.5V, V <sub>SS</sub> = GND. |                |     |     |      |       |            |  |  |

|-----------------------------------------------------------------------------------------------------------------|----------------|-----|-----|------|-------|------------|--|--|

| Parameters                                                                                                      | Sym            | Min | Тур | Max  | Units | Conditions |  |  |

| Temperature Ranges                                                                                              |                |     |     |      |       |            |  |  |

| Specified Temperature Range                                                                                     | T <sub>A</sub> | -40 | _   | +85  | °C    |            |  |  |

| Operating Temperature Range                                                                                     | T <sub>A</sub> | -40 | _   | +85  | °C    |            |  |  |

| Storage Temperature Range                                                                                       | T <sub>A</sub> | -65 | _   | +150 | °C    |            |  |  |

| Thermal Package Resistances                                                                                     |                |     |     |      |       |            |  |  |

| Thermal Resistance, 14L-PDIP                                                                                    | $\theta_{JA}$  | _   | 70  | _    | °C/W  |            |  |  |

| Thermal Resistance, 14L-SOIC                                                                                    | $\theta_{JA}$  | _   | 108 | _    | °C/W  |            |  |  |

| Thermal Resistance, 14L-TSSOP                                                                                   | $\theta_{JA}$  | _   | 100 | _    | °C/W  |            |  |  |

| Thermal Resistance, 16L-PDIP                                                                                    | $\theta_{JA}$  | _   | 70  | _    | °C/W  |            |  |  |

| Thermal Resistance, 16L-SOIC                                                                                    | $\theta_{JA}$  | _   | 90  | _    | °C/W  |            |  |  |

FIGURE 1-1: Serial Interface Timing.

**FIGURE 1-2:** Load Circuit for  $t_R$ ,  $t_F$ ,  $t_{DO}$ .

**FIGURE 1-3:** Load circuit for  $t_{DIS}$  and  $t_{EN}$ .

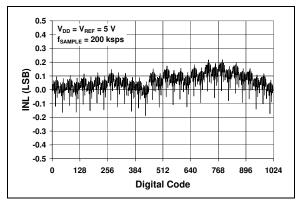

#### 2.0 TYPICAL PERFORMANCE CHARACTERISTICS

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

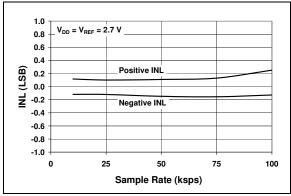

**FIGURE 2-1:** Integral Nonlinearity (INL) vs. Sample Rate.

**FIGURE 2-2:** Integral Nonlinearity (INL) vs. V<sub>REF</sub>

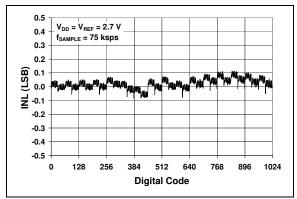

**FIGURE 2-3:** Integral Nonlinearity (INL) vs. Code (Representative Part).

**FIGURE 2-4:** Integral Nonlinearity (INL) vs. Sample Rate  $(V_{DD} = 2.7V)$ .

**FIGURE 2-5:** Integral Nonlinearity (INL) vs.  $V_{REF}$  ( $V_{DD}$  = 2.7V).

**FIGURE 2-6:** Integral Nonlinearity (INL) vs. Code (Representative Part,  $V_{DD} = 2.7V$ ).

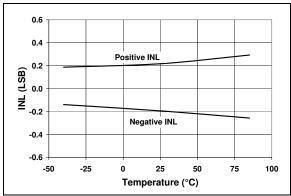

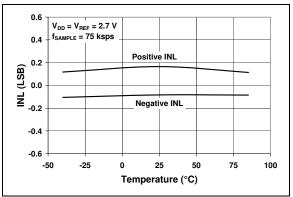

**FIGURE 2-7:** Integral Nonlinearity (INL) vs. Temperature.

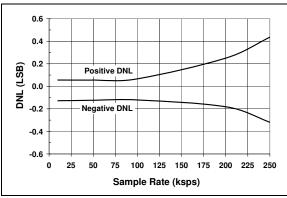

FIGURE 2-8: Differential Nonlinearity (DNL) vs. Sample Rate.

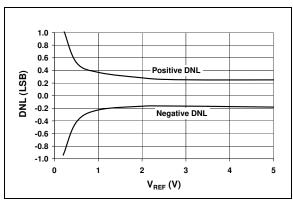

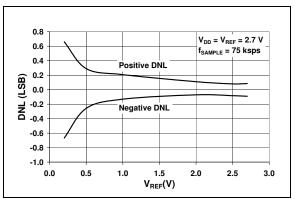

**FIGURE 2-9:** Differential Nonlinearity (DNL) vs.  $V_{REF}$

**FIGURE 2-10:** Integral Nonlinearity (INL) vs. Temperature  $(V_{DD} = 2.7V)$ .

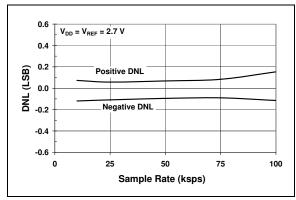

**FIGURE 2-11:** Differential Nonlinearity (DNL) vs. Sample Rate  $(V_{DD} = 2.7V)$ .

**FIGURE 2-12:** Differential Nonlinearity (DNL) vs.  $V_{REF}$  ( $V_{DD} = 2.7V$ ).

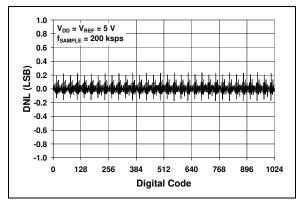

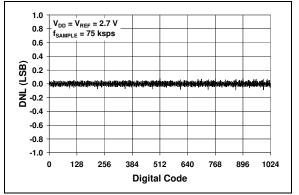

**FIGURE 2-13:** Differential Nonlinearity (DNL) vs. Code (Representative Part).

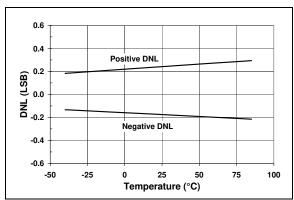

**FIGURE 2-14:** Differential Nonlinearity (DNL) vs. Temperature.

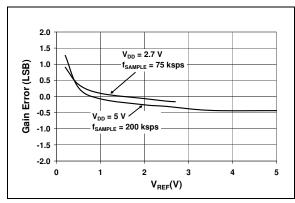

FIGURE 2-15: Gain Error vs. V<sub>REF</sub>

**FIGURE 2-16:** Differential Nonlinearity (DNL) vs. Code (Representative Part,  $V_{DD} = 2.7V$ ).

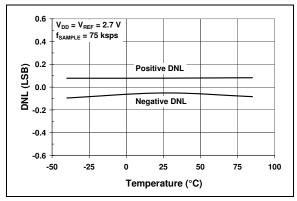

**FIGURE 2-17:** Differential Nonlinearity (DNL) vs. Temperature ( $V_{DD} = 2.7V$ ).

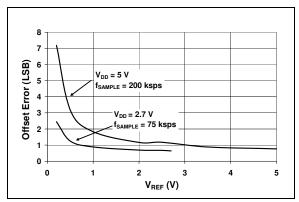

FIGURE 2-18: Offset Error vs. V<sub>RFF</sub>

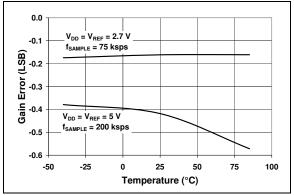

FIGURE 2-19: Gain Error vs. Temperature.

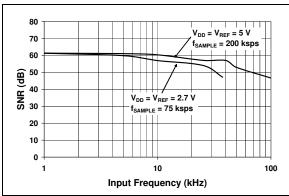

FIGURE 2-20: Signal-to-Noise (SNR) vs. Input Frequency.

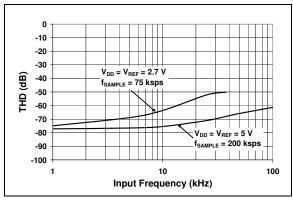

**FIGURE 2-21:** Total Harmonic Distortion (THD) vs. Input Frequency.

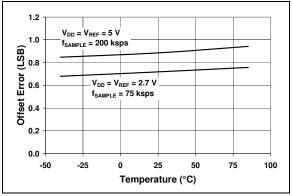

**FIGURE 2-22:** Offset Error vs. Temperature.

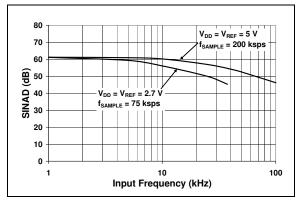

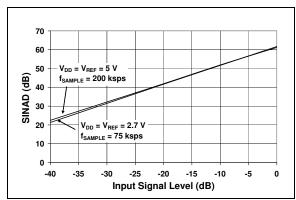

FIGURE 2-23: Signal-to-Noise and Distortion (SINAD) vs. Input Frequency.

FIGURE 2-24: Signal-to-Noise and Distortion (SINAD) vs. Input Signal Level.

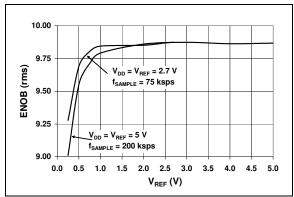

**FIGURE 2-25:** Effective Number of Bits (ENOB) vs.  $V_{RFF}$

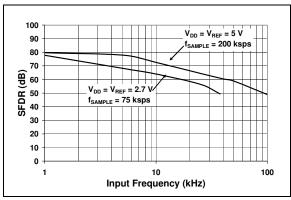

FIGURE 2-26: Spurious Free Dynamic Range (SFDR) vs. Input Frequency.

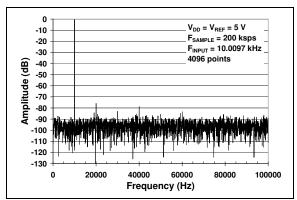

FIGURE 2-27: Frequency Spectrum of 10 kHz Input (Representative Part).

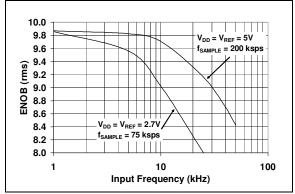

**FIGURE 2-28:** Effective Number of Bits (ENOB) vs. Input Frequency.

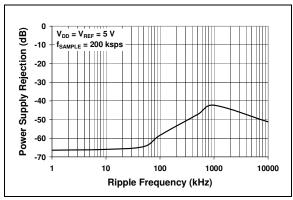

**FIGURE 2-29:** Power Supply Rejection (PSR) vs. Ripple Frequency.

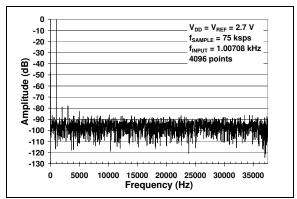

**FIGURE 2-30:** Frequency Spectrum of 1 kHz Input (Representative Part,  $V_{DD} = 2.7V$ ).

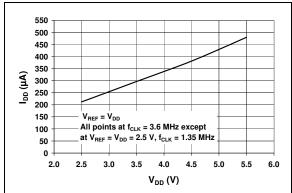

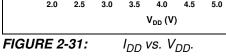

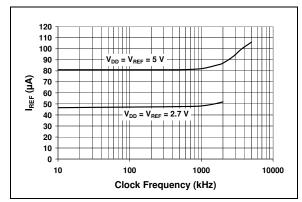

FIGURE 2-32:

I<sub>DD</sub> vs. Clock Frequency.

**FIGURE 2-33:**

I<sub>DD</sub> vs. Temperature.

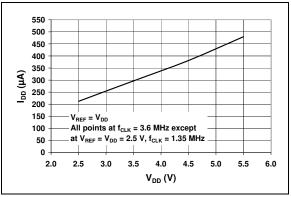

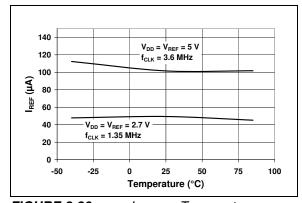

FIGURE 2-34:

$I_{REF}$  vs.  $V_{DD}$ .

**FIGURE 2-35:**

I<sub>REF</sub> vs. Clock Frequency.

**FIGURE 2-36:**

I<sub>REF</sub> vs. Temperature.

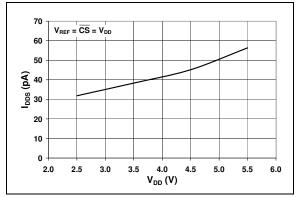

FIGURE 2-37:  $I_{DDS}$  vs.  $V_{DD}$ .

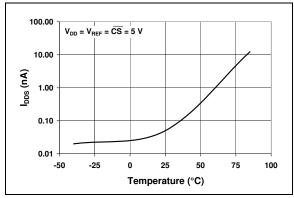

FIGURE 2-38: I<sub>DDS</sub> vs. Temperature.

**FIGURE 2-39:** Analog Input Leakage Current vs. Temperature.

**NOTES:**

#### 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1. Additional descriptions of the device pins follows.

TABLE 3-1: PIN FUNCTION TABLE

| MCP3004              | MCP3008    |                  |                            |  |

|----------------------|------------|------------------|----------------------------|--|

| PDIP, SOIC,<br>TSSOP | PDIP, SOIC | Symbol           | Description                |  |

| 1                    | 1          | CH0              | Analog Input               |  |

| 2                    | 2          | CH1              | Analog Input               |  |

| 3                    | 3          | CH2              | Analog Input               |  |

| 4                    | 4          | CH3              | Analog Input               |  |

| _                    | 5          | CH4              | Analog Input               |  |

| _                    | 6          | CH5              | Analog Input               |  |

| _                    | 7          | CH6              | Analog Input               |  |

| _                    | 8          | CH7              | Analog Input               |  |

| 7                    | 9          | DGND             | Digital Ground             |  |

| 8                    | 10         | CS/SHDN          | Chip Select/Shutdown Input |  |

| 9                    | 11         | D <sub>IN</sub>  | Serial Data In             |  |

| 10                   | 12         | D <sub>OUT</sub> | Serial Data Out            |  |

| 11                   | 13         | CLK              | Serial Clock               |  |

| 12                   | 14         | AGND             | Analog Ground              |  |

| 13                   | 15         | V <sub>REF</sub> | Reference Voltage Input    |  |

| 14                   | 16         | V <sub>DD</sub>  | +2.7V to 5.5V Power Supply |  |

| 5,6                  | _          | NC               | No Connection              |  |

#### 3.1 Digital Ground (DGND)

Digital ground connection to internal digital circuitry.

#### 3.2 Analog Ground (AGND)

Analog ground connection to internal analog circuitry.

#### 3.3 Analog inputs (CH0 - CH7)

Analog inputs for channels 0 - 7, respectively, for the multiplexed inputs. Each pair of channels can be programmed to be used as two independent channels in single-ended mode or as a single pseudo-differential input where one channel is IN+ and one channel is IN. See Section 4.1 "Analog Inputs", "Analog Inputs", and Section 5.0 "Serial Communication", "Serial Communication", for information on programming the channel configuration.

#### 3.4 Serial Clock (CLK)

The SPI clock pin is used to initiate a conversion and clock out each bit of the conversion as it takes place. See **Section 6.2 "Maintaining Minimum Clock Speed"**, "Maintaining Minimum Clock Speed", for constraints on clock speed.

#### 3.5 Serial Data Input (D<sub>IN</sub>)

The SPI port serial data input pin is used to load channel configuration data into the device.

#### 3.6 Serial Data Output (DOUT)

The SPI serial data output pin is used to shift out the results of the A/D conversion. Data will always change on the falling edge of each clock as the conversion takes place.

#### 3.7 Chip Select/Shutdown (CS/SHDN)

The  $\overline{\text{CS}}/\text{SHDN}$  pin is used to initiate communication with the device when pulled low. When pulled high, it will end a conversion and put the device in low-power standby. The  $\overline{\text{CS}}/\text{SHDN}$  pin must be pulled high between conversions.

**NOTES:**

#### 4.0 DEVICE OPERATION

The MCP3004/3008 A/D converters employ a conventional SAR architecture. With this architecture, a sample is acquired on an internal sample/hold capacitor for 1.5 clock cycles starting on the first rising edge of the serial clock once  $\overline{CS}$  has been pulled low. Following this sample time, the device uses the collected charge on the internal sample and hold capacitor to produce a serial 10-bit digital output code. Conversion rates of 100 ksps are possible on the MCP3004/3008. See Section 6.2 "Maintaining Minimum Clock Speed", "Maintaining Minimum Clock Speed", for information on minimum clock rates. Communication with the device is accomplished using a 4-wire SPI-compatible interface.

#### 4.1 Analog Inputs

The MCP3004/3008 devices offer the choice of using the analog input channels configured as single-ended inputs or pseudo-differential pairs. The MCP3004 can be configured to provide two pseudo-differential input pairs or four single-ended inputs. The MCP3008 can be configured to provide four pseudo-differential input pairs or eight single-ended inputs. Configuration is done as part of the serial command before each conversion begins. When used in the pseudodifferential mode, each channel pair (i.e., CH0 and CH1, CH2 and CH3 etc.) are programmed as the IN+ and IN- inputs as part of the command string transmitted to the device. The IN+ input can range from IN- to (V<sub>REF</sub> + IN-). The IN- input is limited to ±100 mV from the  $V_{SS}$  rail. The IN- input can be used to cancel small signal common-mode noise, which is present on both the IN+ and IN- inputs.

When operating in the pseudo-differential mode, if the voltage level of IN+ is equal to or less than IN-, the resultant code will be 000h. If the voltage at IN+ is equal to or greater than {[V\_{REF} + (IN-)] - 1 LSB}, then the output code will be 3FFh. If the voltage level at IN-is more than 1 LSB below V\_{SS}, the voltage level at the IN+ input will have to go below V\_{SS} to see the 000h output code. Conversely, if IN- is more than 1 LSB above V\_{SS}, the 3FFh code will not be seen unless the IN+ input level goes above  $V_{REF}$  level.

For the A/D converter to meet specification, the charge holding capacitor ( $C_{SAMPLE}$ ) must be given enough time to acquire a 10-bit accurate voltage level during the 1.5 clock cycle sampling period. The analog input model is shown in Figure 4-1.

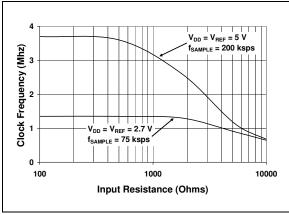

This diagram illustrates that the source impedance ( $R_S$ ) adds to the internal sampling switch ( $R_{SS}$ ) impedance, directly affecting the time that is required to charge the capacitor ( $C_{SAMPLE}$ ). Consequently, larger source impedances increase the offset, gain and integral linearity errors of the conversion (see Figure 4-2).

#### 4.2 Reference Input

For each device in the family, the reference input  $(V_{REF})$  determines the analog input voltage range. As the reference input is reduced, the LSB size is reduced accordingly.

#### **EQUATION 4-1: LSB SIZE CALCULATION**

$$LSB \ Size = \frac{V_{REF}}{1024}$$

The theoretical digital output code produced by the A/D converter is a function of the analog input signal and the reference input, as shown below.

### EQUATION 4-2: DIGITAL OUTPUT CODE CALCULATION

$$Digital\ Output\ Code\ =\ \frac{1024\times V_{IN}}{V_{REF}}$$

Where:

$V_{IN}$  = analog input voltage  $V_{REF}$  = analog input voltage

When using an external voltage reference device, the system designer should always refer to the manufacturer's recommendations for circuit layout. Any instability in the operation of the reference device will have a direct effect on the operation of the A/D converter.

FIGURE 4-1: Analog Input Model.

**FIGURE 4-2:** Maximum Clock Frequency vs. Input resistance (R<sub>S</sub>) to maintain less than a 0.1 LSB deviation in INL from nominal conditions.

#### 5.0 SERIAL COMMUNICATION

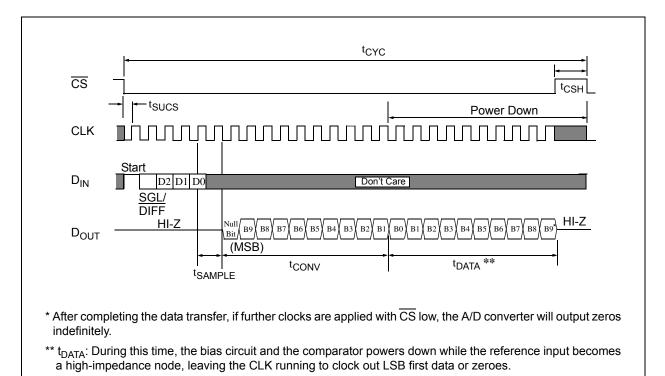

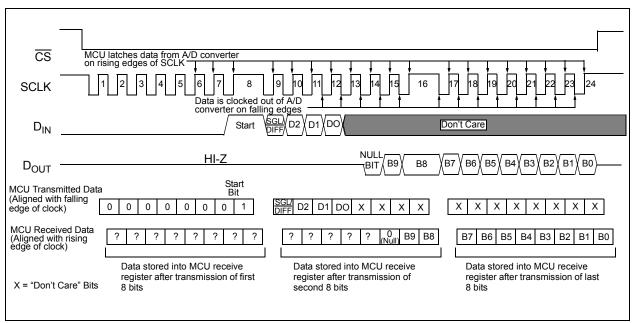

Communication with the MCP3004/3008 devices is accomplished using a standard SPI-compatible serial interface. Initiating communication with either device is done by bringing the CS line low (see Figure 5-1). If the device was powered up with the CS pin low, it must be brought high and back low to initiate communication. The first clock received with  $\overline{\text{CS}}$  low and D<sub>IN</sub> high will constitute a start bit. The SGL/DIFF bit follows the start bit and will determine if the conversion will be done using single-ended or differential input mode. The next three bits (D0, D1 and D2) are used to select the input channel configuration. Table 5-1 and Table 5-2 show the configuration bits for the MCP3004 and MCP3008. respectively. The device will begin to sample the analog input on the fourth rising edge of the clock after the start bit has been received. The sample period will end on the falling edge of the fifth clock following the start bit.

Once the D0 bit is input, one more clock is required to complete the sample and hold period (D $_{\text{IN}}$  is a "don't care" for this clock). On the falling edge of the next clock, the device will output a low null bit. The next 10 clocks will output the result of the conversion with MSB first, as shown in Figure 5-1. Data is always output from the device on the falling edge of the clock. If all 10 data bits have been transmitted and the device continues to receive clocks while the  $\overline{\text{CS}}$  is held low, the device will output the conversion result LSB first, as is shown in Figure 5-2. If more clocks are provided to the device while  $\overline{\text{CS}}$  is still low (after the LSB first data has been transmitted), the device will clock out zeros indefinitely.

If necessary, it is possible to bring CS low and clock in leading zeros on the  $D_{\rm IN}$  line before the start bit. This is often done when dealing with microcontroller-based SPI ports that must send 8 bits at a time. Refer to Section 6.1 "Using the MCP3004/3008 with Microcontroller (MCU) SPI Ports", "Using the MCP3004/3008 with Microcontroller (MCU) SPI Ports", for more details on using the MCP3004/3008 devices with hardware SPI ports.

TABLE 5-1: CONFIGURE BITS FOR THE MCP3004

|                          | Control Bit<br>Selections |    |    | Input         | Channel                |  |

|--------------------------|---------------------------|----|----|---------------|------------------------|--|

| Si <u>ngl</u> e/<br>Diff | D2*                       | D1 | D0 | Configuration | Selection              |  |

| 1                        | Χ                         | 0  | 0  | single-ended  | CH0                    |  |

| 1                        | Х                         | 0  | 1  | single-ended  | CH1                    |  |

| 1                        | Х                         | 1  | 0  | single-ended  | CH2                    |  |

| 1                        | Х                         | 1  | 1  | single-ended  | CH3                    |  |

| 0                        | Х                         | 0  | 0  | differential  | CH0 = IN+<br>CH1 = IN- |  |

| 0                        | Х                         | 0  | 1  | differential  | CH0 = IN-<br>CH1 = IN+ |  |

| 0                        | Х                         | 1  | 0  | differential  | CH2 = IN+<br>CH3 = IN- |  |

| 0                        | Х                         | 1  | 1  | differential  | CH2 = IN-<br>CH3 = IN+ |  |

<sup>\*</sup> D2 is "don't care" for MCP3004

TABLE 5-2: CONFIGURE BITS FOR THE MCP3008

|                          | ontrol | -  |    | Input         | Channel                |

|--------------------------|--------|----|----|---------------|------------------------|

| Si <u>ngl</u> e<br>/Diff | D2     | D1 | D0 | Configuration | Selection              |

| 1                        | 0      | 0  | 0  | single-ended  | CH0                    |

| 1                        | 0      | 0  | 1  | single-ended  | CH1                    |

| 1                        | 0      | 1  | 0  | single-ended  | CH2                    |

| 1                        | 0      | 1  | 1  | single-ended  | CH3                    |

| 1                        | 1      | 0  | 0  | single-ended  | CH4                    |

| 1                        | 1      | 0  | 1  | single-ended  | CH5                    |

| 1                        | 1      | 1  | 0  | single-ended  | CH6                    |

| 1                        | 1      | 1  | 1  | single-ended  | CH7                    |

| 0                        | 0      | 0  | 0  | differential  | CH0 = IN+<br>CH1 = IN- |

| 0                        | 0      | 0  | 1  | differential  | CH0 = IN-<br>CH1 = IN+ |

| 0                        | 0      | 1  | 0  | differential  | CH2 = IN+<br>CH3 = IN- |

| 0                        | 0      | 1  | 1  | differential  | CH2 = IN-<br>CH3 = IN+ |

| 0                        | 1      | 0  | 0  | differential  | CH4 = IN+<br>CH5 = IN- |

| 0                        | 1      | 0  | 1  | differential  | CH4 = IN-<br>CH5 = IN+ |

| 0                        | 1      | 1  | 0  | differential  | CH6 = IN+<br>CH7 = IN- |

| 0                        | 1      | 1  | 1  | differential  | CH6 = IN-<br>CH7 = IN+ |

- \* After completing the data transfer, if further clocks are applied with  $\overline{\text{CS}}$  low, the A/D converter will output LSB first data, then followed with zeros indefinitely. See Figure 5-2 below.

- \*\* t<sub>DATA</sub>: during this time, the bias current and the comparator powers down while the reference input becomes a high-impedance node.

FIGURE 5-1: Communication with the MCP3004 or MCP3008.

FIGURE 5-2: Communication with MCP3004 or MCP3008 in LSB First Format.

#### 6.0 APPLICATIONS INFORMATION

### 6.1 Using the MCP3004/3008 with Microcontroller (MCU) SPI Ports

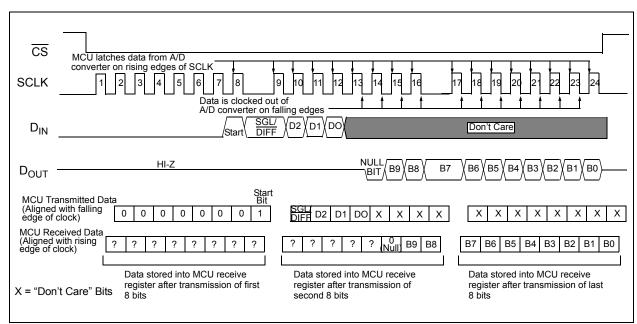

With most microcontroller SPI ports, it is required to send groups of eight bits. It is also required that the microcontroller SPI port be configured to clock out data on the falling edge of clock and latch data in on the rising edge. Because communication with the MCP3004/3008 devices may not need multiples of eight clocks, it will be necessary to provide more clocks than are required. This is usually done by sending 'leading zeros' before the start bit. As an example, Figure 6-1 and Figure 6-2 shows how the MCP3004/ 3008 can be interfaced to a MCU with a hardware SPI port. Figure 6-1 depicts the operation shown in SPI Mode 0,0, which requires that the SCLK from the MCU idles in the 'low' state, while Figure 6-2 shows the similar case of SPI Mode 1,1, where the clock idles in the 'high' state.

As is shown in Figure 6-1, the first byte transmitted to the A/D converter contains seven leading zeros before the start bit. Arranging the leading zeros this way induces the 10 data bits to fall in positions easily manipulated by the MCU. The MSB is clocked out of the A/D converter on the falling edge of clock number 14. Once the second eight clocks have been sent to the device, the MCU receive buffer will contain five unknown bits (the output is at high-impedance for the first two clocks), the null bit and the highest order 2 bits of the conversion. Once the third byte has been sent to the device, the receive register will contain the lowest order eight bits of the conversion results. Employing this method ensures simpler manipulation of the converted data.

Figure 6-2 shows the same thing in SPI Mode 1,1, which requires that the clock idles in the high state. As with mode 0,0, the A/D converter outputs data on the falling edge of the clock and the MCU latches data from the A/D converter in on the rising edge of the clock.

**FIGURE 6-1:** SPI Communication with the MCP3004/3008 using 8-bit segments (Mode 0,0: SCLK idles low).

FIGURE 6-2: SPI Communication with the MCP3004/3008 using 8-bit segments (Mode 1,1: SCLK idles high).

#### 6.2 Maintaining Minimum Clock Speed

When the MCP3004/3008 initiates the sample period. charge is stored on the sample capacitor. When the sample period is complete, the device converts one bit for each clock that is received. It is important for the user to note that a slow clock rate will allow charge to bleed off the sample capacitor while the conversion is taking place. At 85°C (worst case condition), the part will maintain proper charge on the sample capacitor for at least 1.2 ms after the sample period has ended. This means that the time between the end of the sample period and the time that all 10 data bits have been clocked out must not exceed 1.2 ms (effective clock frequency of 10 kHz). Failure to meet this criterion may introduce linearity errors into the conversion outside the rated specifications. It should be noted that during the entire conversion cycle, the A/D converter does not require a constant clock speed or duty cycle, as long as all timing specifications are met.

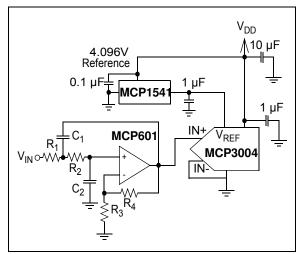

## 6.3 Buffering/Filtering the Analog Inputs

If the signal source for the A/D converter is not a low-impedance source, it will have to be buffered or inaccurate conversion results may occur (see Figure 4-2). It is also recommended that a filter be used to eliminate any signals that may be aliased back in to the conversion results, as is illustrated in Figure 6-3, where an op amp is used to drive, filter and gain the analog input of the MCP3004/3008. This amplifier provides a low-impedance source for the converter input, plus a low-pass filter, which eliminates unwanted high-frequency noise.

Low-pass (anti-aliasing) filters can be designed using Microchip's free interactive FilterLab<sup>®</sup> software. FilterLab will calculate capacitor and resistors values, as well as determine the number of poles that are required for the application. For more information on filtering signals, see AN699, "Anti-Aliasing Analog Filters for Data Acquisition Systems".

FIGURE 6-3: The MCP601 Operational Amplifier is used to implement a second order anti-aliasing filter for the signal being converted by the MCP3004.

#### 6.4 Layout Considerations

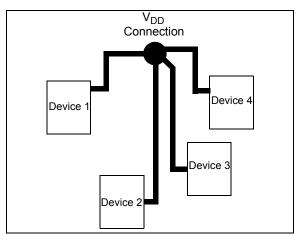

When laying out a printed circuit board for use with analog components, care should be taken to reduce noise wherever possible. A bypass capacitor should always be used with this device and should be placed as close as possible to the device pin. A bypass capacitor value of 1  $\mu$ F is recommended.

Digital and analog traces should be separated as much as possible on the board, with no traces running underneath the device or bypass capacitor. Extra precautions should be taken to keep traces with high-frequency signals (such as clock lines) as far as possible from analog traces.

Use of an analog ground plane is recommended in order to keep the ground potential the same for all devices on the board. Providing V<sub>DD</sub> connections to devices in a "star" configuration can also reduce noise by eliminating return current paths and associated errors (see Figure 6-4). For more information on layout tips when using A/D converters, refer to AN688, "Layout Tips for 12-Bit A/D Converter Applications".

**FIGURE 6-4:**  $V_{DD}$  traces arranged in a 'Star' configuration in order to reduce errors caused by current return paths.

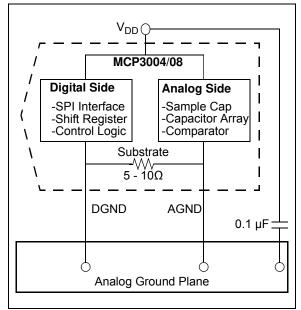

### 6.5 Utilizing the Digital and Analog Ground Pins

The MCP3004/3008 devices provide both digital and analog ground connections to provide additional means of noise reduction. As is shown in Figure 6-5, the analog and digital circuitry is separated internal to the device. This reduces noise from the digital portion of the device being coupled into the analog portion of the device. The two grounds are connected internally through the substrate which has a resistance of 5 -10  $\Omega$ .

If no ground plane is utilized, both grounds must be connected to  $V_{\rm SS}$  on the board. If a ground plane is available, both digital and analog ground pins should be connected to the analog ground plane. If both an analog and a digital ground plane are available, both the digital and the analog ground pins should be connected to the analog ground plane. Following these steps will reduce the amount of digital noise from the rest of the board being coupled into the A/D converter.

**FIGURE 6-5:** Separation of Analog and Digital Ground Pins.

**NOTES:**

#### 7.0 PACKAGING INFORMATION

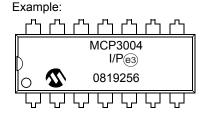

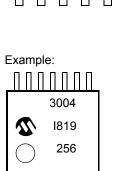

#### 7.1 Package Marking Information

MCP3004

ISL@3

0819256

Example:

Legend: XX...X Customer-specific information

Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

By Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (a)

can be found on the outer packaging for this package.

Note: In the event the full Microchip part number cannot be marked on one line, it will

for customer-specific information.

be carried over to the next line, thus limiting the number of available characters